# E. Lattice Semiconductor Corporation - <u>LFE3-35EA-7LFN484C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 4125                                                                          |

| Number of Logic Elements/Cells | 33000                                                                         |

| Total RAM Bits                 | 1358848                                                                       |

| Number of I/O                  | 295                                                                           |

| Number of Gates                |                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 484-BBGA                                                                      |

| Supplier Device Package        | 484-FPBGA (23x23)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-35ea-7lfn484c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeECP3 Family Data Sheet Introduction

#### February 2012

## **Features**

- Higher Logic Density for Increased System Integration

- 17K to 149K LUTs

- 116 to 586 I/Os

- Embedded SERDES

- 150 Mbps to 3.2 Gbps for Generic 8b10b, 10-bit SERDES, and 8-bit SERDES modes

- Data Rates 230 Mbps to 3.2 Gbps per channel for all other protocols

- Up to 16 channels per device: PCI Express, SONET/SDH, Ethernet (1GbE, SGMII, XAUI), CPRI, SMPTE 3G and Serial RapidIO

#### ■ sysDSP<sup>™</sup>

- Fully cascadable slice architecture

- 12 to 160 slices for high performance multiply and accumulate

- Powerful 54-bit ALU operations

- Time Division Multiplexing MAC Sharing

- Rounding and truncation

- Each slice supports

- -Half 36x36, two 18x18 or four 9x9 multipliers

- Advanced 18x36 MAC and 18x18 Multiply-

- Multiply-Accumulate (MMAC) operations

#### ■ Flexible Memory Resources

- Up to 6.85Mbits sysMEM<sup>™</sup> Embedded Block RAM (EBR)

- 36K to 303K bits distributed RAM

- sysCLOCK Analog PLLs and DLLs

Two DLLs and up to ten PLLs per device

- Pre-Engineered Source Synchronous I/O

- DDR registers in I/O cells

#### Table 1-1. LatticeECP3™ Family Selection Guide

• Dedicated read/write levelling functionality

Data Sheet DS1021

- Dedicated gearing logic

- Source synchronous standards support

ADC/DAC, 7:1 LVDS, XGMII

Link Speed ADC/DAC devices

- -High Speed ADC/DAC devices

- Dedicated DDR/DDR2/DDR3 memory with DQS support

- Optional Inter-Symbol Interference (ISI) correction on outputs

- Programmable sysl/O<sup>TM</sup> Buffer Supports Wide Range of Interfaces

- On-chip termination

- Optional equalization filter on inputs

- LVTTL and LVCMOS 33/25/18/15/12

- SSTL 33/25/18/15 I, II

- HSTL15 I and HSTL18 I, II

- PCI and Differential HSTL, SSTL

- LVDS, Bus-LVDS, LVPECL, RSDS, MLVDS

- Flexible Device Configuration

- Dedicated bank for configuration I/Os

- SPI boot flash interface

- Dual-boot images supported

- Slave SPI

- TransFR™ I/O for simple field updates

- Soft Error Detect embedded macro

#### System Level Support

- IEEE 1149.1 and IEEE 1532 compliant

- Reveal Logic Analyzer

- ORCAstra FPGA configuration utility

- · On-chip oscillator for initialization & general use

- 1.2 V core power supply

| ECP3-17            | ECP3-35                                                                               | ECP3-70                                                                                                                                                                                                         | ECP3-95                                               | ECP3-150                                              |

|--------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| 17                 | 33                                                                                    | 67                                                                                                                                                                                                              | 92                                                    | 149                                                   |

| 38                 | 72                                                                                    | 240                                                                                                                                                                                                             | 240                                                   | 372                                                   |

| 700                | 1327                                                                                  | 4420                                                                                                                                                                                                            | 4420                                                  | 6850                                                  |

| 36                 | 68                                                                                    | 145                                                                                                                                                                                                             | 188                                                   | 303                                                   |

| 24                 | 64                                                                                    | 128                                                                                                                                                                                                             | 128                                                   | 320                                                   |

| 1                  | 1                                                                                     | 3                                                                                                                                                                                                               | 3                                                     | 4                                                     |

| 2/2                | 4/2                                                                                   | 10/2                                                                                                                                                                                                            | 10 / 2                                                | 10/2                                                  |

| ls/ I/O Combinatio | ns                                                                                    | •                                                                                                                                                                                                               |                                                       | •                                                     |

| 2/116              |                                                                                       |                                                                                                                                                                                                                 |                                                       |                                                       |

| 4 / 133            | 4 / 133                                                                               |                                                                                                                                                                                                                 |                                                       |                                                       |

| 4 / 222            | 4 / 295                                                                               | 4 / 295                                                                                                                                                                                                         | 4 / 295                                               |                                                       |

|                    | 4 / 310                                                                               | 8 / 380                                                                                                                                                                                                         | 8 / 380                                               | 8 / 380                                               |

|                    |                                                                                       | 12 / 490                                                                                                                                                                                                        | 12 / 490                                              | 16 / 586                                              |

|                    | 17<br>38<br>700<br>36<br>24<br>1<br>2 / 2<br>Is/ I/O Combinatio<br>2 / 116<br>4 / 133 | 17      33        38      72        700      1327        36      68        24      64        1      1        2/2      4/2        Is/I/O Combinations      2/116        4/133      4/133        4/222      4/295 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Introduction

The LatticeECP3<sup>™</sup> (EConomy Plus Third generation) family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES and high speed source synchronous interfaces in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 65 nm technology making the devices suitable for high-volume, high-speed, low-cost applications.

The LatticeECP3 device family expands look-up-table (LUT) capacity to 149K logic elements and supports up to 586 user I/Os. The LatticeECP3 device family also offers up to 320 18 x 18 multipliers and a wide range of parallel I/O standards.

The LatticeECP3 FPGA fabric is optimized with high performance and low cost in mind. The LatticeECP3 devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), Delay Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the LatticeECP3 device family supports a broad range of interface standards, including DDR3, XGMII and 7:1 LVDS.

The LatticeECP3 device family also features high speed SERDES with dedicated PCS functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, SMPTE, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit Pre-emphasis and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The LatticeECP3 devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

The Lattice Diamond<sup>™</sup> and ispLEVER<sup>®</sup> design software allows large complex designs to be efficiently implemented using the LatticeECP3 FPGA family. Synthesis library support for LatticeECP3 is available for popular logic synthesis tools. Diamond and ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP3 device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the LatticeECP3 family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

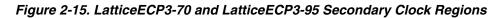

#### Table 2-6. Secondary Clock Regions

| Device   | Number of Secondary Clock<br>Regions |

|----------|--------------------------------------|

| ECP3-17  | 16                                   |

| ECP3-35  | 16                                   |

| ECP3-70  | 20                                   |

| ECP3-95  | 20                                   |

| ECP3-150 | 36                                   |

Spine Repeaters

### Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports the following forms of write behavior for single port or dual port operation:

- 1. **Normal** Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- 3. **Read-Before-Write (EA devices only)** When new data is written, the old content of the address appears at the output. This mode is supported for x9, x18, and x36 data widths.

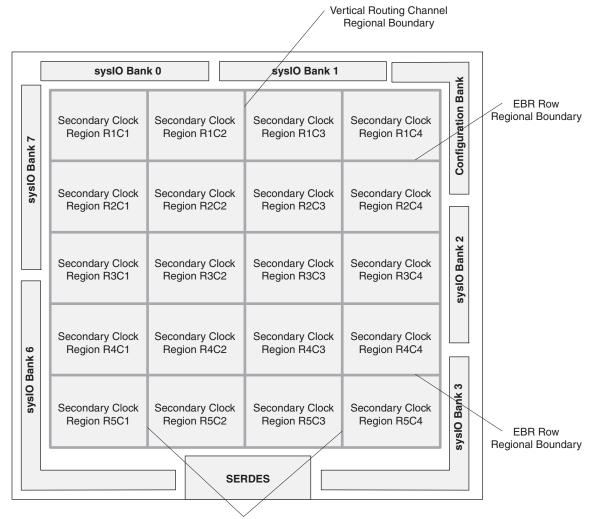

#### Memory Core Reset

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal can reset both ports. The output data latches and associated resets for both ports are as shown in Figure 2-22.

#### Figure 2-22. Memory Core Reset

For further information on the sysMEM EBR block, please see the list of technical documentation at the end of this data sheet.

# sysDSP<sup>™</sup> Slice

The LatticeECP3 family provides an enhanced sysDSP architecture, making it ideally suited for low-cost, high-performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters, Fast Fourier Transforms (FFT) functions, Correlators, Reed-Solomon/Turbo/Convolution encoders and decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

### sysDSP Slice Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeECP3, on the other hand, has many DSP slices that support different data widths.

## ALU Flags

The sysDSP slice provides a number of flags from the ALU including:

- Equal to zero (EQZ)

- Equal to zero with mask (EQZM)

- Equal to one with mask (EQOM)

- Equal to pattern with mask (EQPAT)

- Equal to bit inverted pattern with mask (EQPATB)

- Accumulator Overflow (OVER)

- Accumulator Underflow (UNDER)

- Either over or under flow supporting LatticeECP2 legacy designs (OVERUNDER)

## **Clock, Clock Enable and Reset Resources**

Global Clock, Clock Enable and Reset signals from routing are available to every sysDSP slice. From four clock sources (CLK0, CLK1, CLK2, and CLK3) one clock is selected for each input register, pipeline register and output register. Similarly Clock Enable (CE) and Reset (RST) are selected at each input register, pipeline register and output register.

# **Resources Available in the LatticeECP3 Family**

Table 2-9 shows the maximum number of multipliers for each member of the LatticeECP3 family. Table 2-10 shows the maximum available EBR RAM Blocks in each LatticeECP3 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

| Device   | DSP Slices | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|----------|------------|----------------|------------------|------------------|

| ECP3-17  | 12         | 48             | 24               | 6                |

| ECP3-35  | 32         | 128            | 64               | 16               |

| ECP3-70  | 64         | 256            | 128              | 32               |

| ECP3-95  | 64         | 256            | 128              | 32               |

| ECP3-150 | 160        | 640            | 320              | 80               |

Table 2-9. Maximum Number of DSP Slices in the LatticeECP3 Family

Table 2-10. Embedded SRAM in the LatticeECP3 Family

| Device   | EBR SRAM Block | Total EBR SRAM<br>(Kbits) |

|----------|----------------|---------------------------|

| ECP3-17  | 38             | 700                       |

| ECP3-35  | 72             | 1327                      |

| ECP3-70  | 240            | 4420                      |

| ECP3-95  | 240            | 4420                      |

| ECP3-150 | 372            | 6850                      |

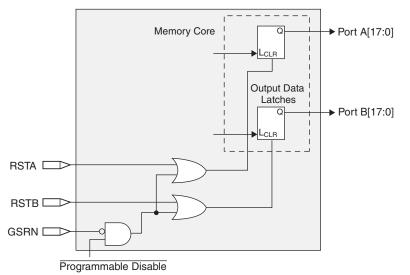

Figure 2-34. Output and Tristate Block for Left and Right Edges

# Tristate Register Block

The tristate register block registers tri-state control signals from the core of the device before they are passed to the sysl/O buffers. The block contains a register for SDR operation and an additional register for DDR operation.

In SDR and non-gearing DDR modes, TS input feeds one of the flip-flops that then feeds the output. In DDRX2 mode, the register TS input is fed into another register that is clocked using the DQCLK0 and DQCLK1 signals. The output of this register is used as a tristate control.

# **ISI** Calibration

The setting for Inter-Symbol Interference (ISI) cancellation occurs in the output register block. ISI correction is only available in the DDRX2 modes. ISI calibration settings exist once per output register block, so each I/O in a DQS-12 group may have a different ISI calibration setting.

The ISI block extends output signals at certain times, as a function of recent signal history. So, if the output pattern consists of a long strings of 0's to long strings of 1's, there are no delays on output signals. However, if there are quick, successive transitions from 010, the block will stretch out the binary 1. This is because the long trail of 0's will cause these symbols to interfere with the logic 1. Likewise, if there are quick, successive transitions from 101, the block will stretch out the binary 0. This block is controlled by a 3-bit delay control that can be set in the DQS control logic block.

For more information about this topic, please see the list of technical documentation at the end of this data sheet.

#### Figure 2-36. Edge Clock, DLL Calibration and DQS Local Bus Distribution

DQS Strobe and Transition Detect Logic

#### I/O Ring

\*Includes shared configuration I/Os and dedicated configuration I/Os.

To accomplish write leveling in DDR3, each DQS group has a slightly different delay that is set by DYN DELAY[7:0] in the DQS Write Control logic block. The DYN DELAY can set 128 possible delay step settings. In addition, the most significant bit will invert the clock for a 180-degree shift of the incoming clock.

LatticeECP3 input and output registers can also support DDR gearing that is used to receive and transmit the high speed DDR data from and to the DDR3 Memory.

LatticeECP3 supports the 1.5V SSTL I/O standard required for the DDR3 memory interface. For more information, refer to the sysIO section of this data sheet.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on DDR Memory interface implementation in LatticeECP3.

# sysl/O Buffer

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow users to implement the wide variety of standards that are found in today's systems including LVDS, BLVDS, HSTL, SSTL Class I & II, LVCMOS, LVTTL, LVPECL, PCI.

### sysl/O Buffer Banks

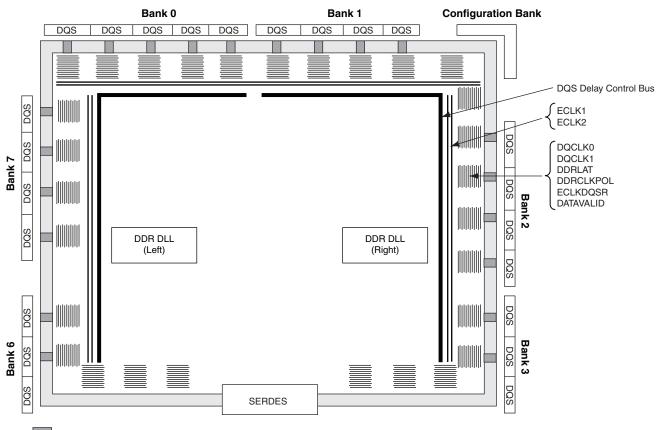

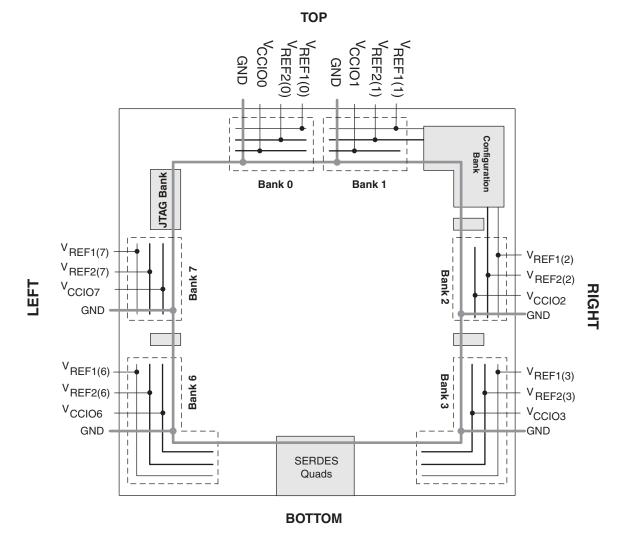

LatticeECP3 devices have six sysl/O buffer banks: six banks for user I/Os arranged two per side. The banks on the bottom side are wraparounds of the banks on the lower right and left sides. The seventh sysl/O buffer bank (Configuration Bank) is located adjacent to Bank 2 and has dedicated/shared I/Os for configuration. When a shared pin is not used for configuration it is available as a user I/O. Each bank is capable of supporting multiple I/O standards. Each sysl/O bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, each bank, except the Configuration Bank, has voltage references,  $V_{REF1}$  and  $V_{REF2}$ , which allow it to be completely independent from the others. Figure 2-38 shows the seven banks and their associated supplies.

In LatticeECP3 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

### Figure 2-38. LatticeECP3 Banks

LatticeECP3 devices contain two types of sysI/O buffer pairs.

#### 1. Top (Bank 0 and Bank 1) and Bottom sysIO Buffer Pairs (Single-Ended Outputs Only)

The sysl/O buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be configured as a differential input. Only the top edge buffers have a programmable PCI clamp.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

The top and bottom sides are ideal for general purpose I/O, PCI, and inputs for LVDS (LVDS outputs are only allowed on the left and right sides). The top side can be used for the DDR3 ADDR/CMD signals.

The I/O pins located on the top and bottom sides of the device (labeled PTxxA/B or PBxxA/B) are fully hot socketable. Note that the pads in Banks 3, 6 and 8 are wrapped around the corner of the device. In these banks, only the pads located on the top or bottom of the device are hot socketable. The top and bottom side pads can be identified by the Lattice Diamond tool.

| Package    | ECP3-17    | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|------------|------------|---------|---------|---------|----------|

| 256 ftBGA  | 1          | 1       | —       | —       | —        |

| 328 csBGA  | 2 channels | —       | —       | —       | _        |

| 484 fpBGA  | 1          | 1       | 1       | 1       |          |

| 672 fpBGA  | —          | 1       | 2       | 2       | 2        |

| 1156 fpBGA | —          | —       | 3       | 3       | 4        |

### SERDES Block

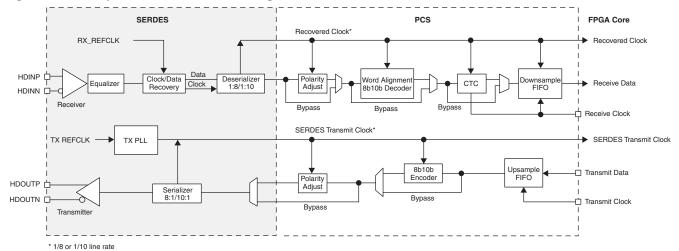

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2-41 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCOB and VCCIB).

Figure 2-41. Simplified Channel Block Diagram for SERDES/PCS Block

# PCS

As shown in Figure 2-41, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic.

# SERDES Power Supply Requirements<sup>1, 2, 3</sup>

| Symbol                   | Description                            | Тур. | Max. | Units |

|--------------------------|----------------------------------------|------|------|-------|

| Standby (Power I         | Down)                                  | •    |      |       |

| I <sub>CCA-SB</sub>      | V <sub>CCA</sub> current (per channel) | 3    | 5    | mA    |

| I <sub>CCIB-SB</sub>     | Input buffer current (per channel)     | —    | —    | mA    |

| I <sub>CCOB-SB</sub>     | Output buffer current (per channel)    | —    | —    | mA    |

| Operating (Data F        | Rate = 3.2 Gbps)                       |      |      | •     |

| I <sub>CCA-OP</sub>      | V <sub>CCA</sub> current (per channel) | 68   | 77   | mA    |

| I <sub>CCIB-OP</sub>     | Input buffer current (per channel)     | 5    | 7    | mA    |

| I <sub>CCOB-OP</sub>     | Output buffer current (per channel)    | 19   | 25   | mA    |

| Operating (Data F        | Rate = 2.5 Gbps)                       |      |      | •     |

| I <sub>CCA-OP</sub>      | V <sub>CCA</sub> current (per channel) | 66   | 76   | mA    |

| I <sub>CCIB-OP</sub>     | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub>     | Output buffer current (per channel)    | 15   | 18   | mA    |

| Operating (Data F        | Rate = 1.25 Gbps)                      |      |      | •     |

| I <sub>CCA-OP</sub>      | V <sub>CCA</sub> current (per channel) | 62   | 72   | mA    |

| I <sub>CCIB-OP</sub>     | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub>     | Output buffer current (per channel)    | 15   | 18   | mA    |

| <b>Operating</b> (Data I | Rate = 250 Mbps)                       | •    |      |       |

| I <sub>CCA-OP</sub>      | V <sub>CCA</sub> current (per channel) | 55   | 65   | mA    |

| I <sub>CCIB-OP</sub>     | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub>     | Output buffer current (per channel)    | 14   | 17   | mA    |

| Operating (Data F        | Rate = 150 Mbps)                       | •    | •    | •     |

| I <sub>CCA-OP</sub>      | V <sub>CCA</sub> current (per channel) | 55   | 65   | mA    |

| I <sub>CCIB-OP</sub>     | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub>     | Output buffer current (per channel)    | 14   | 17   | mA    |

1. Equalization enabled, pre-emphasis disabled.

2. One quarter of the total quad power (includes contribution from common circuits, all channels in the quad operating, pre-emphasis disabled, equalization enabled).

3. Pre-emphasis adds 20 mA to ICCA-OP data.

# sysl/O Recommended Operating Conditions

|                                                |           | V <sub>CCIO</sub> |           |       | V <sub>REF</sub> (V) |       |  |  |

|------------------------------------------------|-----------|-------------------|-----------|-------|----------------------|-------|--|--|

| Standard                                       | Min.      | Тур.              | Max.      | Min.  | Тур.                 | Max.  |  |  |

| LVCMOS33 <sup>2</sup>                          | 3.135     | 3.3               | 3.465     | —     | —                    |       |  |  |

| LVCMOS33D                                      | 3.135     | 3.3               | 3.465     | —     | —                    | —     |  |  |

| LVCMOS25 <sup>2</sup>                          | 2.375     | 2.5               | 2.625     | —     | —                    |       |  |  |

| LVCMOS18                                       | 1.71      | 1.8               | 1.89      | —     | —                    |       |  |  |

| LVCMOS15                                       | 1.425     | 1.5               | 1.575     | —     | —                    |       |  |  |

| LVCMOS12 <sup>2</sup>                          | 1.14      | 1.2               | 1.26      | —     | —                    |       |  |  |

| LVTTL33 <sup>2</sup>                           | 3.135     | 3.3               | 3.465     | —     | —                    |       |  |  |

| PCI33                                          | 3.135     | 3.3               | 3.465     | —     | —                    |       |  |  |

| SSTL15 <sup>3</sup>                            | 1.43      | 1.5               | 1.57      | 0.68  | 0.75                 | 0.9   |  |  |

| SSTL18_I, II <sup>2</sup>                      | 1.71      | 1.8               | 1.89      | 0.833 | 0.9                  | 0.969 |  |  |

| SSTL25_I, II <sup>2</sup>                      | 2.375     | 2.5               | 2.625     | 1.15  | 1.25                 | 1.35  |  |  |

| SSTL33_I, II <sup>2</sup>                      | 3.135     | 3.3               | 3.465     | 1.3   | 1.5                  | 1.7   |  |  |

| HSTL15_l <sup>2</sup>                          | 1.425     | 1.5               | 1.575     | 0.68  | 0.75                 | 0.9   |  |  |

| HSTL18_I, II <sup>2</sup>                      | 1.71      | 1.8               | 1.89      | 0.816 | 0.9                  | 1.08  |  |  |

| LVDS25 <sup>2</sup>                            | 2.375     | 2.5               | 2.625     | —     | _                    | _     |  |  |

| LVDS25E                                        | 2.375     | 2.5               | 2.625     | —     | —                    | —     |  |  |

| MLVDS <sup>1</sup>                             | 2.375     | 2.5               | 2.625     | —     | —                    | —     |  |  |

| LVPECL33 <sup>1, 2</sup>                       | 3.135     | 3.3               | 3.465     | —     | —                    |       |  |  |

| Mini LVDS                                      | 2.375     | 2.5               | 2.625     | —     | —                    | —     |  |  |

| BLVDS25 <sup>1, 2</sup>                        | 2.375     | 2.5               | 2.625     | —     | —                    | —     |  |  |

| RSDS <sup>2</sup>                              | 2.375     | 2.5               | 2.625     | —     | —                    |       |  |  |

| RSDSE <sup>1, 2</sup>                          | 2.375     | 2.5               | 2.625     | —     | —                    | —     |  |  |

| TRLVDS                                         | 3.14      | 3.3               | 3.47      | —     | —                    | —     |  |  |

| PPLVDS                                         | 3.14/2.25 | 3.3/2.5           | 3.47/2.75 | —     | —                    |       |  |  |

| SSTL15D <sup>3</sup>                           | 1.43      | 1.5               | 1.57      | —     | —                    |       |  |  |

| SSTL18D_I <sup>2, 3</sup> , II <sup>2, 3</sup> | 1.71      | 1.8               | 1.89      | —     | —                    |       |  |  |

| SSTL25D_ I <sup>2</sup> , II <sup>2</sup>      | 2.375     | 2.5               | 2.625     | —     | _                    | —     |  |  |

| SSTL33D_ I <sup>2</sup> , II <sup>2</sup>      | 3.135     | 3.3               | 3.465     | —     | _                    | —     |  |  |

| HSTL15D_ I <sup>2</sup>                        | 1.425     | 1.5               | 1.575     | —     | —                    | —     |  |  |

| HSTL18D_ I <sup>2</sup> , II <sup>2</sup>      | 1.71      | 1.8               | 1.89      | —     | —                    | —     |  |  |

1. Inputs on chip. Outputs are implemented with the addition of external resistors.

2. For input voltage compatibility, see TN1177, LatticeECP3 sysIO Usage Guide.

3. VREF is required when using Differential SSTL to interface to DDR memory.

## LVPECL33

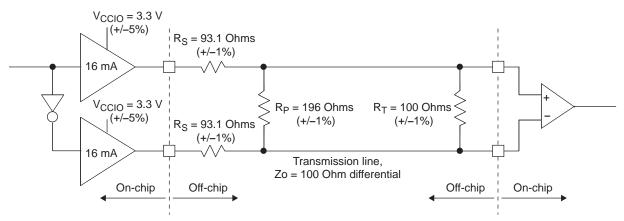

The LatticeECP3 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

#### Figure 3-3. Differential LVPECL33

#### Table 3-3. LVPECL33 DC Conditions<sup>1</sup>

| Parameter         | Description                      | Typical | Units |  |

|-------------------|----------------------------------|---------|-------|--|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 3.30    | V     |  |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10      | Ω     |  |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 93      | Ω     |  |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 196     | Ω     |  |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |  |

| V <sub>OH</sub>   | Output High Voltage              | 2.05    | V     |  |

| V <sub>OL</sub>   | Output Low Voltage               | 1.25    | V     |  |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.80    | V     |  |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.65    | V     |  |

| ZBACK             | Back Impedance                   | 100.5   | Ω     |  |

| I <sub>DC</sub>   | DC Output Current                | 12.11   | mA    |  |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                         |                                                 |                                  | _          | -8       | -        | -7        | _        | 6         |           |

|-------------------------|-------------------------------------------------|----------------------------------|------------|----------|----------|-----------|----------|-----------|-----------|

| Parameter               | Description                                     | Device                           | Min.       | Max.     | Min.     | Max.      | Min.     | Max.      | Units     |

|                         | nputs with Clock and Data (>10bi                | its wide) are Aligned at I       | Pin (GDD   | RX2_RX   | ECLK.A   | ligned)   |          |           |           |

| (No CLKDIV)             | des Using DLLCLKPIN for Clock                   | Innut                            |            |          |          |           |          |           |           |

|                         | Data Setup Before CLK                           | ECP3-150EA                       | _          | 0.225    | _        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVACLKGDDR</sub> | Data Hold After CLK                             | ECP3-150EA                       | 0.775      | 0.225    | 0.775    | 0.225     | 0.775    | 0.225     | UI        |

|                         | DDRX2 Clock Frequency                           | ECP3-150EA                       | 0.775      | 460      | 0.775    | 385       | 0.775    | 345       | MHz       |

| <sup>†</sup> MAX_GDDR   | Data Setup Before CLK                           |                                  | _          |          | _        |           | _        |           | UI        |

|                         | -                                               | ECP3-70EA/95EA                   | 0.775      | 0.225    |          | 0.225     |          | 0.225     |           |

| <sup>I</sup> DVECLKGDDR | Data Hold After CLK                             | ECP3-70EA/95EA<br>ECP3-70EA/95EA | 0.775      |          | 0.775    |           | 0.775    | -         | UI<br>MHz |

| fMAX_GDDR               | DDRX2 Clock Frequency                           |                                  | —          | 460      |          | 385       | —        | 311       |           |

|                         | Data Setup Before CLK                           | ECP3-35EA                        | - 700      | 0.210    | -        | 0.210     | -        | 0.210     |           |

|                         | Data Hold After CLK                             | ECP3-35EA                        | 0.790      | -        | 0.790    | -         | 0.790    | _         | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-35EA                        | _          | 460      | _        | 385       | _        | 311       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK<br>(Left and Right Sides) | ECP3-17EA                        | _          | 0.210    | _        | 0.210     | _        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-17EA                        | 0.790      | —        | 0.790    | —         | 0.790    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-17EA                        | _          | 460      |          | 385       |          | 311       | MHz       |

| Top Side Using P        | CLK Pin for Clock Input                         |                                  |            |          |          |           |          |           |           |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-150EA                       |            | 0.225    | —        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-150EA                       | 0.775      | —        | 0.775    | —         | 0.775    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-150EA                       | _          | 235      | —        | 170       | _        | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-70EA/95EA                   | _          | 0.225    |          | 0.225     |          | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-70EA/95EA                   | 0.775      |          | 0.775    |           | 0.775    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-70EA/95EA                   | _          | 235      |          | 170       |          | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-35EA                        |            | 0.210    | —        | 0.210     | _        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-35EA                        | 0.790      | —        | 0.790    | —         | 0.790    | _         | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-35EA                        | _          | 235      | —        | 170       | _        | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-17EA                        | _          | 0.210    | —        | 0.210     | —        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-17EA                        | 0.790      | _        | 0.790    | _         | 0.790    | —         | UI        |

| f <sub>MAX GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-17EA                        | _          | 235      | _        | 170       |          | 130       | MHz       |

| -                       | nputs with Clock and Data (<10 E                | Bits Wide) Centered at Pi        | in (GDDF   | X2_RX.   | DQS.Cen  | tered) U  | sing DQ  | S Pin for | Clock     |

| Left and Right Sid      | des                                             |                                  |            |          |          |           |          |           |           |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK                           | All ECP3EA Devices               | 330        | _        | 330      | _         | 352      |           | ps        |

| t <sub>HOGDDR</sub>     | Data Hold After CLK                             | All ECP3EA Devices               | 330        | _        | 330      | —         | 352      | _         | ps        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | All ECP3EA Devices               | _          | 400      | _        | 400       | _        | 375       | MHz       |

|                         | nputs with Clock and Data (<10 E                | Bits Wide) Aligned at Pin        | (GDDR)     | (2 RX.D0 | QS.Align | ed) Usin  | g DQS Pi | n for Clo | ck Input  |

| Left and Right Sid      |                                                 | <b>J J J J J J J J J J</b>       | <b>1</b> - | _        | <b>J</b> | . ,       | <b>J</b> |           |           |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | All ECP3EA Devices               | —          | 0.225    | —        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | All ECP3EA Devices               | 0.775      | _        | 0.775    | _         | 0.775    | —         | UI        |

| f <sub>MAX GDDR</sub>   | DDRX2 Clock Frequency                           | All ECP3EA Devices               | _          | 400      | —        | 400       | _        | 375       | MHz       |

|                         | Output with Clock and Data (>10 I               | Bits Wide) Centered at P         | in (GDD    | RX1_TX.  | SCLK.Ce  | ntered)10 | )        |           | 1         |

| t <sub>DVBGDDR</sub>    | Data Valid Before CLK                           | ECP3-150EA                       | 670        | —        | 670      | _         | 670      |           | ps        |

| t <sub>DVAGDDR</sub>    | Data Valid After CLK                            | ECP3-150EA                       | 670        |          | 670      |           | 670      |           | ps        |

| f <sub>MAX_GDDR</sub>   | DDRX1 Clock Frequency                           | ECP3-150EA                       |            | 250      |          | 250       |          | 250       | MHz       |

|                         |                                                 |                                  | 666        |          | CCE      |           | 664      |           |           |

| t <sub>DVBGDDR</sub>    | Data Valid Before CLK                           | ECP3-70EA/95EA                   | 666        |          | 665      |           | 664      |           | ps        |

# Over Recommended Commercial Operating Conditions

# LatticeECP3 Internal Switching Characteristics<sup>1, 2, 5</sup>

|                         |                                                       | -8     |       | -7     |       | -6     |       |        |

|-------------------------|-------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|

| Parameter               | Description                                           | Min.   | Max.  | Min.   | Max.  | Min.   | Max.  | Units. |

| PFU/PFF Logi            | c Mode Timing                                         |        |       |        |       |        |       |        |

| t <sub>LUT4_PFU</sub>   | LUT4 delay (A to D inputs to F output)                |        | 0.147 | _      | 0.163 | _      | 0.179 | ns     |

| t <sub>LUT6_PFU</sub>   | LUT6 delay (A to D inputs to OFX output)              | —      | 0.281 | —      | 0.335 | —      | 0.379 | ns     |

| t <sub>LSR_PFU</sub>    | Set/Reset to output of PFU (Asynchronous)             | —      | 0.593 | —      | 0.674 | —      | 0.756 | ns     |

| t <sub>LSRREC_PFU</sub> | Asynchronous Set/Reset recovery time for<br>PFU Logic |        | 0.298 |        | 0.345 |        | 0.391 | ns     |

| t <sub>SUM_PFU</sub>    | Clock to Mux (M0,M1) Input Setup Time                 | 0.134  | —     | 0.144  | —     | 0.153  | —     | ns     |

| t <sub>HM_PFU</sub>     | Clock to Mux (M0,M1) Input Hold Time                  | -0.097 | —     | -0.103 |       | -0.109 |       | ns     |

| t <sub>SUD_PFU</sub>    | Clock to D input setup time                           | 0.061  | —     | 0.068  | —     | 0.075  | —     | ns     |

| t <sub>HD_PFU</sub>     | Clock to D input hold time                            | 0.019  | —     | 0.013  | —     | 0.015  | —     | ns     |

| t <sub>CK2Q_PFU</sub>   | Clock to Q delay, (D-type Register Configuration)     | _      | 0.243 | _      | 0.273 | _      | 0.303 | ns     |

| PFU Dual Port           | Memory Mode Timing                                    |        |       |        |       |        |       |        |

| t <sub>CORAM_PFU</sub>  | Clock to Output (F Port)                              | —      | 0.710 | —      | 0.803 | —      | 0.897 | ns     |

| t <sub>SUDATA_PFU</sub> | Data Setup Time                                       | -0.137 |       | -0.155 |       | -0.174 |       | ns     |

| t <sub>HDATA_PFU</sub>  | Data Hold Time                                        | 0.188  |       | 0.217  |       | 0.246  | —     | ns     |

| t <sub>SUADDR_PFU</sub> | Address Setup Time                                    | -0.227 | —     | -0.257 | —     | -0.286 | —     | ns     |

| t <sub>HADDR_PFU</sub>  | Address Hold Time                                     | 0.240  |       | 0.275  |       | 0.310  |       | ns     |

| t <sub>SUWREN_PFU</sub> | Write/Read Enable Setup Time                          | -0.055 |       | -0.055 |       | -0.063 | —     | ns     |

| t <sub>HWREN_PFU</sub>  | Write/Read Enable Hold Time                           | 0.059  |       | 0.059  |       | 0.071  |       | ns     |

| PIC Timing              |                                                       |        |       |        |       |        |       |        |

| PIO Input/Out           | put Buffer Timing                                     |        |       |        |       |        |       |        |

| t <sub>IN_PIO</sub>     | Input Buffer Delay (LVCMOS25)                         |        | 0.423 | —      | 0.466 | —      | 0.508 | ns     |

| t <sub>OUT_PIO</sub>    | Output Buffer Delay (LVCMOS25)                        |        | 1.241 | —      | 1.301 | —      | 1.361 | ns     |

| IOLOGIC Inpu            | t/Output Timing                                       |        |       |        |       |        |       |        |

| t <sub>SUI_PIO</sub>    | Input Register Setup Time (Data Before Clock)         | 0.956  | _     | 1.124  | _     | 1.293  | _     | ns     |

| t <sub>HI_PIO</sub>     | Input Register Hold Time (Data after Clock)           | 0.225  |       | 0.184  |       | 0.240  | —     | ns     |

| t <sub>COO_PIO</sub>    | Output Register Clock to Output Delay <sup>4</sup>    | -      | 1.09  | -      | 1.16  | -      | 1.23  | ns     |

| t <sub>SUCE_PIO</sub>   | Input Register Clock Enable Setup Time                | 0.220  | _     | 0.185  |       | 0.150  | _     | ns     |

| t <sub>HCE_PIO</sub>    | Input Register Clock Enable Hold Time                 | -0.085 |       | -0.072 |       | -0.058 |       | ns     |

| t <sub>SULSR_PIO</sub>  | Set/Reset Setup Time                                  | 0.117  |       | 0.103  |       | 0.088  | _     | ns     |

| t <sub>HLSR_PIO</sub>   | Set/Reset Hold Time                                   | -0.107 | _     | -0.094 |       | -0.081 | _     | ns     |

| EBR Timing              |                                                       |        |       |        |       |        |       |        |

| t <sub>CO_EBR</sub>     | Clock (Read) to output from Address or Data           | _      | 2.78  | —      | 2.89  | —      | 2.99  | ns     |

| t <sub>COO_EBR</sub>    | Clock (Write) to output from EBR output Register      | _      | 0.31  | —      | 0.32  | —      | 0.33  | ns     |

| t <sub>SUDATA_EBR</sub> | Setup Data to EBR Memory                              | -0.218 | —     | -0.227 | —     | -0.237 | —     | ns     |

| t <sub>HDATA_EBR</sub>  | Hold Data to EBR Memory                               | 0.249  | —     | 0.257  | —     | 0.265  | —     | ns     |

| t <sub>SUADDR_EBR</sub> | Setup Address to EBR Memory                           | -0.071 | —     | -0.070 | —     | -0.068 | —     | ns     |

| t <sub>HADDR_EBR</sub>  | Hold Address to EBR Memory                            | 0.118  | —     | 0.098  | —     | 0.077  | —     | ns     |

| t <sub>SUWREN_EBR</sub> | Setup Write/Read Enable to EBR Memory                 | -0.107 |       | -0.106 |       | -0.106 |       | ns     |

## **Over Recommended Commercial Operating Conditions**

#### Table 3-7. Channel Output Jitter

| Description   | Frequency  | Min. | Тур. | Max. | Units   |

|---------------|------------|------|------|------|---------|

| Deterministic | 3.125 Gbps | _    | _    | 0.17 | UI, p-p |

| Random        | 3.125 Gbps | _    | _    | 0.25 | UI, p-p |

| Total         | 3.125 Gbps | _    | _    | 0.35 | UI, p-p |

| Deterministic | 2.5 Gbps   | _    | _    | 0.17 | UI, p-p |

| Random        | 2.5 Gbps   | _    | _    | 0.20 | UI, p-p |

| Total         | 2.5 Gbps   | _    | _    | 0.35 | UI, p-p |

| Deterministic | 1.25 Gbps  | _    | _    | 0.10 | UI, p-p |

| Random        | 1.25 Gbps  | _    | _    | 0.22 | UI, p-p |

| Total         | 1.25 Gbps  | _    | _    | 0.24 | UI, p-p |

| Deterministic | 622 Mbps   | _    | _    | 0.10 | UI, p-p |

| Random        | 622 Mbps   | _    | _    | 0.20 | UI, p-p |

| Total         | 622 Mbps   | _    | _    | 0.24 | UI, p-p |

| Deterministic | 250 Mbps   | _    | _    | 0.10 | UI, p-p |

| Random        | 250 Mbps   | _    | _    | 0.18 | UI, p-p |

| Total         | 250 Mbps   | _    | _    | 0.24 | UI, p-p |

| Deterministic | 150 Mbps   | _    | —    | 0.10 | UI, p-p |

| Random        | 150 Mbps   | —    | —    | 0.18 | UI, p-p |

| Total         | 150 Mbps   | —    | —    | 0.24 | UI, p-p |

Note: Values are measured with PRBS 2<sup>7</sup>-1, all channels operating, FPGA logic active, I/Os around SERDES pins quiet, reference clock @ 10X mode.

# **SERDES High Speed Data Receiver**

#### Table 3-9. Serial Input Data Specifications

| Symbol                 | Description                                                                                           | Min.    | Тур. | Max.                               | Units |         |

|------------------------|-------------------------------------------------------------------------------------------------------|---------|------|------------------------------------|-------|---------|

|                        |                                                                                                       | 3.125 G | —    | —                                  | 136   | Bits    |

|                        |                                                                                                       | 2.5 G   | —    | —                                  | 144   |         |

|                        | Stream of nontransitions <sup>1</sup><br>(CID = Consecutive Identical Digits) @ 10 <sup>-12</sup> BER | 1.485 G | —    | —                                  | 160   |         |

| RX-CID <sub>S</sub>    |                                                                                                       | 622 M   | —    | —                                  | 204   |         |

|                        |                                                                                                       | 270 M   | —    | —                                  | 228   |         |

|                        |                                                                                                       | 150 M   | —    | —                                  | 296   |         |

| V <sub>RX-DIFF-S</sub> | Differential input sensitivity                                                                        |         | 150  | —                                  | 1760  | mV, p-p |

| V <sub>RX-IN</sub>     | Input levels                                                                                          | 0       | —    | V <sub>CCA</sub> +0.5 <sup>4</sup> | V     |         |

| V <sub>RX-CM-DC</sub>  | Input common mode range (DC coupled)                                                                  | 0.6     | —    | V <sub>CCA</sub>                   | V     |         |

| V <sub>RX-CM-AC</sub>  | Input common mode range (AC coupled) <sup>3</sup>                                                     | 0.1     | —    | V <sub>CCA</sub> +0.2              | V     |         |

| T <sub>RX-RELOCK</sub> | SCDR re-lock time <sup>2</sup>                                                                        | —       | 1000 | —                                  | Bits  |         |

| Z <sub>RX-TERM</sub>   | Input termination 50/75 Ohm/High Z                                                                    |         | -20% | 50/75/HiZ                          | +20%  | Ohms    |

| RL <sub>RX-RL</sub>    | Return loss (without package)                                                                         | 10      |      |                                    | dB    |         |

1. This is the number of bits allowed without a transition on the incoming data stream when using DC coupling.

2. This is the typical number of bit times to re-lock to a new phase or frequency within +/- 300 ppm, assuming 8b10b encoded data.

3. AC coupling is used to interface to LVPECL and LVDS. LVDS interfaces are found in laser drivers and Fibre Channel equipment. LVDS interfaces are generally found in 622 Mbps SERDES devices.

4. Up to 1.76 V.

## Input Data Jitter Tolerance

A receiver's ability to tolerate incoming signal jitter is very dependent on jitter type. High speed serial interface standards have recognized the dependency on jitter type and have specifications to indicate tolerance levels for different jitter types as they relate to specific protocols. Sinusoidal jitter is considered to be a worst case jitter type.

| Description   | Frequency  | Condition               | Min. | Тур. | Max. | Units   |

|---------------|------------|-------------------------|------|------|------|---------|

| Deterministic |            | 600 mV differential eye | —    | —    | 0.47 | UI, p-p |

| Random        | 3.125 Gbps | 600 mV differential eye | —    | —    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | —    | —    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | —    | —    | 0.47 | UI, p-p |

| Random        | 2.5 Gbps   | 600 mV differential eye | —    | —    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | —    | —    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | —    | —    | 0.47 | UI, p-p |

| Random        | 1.25 Gbps  | 600 mV differential eye | —    | —    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | —    | —    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | —    | —    | 0.47 | UI, p-p |

| Random        | 622 Mbps   | 600 mV differential eye | —    | —    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | —    | —    | 0.65 | UI, p-p |

Table 3-10. Receiver Total Jitter Tolerance Specification

Note: Values are measured with CJPAT, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal, room temperature.

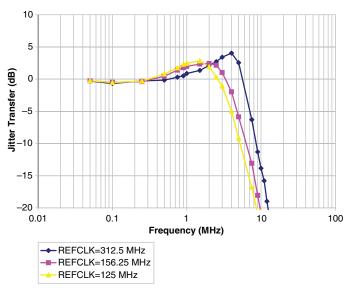

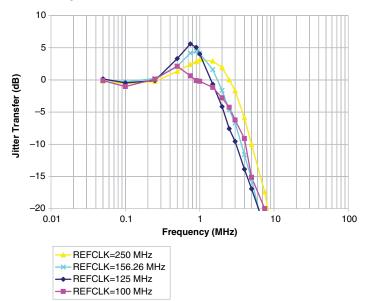

### Figure 3-14. Jitter Transfer – 3.125 Gbps

Figure 3-15. Jitter Transfer – 2.5 Gbps

# LatticeECP3 sysCONFIG Port Timing Specifications (Continued)

**Over Recommended Operating Conditions**

| Parameter         | Description                              | Min. | Max. | Units |

|-------------------|------------------------------------------|------|------|-------|

| t <sub>SSCL</sub> | CCLK Minimum Low Pulse                   | 5    | _    | ns    |

| t <sub>HLCH</sub> | HOLDN Low Setup Time (Relative to CCLK)  | 5    | _    | ns    |

| t <sub>CHHH</sub> | HOLDN Low Hold Time (Relative to CCLK)   | 5    | _    | ns    |

| Master and        | Slave SPI (Continued)                    |      |      |       |

| t <sub>CHHL</sub> | HOLDN High Hold Time (Relative to CCLK)  | 5    | _    | ns    |

| t <sub>HHCH</sub> | HOLDN High Setup Time (Relative to CCLK) | 5    | _    | ns    |

| t <sub>HLQZ</sub> | HOLDN to Output High-Z                   | —    | 9    | ns    |

| t <sub>HHQX</sub> | HOLDN to Output Low-Z                    | —    | 9    | ns    |

1. Re-toggling the PROGRAMN pin is not permitted until the INITN pin is high. Avoid consecutive toggling of the PROGRAMN.

| Parameter              | Min.                 | Max.                 | Units |

|------------------------|----------------------|----------------------|-------|

| Master Clock Frequency | Selected value - 15% | Selected value + 15% | MHz   |

| Duty Cycle             | 40                   | 60                   | %     |

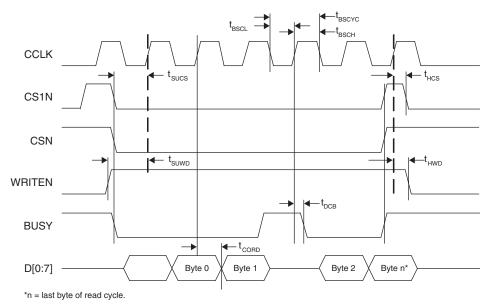

#### Figure 3-20. sysCONFIG Parallel Port Read Cycle

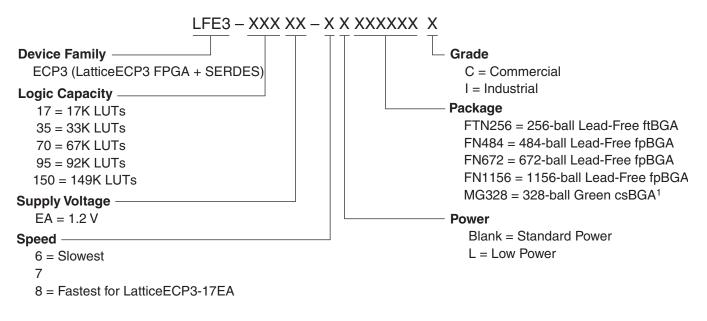

# LatticeECP3 Family Data Sheet Ordering Information

April 2014

Data Sheet DS1021

# LatticeECP3 Part Number Description

1. Green = Halogen free and lead free.

# **Ordering Information**

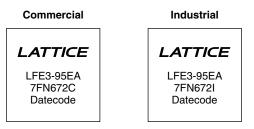

LatticeECP3 devices have top-side markings, for commercial and industrial grades, as shown below:

Note: See PCN 05A-12 for information regarding a change to the top-side mark logo.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.