# E. Lattice Semiconductor Corporation - <u>LFE3-35EA-8LFN484I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 4125                                                                          |

| Number of Logic Elements/Cells | 33000                                                                         |

| Total RAM Bits                 | 1358848                                                                       |

| Number of I/O                  | 295                                                                           |

| Number of Gates                |                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

| Package / Case                 | 484-BBGA                                                                      |

| Supplier Device Package        | 484-FPBGA (23x23)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-35ea-8lfn484i |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

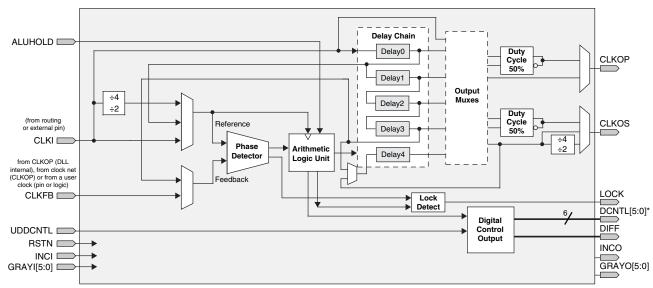

chain in order to better match the reference and feedback signals. This digital code from the ALU is also transmitted via the Digital Control bus (DCNTL) bus to its associated Slave Delay lines (two per DLL). The ALUHOLD input allows the user to suspend the ALU output at its current value. The UDDCNTL signal allows the user to latch the current value on the DCNTL bus.

The DLL has two clock outputs, CLKOP and CLKOS. These outputs can individually select one of the outputs from the tapped delay line. The CLKOS has optional fine delay shift and divider blocks to allow this output to be further modified, if required. The fine delay shift block allows the CLKOS output to phase shifted a further 45, 22.5 or 11.25 degrees relative to its normal position. Both the CLKOS and CLKOP outputs are available with optional duty cycle correction. Divide by two and divide by four frequencies are available at CLKOS. The LOCK output signal is asserted when the DLL is locked. Figure 2-5 shows the DLL block diagram and Table 2-5 provides a description of the DLL inputs and outputs.

The user can configure the DLL for many common functions such as time reference delay mode and clock injection removal mode. Lattice provides primitives in its design tools for these functions.

Figure 2-5. Delay Locked Loop Diagram (DLL)

\* This signal is not user accessible. This can only be used to feed the slave delay line.

### Secondary Clock/Control Sources

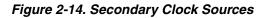

LatticeECP3 devices derive eight secondary clock sources (SC0 through SC7) from six dedicated clock input pads and the rest from routing. Figure 2-14 shows the secondary clock sources. All eight secondary clock sources are defined as inputs to a per-region mux SC0-SC7. SC0-SC3 are primary for control signals (CE and/or LSR), and SC4-SC7 are for the clock.

In an actual implementation, there is some overlap to maximize routability. In addition to SC0-SC3, SC7 is also an input to the control signals (LSR or CE). SC0-SC2 are also inputs to clocks along with SC4-SC7.

Note: Clock inputs can be configured in differential or single-ended mode.

### Secondary Clock/Control Routing

Global secondary clock is a secondary clock that is distributed to all regions. The purpose of the secondary clock routing is to distribute the secondary clock sources to the secondary clock regions. Secondary clocks in the LatticeECP3 devices are region-based resources. Certain EBR rows and special vertical routing channels bind the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP slice in the DSP row or the center of the DSP row. Figure 2-15 shows this special vertical routing channel and the 20 secondary clock regions for the LatticeECP3 family of devices. All devices in the LatticeECP3 family have eight secondary clock resources per region (SC0 to SC7). The same secondary clock routing can be used for control signals.

### Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports the following forms of write behavior for single port or dual port operation:

- 1. **Normal** Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- 3. **Read-Before-Write (EA devices only)** When new data is written, the old content of the address appears at the output. This mode is supported for x9, x18, and x36 data widths.

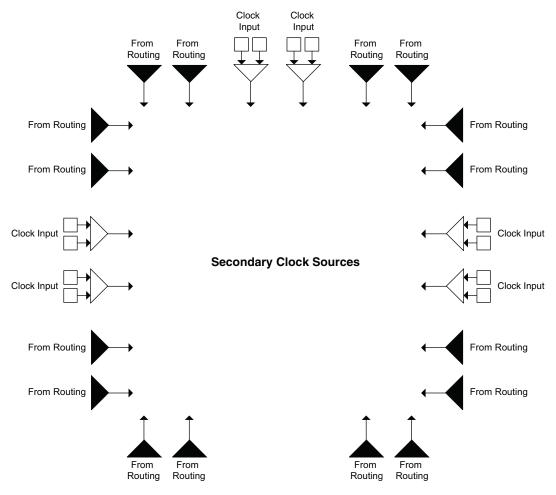

### Memory Core Reset

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal can reset both ports. The output data latches and associated resets for both ports are as shown in Figure 2-22.

#### Figure 2-22. Memory Core Reset

For further information on the sysMEM EBR block, please see the list of technical documentation at the end of this data sheet.

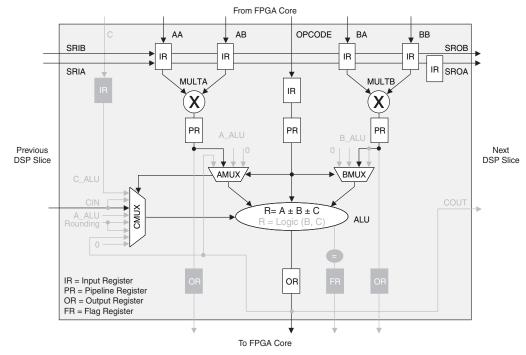

### sysDSP<sup>™</sup> Slice

The LatticeECP3 family provides an enhanced sysDSP architecture, making it ideally suited for low-cost, high-performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters, Fast Fourier Transforms (FFT) functions, Correlators, Reed-Solomon/Turbo/Convolution encoders and decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

### sysDSP Slice Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeECP3, on the other hand, has many DSP slices that support different data widths.

### Figure 2-31. MULTADDSUBSUM Slice 1

## Advanced sysDSP Slice Features

### Cascading

The LatticeECP3 sysDSP slice has been enhanced to allow cascading. Adder trees are implemented fully in sys-DSP slices, improving the performance. Cascading of slices uses the signals CIN, COUT and C Mux of the slice.

### Addition

The LatticeECP3 sysDSP slice allows for the bypassing of multipliers and cascading of adder logic. High performance adder functions are implemented without the use of LUTs. The maximum width adders that can be implemented are 54-bit.

### Rounding

The rounding operation is implemented in the ALU and is done by adding a constant followed by a truncation operation. The rounding methods supported are:

- Rounding to zero (RTZ)

- Rounding to infinity (RTI)

- Dynamic rounding

- Random rounding

- Convergent rounding

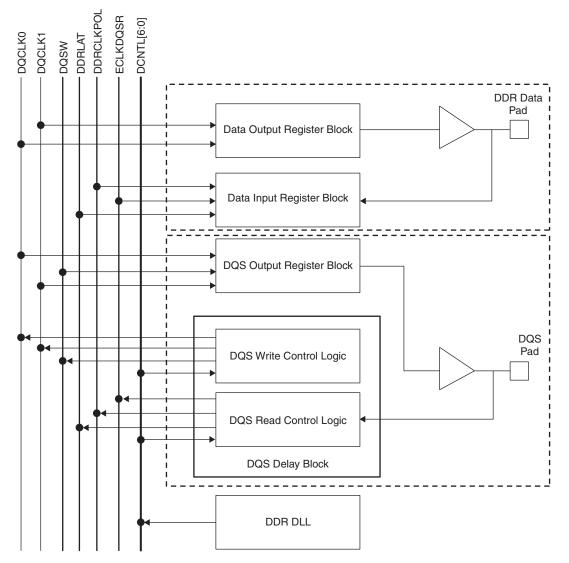

### Figure 2-37. DQS Local Bus

### **Polarity Control Logic**

In a typical DDR Memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the READ cycle) is unknown. The LatticeECP3 family contains dedicated circuits to transfer data between these domains. A clock polarity selector is used to prevent set-up and hold violations at the domain transfer between DQS (delayed) and the system clock. This changes the edge on which the data is registered in the synchronizing registers in the input register block. This requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects the first DQS rising edge after the preamble state. This signal is used to control the polarity of the clock to the synchronizing registers.

### DDR3 Memory Support

LatticeECP3 supports the read and write leveling required for DDR3 memory interfaces.

Read leveling is supported by the use of the DDRCLKPOL and the DDRLAT signals generated in the DQS Read Control logic block. These signals dynamically control the capture of the data with respect to the DQS at the input register block.

| Package    | ECP3-17    | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|------------|------------|---------|---------|---------|----------|

| 256 ftBGA  | 1          | 1       | —       | —       | —        |

| 328 csBGA  | 2 channels | —       | —       | —       | _        |

| 484 fpBGA  | 1          | 1       | 1       | 1       |          |

| 672 fpBGA  | —          | 1       | 2       | 2       | 2        |

| 1156 fpBGA | —          | —       | 3       | 3       | 4        |

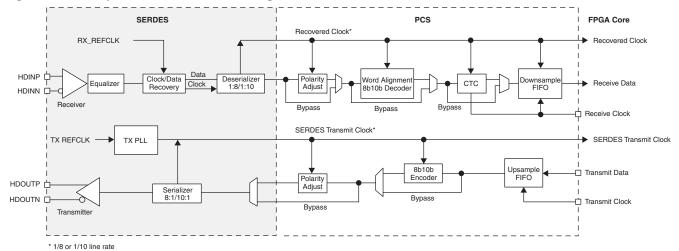

### SERDES Block

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2-41 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCOB and VCCIB).

Figure 2-41. Simplified Channel Block Diagram for SERDES/PCS Block

### PCS

As shown in Figure 2-41, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic.

| MCCLK (MHz)      | MCCLK (MHz)     |

|------------------|-----------------|

|                  | 10              |

| 2.5 <sup>1</sup> | 13              |

| 4.3              | 15 <sup>2</sup> |

| 5.4              | 20              |

| 6.9              | 26              |

| 8.1              | 33 <sup>3</sup> |

| 9.2              |                 |

Table 2-16. Selectable Master Clock (MCCLK) Frequencies During Configuration (Nominal)

1. Software default MCCLK frequency. Hardware default is 3.1 MHz.

2. Maximum MCCLK with encryption enabled.

3. Maximum MCCLK without encryption.

## **Density Shifting**

The LatticeECP3 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the LatticeECP3 Pin Migration Tables and Diamond software for specific restrictions and limitations.

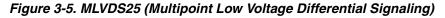

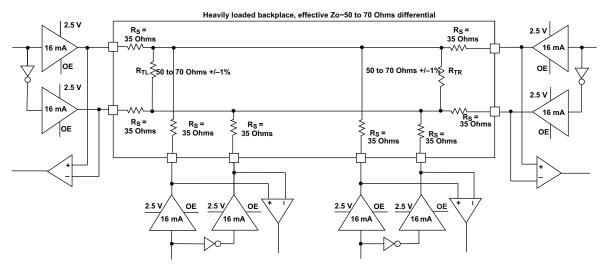

### MLVDS25

The LatticeECP3 devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-5 is one possible solution for MLVDS standard implementation. Resistor values in Figure 3-5 are industry standard values for 1% resistors.

Table 3-5. MLVDS25 DC Conditions<sup>1</sup>

|                   |                                  | Тур            | ical           |       |

|-------------------|----------------------------------|----------------|----------------|-------|

| Parameter         | Description                      | <b>Ζο=50</b> Ω | <b>Ζο=70</b> Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50           | 2.50           | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10.00          | 10.00          | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/–1%)   | 35.00          | 35.00          | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/-1%) | 50.00          | 70.00          | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/-1%)     | 50.00          | 70.00          | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.52           | 1.60           | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 0.98           | 0.90           | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.54           | 0.70           | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.25           | 1.25           | V     |

| I <sub>DC</sub>   | DC Output Current                | 21.74          | 20.00          | mA    |

1. For input buffer, see LVDS table.

# LatticeECP3 External Switching Characteristics <sup>1, 2, 3, 13</sup>

|                            |                                                                   |                     | -         | -8              | •    | -7         |      |            |       |

|----------------------------|-------------------------------------------------------------------|---------------------|-----------|-----------------|------|------------|------|------------|-------|

| Parameter                  | Description                                                       | Device              | Min.      | -8<br>Max.      | Min. | -7<br>Max. | Min. | -6<br>Max. | Units |

| Clocks                     | Description                                                       | Device              | Min.      | wax.            | win. | wax.       | MIN. | wax.       | Units |

| Primary Clock <sup>6</sup> |                                                                   |                     |           |                 |      |            |      |            |       |

|                            | Frequency for Primary Clock Tree                                  | ECP3-150EA          | _         | 500             |      | 420        | _    | 375        | MHz   |

| t <sub>MAX_PRI</sub>       | Clock Pulse Width for Primary                                     |                     |           | 000             |      | 420        |      | 0/0        |       |

| t <sub>W_PRI</sub>         | Clock                                                             | ECP3-150EA          | 0.8       | —               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-150EA          | -         | 300             | —    | 330        | —    | 360        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-150EA          | _         | 250             | —    | 280        | —    | 300        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-70EA/95EA      | -         | 500             | —    | 420        | -    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-70EA/95EA      | 0.8       | —               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-70EA/95EA      | _         | 360             | _    | 370        | _    | 380        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-70EA/95EA      | —         | 310             | —    | 320        | —    | 330        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-35EA           | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-35EA           | 0.8       | —               | 0.9  |            | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-35EA           | -         | 300             | —    | 330        | _    | 360        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-35EA           | _         | 250             | —    | 280        | —    | 300        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-17EA           | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-17EA           | 0.8       | _               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-17EA           | _         | 310             | —    | 340        | —    | 370        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-17EA           | _         | 220             | —    | 230        | —    | 240        | ps    |

| Edge Clock <sup>6</sup>    | •                                                                 |                     | •         |                 |      | •          | •    | •          |       |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-150EA          | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-150EA          | 0.9       | —               | 1.0  | —          | 1.2  | —          | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device                      | ECP3-150EA          | -         | 200             | —    | 210        | _    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-70EA/95EA      | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-70EA/95EA      | 0.9       | _               | 1.0  | —          | 1.2  | —          | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device                      | ECP3-70EA/95EA      | _         | 200             | _    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-35EA           | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-35EA           | 0. 9      | —               | 1.0  | —          | 1.2  | —          | ns    |

| <sup>t</sup> skew_edge_dqs | Edge Clock Skew Within an Edge of the Device                      | ECP3-35EA           | _         | 200             | —    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-17EA           | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-17EA           | 0. 9      | —               | 1.0  | —          | 1.2  | —          | ns    |

| tskew_edge_dqs             | Edge Clock Skew Within an Edge of the Device                      | ECP3-17EA           | _         | 200             | _    | 210        | —    | 220        | ps    |

| Generic SDR                | •                                                                 |                     | •         | •               |      | •          | •    | •          | ·     |

| General I/O Pin Pa         | arameters Using Dedicated Clock In                                | put Primary Clock V | Vithout P | LL <sup>2</sup> |      |            |      |            |       |

| t <sub>CO</sub>            | Clock to Output - PIO Output<br>Register                          | ECP3-150EA          | _         | 3.9             | —    | 4.3        | —    | 4.7        | ns    |

| t <sub>SU</sub>            | Clock to Data Setup - PIO Input<br>Register                       | ECP3-150EA          | 0.0       | _               | 0.0  |            | 0.0  | _          | ns    |

| t <sub>H</sub>             | Clock to Data Hold - PIO Input<br>Register                        | ECP3-150EA          | 1.5       | _               | 1.7  |            | 2.0  |            | ns    |

| t <sub>SU_DEL</sub>        | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-150EA          | 1.3       | —               | 1.5  | _          | 1.7  |            | ns    |

### **Over Recommended Commercial Operating Conditions**

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                         |                                |                           | -8 -7    |          |          | - 1        | -6            | r –   |       |

|-------------------------|--------------------------------|---------------------------|----------|----------|----------|------------|---------------|-------|-------|

| Parameter               | Description                    | Device                    | Min.     | Max.     | Min.     | Max.       | Min.          | Max.  | Units |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | All ECP3EA Devices        | 0.775    | _        | 0.775    | _          | 0.775         | _     | UI    |

| f <sub>MAX</sub> GDDR   | DDRX1 Clock Frequency          | All ECP3EA Devices        | _        | 250      | _        | 250        | _             | 250   | MHz   |

|                         | nputs with Clock and Data (>10 |                           | in (GDDF |          | ECLK Ce  |            | l<br>Isina PC |       |       |

| Input                   |                                |                           | in (abbi |          |          | intered) e | Joing TO      |       |       |

| Left and Right Si       | des                            |                           |          |          |          |            |               |       |       |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-150EA                | 321      | —        | 403      | —          | 471           |       | ps    |

| t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-150EA                | 321      | _        | 403      | —          | 471           | —     | ps    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-150EA                | _        | 405      | _        | 325        | —             | 280   | MHz   |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-70EA/95EA            | 321      | _        | 403      | —          | 535           |       | ps    |

| t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-70EA/95EA            | 321      | _        | 403      | —          | 535           | _     | ps    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-70EA/95EA            |          | 405      | —        | 325        | —             | 250   | MHz   |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-35EA                 | 335      | _        | 425      |            | 535           |       | ps    |

| t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-35EA                 | 335      | —        | 425      | —          | 535           | —     | ps    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-35EA                 | _        | 405      | —        | 325        | —             | 250   | MHz   |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-17EA                 | 335      | _        | 425      | —          | 535           | —     | ps    |

| t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-17EA                 | 335      |          | 425      |            | 535           |       | ps    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-17EA                 |          | 405      |          | 325        | —             | 250   | MHz   |

| Generic DDRX2 I         | nputs with Clock and Data (>10 | Bits Wide) Aligned at Pin | (GDDR)   | (2_RX.EC | CLK.Alig | ned)       |               |       |       |

| Left and Right Si       | de Using DLLCLKIN Pin for Clo  | ck Input                  |          |          |          |            |               |       |       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-150EA                |          | 0.225    |          | 0.225      | _             | 0.225 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-150EA                | 0.775    | —        | 0.775    | —          | 0.775         | _     | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-150EA                | _        | 460      |          | 385        | —             | 345   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-70EA/95EA            | _        | 0.225    | —        | 0.225      | —             | 0.225 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-70EA/95EA            | 0.775    | —        | 0.775    | —          | 0.775         | —     | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-70EA/95EA            |          | 460      |          | 385        | —             | 311   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-35EA                 | _        | 0.210    | _        | 0.210      | _             | 0.210 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-35EA                 | 0.790    | —        | 0.790    | —          | 0.790         | —     | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-35EA                 | —        | 460      | —        | 385        | —             | 311   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-17EA                 | _        | 0.210    | —        | 0.210      | —             | 0.210 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-17EA                 | 0.790    | _        | 0.790    |            | 0.790         |       | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-17EA                 | —        | 460      | —        | 385        | —             | 311   | MHz   |

| Top Side Using P        | CLK Pin for Clock Input        |                           |          |          |          |            |               |       |       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-150EA                |          | 0.225    |          | 0.225      | —             | 0.225 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-150EA                | 0.775    |          | 0.775    |            | 0.775         |       | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-150EA                |          | 235      |          | 170        | —             | 130   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-70EA/95EA            |          | 0.225    |          | 0.225      | —             | 0.225 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-70EA/95EA            | 0.775    |          | 0.775    |            | 0.775         |       | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-70EA/95EA            |          | 235      | —        | 170        | —             | 130   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-35EA                 | —        | 0.210    |          | 0.210      | —             | 0.210 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-35EA                 | 0.790    |          | 0.790    |            | 0.790         |       | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-35EA                 |          | 235      | —        | 170        | —             | 130   | MHz   |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK          | ECP3-17EA                 |          | 0.210    |          | 0.210      | —             | 0.210 | UI    |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | ECP3-17EA                 | 0.790    | —        | 0.790    | —          | 0.790         | —     | UI    |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency          | ECP3-17EA                 | _        | 235      | _        | 170        | _             | 130   | MHz   |

### **Over Recommended Commercial Operating Conditions**

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5, 7</sup> (Continued)

| Buffer Type   | Description                            | -8    | -7    | -6    | Units |

|---------------|----------------------------------------|-------|-------|-------|-------|

| LVCMOS15_4mA  | LVCMOS 1.5 4 mA drive, fast slew rate  | 0.21  | 0.25  | 0.29  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8 mA drive, fast slew rate  | 0.05  | 0.07  | 0.09  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2 mA drive, fast slew rate  | 0.43  | 0.51  | 0.59  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6 mA drive, fast slew rate  | 0.23  | 0.28  | 0.33  | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4 mA drive, slow slew rate  | 1.44  | 1.58  | 1.72  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8 mA drive, slow slew rate  | 0.98  | 1.10  | 1.22  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12 mA drive, slow slew rate | 0.67  | 0.77  | 0.86  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16 mA drive, slow slew rate | 0.97  | 1.09  | 1.21  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20 mA drive, slow slew rate | 0.67  | 0.76  | 0.85  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4 mA drive, slow slew rate  | 1.48  | 1.63  | 1.78  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8 mA drive, slow slew rate  | 1.02  | 1.14  | 1.27  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12 mA drive, slow slew rate | 0.74  | 0.84  | 0.94  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16 mA drive, slow slew rate | 1.02  | 1.14  | 1.26  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20 mA drive, slow slew rate | 0.74  | 0.83  | 0.93  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4 mA drive, slow slew rate  | 1.60  | 1.77  | 1.93  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8 mA drive, slow slew rate  | 1.11  | 1.25  | 1.38  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12 mA drive, slow slew rate | 0.87  | 0.98  | 1.09  | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16 mA drive, slow slew rate | 0.86  | 0.97  | 1.07  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4 mA drive, slow slew rate  | 1.71  | 1.89  | 2.08  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8 mA drive, slow slew rate  | 1.20  | 1.34  | 1.48  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2 mA drive, slow slew rate  | 1.37  | 1.56  | 1.74  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6 mA drive, slow slew rate  | 1.11  | 1.27  | 1.43  | ns    |

| PCI33         | PCI, VCCIO = 3.3 V                     | -0.12 | -0.13 | -0.14 | ns    |

1. Timing adders are characterized but not tested on every device.

2. LVCMOS timing measured with the load specified in Switching Test Condition table.

3. All other standards tested according to the appropriate specifications.

4. Not all I/O standards and drive strengths are supported for all banks. See the Architecture section of this data sheet for details.

5. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

6. This data does not apply to the LatticeECP3-17EA device.

7. For details on -9 speed grade devices, please contact your Lattice Sales Representative.

# LatticeECP3 Maximum I/O Buffer Speed (Continued)<sup>1, 2, 3, 4, 5, 6</sup>

#### **Over Recommended Operating Conditions**

| Buffer | Description                    | Max. | Units |

|--------|--------------------------------|------|-------|

| PCI33  | PCI, V <sub>CCIO</sub> = 3.3 V | 66   | MHz   |

1. These maximum speeds are characterized but not tested on every device.

2. Maximum I/O speed for differential output standards emulated with resistors depends on the layout.

3. LVCMOS timing is measured with the load specified in the Switching Test Conditions table of this document.

4. All speeds are measured at fast slew.

5. Actual system operation may vary depending on user logic implementation.

6. Maximum data rate equals 2 times the clock rate when utilizing DDR.

# SERDES High-Speed Data Transmitter<sup>1</sup>

### Table 3-6. Serial Output Timing and Levels

| Symbol                                 | Description                                                  | Frequency          | Min.                       | Тур.                       | Max.                       | Units   |

|----------------------------------------|--------------------------------------------------------------|--------------------|----------------------------|----------------------------|----------------------------|---------|

| V <sub>TX-DIFF-P-P-1.44</sub>          | Differential swing (1.44 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1150                       | 1440                       | 1730                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.35</sub>          | Differential swing (1.35 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1080                       | 1350                       | 1620                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.26</sub>          | Differential swing (1.26 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1000                       | 1260                       | 1510                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.13</sub>          | Differential swing (1.13 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 840                        | 1130                       | 1420                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.04</sub>          | Differential swing (1.04 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 780                        | 1040                       | 1300                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.92</sub>          | Differential swing (0.92 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 690                        | 920                        | 1150                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.87</sub>          | Differential swing (0.87 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 650                        | 870                        | 1090                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.78</sub>          | Differential swing (0.78 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 585                        | 780                        | 975                        | mV, p-p |

| V <sub>TX-DIFF-P-P-0.64</sub>          | Differential swing (0.64 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 480                        | 640                        | 800                        | mV, p-p |

| V <sub>OCM</sub>                       | Output common mode voltage                                   | _                  | V <sub>CCOB</sub><br>-0.75 | V <sub>CCOB</sub><br>-0.60 | V <sub>CCOB</sub><br>-0.45 | V       |

| T <sub>TX-R</sub>                      | Rise time (20% to 80%)                                       | —                  | 145                        | 185                        | 265                        | ps      |

| T <sub>TX-F</sub>                      | Fall time (80% to 20%)                                       | —                  | 145                        | 185                        | 265                        | ps      |

| Z <sub>TX-OI-SE</sub>                  | Output Impedance 50/75/HiZ Ohms<br>(single ended)            | _                  | -20%                       | 50/75/<br>Hi Z             | +20%                       | Ohms    |

| R <sub>LTX-RL</sub>                    | Return loss (with package)                                   | —                  | 10                         |                            |                            | dB      |

| T <sub>TX-INTRASKEW</sub>              | Lane-to-lane TX skew within a SERDES quad block (intra-quad) | —                  | _                          | _                          | 200                        | ps      |

| T <sub>TX-INTERSKEW</sub> <sup>3</sup> | Lane-to-lane skew between SERDES quad blocks (inter-quad)    | —                  | _                          | _                          | 1UI +200                   | ps      |

1. All measurements are with 50 Ohm impedance.

2. See TN1176, LatticeECP3 SERDES/PCS Usage Guide for actual binary settings and the min-max range.

3. Inter-quad skew is between all SERDES channels on the device and requires the use of a low skew internal reference clock.

# HDMI (High-Definition Multimedia Interface) Electrical and Timing Characteristics

### AC and DC Characteristics

### Table 3-22. Transmit and Receive<sup>1, 2</sup>

|                                |                                                    | Spec. Co   | mpliance   |       |  |

|--------------------------------|----------------------------------------------------|------------|------------|-------|--|

| Symbol                         | Description                                        | Min. Spec. | Max. Spec. | Units |  |

| Transmit                       |                                                    | •          |            |       |  |

| Intra-pair Skew                |                                                    | —          | 75         | ps    |  |

| Inter-pair Skew                |                                                    | —          | 800        | ps    |  |

| TMDS Differential Clock Jitter |                                                    | —          | 0.25       | UI    |  |

| Receive                        |                                                    | •          | •          |       |  |

| R <sub>T</sub>                 | Termination Resistance                             | 40         | 60         | Ohms  |  |

| V <sub>ICM</sub>               | Input AC Common Mode Voltage (50-Ohm Set-<br>ting) | —          | 50         | mV    |  |

| TMDS Clock Jitter              | Clock Jitter Tolerance                             | —          | 0.25       | UI    |  |

1. Output buffers must drive a translation device. Max. speed is 2 Gbps. If translation device does not modify rise/fall time, the maximum speed is 1.5 Gbps.

2. Input buffers must be AC coupled in order to support the 3.3 V common mode. Generally, HDMI inputs are terminated by an external cable equalizer before data/clock is forwarded to the LatticeECP3 device.

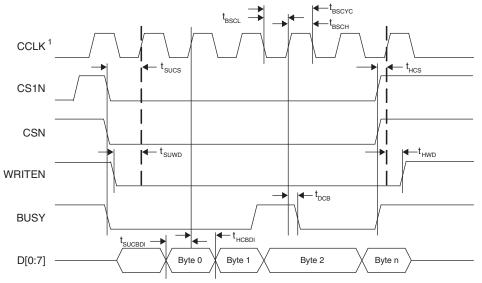

### Figure 3-21. sysCONFIG Parallel Port Write Cycle

1. In Master Parallel Mode the FPGA provides CCLK (MCLK). In Slave Parallel Mode the external device provides CCLK.

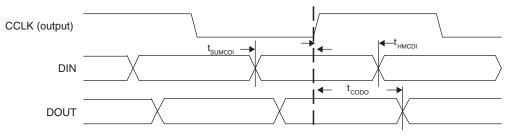

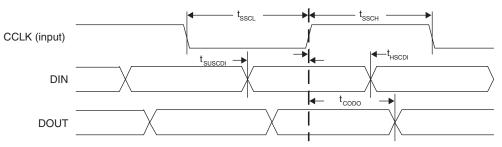

### Figure 3-22. sysCONFIG Master Serial Port Timing

### Point-to-Point LVDS (PPLVDS)

### Over Recommended Operating Conditions

| Description                   | Min. | Тур. | Max. | Units |

|-------------------------------|------|------|------|-------|

| Output driver supply (+/- 5%) | 3.14 | 3.3  | 3.47 | V     |

|                               | 2.25 | 2.5  | 2.75 | V     |

| Input differential voltage    | 100  | —    | 400  | mV    |

| Input common mode voltage     | 0.2  | —    | 2.3  | V     |

| Output differential voltage   | 130  | —    | 400  | mV    |

| Output common mode voltage    | 0.5  | 0.8  | 1.4  | V     |

### RSDS

### **Over Recommended Operating Conditions**

| Parameter Symbol                | Description                                             | Min. | Тур. | Max. | Units |

|---------------------------------|---------------------------------------------------------|------|------|------|-------|

| V <sub>OD</sub>                 | Output voltage, differential, R <sub>T</sub> = 100 Ohms | 100  | 200  | 600  | mV    |

| V <sub>OS</sub>                 | Output voltage, common mode                             | 0.5  | 1.2  | 1.5  | V     |

| I <sub>RSDS</sub>               | Differential driver output current                      | 1    | 2    | 6    | mA    |

| V <sub>THD</sub>                | Input voltage differential                              | 100  | —    | —    | mV    |

| V <sub>CM</sub>                 | Input common mode voltage                               | 0.3  | —    | 1.5  | V     |

| T <sub>R</sub> , T <sub>F</sub> | Output rise and fall times, 20% to 80%                  | —    | 500  | —    | ps    |

| T <sub>ODUTY</sub>              | Output clock duty cycle                                 | 35   | 50   | 65   | %     |

Note: Data is for 2 mA drive. Other differential driver current options are available.

# Signal Descriptions (Cont.)

| Signal Name                     | I/O      | Description                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [LOC]DQS[num]                   | I/O      | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQS, num = ball function number.                                                                                                                                                                                                                                                                         |

| [LOC]DQ[num]                    | I/O      | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQ, associated DQS number.                                                                                                                                                                                                                                                                               |

| Test and Programming (Dedicated | Pins)    |                                                                                                                                                                                                                                                                                                                                                                          |

| TMS                             | I        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                                                                                                                               |

| тск                             | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                                                                                                                        |

| TDI                             | I        | Test Data in pin. Used to load data into device using 1149.1 state machine.<br>After power-up, this TAP port can be activated for configuration by sending<br>appropriate command. (Note: once a configuration port is selected it is<br>locked. Another configuration port cannot be selected until the power-up<br>sequence). Pull-up is enabled during configuration. |

| TDO                             | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.                                                                                                                                                                                                                                                                                           |

| VCCJ                            | _        | Power supply pin for JTAG Test Access Port.                                                                                                                                                                                                                                                                                                                              |

| Configuration Pads (Used During | sysCONFI | Ġ)                                                                                                                                                                                                                                                                                                                                                                       |

| CFG[2:0]                        | I        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled. These are dedicated pins.                                                                                                                                                                                                               |

| INITN                           | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled. It is a dedicated pin.                                                                                                                                                                                                                                         |

| PROGRAMN                        | I        | Initiates configuration sequence when asserted low. This pin always has an active pull-up. It is a dedicated pin.                                                                                                                                                                                                                                                        |

| DONE                            | I/O      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress. It is a dedicated pin.                                                                                                                                                                                                                                   |

| CCLK                            | I        | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. It is a dedicated pin.                                                                                                                                                                                                                                                            |

| MCLK                            | I/O      | Output Configuration Clock for configuring an FPGA in SPI, SPIm, and Master configuration modes.                                                                                                                                                                                                                                                                         |

| BUSY/SISPI                      | 0        | Parallel configuration mode busy indicator. SPI/SPIm mode data output.                                                                                                                                                                                                                                                                                                   |

| CSN/SN/OEN                      | I/O      | Parallel configuration mode active-low chip select. Slave SPI chip select.<br>Parallel burst Flash output enable.                                                                                                                                                                                                                                                        |

| CS1N/HOLDN/RDY                  | I        | Parallel configuration mode active-low chip select. Slave SPI hold input.                                                                                                                                                                                                                                                                                                |

| WRITEN                          | I        | Write enable for parallel configuration modes.                                                                                                                                                                                                                                                                                                                           |

| DOUT/CSON/CSSPI1N               | 0        | Serial data output. Chip select output. SPI/SPIm mode chip select.                                                                                                                                                                                                                                                                                                       |

|                                 |          | sysCONFIG Port Data I/O for Parallel mode. Open drain during configuration.                                                                                                                                                                                                                                                                                              |

| D[0]/SPIFASTN                   | I/O      | sysCONFIG Port Data I/O for SPI or SPIm. When using the SPI or SPIm mode, this pin should either be tied high or low, must not be left floating. Open drain during configuration.                                                                                                                                                                                        |

| D1                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D2                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D3/SI                           | I/O      | Parallel configuration I/O. Slave SPI data input. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                  |

| D4/SO                           | I/O      | Parallel configuration I/O. Slave SPI data output. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                 |

| D5                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D6/SPID1                        | I/O      | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                   |

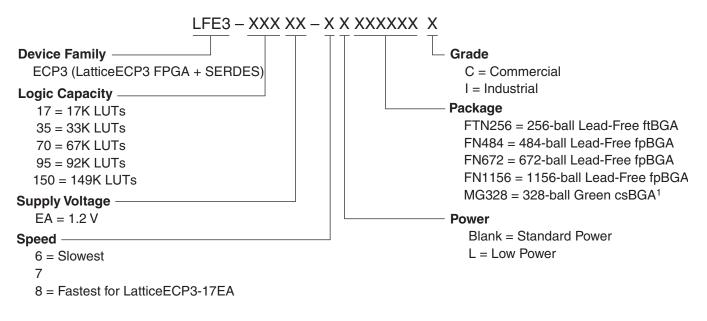

# LatticeECP3 Family Data Sheet Ordering Information

April 2014

Data Sheet DS1021

## LatticeECP3 Part Number Description

1. Green = Halogen free and lead free.

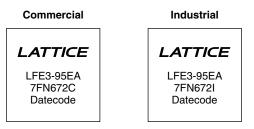

# **Ordering Information**

LatticeECP3 devices have top-side markings, for commercial and industrial grades, as shown below:

Note: See PCN 05A-12 for information regarding a change to the top-side mark logo.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### LatticeECP3 Devices, Green and Lead-Free Packaging

The following devices may have associated errata. Specific devices with associated errata will be notated with a footnote.

| Part Number         | Voltage | Grade | Power | Package <sup>1</sup> | Pins | Temp. | LUTs (K) |

|---------------------|---------|-------|-------|----------------------|------|-------|----------|

| LFE3-17EA-6FTN256C  | 1.2 V   | -6    | STD   | Lead-Free ftBGA      | 256  | СОМ   | 17       |

| LFE3-17EA-7FTN256C  | 1.2 V   | -7    | STD   | Lead-Free ftBGA      | 256  | СОМ   | 17       |

| LFE3-17EA-8FTN256C  | 1.2 V   | -8    | STD   | Lead-Free ftBGA      | 256  | COM   | 17       |

| LFE3-17EA-6LFTN256C | 1.2 V   | -6    | LOW   | Lead-Free ftBGA      | 256  | COM   | 17       |

| LFE3-17EA-7LFTN256C | 1.2 V   | -7    | LOW   | Lead-Free ftBGA      | 256  | COM   | 17       |

| LFE3-17EA-8LFTN256C | 1.2 V   | -8    | LOW   | Lead-Free ftBGA      | 256  | COM   | 17       |

| LFE3-17EA-6MG328C   | 1.2 V   | -6    | STD   | Green csBGA          | 328  | COM   | 17       |

| LFE3-17EA-7MG328C   | 1.2 V   | -7    | STD   | Green csBGA          | 328  | COM   | 17       |

| LFE3-17EA-8MG328C   | 1.2 V   | -8    | STD   | Green csBGA          | 328  | COM   | 17       |

| LFE3-17EA-6LMG328C  | 1.2 V   | -6    | LOW   | Green csBGA          | 328  | COM   | 17       |

| LFE3-17EA-7LMG328C  | 1.2 V   | -7    | LOW   | Green csBGA          | 328  | COM   | 17       |

| LFE3-17EA-8LMG328C  | 1.2 V   | -8    | LOW   | Green csBGA          | 328  | COM   | 17       |

| LFE3-17EA-6FN484C   | 1.2 V   | -6    | STD   | Lead-Free fpBGA      | 484  | COM   | 17       |

| LFE3-17EA-7FN484C   | 1.2 V   | -7    | STD   | Lead-Free fpBGA      | 484  | COM   | 17       |

| LFE3-17EA-8FN484C   | 1.2 V   | -8    | STD   | Lead-Free fpBGA      | 484  | COM   | 17       |

| LFE3-17EA-6LFN484C  | 1.2 V   | -6    | LOW   | Lead-Free fpBGA      | 484  | COM   | 17       |

| LFE3-17EA-7LFN484C  | 1.2 V   | -7    | LOW   | Lead-Free fpBGA      | 484  | COM   | 17       |

| LFE3-17EA-8LFN484C  | 1.2 V   | -8    | LOW   | Lead-Free fpBGA      | 484  | COM   | 17       |

Commercial

1. Green = Halogen free and lead free.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-35EA-6FTN256C  | 1.2 V   | -6                 | STD   | Lead-Free ftBGA | 256  | COM   | 33       |

| LFE3-35EA-7FTN256C  | 1.2 V   | -7                 | STD   | Lead-Free ftBGA | 256  | COM   | 33       |

| LFE3-35EA-8FTN256C  | 1.2 V   | -8                 | STD   | Lead-Free ftBGA | 256  | COM   | 33       |

| LFE3-35EA-6LFTN256C | 1.2 V   | -6                 | LOW   | Lead-Free ftBGA | 256  | COM   | 33       |

| LFE3-35EA-7LFTN256C | 1.2 V   | -7                 | LOW   | Lead-Free ftBGA | 256  | COM   | 33       |

| LFE3-35EA-8LFTN256C | 1.2 V   | -8                 | LOW   | Lead-Free ftBGA | 256  | COM   | 33       |

| LFE3-35EA-6FN484C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | COM   | 33       |

| LFE3-35EA-7FN484C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | COM   | 33       |

| LFE3-35EA-8FN484C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | COM   | 33       |

| LFE3-35EA-6LFN484C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | COM   | 33       |

| LFE3-35EA-7LFN484C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | COM   | 33       |

| LFE3-35EA-8LFN484C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | COM   | 33       |

| LFE3-35EA-6FN672C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | COM   | 33       |

| LFE3-35EA-7FN672C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | COM   | 33       |

| LFE3-35EA-8FN672C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | COM   | 33       |

| LFE3-35EA-6LFN672C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | COM   | 33       |

| LFE3-35EA-7LFN672C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | COM   | 33       |

| LFE3-35EA-8LFN672C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | COM   | 33       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Date                | Version                             | Section                                                                                                                                                                 | Change Summary                                                                                                                                                              |  |

|---------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| September 2009 01.4 | Architecture                        | Corrected link in sysMEM Memory Block section.                                                                                                                          |                                                                                                                                                                             |  |

|                     |                                     |                                                                                                                                                                         | Updated information for On-Chip Programmable Termination and modi-<br>fied corresponding figure.                                                                            |  |

|                     |                                     |                                                                                                                                                                         | Added footnote 2 to On-Chip Programmable Termination Options for Input Modes table.                                                                                         |  |

|                     |                                     |                                                                                                                                                                         | Corrected Per Quadrant Primary Clock Selection figure.                                                                                                                      |  |

|                     |                                     | DC and Switching<br>Characteristics                                                                                                                                     | Modified -8 Timing data for 1024x18 True-Dual Port RAM (Read-Before-<br>Write, EBR Output Registers)                                                                        |  |

|                     |                                     |                                                                                                                                                                         | Added ESD Performance table.                                                                                                                                                |  |

|                     |                                     |                                                                                                                                                                         | LatticeECP3 External Switching Characteristics table - updated data for<br>t <sub>DIBGDDR</sub> , t <sub>W_PRI</sub> , t <sub>W_EDGE</sub> and t <sub>SKEW_EDGE_DQS</sub> . |  |

|                     |                                     |                                                                                                                                                                         | LatticeECP3 Internal Switching Characteristics table - updated data for $t_{COO\ PIO}$ and added footnote #4.                                                               |  |

|                     |                                     |                                                                                                                                                                         | sysCLOCK PLL Timing table - updated data for f <sub>OUT</sub> .                                                                                                             |  |

|                     |                                     |                                                                                                                                                                         | External Reference Clock Specification (refclkp/refclkn) table - updated data for $V_{REF\text{-}IN\text{-}SE}$ and $V_{REF\text{-}IN\text{-}DIFF}$                         |  |

|                     |                                     |                                                                                                                                                                         | LatticeECP3 sysCONFIG Port Timing Specifications table - updated data for t <sub>MWC</sub> .                                                                                |  |

|                     |                                     |                                                                                                                                                                         | Added TRLVDS DC Specification table and diagram.                                                                                                                            |  |

|                     |                                     |                                                                                                                                                                         | Updated Mini LVDS table.                                                                                                                                                    |  |

| August 2009         | 01.3                                | DC and Switching<br>Characteristics                                                                                                                                     | Corrected truncated numbers for $V_{CCIB}$ and $V_{CCOB}$ in Recommended Operating Conditions table.                                                                        |  |

| July 2009 01.2      | Multiple                            | Changed references of "multi-boot" to "dual-boot" throughout the data sheet.                                                                                            |                                                                                                                                                                             |  |

|                     |                                     | Architecture                                                                                                                                                            | Updated On-Chip Programmable Termination bullets.                                                                                                                           |  |

|                     |                                     |                                                                                                                                                                         | Updated On-Chip Termination Options for Input Modes table.                                                                                                                  |  |

|                     |                                     |                                                                                                                                                                         | Updated On-Chip Termination figure.                                                                                                                                         |  |

|                     | DC and Switching<br>Characteristics | Changed min/max data for FREF_PPM and added footnote 4 in SERDES External Reference Clock Specification table.                                                          |                                                                                                                                                                             |  |

|                     |                                     |                                                                                                                                                                         | Updated SERDES minimum frequency.                                                                                                                                           |  |

|                     |                                     | Pinout Information                                                                                                                                                      | Corrected MCLK to be I/O and CCLK to be I in Signal Descriptions table                                                                                                      |  |

| May 2009            | 01.1                                | All                                                                                                                                                                     | Removed references to Parallel burst mode Flash.                                                                                                                            |  |

|                     | Introduction                        | Features - Changed 250 Mbps to 230 Mbps in Embedded SERDES bul-<br>leted section and added a footnote to indicate 230 Mbps applies to<br>8b10b and 10b12b applications. |                                                                                                                                                                             |  |

|                     |                                     |                                                                                                                                                                         | Updated data for ECP3-17 in LatticeECP3 Family Selection Guide table.                                                                                                       |  |

|                     |                                     |                                                                                                                                                                         | Changed embedded memory from 552 to 700 Kbits in LatticeECP3<br>Family Selection Guide table.                                                                               |  |

|                     | •                                   | Architecture                                                                                                                                                            | Updated description for CLKFB in General Purpose PLL Diagram.                                                                                                               |  |

|                     |                                     |                                                                                                                                                                         | Corrected Primary Clock Sources text section.                                                                                                                               |  |

|                     |                                     | Corrected Secondary Clock/Control Sources text section.                                                                                                                 |                                                                                                                                                                             |  |

|                     |                                     | Corrected Secondary Clock Regions table.                                                                                                                                |                                                                                                                                                                             |  |

|                     |                                     | Corrected note below Detailed sysDSP Slice Diagram.                                                                                                                     |                                                                                                                                                                             |  |

|                     |                                     |                                                                                                                                                                         | Corrected Clock, Clock Enable, and Reset Resources text section.                                                                                                            |  |

|                     |                                     | Corrected ECP3-17 EBR number in Embedded SRAM in the LatticeECP3 Family table.                                                                                          |                                                                                                                                                                             |  |

|                     |                                     |                                                                                                                                                                         | Added On-Chip Termination Options for Input Modes table.                                                                                                                    |  |

|                     |                                     |                                                                                                                                                                         | Updated Available SERDES Quads per LatticeECP3 Devices table.                                                                                                               |  |