# E.J. Lattice Semiconductor Corporation - LFE3-35EA-9FN484C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Not For New Designs                                                          |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 4125                                                                         |

| Number of Logic Elements/Cells | 33000                                                                        |

| Total RAM Bits                 | 1358848                                                                      |

| Number of I/O                  | 295                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 484-BBGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-35ea-9fn484c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeECP3 Family Data Sheet Introduction

#### February 2012

## **Features**

- Higher Logic Density for Increased System Integration

- 17K to 149K LUTs

- 116 to 586 I/Os

- Embedded SERDES

- 150 Mbps to 3.2 Gbps for Generic 8b10b, 10-bit SERDES, and 8-bit SERDES modes

- Data Rates 230 Mbps to 3.2 Gbps per channel for all other protocols

- Up to 16 channels per device: PCI Express, SONET/SDH, Ethernet (1GbE, SGMII, XAUI), CPRI, SMPTE 3G and Serial RapidIO

### ■ sysDSP<sup>™</sup>

- Fully cascadable slice architecture

- 12 to 160 slices for high performance multiply and accumulate

- Powerful 54-bit ALU operations

- Time Division Multiplexing MAC Sharing

- Rounding and truncation

- Each slice supports

- -Half 36x36, two 18x18 or four 9x9 multipliers

- Advanced 18x36 MAC and 18x18 Multiply-

- Multiply-Accumulate (MMAC) operations

### ■ Flexible Memory Resources

- Up to 6.85Mbits sysMEM<sup>™</sup> Embedded Block RAM (EBR)

- 36K to 303K bits distributed RAM

- sysCLOCK Analog PLLs and DLLs

Two DLLs and up to ten PLLs per device

- Pre-Engineered Source Synchronous I/O

- DDR registers in I/O cells

#### Table 1-1. LatticeECP3™ Family Selection Guide

• Dedicated read/write levelling functionality

Data Sheet DS1021

- Dedicated gearing logic

- Source synchronous standards support

ADC/DAC, 7:1 LVDS, XGMII

Link Speed ADC/DAC devices

- -High Speed ADC/DAC devices

- Dedicated DDR/DDR2/DDR3 memory with DQS support

- Optional Inter-Symbol Interference (ISI) correction on outputs

- Programmable sysl/O<sup>TM</sup> Buffer Supports Wide Range of Interfaces

- On-chip termination

- Optional equalization filter on inputs

- LVTTL and LVCMOS 33/25/18/15/12

- SSTL 33/25/18/15 I, II

- HSTL15 I and HSTL18 I, II

- PCI and Differential HSTL, SSTL

- LVDS, Bus-LVDS, LVPECL, RSDS, MLVDS

- Flexible Device Configuration

- Dedicated bank for configuration I/Os

- SPI boot flash interface

- Dual-boot images supported

- Slave SPI

- TransFR™ I/O for simple field updates

- Soft Error Detect embedded macro

#### System Level Support

- IEEE 1149.1 and IEEE 1532 compliant

- Reveal Logic Analyzer

- ORCAstra FPGA configuration utility

- · On-chip oscillator for initialization & general use

- 1.2 V core power supply

| ECP3-17            | ECP3-35                                                                               | ECP3-70                                                                                                                                                                                                         | ECP3-95                                               | ECP3-150                                              |  |

|--------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|--|

| 17                 | 33                                                                                    | 67                                                                                                                                                                                                              | 92                                                    | 149                                                   |  |

| 38                 | 72                                                                                    | 240                                                                                                                                                                                                             | 240                                                   | 372                                                   |  |

| 700                | 1327                                                                                  | 4420                                                                                                                                                                                                            | 4420                                                  | 6850                                                  |  |

| 36                 | 68                                                                                    | 145                                                                                                                                                                                                             | 188                                                   | 303                                                   |  |

| 24                 | 64                                                                                    | 128                                                                                                                                                                                                             | 128                                                   | 320                                                   |  |

| 1                  | 1                                                                                     | 3                                                                                                                                                                                                               | 3                                                     | 4                                                     |  |

| 2/2                | 4/2                                                                                   | 10/2                                                                                                                                                                                                            | 10 / 2                                                | 10/2                                                  |  |

| ls/ I/O Combinatio | ns                                                                                    | •                                                                                                                                                                                                               |                                                       | •                                                     |  |

| 2/116              |                                                                                       |                                                                                                                                                                                                                 |                                                       |                                                       |  |

| 4 / 133            | 4 / 133                                                                               |                                                                                                                                                                                                                 |                                                       |                                                       |  |

| 4 / 222            | 4 / 295                                                                               | 4 / 295                                                                                                                                                                                                         | 4 / 295                                               |                                                       |  |

|                    | 4 / 310                                                                               | 8 / 380                                                                                                                                                                                                         | 8 / 380                                               | 8 / 380                                               |  |

|                    |                                                                                       | 12 / 490                                                                                                                                                                                                        | 12 / 490                                              | 16 / 586                                              |  |

|                    | 17<br>38<br>700<br>36<br>24<br>1<br>2 / 2<br>Is/ I/O Combinatio<br>2 / 116<br>4 / 133 | 17      33        38      72        700      1327        36      68        24      64        1      1        2/2      4/2        Is/I/O Combinations      2/116        4/133      4/133        4/222      4/295 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Introduction

The LatticeECP3<sup>™</sup> (EConomy Plus Third generation) family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES and high speed source synchronous interfaces in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 65 nm technology making the devices suitable for high-volume, high-speed, low-cost applications.

The LatticeECP3 device family expands look-up-table (LUT) capacity to 149K logic elements and supports up to 586 user I/Os. The LatticeECP3 device family also offers up to 320 18 x 18 multipliers and a wide range of parallel I/O standards.

The LatticeECP3 FPGA fabric is optimized with high performance and low cost in mind. The LatticeECP3 devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), Delay Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the LatticeECP3 device family supports a broad range of interface standards, including DDR3, XGMII and 7:1 LVDS.

The LatticeECP3 device family also features high speed SERDES with dedicated PCS functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, SMPTE, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit Pre-emphasis and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The LatticeECP3 devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

The Lattice Diamond<sup>™</sup> and ispLEVER<sup>®</sup> design software allows large complex designs to be efficiently implemented using the LatticeECP3 FPGA family. Synthesis library support for LatticeECP3 is available for popular logic synthesis tools. Diamond and ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP3 device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the LatticeECP3 family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

# LatticeECP3 Family Data Sheet Architecture

June 2013

Data Sheet DS1021

# **Architecture Overview**

Each LatticeECP3 device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM<sup>™</sup> Embedded Block RAM (EBR) and rows of sys-DSP<sup>™</sup> Digital Signal Processing slices, as shown in Figure 2-1. The LatticeECP3-150 has four rows of DSP slices; all other LatticeECP3 devices have two rows of DSP slices. In addition, the LatticeECP3 family contains SERDES Quads on the bottom of the device.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional Unit without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

The LatticeECP3 devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large, dedicated 18Kbit fast memory blocks. Each sysMEM block can be configured in a variety of depths and widths as RAM or ROM. In addition, LatticeECP3 devices contain up to two rows of DSP slices. Each DSP slice has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

The LatticeECP3 devices feature up to 16 embedded 3.2 Gbps SERDES (Serializer / Deserializer) channels. Each SERDES channel contains independent 8b/10b encoding / decoding, polarity adjust and elastic buffer logic. Each group of four SERDES channels, along with its Physical Coding Sub-layer (PCS) block, creates a quad. The functionality of the SERDES/PCS quads can be controlled by memory cells set during device configuration or by registers that are addressable during device operation. The registers in every quad can be programmed via the SERDES Client Interface (SCI). These quads (up to four) are located at the bottom of the devices.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysl/O buffers. The sysl/O buffers of the LatticeECP3 devices are arranged in seven banks, allowing the implementation of a wide variety of I/O standards. In addition, a separate I/O bank is provided for the programming interfaces. 50% of the PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as XGMII, 7:1 LVDS, along with memory interfaces including DDR3.

The LatticeECP3 registers in PFU and sysI/O can be configured to be SET or RESET. After power up and the device is configured, it enters into user mode with these registers SET/RESET according to the configuration setting, allowing the device entering to a known state for predictable system function.

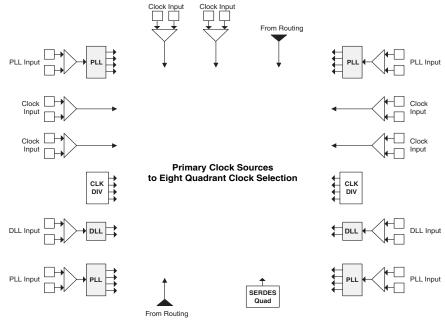

Other blocks provided include PLLs, DLLs and configuration functions. The LatticeECP3 architecture provides two Delay Locked Loops (DLLs) and up to ten Phase Locked Loops (PLLs). The PLL and DLL blocks are located at the end of the EBR/DSP rows.

The configuration block that supports features such as configuration bit-stream decryption, transparent updates and dual-boot support is located toward the center of this EBR row. Every device in the LatticeECP3 family supports a sysCONFIG<sup>™</sup> port located in the corner between banks one and two, which allows for serial or parallel device configuration.

In addition, every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detect capability. The LatticeECP3 devices use 1.2 V as their core voltage.

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Figure 2-2. PFU Diagram

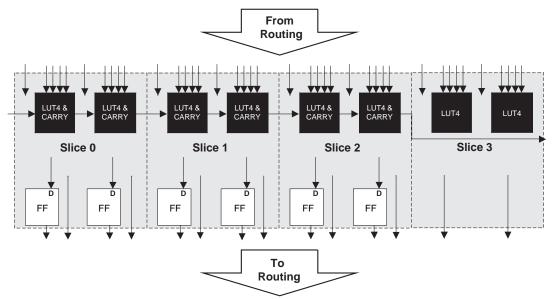

## Slice

Slice 0 through Slice 2 contain two LUT4s feeding two registers, whereas Slice 3 contains two LUT4s only. For PFUs, Slice 0 through Slice 2 can be configured as distributed memory, a capability not available in the PFF. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/ asynchronous), clock select, chip-select and wider RAM/ROM functions.

|         | PFU                     | 3Lock                   | PFF Block               |                    |  |

|---------|-------------------------|-------------------------|-------------------------|--------------------|--|

| Slice   | Resources               | Modes                   | Resources               | Modes              |  |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |  |

Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks.

Slices 0, 1 and 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 10 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

#### Figure 2-10. Primary Clock Sources for LatticeECP3-35

Note: Clock inputs can be configured in differential or single-ended mode.

#### Figure 2-11. Primary Clock Sources for LatticeECP3-70, -95, -150

Note: Clock inputs can be configured in differential or single-ended mode.

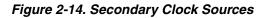

## Secondary Clock/Control Sources

LatticeECP3 devices derive eight secondary clock sources (SC0 through SC7) from six dedicated clock input pads and the rest from routing. Figure 2-14 shows the secondary clock sources. All eight secondary clock sources are defined as inputs to a per-region mux SC0-SC7. SC0-SC3 are primary for control signals (CE and/or LSR), and SC4-SC7 are for the clock.

In an actual implementation, there is some overlap to maximize routability. In addition to SC0-SC3, SC7 is also an input to the control signals (LSR or CE). SC0-SC2 are also inputs to clocks along with SC4-SC7.

Note: Clock inputs can be configured in differential or single-ended mode.

# Secondary Clock/Control Routing

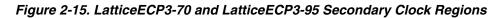

Global secondary clock is a secondary clock that is distributed to all regions. The purpose of the secondary clock routing is to distribute the secondary clock sources to the secondary clock regions. Secondary clocks in the LatticeECP3 devices are region-based resources. Certain EBR rows and special vertical routing channels bind the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP slice in the DSP row or the center of the DSP row. Figure 2-15 shows this special vertical routing channel and the 20 secondary clock regions for the LatticeECP3 family of devices. All devices in the LatticeECP3 family have eight secondary clock resources per region (SC0 to SC7). The same secondary clock routing can be used for control signals.

#### Table 2-6. Secondary Clock Regions

| Device   | Number of Secondary Clock<br>Regions |

|----------|--------------------------------------|

| ECP3-17  | 16                                   |

| ECP3-35  | 16                                   |

| ECP3-70  | 20                                   |

| ECP3-95  | 20                                   |

| ECP3-150 | 36                                   |

Spine Repeaters

## ALU Flags

The sysDSP slice provides a number of flags from the ALU including:

- Equal to zero (EQZ)

- Equal to zero with mask (EQZM)

- Equal to one with mask (EQOM)

- Equal to pattern with mask (EQPAT)

- Equal to bit inverted pattern with mask (EQPATB)

- Accumulator Overflow (OVER)

- Accumulator Underflow (UNDER)

- Either over or under flow supporting LatticeECP2 legacy designs (OVERUNDER)

## **Clock, Clock Enable and Reset Resources**

Global Clock, Clock Enable and Reset signals from routing are available to every sysDSP slice. From four clock sources (CLK0, CLK1, CLK2, and CLK3) one clock is selected for each input register, pipeline register and output register. Similarly Clock Enable (CE) and Reset (RST) are selected at each input register, pipeline register and output register.

# **Resources Available in the LatticeECP3 Family**

Table 2-9 shows the maximum number of multipliers for each member of the LatticeECP3 family. Table 2-10 shows the maximum available EBR RAM Blocks in each LatticeECP3 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

| Device   | DSP Slices | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|----------|------------|----------------|------------------|------------------|

| ECP3-17  | 12         | 48             | 24               | 6                |

| ECP3-35  | 32         | 128            | 64               | 16               |

| ECP3-70  | 64         | 256            | 128              | 32               |

| ECP3-95  | 64         | 256            | 128              | 32               |

| ECP3-150 | 160        | 640            | 320              | 80               |

Table 2-9. Maximum Number of DSP Slices in the LatticeECP3 Family

Table 2-10. Embedded SRAM in the LatticeECP3 Family

| Device   | EBR SRAM Block | Total EBR SRAM<br>(Kbits) |

|----------|----------------|---------------------------|

| ECP3-17  | 38             | 700                       |

| ECP3-35  | 72             | 1327                      |

| ECP3-70  | 240            | 4420                      |

| ECP3-95  | 240            | 4420                      |

| ECP3-150 | 372            | 6850                      |

# sysI/O Differential Electrical Characteristics LVDS25

| Parameter                                                     | Description                                       | Test Conditions                                                | Min.   | Тур. | Max.  | Units |

|---------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------|--------|------|-------|-------|

| V <sub>INP</sub> <sup>1</sup> , V <sub>INM</sub> <sup>1</sup> | Input Voltage                                     |                                                                | 0      | _    | 2.4   | V     |

| V <sub>CM</sub> <sup>1</sup>                                  | Input Common Mode Voltage                         | Half the Sum of the Two Inputs                                 | 0.05   | _    | 2.35  | V     |

| V <sub>THD</sub>                                              | Differential Input Threshold                      | Difference Between the Two Inputs                              | +/-100 | _    | —     | mV    |

| I <sub>IN</sub>                                               | Input Current                                     | Power On or Power Off                                          | —      | _    | +/-10 | μA    |

| V <sub>OH</sub>                                               | Output High Voltage for $V_{OP}$ or $V_{OM}$      | R <sub>T</sub> = 100 Ohm                                       | —      | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                                               | Output Low Voltage for $V_{OP}$ or $V_{OM}$       | R <sub>T</sub> = 100 Ohm                                       | 0.9 V  | 1.03 | —     | V     |

| V <sub>OD</sub>                                               | Output Voltage Differential                       | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250    | 350  | 450   | mV    |

| ΔV <sub>OD</sub>                                              | Change in V <sub>OD</sub> Between High and<br>Low |                                                                | —      |      | 50    | mV    |

| V <sub>OS</sub>                                               | Output Voltage Offset                             | $(V_{OP} + V_{OM})/2, R_{T} = 100 \text{ Ohm}$                 | 1.125  | 1.20 | 1.375 | V     |

| $\Delta V_{OS}$                                               | Change in V <sub>OS</sub> Between H and L         |                                                                | —      | _    | 50    | mV    |

| I <sub>SAB</sub>                                              | Output Short Circuit Current                      | V <sub>OD</sub> = 0V Driver Outputs Shorted to Each Other      | —      |      | 12    | mA    |

1, On the left and right sides of the device, this specification is valid only for  $V_{CCIO} = 2.5$  V or 3.3 V.

# **Differential HSTL and SSTL**

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

# LatticeECP3 Internal Switching Characteristics<sup>1, 2, 5</sup> (Continued)

|                         |                                                           | -      | 8    | -      | 7    | -6     |      |        |

|-------------------------|-----------------------------------------------------------|--------|------|--------|------|--------|------|--------|

| Parameter               | Description                                               | Min.   | Max. | Min.   | Max. | Min.   | Max. | Units. |

| t <sub>HWREN_EBR</sub>  | Hold Write/Read Enable to EBR Memory                      | 0.141  |      | 0.145  |      | 0.149  |      | ns     |

| t <sub>SUCE_EBR</sub>   | Clock Enable Setup Time to EBR Output Register            | 0.087  | _    | 0.096  | _    | 0.104  | _    | ns     |

| t <sub>HCE_EBR</sub>    | Clock Enable Hold Time to EBR Output Register             | -0.066 | _    | -0.080 | _    | -0.094 | _    | ns     |

| t <sub>SUBE_EBR</sub>   | Byte Enable Set-Up Time to EBR Output Register            | -0.071 | _    | -0.070 | _    | -0.068 | _    | ns     |

| t <sub>HBE_EBR</sub>    | Byte Enable Hold Time to EBR Output Register              | 0.118  | _    | 0.098  | _    | 0.077  | _    | ns     |

| DSP Block Tin           | ning <sup>3</sup>                                         |        |      |        |      |        |      |        |

| t <sub>SUI_DSP</sub>    | Input Register Setup Time                                 | 0.32   |      | 0.36   |      | 0.39   |      | ns     |

| t <sub>HI_DSP</sub>     | Input Register Hold Time                                  | -0.17  | _    | -0.19  | _    | -0.21  |      | ns     |

| t <sub>SUP_DSP</sub>    | Pipeline Register Setup Time                              | 2.23   | _    | 2.30   | _    | 2.37   | _    | ns     |

| t <sub>HP_DSP</sub>     | Pipeline Register Hold Time                               | -1.02  | _    | -1.09  | _    | -1.15  |      | ns     |

| t <sub>SUO_DSP</sub>    | Output Register Setup Time                                | 3.09   |      | 3.22   |      | 3.34   |      | ns     |

| t <sub>HO_DSP</sub>     | Output Register Hold Time                                 | -1.67  | _    | -1.76  | _    | -1.84  |      | ns     |

| t <sub>COI_DSP</sub>    | Input Register Clock to Output Time                       | _      | 3.05 |        | 3.35 |        | 3.73 | ns     |

| t <sub>COP_DSP</sub>    | Pipeline Register Clock to Output Time                    | _      | 1.30 | —      | 1.47 | —      | 1.64 | ns     |

| t <sub>COO_DSP</sub>    | Output Register Clock to Output Time                      | _      | 0.58 |        | 0.60 |        | 0.62 | ns     |

| t <sub>SUOPT_DSP</sub>  | Opcode Register Setup Time                                | 0.31   |      | 0.35   |      | 0.39   |      | ns     |

| t <sub>HOPT_DSP</sub>   | Opcode Register Hold Time                                 | -0.20  |      | -0.24  |      | -0.27  |      | ns     |

| t <sub>SUDATA_DSP</sub> | Cascade_data through ALU to Output<br>Register Setup Time | 1.69   | _    | 1.94   | _    | 2.14   | _    | ns     |

| t <sub>HPDATA_DSP</sub> | Cascade_data through ALU to Output<br>Register Hold Time  | -0.58  | _    | -0.80  | _    | -0.97  | _    | ns     |

## **Over Recommended Commercial Operating Conditions**

1. Internal parameters are characterized but not tested on every device.

2. Commercial timing numbers are shown. Industrial timing numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

3. DSP slice is configured in Multiply Add/Sub 18 x 18 mode.

4. The output register is in Flip-flop mode.

5. For details on –9 speed grade devices, please contact your Lattice Sales Representative.

# LatticeECP3 Maximum I/O Buffer Speed (Continued)<sup>1, 2, 3, 4, 5, 6</sup>

#### **Over Recommended Operating Conditions**

| Buffer | Description                    | Max. | Units |

|--------|--------------------------------|------|-------|

| PCI33  | PCI, V <sub>CCIO</sub> = 3.3 V | 66   | MHz   |

1. These maximum speeds are characterized but not tested on every device.

2. Maximum I/O speed for differential output standards emulated with resistors depends on the layout.

3. LVCMOS timing is measured with the load specified in the Switching Test Conditions table of this document.

4. All speeds are measured at fast slew.

5. Actual system operation may vary depending on user logic implementation.

6. Maximum data rate equals 2 times the clock rate when utilizing DDR.

# sysCLOCK PLL Timing

| Parameter                      | Descriptions                                         | Conditions                           | Clock                      | Min.    | Тур. | Max.  | Units       |

|--------------------------------|------------------------------------------------------|--------------------------------------|----------------------------|---------|------|-------|-------------|

| £                              | Input clock frequency (CLKI,                         |                                      | Edge clock                 | 2       | _    | 500   | MHz         |

| f <sub>IN</sub>                | CLKFB)                                               |                                      | Primary clock <sup>4</sup> | 2       | _    | 420   | MHz         |

| 4                              | Output clock frequency (CLKOP,                       |                                      | Edge clock                 | 4       | _    | 500   | MHz         |

| fout                           | CLKOS)                                               |                                      | Primary clock <sup>4</sup> | 4       | _    | 420   | MHz         |

| f <sub>OUT1</sub>              | K-Divider output frequency                           | CLKOK                                |                            | 0.03125 | _    | 250   | MHz         |

| f <sub>OUT2</sub>              | K2-Divider output frequency                          | CLKOK2                               |                            | 0.667   | -    | 166   | MHz         |

| f <sub>VCO</sub>               | PLL VCO frequency                                    |                                      |                            | 500     | _    | 1000  | MHz         |

| f <sub>PFD</sub> ³             | Phase detector input frequency                       |                                      | Edge clock                 | 2       | -    | 500   | MHz         |

|                                |                                                      |                                      | Primary clock <sup>4</sup> | 2       | _    | 420   | MHz         |

| AC Charac                      | teristics                                            |                                      |                            |         |      | 1     |             |

| t <sub>PA</sub>                | Programmable delay unit                              |                                      |                            | 65      | 130  | 260   | ps          |

|                                |                                                      |                                      | Edge clock                 | 45      | 50   | 55    | %           |

| t <sub>DT</sub>                | Output clock duty cycle<br>(CLKOS, at 50% setting)   | f <sub>OUT</sub> ≤ 250 MHz           | Primary clock              | 45      | 50   | 55    | %           |

|                                |                                                      | f <sub>OUT</sub> > 250 MHz           | Primary clock              | 30      | 50   | 70    | %           |

| t <sub>CPA</sub>               | Coarse phase shift error<br>(CLKOS, at all settings) |                                      |                            | -5      | 0    | +5    | % of period |

| t <sub>OPW</sub>               | Output clock pulse width high or<br>low<br>(CLKOS)   |                                      |                            | 1.8     |      | _     | ns          |

|                                |                                                      | f <sub>OUT</sub> ≥ 420 MHz           |                            | _       |      | 200   | ps          |

| t <sub>OPJIT</sub> 1           | Output clock period jitter                           | 420 MHz > f <sub>OUT</sub> ≥ 100 MHz |                            | _       | _    | 250   | ps          |

|                                |                                                      | f <sub>OUT</sub> < 100 MHz           |                            | _       |      | 0.025 | UIPP        |

| t <sub>SK</sub>                | Input clock to output clock skew when N/M = integer  |                                      |                            | _       |      | 500   | ps          |

| . 2                            |                                                      | 2 to 25 MHz                          |                            |         | _    | 200   | us          |

| t <sub>LOCK</sub> <sup>2</sup> | Lock time                                            | 25 to 500 MHz                        |                            | _       | _    | 50    | us          |

| t <sub>UNLOCK</sub>            | Reset to PLL unlock time to ensure fast reset        |                                      |                            | _       | _    | 50    | ns          |

| t <sub>HI</sub>                | Input clock high time                                | 90% to 90%                           |                            | 0.5     | _    | _     | ns          |

| t <sub>LO</sub>                | Input clock low time                                 | 10% to 10%                           |                            | 0.5     | _    | -     | ns          |

| t <sub>IPJIT</sub>             | Input clock period jitter                            |                                      |                            | —       | _    | 400   | ps          |

|                                | Reset signal pulse width high,<br>RSTK               |                                      |                            | 10      |      | _     | ns          |

| t <sub>RST</sub>               | Reset signal pulse width high,<br>RST                |                                      |                            | 500     | _    | -     | ns          |

#### **Over Recommended Operating Conditions**

1. Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock with no additional I/O toggling.

2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

3. Period jitter and cycle-to-cycle jitter numbers are guaranteed for  $f_{PFD} > 4$  MHz. For  $f_{PFD} < 4$  MHz, the jitter numbers may not be met in certain conditions. Please contact the factory for  $f_{PFD} < 4$  MHz.

4. When using internal feedback, maximum can be up to 500 MHz.

# Serial Rapid I/O Type 2/CPRI LV E.24 Electrical and Timing Characteristics

# **AC and DC Characteristics**

## Table 3-15. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub> <sup>1</sup>             | Differential rise/fall time      | 20%-80%         |      | 80   | —    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 |      | —    | 0.17 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | _    | —    | 0.35 | UI    |

1. Rise and Fall times measured with board trace, connector and approximately 2.5pf load.

2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

3. Jitter values are measured with each CML output AC coupled into a 50-Ohm impedance (100-Ohm differential impedance).

4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

5. Values are measured at 2.5 Gbps.

#### Table 3-16. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions         | Min. | Тур. | Max. | Units |

|---------------------------------------------|-----------------------------------------------|-------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 2.5 GHz | 10   | _    | _    | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 2.5 GHz | 6    | _    | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                         | 80   | 100  | 120  | Ohms  |

| J <sub>RX_DJ</sub> <sup>2, 3, 4, 5</sup>    | Deterministic jitter tolerance (peak-to-peak) |                         | _    | _    | 0.37 | UI    |

| J <sub>RX_RJ</sub> <sup>2, 3, 4, 5</sup>    | Random jitter tolerance (peak-to-peak)        |                         | _    | _    | 0.18 | UI    |

| J <sub>RX_SJ</sub> <sup>2, 3, 4, 5</sup>    | Sinusoidal jitter tolerance (peak-to-peak)    |                         | _    | _    | 0.10 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                         | _    | —    | 0.65 | UI    |

| T <sub>RX_EYE</sub>                         | Receiver eye opening                          |                         | 0.35 | _    | —    | UI    |

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-18.

2. Jitter values are measured with each high-speed input AC coupled into a 50-Ohm impedance.

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

5. Values are measured at 2.5 Gbps.

# SMPTE SD/HD-SDI/3G-SDI (Serial Digital Interface) Electrical and Timing Characteristics

## AC and DC Characteristics

#### Table 3-19. Transmit

| Symbol                                  | Description                     | Test Conditions | Min. | Тур. | Max. | Units |

|-----------------------------------------|---------------------------------|-----------------|------|------|------|-------|

| BR <sub>SDO</sub>                       | Serial data rate                |                 | 270  | —    | 2975 | Mbps  |

| T <sub>JALIGNMENT</sub> <sup>2</sup>    | Serial output jitter, alignment | 270 Mbps        | —    | —    | 0.20 | UI    |

| T <sub>JALIGNMENT</sub> <sup>2</sup>    | Serial output jitter, alignment | 1485 Mbps       | —    | —    | 0.20 | UI    |

| T <sub>JALIGNMENT</sub> <sup>1, 2</sup> | Serial output jitter, alignment | 2970Mbps        | —    | —    | 0.30 | UI    |

| T <sub>JTIMING</sub>                    | Serial output jitter, timing    | 270 Mbps        | —    | —    | 0.20 | UI    |

| T <sub>JTIMING</sub>                    | Serial output jitter, timing    | 1485 Mbps       | —    | —    | 1.0  | UI    |

| T <sub>JTIMING</sub>                    | Serial output jitter, timing    | 2970 Mbps       | —    | —    | 2.0  | UI    |

Notes:

Timing jitter is measured in accordance with SMPTE RP 184-1996, SMPTE RP 192-1996 and the applicable serial data transmission standard, SMPTE 259M-1997 or SMPTE 292M (proposed). A color bar test pattern is used. The value of f<sub>SCLK</sub> is 270 MHz or 360 MHz for SMPTE 259M, 540 MHz for SMPTE 344M or 1485 MHz for SMPTE 292M serial data rates. See the Timing Jitter Bandpass section.

2. Jitter is defined in accordance with SMPTE RP1 184-1996 as: jitter at an equipment output in the absence of input jitter.

3. All Tx jitter is measured at the output of an industry standard cable driver; connection to the cable driver is via a 50 Ohm impedance differential signal from the Lattice SERDES device.

4. The cable driver drives: RL=75 Ohm, AC-coupled at 270, 1485, or 2970 Mbps, RREFLVL=RREFPRE=4.75 kOhm 1%.

#### Table 3-20. Receive

| Symbol            | Description                                                  | Test Conditions | Min.                                           | Тур. | Max. | Units |

|-------------------|--------------------------------------------------------------|-----------------|------------------------------------------------|------|------|-------|

| BR <sub>SDI</sub> | Serial input data rate                                       |                 | 270                                            | —    | 2970 | Mbps  |

| CID               | Stream of non-transitions<br>(=Consecutive Identical Digits) |                 | 7(3G)/26(SMPTE<br>Triple rates)<br>@ 10-12 BER | _    | _    | Bits  |

#### Table 3-21. Reference Clock

| Symbol            | Description                  | Test Conditions | Min. | Тур. | Max.  | Units |

|-------------------|------------------------------|-----------------|------|------|-------|-------|

| F <sub>VCLK</sub> | Video output clock frequency |                 | 27   | -    | 74.25 | MHz   |

| DCV               | Duty cycle, video clock      |                 | 45   | 50   | 55    | %     |

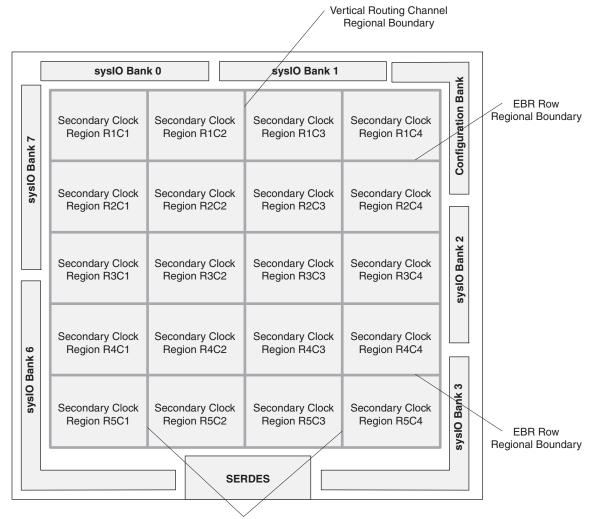

## Figure 3-26. Configuration from PROGRAMN Timing

1. The CFG pins are normally static (hard wired)

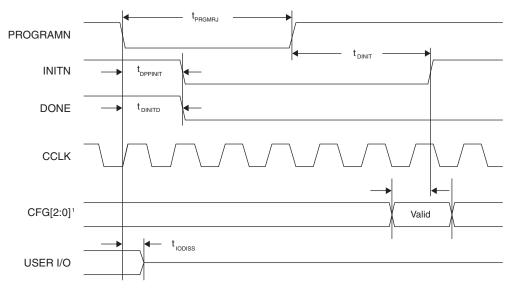

#### Figure 3-27. Wake-Up Timing

# sysl/O Differential Electrical Characteristics

# Transition Reduced LVDS (TRLVDS DC Specification)

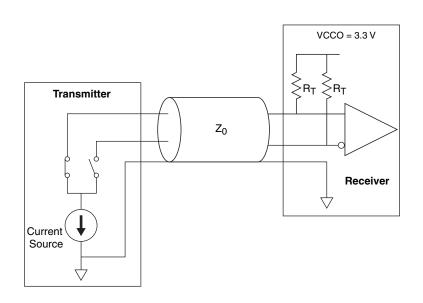

### **Over Recommended Operating Conditions**

| Symbol           | Description                       | Min. | Nom. | Max.  | Units |

|------------------|-----------------------------------|------|------|-------|-------|

| V <sub>CCO</sub> | Driver supply voltage (+/- 5%)    | 3.14 | 3.3  | 3.47  | V     |

| V <sub>ID</sub>  | Input differential voltage        | 150  | —    | 1200  | mV    |

| V <sub>ICM</sub> | Input common mode voltage         | 3    | —    | 3.265 | V     |

| V <sub>CCO</sub> | Termination supply voltage        | 3.14 | 3.3  | 3.47  | V     |

| R <sub>T</sub>   | Termination resistance (off-chip) | 45   | 50   | 55    | Ohms  |

Note: LatticeECP3 only supports the TRLVDS receiver.

## Mini LVDS

#### **Over Recommended Operating Conditions**

| Parameter Symbol                | Description                                                       | Min.                      | Тур. | Max.                      | Units |

|---------------------------------|-------------------------------------------------------------------|---------------------------|------|---------------------------|-------|

| Z <sub>O</sub>                  | Single-ended PCB trace impedance                                  | 30                        | 50   | 75                        | Ohms  |

| R <sub>T</sub>                  | Differential termination resistance                               | 50                        | 100  | 150                       | Ohms  |

| V <sub>OD</sub>                 | Output voltage, differential,  V <sub>OP</sub> - V <sub>OM</sub>  | 300                       | —    | 600                       | mV    |

| V <sub>OS</sub>                 | Output voltage, common mode, $ V_{OP} + V_{OM} /2$                | 1                         | 1.2  | 1.4                       | V     |

| ΔV <sub>OD</sub>                | Change in V <sub>OD</sub> , between H and L                       | —                         | —    | 50                        | mV    |

| $\Delta V_{ID}$                 | Change in V <sub>OS</sub> , between H and L                       | —                         | —    | 50                        | mV    |

| V <sub>THD</sub>                | Input voltage, differential,  V <sub>INP</sub> - V <sub>INM</sub> | 200                       | —    | 600                       | mV    |

| V <sub>CM</sub>                 | Input voltage, common mode, $ V_{INP} + V_{INM} /2$               | 0.3+(V <sub>THD</sub> /2) | —    | 2.1-(V <sub>THD</sub> /2) |       |

| T <sub>R</sub> , T <sub>F</sub> | Output rise and fall times, 20% to 80%                            | —                         | —    | 550                       | ps    |

| T <sub>ODUTY</sub>              | Output clock duty cycle                                           | 40                        | _    | 60                        | %     |

Note: Data is for 6 mA differential current drive. Other differential driver current options are available.

# Signal Descriptions (Cont.)

| Signal Name                     | I/O      | Description                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [LOC]DQS[num]                   | I/O      | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQS, num = ball function number.                                                                                                                                                                                                                                                                         |

| [LOC]DQ[num]                    | I/O      | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQ, associated DQS number.                                                                                                                                                                                                                                                                               |

| Test and Programming (Dedicated | Pins)    |                                                                                                                                                                                                                                                                                                                                                                          |

| TMS                             | I        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                                                                                                                               |

| тск                             | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                                                                                                                        |

| TDI                             | I        | Test Data in pin. Used to load data into device using 1149.1 state machine.<br>After power-up, this TAP port can be activated for configuration by sending<br>appropriate command. (Note: once a configuration port is selected it is<br>locked. Another configuration port cannot be selected until the power-up<br>sequence). Pull-up is enabled during configuration. |

| TDO                             | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.                                                                                                                                                                                                                                                                                           |

| VCCJ                            | _        | Power supply pin for JTAG Test Access Port.                                                                                                                                                                                                                                                                                                                              |

| Configuration Pads (Used During | sysCONFI | Ġ)                                                                                                                                                                                                                                                                                                                                                                       |

| CFG[2:0]                        | I        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled. These are dedicated pins.                                                                                                                                                                                                               |

| INITN                           | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled. It is a dedicated pin.                                                                                                                                                                                                                                         |

| PROGRAMN                        | I        | Initiates configuration sequence when asserted low. This pin always has an active pull-up. It is a dedicated pin.                                                                                                                                                                                                                                                        |

| DONE                            | I/O      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress. It is a dedicated pin.                                                                                                                                                                                                                                   |

| CCLK                            | I        | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. It is a dedicated pin.                                                                                                                                                                                                                                                            |

| MCLK                            | I/O      | Output Configuration Clock for configuring an FPGA in SPI, SPIm, and Master configuration modes.                                                                                                                                                                                                                                                                         |

| BUSY/SISPI                      | 0        | Parallel configuration mode busy indicator. SPI/SPIm mode data output.                                                                                                                                                                                                                                                                                                   |

| CSN/SN/OEN                      | I/O      | Parallel configuration mode active-low chip select. Slave SPI chip select.<br>Parallel burst Flash output enable.                                                                                                                                                                                                                                                        |

| CS1N/HOLDN/RDY                  | I        | Parallel configuration mode active-low chip select. Slave SPI hold input.                                                                                                                                                                                                                                                                                                |

| WRITEN                          | I        | Write enable for parallel configuration modes.                                                                                                                                                                                                                                                                                                                           |

| DOUT/CSON/CSSPI1N               | 0        | Serial data output. Chip select output. SPI/SPIm mode chip select.                                                                                                                                                                                                                                                                                                       |

|                                 |          | sysCONFIG Port Data I/O for Parallel mode. Open drain during configuration.                                                                                                                                                                                                                                                                                              |

| D[0]/SPIFASTN                   | I/O      | sysCONFIG Port Data I/O for SPI or SPIm. When using the SPI or SPIm mode, this pin should either be tied high or low, must not be left floating. Open drain during configuration.                                                                                                                                                                                        |

| D1                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D2                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D3/SI                           | I/O      | Parallel configuration I/O. Slave SPI data input. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                  |

| D4/SO                           | I/O      | Parallel configuration I/O. Slave SPI data output. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                 |

| D5                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D6/SPID1                        | I/O      | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                   |

# **Signal Descriptions (Cont.)**

| I/O | Description                                                                            |

|-----|----------------------------------------------------------------------------------------|

| I/O | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura-<br>tion. |

| I/O | Serial data input for slave serial mode. SPI/SPIm mode chip select.                    |

|     |                                                                                        |

| I   | High-speed input, negative channel m                                                   |

| 0   | High-speed output, negative channel m                                                  |

| I   | Negative Reference Clock Input                                                         |

| I   | High-speed input, positive channel m                                                   |

| 0   | High-speed output, positive channel m                                                  |

| I   | Positive Reference Clock Input                                                         |

| —   | Output buffer power supply, channel m (1.2V/1.5)                                       |

|     | Input buffer power supply, channel m (1.2V/1.5V)                                       |

|     | I/O<br>I/O<br>I<br>I<br>I<br>I<br>I<br>I                                               |

1. When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

2. These pins are dedicated inputs or can be used as general purpose I/O.

3. m defines the associated channel in the quad.

# Pin Information Summary (Cont.)

| Pin Information                  | n Summary              |           | ECP3-95EA |            | ECP3-        | 150EA         |

|----------------------------------|------------------------|-----------|-----------|------------|--------------|---------------|

| Pin Ty                           | ре                     | 484 fpBGA | 672 fpBGA | 1156 fpBGA | 672<br>fpBGA | 1156<br>fpBGA |

|                                  | Bank 0                 | 21        | 30        | 43         | 30           | 47            |

|                                  | Bank 1                 | 18        | 24        | 39         | 24           | 43            |

| Emulated                         | Bank 2                 | 8         | 12        | 13         | 12           | 18            |

| Differential I/O                 | Bank 3                 | 20        | 23        | 33         | 23           | 37            |

| per Bank                         | Bank 6                 | 22        | 25        | 33         | 25           | 37            |

|                                  | Bank 7                 | 11        | 16        | 18         | 16           | 24            |

|                                  | Bank 8                 | 12        | 12        | 12         | 12           | 12            |

|                                  | Bank 0                 | 0         | 0         | 0          | 0            | 0             |

|                                  | Bank 1                 | 0         | 0         | 0          | 0            | 0             |

| Highspeed                        | Bank 2                 | 6         | 9         | 9          | 9            | 15            |

| Differential I/O                 | Bank 3                 | 9         | 12        | 16         | 12           | 21            |

| per Bank                         | Bank 6                 | 11        | 14        | 16         | 14           | 21            |

|                                  | Bank 7                 | 9         | 12        | 13         | 12           | 18            |

|                                  | Bank 8                 | 0         | 0         | 0          | 0            | 0             |

|                                  | Bank 0                 | 42/21     | 60/30     | 86/43      | 60/30        | 94/47         |

|                                  | Bank 1                 | 36/18     | 48/24     | 78/39      | 48/24        | 86/43         |

| Total Single Ended/              | Bank 2                 | 28/14     | 42/21     | 44/22      | 42/21        | 66/33         |

| Total Differential               | Bank 3                 | 58/29     | 71/35     | 98/49      | 71/35        | 116/58        |

| I/O per Bank                     | Bank 6                 | 67/33     | 78/39     | 98/49      | 78/39        | 116/58        |

|                                  | Bank 7                 | 40/20     | 56/28     | 62/31      | 56/28        | 84/42         |

|                                  | Bank 8                 | 24/12     | 24/12     | 24/12      | 24/12        | 24/12         |

|                                  | Bank 0                 | 3         | 5         | 7          | 5            | 7             |

|                                  | Bank 1                 | 3         | 4         | 7          | 4            | 7             |

|                                  | Bank 2                 | 2         | 3         | 3          | 3            | 4             |

| DDR Groups<br>Bonded<br>per Bank | Bank 3                 | 3         | 4         | 5          | 4            | 7             |

|                                  | Bank 6                 | 4         | 4         | 5          | 4            | 7             |

|                                  | Bank 7                 | 3         | 4         | 4          | 4            | 6             |

|                                  | Configuration<br>Bank8 | 0         | 0         | 0          | 0            | 0             |

| SERDES Quads                     | •                      | 1         | 2         | 3          | 2            | 4             |

1. These pins must remain floating on the board.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-7FN484C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-8FN484C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-6LFN484C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-7LFN484C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-8LFN484C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-6FN672C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-7FN672C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-8FN672C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-6LFN672C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-7LFN672C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-8LFN672C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-6FN1156C  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-7FN1156C  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-8FN1156C  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-6LFN1156C | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-7LFN1156C | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-8LFN1156C | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-7FN484C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-8FN484C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-6LFN484C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-7LFN484C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-8LFN484C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-6FN672C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-7FN672C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-8FN672C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-6LFN672C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-7LFN672C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-8LFN672C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-6FN1156C  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-7FN1156C  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-8FN1156C  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-6LFN1156C | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-7LFN1156C | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-8LFN1156C | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.