Welcome to **E-XFL.COM**

### Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Not For New Designs                                                          |

| Number of LABs/CLBs            | 4125                                                                         |

| Number of Logic Elements/Cells | 33000                                                                        |

| Total RAM Bits                 | 1358848                                                                      |

| Number of I/O                  | 310                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 672-BBGA                                                                     |

| Supplier Device Package        | 672-FPBGA (27x27)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-35ea-9fn672i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

The LatticeECP3™ (EConomy Plus Third generation) family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES and high speed source synchronous interfaces in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 65 nm technology making the devices suitable for high-volume, high-speed, low-cost applications.

The LatticeECP3 device family expands look-up-table (LUT) capacity to 149K logic elements and supports up to 586 user I/Os. The LatticeECP3 device family also offers up to 320 18 x 18 multipliers and a wide range of parallel I/O standards.

The LatticeECP3 FPGA fabric is optimized with high performance and low cost in mind. The LatticeECP3 devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), Delay Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the LatticeECP3 device family supports a broad range of interface standards, including DDR3, XGMII and 7:1 LVDS.

The LatticeECP3 device family also features high speed SERDES with dedicated PCS functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, SMPTE, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit Pre-emphasis and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The LatticeECP3 devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

The Lattice Diamond<sup>TM</sup> and ispLEVER<sup>®</sup> design software allows large complex designs to be efficiently implemented using the LatticeECP3 FPGA family. Synthesis library support for LatticeECP3 is available for popular logic synthesis tools. Diamond and ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP3 device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the LatticeECP3 family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

syslO syslO Configuration Logic: Bank 0 Bank 1 Dual-boot, Encryption and Transparent Updates **JTAG** On-chip Oscillator Pre-engineered Source Synchronous Support: DDR3 - 800 Mbps syslO sysIO Generic - Up to 1 Gbps Bank Bank **Enhanced DSP** Slices: Multiply, Accumulate and ALU svsCLOCK PLLs & DLLs: Frequency Synthesis and Clock Alignment Flexible sysIO: LVCMOS, HSTL, SSTL LVDS Up to 486 I/Os sysMEM Block RAM: 18 Kbit Flexible Routing: Optimized for speed and routability Programmable SERDES/PCS SERDES/PCS SERDES/PCS SERDES/PC **Function Units:** CH 3 CH 2 CH 1 CH 0 Up to 149K LUTs sysIO Bank 6 sysIO Bank 3 3.2 Gbps SERDES

Figure 2-1. Simplified Block Diagram, LatticeECP3-35 Device (Top Level)

Note: There is no Bank 4 or Bank 5 in LatticeECP3 devices.

#### **PFU Blocks**

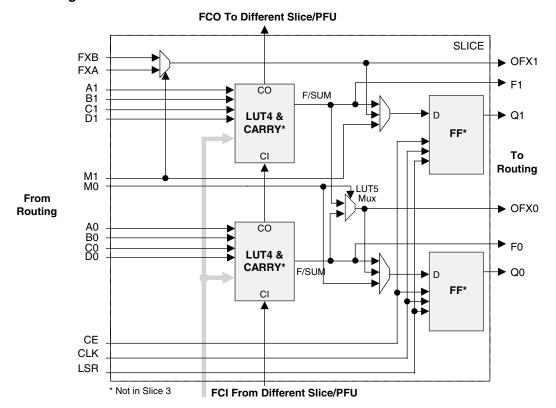

The core of the LatticeECP3 device consists of PFU blocks, which are provided in two forms, the PFU and PFF. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic and ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

Each PFU block consists of four interconnected slices numbered 0-3 as shown in Figure 2-2. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

Figure 2-3. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

WCK is CLK WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2 WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре               | Signal Names   | Description                                                          |

|----------|--------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose      | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                                   |

| Input    | Control signal     | CE             | Clock Enable                                                         |

| Input    | Control signal     | LSR            | Local Set/Reset                                                      |

| Input    | Control signal     | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal   | FC             | Fast Carry-in <sup>1</sup>                                           |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6 and LUT7                        |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6 and LUT7                        |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals       | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals       | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal   | FCO            | Slice 2 of each PFU is the fast carry chain output <sup>1</sup>      |

<sup>1.</sup> See Figure 2-3 for connection details.

<sup>2.</sup> Requires two PFUs.

#### **ROM Mode**

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information, please refer to TN1179, LatticeECP3 Memory Usage Guide.

#### Routing

There are many resources provided in the LatticeECP3 devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The LatticeECP3 family has an enhanced routing architecture that produces a compact design. The Diamond and ispLEVER design software tool suites take the output of the synthesis tool and places and routes the design.

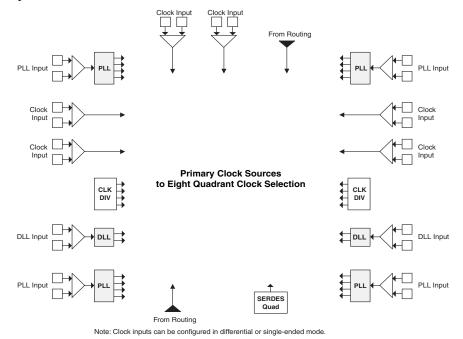

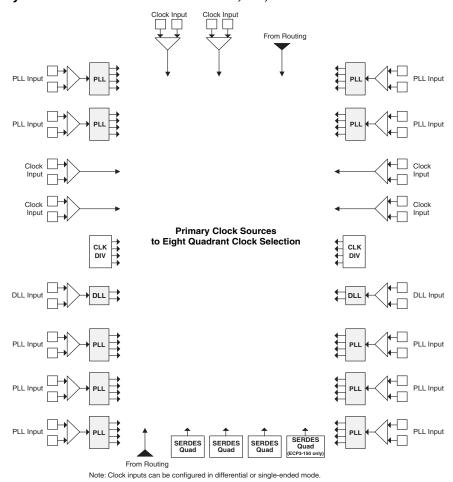

#### sysCLOCK PLLs and DLLs

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The devices in the LatticeECP3 family support two to ten full-featured General Purpose PLLs.

#### **General Purpose PLL**

The architecture of the PLL is shown in Figure 2-4. A description of the PLL functionality follows.

CLKI is the reference frequency (generated either from the pin or from routing) for the PLL. CLKI feeds into the Input Clock Divider block. The CLKFB is the feedback signal (generated from CLKOP, CLKOS or from a user clock pin/logic). This signal feeds into the Feedback Divider. The Feedback Divider is used to multiply the reference frequency.

Both the input path and feedback signals enter the Phase Frequency Detect Block (PFD) which detects first for the frequency, and then the phase, of the CLKI and CLKFB are the same which then drives the Voltage Controlled Oscillator (VCO) block. In this block the difference between the input path and feedback signals is used to control the frequency and phase of the oscillator. A LOCK signal is generated by the VCO to indicate that the VCO has locked onto the input clock signal. In dynamic mode, the PLL may lose lock after a dynamic delay adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied.

The output of the VCO then enters the CLKOP divider. The CLKOP divider allows the VCO to operate at higher frequencies than the clock output (CLKOP), thereby increasing the frequency range. The Phase/Duty Cycle/Duty Trim block adjusts the phase and duty cycle of the CLKOS signal. The phase/duty cycle setting can be pre-programmed or dynamically adjusted. A secondary divider takes the CLKOP or CLKOS signal and uses it to derive lower frequency outputs (CLKOK).

The primary output from the CLKOP divider (CLKOP) along with the outputs from the secondary dividers (CLKOK and CLKOK2) and Phase/Duty select (CLKOS) are fed to the clock distribution network.

The PLL allows two methods for adjusting the phase of signal. The first is referred to as Fine Delay Adjustment. This inserts up to 16 nominal 125 ps delays to be applied to the secondary PLL output. The number of steps may be set statically or from the FPGA logic. The second method is referred to as Coarse Phase Adjustment. This allows the phase of the rising and falling edge of the secondary PLL output to be adjusted in 22.5 degree steps. The number of steps may be set statically or from the FPGA logic.

Figure 2-10. Primary Clock Sources for LatticeECP3-35

Figure 2-11. Primary Clock Sources for LatticeECP3-70, -95, -150

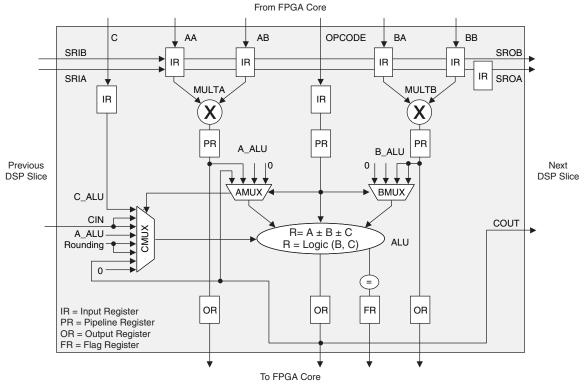

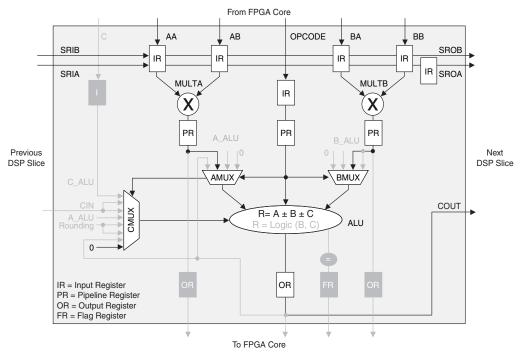

Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | х9             | x18 | x36 |

|-------------------|----------------|-----|-----|

| MULT              | 4              | 2   | 1/2 |

| MAC               | 1              | 1   | _   |

| MULTADDSUB        | 2              | 1   | _   |

| MULTADDSUBSUM     | 1 <sup>1</sup> | 1/2 | _   |

<sup>1.</sup> One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

#### **MULTADDSUBSUM DSP Element**

In this case, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 0. Additionally, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 1. The results of both addition/subtractions are added by the second ALU following the slice cascade path. The user can enable the input, output and pipeline registers. Figure 2-30 and Figure 2-31 show the MULTADDSUBSUM sysDSP element

Figure 2-30. MULTADDSUBSUM Slice 0

D Q

DQ

Clock Transfer & ► INCLK\*\* **Gearing Registers\*** INDD **DDR Registers** Synch Registers To DQSI\*\* 01 D Q INB Fixed Delay D D Q H<sub>DQ</sub> 11 DQ CE D Q Dynamic Delay (From sysIO > R Buffer) IPB 01 D Q G E<sub>D</sub>Q DEL[3:0] С D Q DΩ D Q D Q **ECLKDQSR** DQJ ECLK2 DQ INA CI KP

10

D Q

L,

Figure 2-33. Input Register Block for Left, Right and Top Edges

- \* Only on the left and right sides.

- \*\* Selected PIO.

**DDRCLKPO**

ECLK1

ECLK2 SCLK

Note: Simplified diagram does not show CE/SET/REST details.

#### **Output Register Block**

The output register block registers signals from the core of the device before they are passed to the sysl/O buffers. The blocks on the left and right PIOs contain registers for SDR and full DDR operation. The topside PIO block is the same as the left and right sides except it does not support ODDRX2 gearing of output logic. ODDRX2 gearing is used in DDR3 memory interfaces. The PIO blocks on the bottom contain the SDR registers but do not support generic DDR.

Figure 2-34 shows the Output Register Block for PIOs on the left and right edges.

In SDR mode, OPOSA feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a Dtype or latch. In DDR mode, two of the inputs are fed into registers on the positive edge of the clock. At the next clock cycle, one of the registered outputs is also latched.

A multiplexer running off the same clock is used to switch the mux between the 11 and 01 inputs that will then feed the output.

A gearbox function can be implemented in the output register block that takes four data streams: OPOSA, ONEGA, OPOSB and ONEGB. All four data inputs are registered on the positive edge of the system clock and two of them are also latched. The data is then output at a high rate using a multiplexer that runs off the DQCLK0 and DQCLK1 clocks. DQCLK0 and DQCLK1 are used in this case to transfer data from the system clock to the edge clock domain. These signals are generated in the DQS Write Control Logic block. See Figure 2-37 for an overview of the DQS write control logic.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on this topic.

Further discussion on using the DQS strobe in this module is discussed in the DDR Memory section of this data sheet.

# 2. Left and Right (Banks 2, 3, 6 and 7) sysl/O Buffer Pairs (50% Differential and 100% Single-Ended Outputs)

The sysl/O buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. One of the referenced input buffers can also be configured as a differential input. In these banks the two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp (complementary) pad is associated with the negative side of the differential I/O.

In addition, programmable on-chip input termination (parallel or differential, static or dynamic) is supported on these sides, which is required for DDR3 interface. However, there is no support for hot-socketing for the I/O pins located on the left and right side of the device as the PCI clamp is always enabled on these pins.

LVDS, RSDS, PPLVDS and Mini-LVDS differential output drivers are available on 50% of the buffer pairs on the left and right banks.

## 3. Configuration Bank sysl/O Buffer Pairs (Single-Ended Outputs, Only on Shared Pins When Not Used by Configuration)

The sysl/O buffers in the Configuration Bank consist of ratioed single-ended output drivers and single-ended input buffers. This bank does not support PCI clamp like the other banks on the top, left, and right sides.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Programmable PCI clamps are only available on the top banks. PCI clamps are used primarily on inputs and bidirectional pads to reduce ringing on the receiving end.

#### Typical sysl/O I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$ ,  $V_{CCIO8}$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all other  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. For more information about controlling the output logic state with valid input logic levels during power-up in LatticeECP3 devices, see the list of technical documentation at the end of this data sheet.

The  $V_{CC}$  and  $V_{CCAUX}$  supply the power to the FPGA core fabric, whereas the  $V_{CCIO}$  supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, it is recommended that the I/O buffers be powered-up prior to the FPGA core fabric.  $V_{CCIO}$  supplies should be powered-up before or together with the  $V_{CC}$  and  $V_{CCAUX}$  supplies.

#### Supported sysl/O Standards

The LatticeECP3 sysl/O buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2 V, 1.5 V, 1.8 V, 2.5 V and 3.3 V standards. In the LVCMOS and LVTTL modes, the buffer has individual configuration options for drive strength, slew rates, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL and HSTL. Differential standards supported include LVDS, BLVDS, LVPECL, MLVDS, RSDS, Mini-LVDS, PPLVDS (point-to-point LVDS), TRLVDS (Transition Reduced LVDS), differential SSTL and differential HSTL. For further information on utilizing the sysl/O buffer to support a variety of standards please see TN1177, LatticeECP3 syslO Usage Guide.

| Table 2-14. | Available | <b>SERDES</b> | Quads p | er LatticeECP3 | Devices |

|-------------|-----------|---------------|---------|----------------|---------|

|-------------|-----------|---------------|---------|----------------|---------|

| Package    | ECP3-17    | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|------------|------------|---------|---------|---------|----------|

| 256 ftBGA  | 1          | 1       | _       | _       | _        |

| 328 csBGA  | 2 channels | _       | _       | _       | _        |

| 484 fpBGA  | 1          | 1       | 1       | 1       |          |

| 672 fpBGA  | _          | 1       | 2       | 2       | 2        |

| 1156 fpBGA | _          | _       | 3       | 3       | 4        |

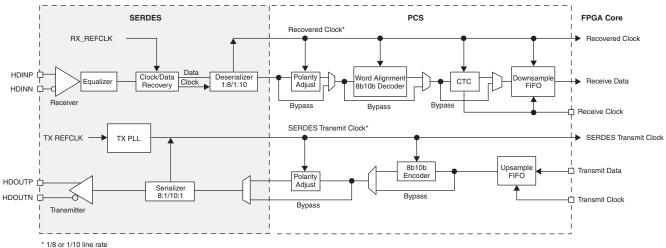

#### **SERDES Block**

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2-41 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCOB and VCCIB).

Figure 2-41. Simplified Channel Block Diagram for SERDES/PCS Block

#### **PCS**

As shown in Figure 2-41, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic.

There are some restrictions to be aware of when using spread spectrum. When a quad shares a PCI Express x1 channel with a non-PCI Express channel, ensure that the reference clock for the quad is compatible with all protocols within the quad. For example, a PCI Express spread spectrum reference clock is not compatible with most Gigabit Ethernet applications because of tight CTC ppm requirements.

While the LatticeECP3 architecture will allow the mixing of a PCI Express channel and a Gigabit Ethernet, Serial RapidIO or SGMII channel within the same quad, using a PCI Express spread spectrum clocking as the transmit reference clock will cause a violation of the Gigabit Ethernet, Serial RapidIO and SGMII transmit jitter specifications.

For further information on SERDES, please see TN1176, LatticeECP3 SERDES/PCS Usage Guide.

#### **IEEE 1149.1-Compliant Boundary Scan Testability**

All LatticeECP3 devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port has its own supply voltage  $V_{CCI}$  and can operate with LVCMOS3.3, 2.5, 1.8, 1.5 and 1.2 standards.

For more information, please see TN1169, LatticeECP3 sysCONFIG Usage Guide.

#### **Device Configuration**

All LatticeECP3 devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration, and the sysCONFIG port, support dual-byte, byte and serial configuration. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. The sysCONFIG port includes seven I/Os used as dedicated pins with the remaining pins used as dual-use pins. See TN1169, LatticeECP3 sysCONFIG Usage Guide for more information about using the dual-use pins as general purpose I/Os.

There are various ways to configure a LatticeECP3 device:

- 1. JTAG

- 2. Standard Serial Peripheral Interface (SPI and SPIm modes) interface to boot PROM memory

- 3. System microprocessor to drive a x8 CPU port (PCM mode)

- 4. System microprocessor to drive a serial slave SPI port (SSPI mode)

- 5. Generic byte wide flash with a MachXO™ device, providing control and addressing

On power-up, the FPGA SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port.

LatticeECP3 devices also support the Slave SPI Interface. In this mode, the FPGA behaves like a SPI Flash device (slave mode) with the SPI port of the FPGA to perform read-write operations.

# LatticeECP3 Family Data Sheet DC and Switching Characteristics

April 2014 Data Sheet DS1021

#### Absolute Maximum Ratings<sup>1, 2, 3</sup>

- 2. Compliance with the Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

- 4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

#### **Recommended Operating Conditions<sup>1</sup>**

| Parameter                                                                      | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Supply Voltage                                                            | 1.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Auxiliary Supply Voltage, Terminating Resistor Switching Power Supply (SERDES) | 3.135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.465                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PLL Supply Voltage                                                             | 3.135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.465                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I/O Driver Supply Voltage                                                      | 1.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.465                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Supply Voltage for IEEE 1149.1 Test Access Port                                | 1.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.465                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input Reference Voltage                                                        | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Termination Voltage                                                            | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.3125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Junction Temperature, Commercial Operation                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Junction Temperature, Industrial Operation                                     | -40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ower Supply <sup>6</sup>                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Input Buffer Power Supply (1.2 V)                                              | 1.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input Buffer Power Supply (1.5 V)                                              | 1.425                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.575                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Output Buffer Power Supply (1.2 V)                                             | 1.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Output Buffer Power Supply (1.5 V)                                             | 1.425                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.575                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Transmit, Receive, PLL and Reference Clock Buffer Power Supply                 | 1.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                | Core Supply Voltage Auxiliary Supply Voltage, Terminating Resistor Switching Power Supply (SERDES)  PLL Supply Voltage I/O Driver Supply Voltage Supply Voltage for IEEE 1149.1 Test Access Port Input Reference Voltage Termination Voltage Junction Temperature, Commercial Operation Junction Temperature, Industrial Operation ower Supply <sup>6</sup> Input Buffer Power Supply (1.2 V) Input Buffer Power Supply (1.5 V) Output Buffer Power Supply (1.5 V) Output Buffer Power Supply (1.5 V) | Core Supply Voltage Auxiliary Supply Voltage, Terminating Resistor Switching Power Supply (SERDES)  PLL Supply Voltage 3.135 I/O Driver Supply Voltage 1.14 Supply Voltage for IEEE 1149.1 Test Access Port 1.14 Input Reference Voltage 0.5 Termination Voltage 0.5 Junction Temperature, Commercial Operation Junction Temperature, Industrial Operation ower Supply <sup>6</sup> Input Buffer Power Supply (1.2 V) Input Buffer Power Supply (1.5 V) Output Buffer Power Supply (1.2 V) 1.14 Output Buffer Power Supply (1.5 V) 1.425 Output Buffer Power Supply (1.5 V) 1.425 | Core Supply Voltage Auxiliary Supply Voltage, Terminating Resistor Switching Power Supply (SERDES)  PLL Supply Voltage 3.135 3.465  I/O Driver Supply Voltage 1.14 3.465  Supply Voltage for IEEE 1149.1 Test Access Port 1.14 3.465  Input Reference Voltage 0.5 Input Reference Voltage 0.5 Junction Temperature, Commercial Operation 0 Supply  Input Buffer Power Supply (1.2 V) Input Buffer Power Supply (1.5 V)  Output Buffer Power Supply (1.5 V) 1.425 1.575  Output Buffer Power Supply (1.5 V) 1.425 1.575 |

For correct operation, all supplies except V<sub>REF</sub> and V<sub>TT</sub> must be held in their valid operation range. This is true independent of feature usage.

<sup>1.</sup> Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 1.2 V, they must be connected to the same power supply as V<sub>CC.</sub> If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 3.3 V, they must be connected to the same power supply as V<sub>CCAUX</sub>.

<sup>3.</sup> See recommended voltages by I/O standard in subsequent table.

<sup>4.</sup>  $V_{CCAUX}$  ramp rate must not exceed 30 mV/ $\mu$ s during power-up when transitioning between 0 V and 3.3 V.

<sup>5.</sup> If not used, V<sub>TT</sub> should be left floating.

<sup>6.</sup> See TN1176, LatticeECP3 SERDES/PCS Usage Guide for information on board considerations for SERDES power supplies.

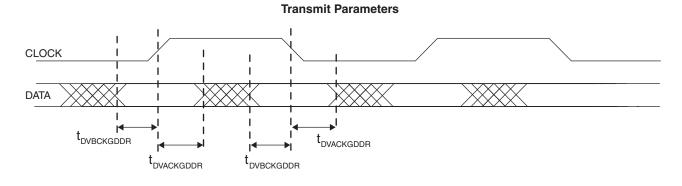

### LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

#### **Over Recommended Commercial Operating Conditions**

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         |                                |                           | -8      |          | <b>-7</b> |           | -6       |           |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------|---------------------------|---------|----------|-----------|-----------|----------|-----------|----------|

| MAX. GDDR   DDRX1 Clock Frequency   All ECPSEA Devices   —   250   —   250   —   250   MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Parameter               | Description                    | Device                    | Min.    | Max.     | Min.      | Max.      | Min.     | Max.      | Units    |

| Left and Right Sides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>DVECLKGDDR</sub> | Data Hold After CLK            | All ECP3EA Devices        | 0.775   | _        | 0.775     | _         | 0.775    | _         | UI       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | f <sub>MAX_GDDR</sub>   | DDRX1 Clock Frequency          | All ECP3EA Devices        | _       | 250      | _         | 250       | _        | 250       | MHz      |

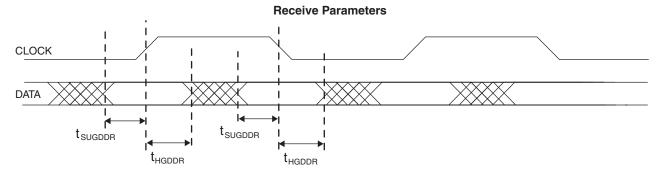

| SUGIDIAN   Data Setup Before CLK   ECP3-150EA   321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         | nputs with Clock and Data (>10 | Bits Wide) Centered at P  | n (GDDF | X2_RX.I  | ECLK.Ce   | ntered) l | Jsing PC | LK Pin fo | or Clock |

| HOGODR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Left and Right Sid      | les                            |                           |         |          |           |           |          |           |          |

| Max. GDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>SUGDDR</sub>     | Data Setup Before CLK          | ECP3-150EA                | 321     | _        | 403       | I —       | 471      | _         | ps       |

| Suggior   Data Setup Before CLK   ECP3-70EA/95EA   321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t <sub>HOGDDR</sub>     | Data Hold After CLK            | ECP3-150EA                | 321     | _        | 403       | _         | 471      | _         | ps       |