# E: Lattice Semiconductor Corporation - LFE3-70EA-6LFN672C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 8375                                                                          |

| Number of Logic Elements/Cells | 67000                                                                         |

| Total RAM Bits                 | 4526080                                                                       |

| Number of I/O                  | 380                                                                           |

| Number of Gates                |                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 672-BBGA                                                                      |

| Supplier Device Package        | 672-FPBGA (27x27)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70ea-6lfn672c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Introduction

The LatticeECP3<sup>™</sup> (EConomy Plus Third generation) family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES and high speed source synchronous interfaces in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 65 nm technology making the devices suitable for high-volume, high-speed, low-cost applications.

The LatticeECP3 device family expands look-up-table (LUT) capacity to 149K logic elements and supports up to 586 user I/Os. The LatticeECP3 device family also offers up to 320 18 x 18 multipliers and a wide range of parallel I/O standards.

The LatticeECP3 FPGA fabric is optimized with high performance and low cost in mind. The LatticeECP3 devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), Delay Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the LatticeECP3 device family supports a broad range of interface standards, including DDR3, XGMII and 7:1 LVDS.

The LatticeECP3 device family also features high speed SERDES with dedicated PCS functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, SMPTE, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit Pre-emphasis and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The LatticeECP3 devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

The Lattice Diamond<sup>™</sup> and ispLEVER<sup>®</sup> design software allows large complex designs to be efficiently implemented using the LatticeECP3 FPGA family. Synthesis library support for LatticeECP3 is available for popular logic synthesis tools. Diamond and ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP3 device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the LatticeECP3 family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

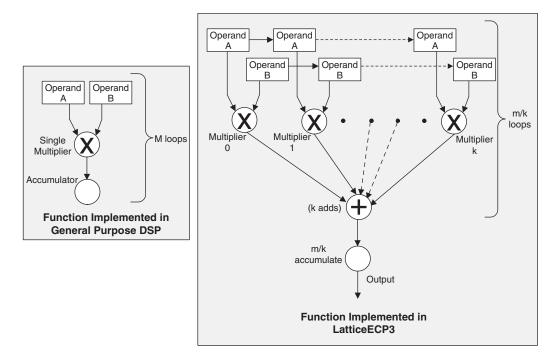

This allows designers to use highly parallel implementations of DSP functions. Designers can optimize DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2-23 compares the fully serial implementation to the mixed parallel and serial implementation.

#### Figure 2-23. Comparison of General DSP and LatticeECP3 Approaches

# LatticeECP3 sysDSP Slice Architecture Features

The LatticeECP3 sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The LatticeECP3 sysDSP Slice supports many functions that include the following:

- Multiply (one 18 x 36, two 18 x 18 or four 9 x 9 Multiplies per Slice)

- Multiply (36 x 36 by cascading across two sysDSP slices)

- Multiply Accumulate (up to 18 x 36 Multipliers feeding an Accumulator that can have up to 54-bit resolution)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18 x 18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- · Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such

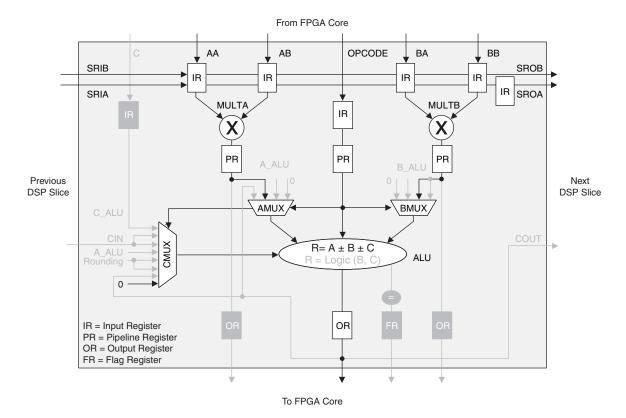

### **MULTADDSUB DSP Element**

In this case, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB. The user can enable the input, output and pipeline registers. Figure 2-29 shows the MULTADDSUB sysDSP element.

#### Figure 2-29. MULTADDSUB

| MCCLK (MHz)      | MCCLK (MHz)     |

|------------------|-----------------|

|                  | 10              |

| 2.5 <sup>1</sup> | 13              |

| 4.3              | 15 <sup>2</sup> |

| 5.4              | 20              |

| 6.9              | 26              |

| 8.1              | 33 <sup>3</sup> |

| 9.2              |                 |

Table 2-16. Selectable Master Clock (MCCLK) Frequencies During Configuration (Nominal)

1. Software default MCCLK frequency. Hardware default is 3.1 MHz.

2. Maximum MCCLK with encryption enabled.

3. Maximum MCCLK without encryption.

# **Density Shifting**

The LatticeECP3 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the LatticeECP3 Pin Migration Tables and Diamond software for specific restrictions and limitations.

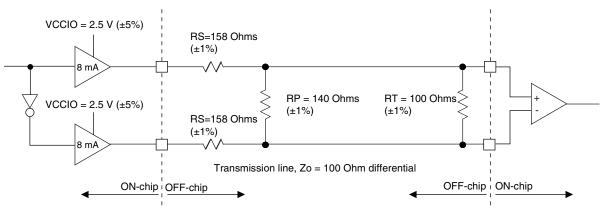

### LVDS25E

The top and bottom sides of LatticeECP3 devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3-1 is one possible solution for point-to-point signals.

#### Table 3-1. LVDS25E DC Conditions

| Parameter         | Description                      | Typical | Units |

|-------------------|----------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 20      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 158     | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 140     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.43    | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 1.07    | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.35    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.25    | V     |

| Z <sub>BACK</sub> | Back Impedance                   | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                | 6.03    | mA    |

### LVCMOS33D

All I/O banks support emulated differential I/O using the LVCMOS33D I/O type. This option, along with the external resistor network, provides the system designer the flexibility to place differential outputs on an I/O bank with 3.3 V V<sub>CCIO</sub>. The default drive current for LVCMOS33D output is 12 mA with the option to change the device strength to 4 mA, 8 mA, 16 mA or 20 mA. Follow the LVCMOS33 specifications for the DC characteristics of the LVCMOS33D.

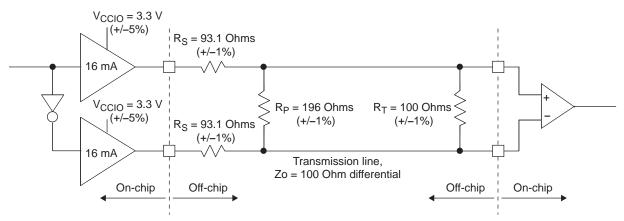

### LVPECL33

The LatticeECP3 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

#### Figure 3-3. Differential LVPECL33

#### Table 3-3. LVPECL33 DC Conditions<sup>1</sup>

| Parameter         | Description                      | Typical | Units |

|-------------------|----------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 3.30    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 93      | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 196     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 2.05    | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 1.25    | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.80    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.65    | V     |

| ZBACK             | Back Impedance                   | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                | 12.11   | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

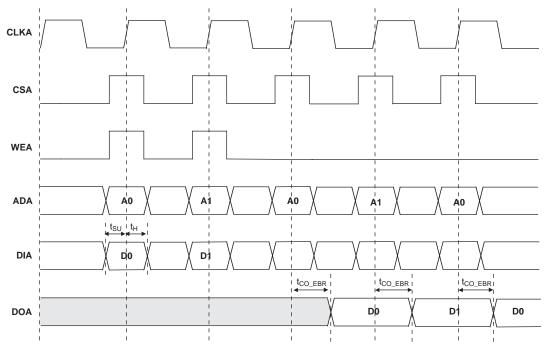

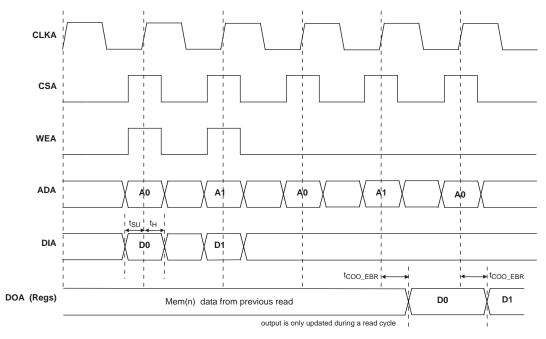

# **Timing Diagrams**

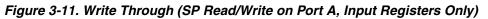

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

Figure 3-10. Read/Write Mode with Input and Output Registers

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5, 7</sup> (Continued)

| Buffer Type   | Description                                            | -8    | -7    | -6    | Units |

|---------------|--------------------------------------------------------|-------|-------|-------|-------|

| RSDS25        | RSDS, VCCIO = 2.5 V                                    | -0.07 | -0.04 | -0.01 | ns    |

| PPLVDS        | Point-to-Point LVDS, True LVDS, VCCIO = 2.5 V or 3.3 V | -0.22 | -0.19 | -0.16 | ns    |

| LVPECL33      | LVPECL, Emulated, VCCIO = 3.3 V                        | 0.67  | 0.76  | 0.86  | ns    |

| HSTL18_I      | HSTL_18 class I 8mA drive, VCCIO = 1.8 V               | 1.20  | 1.34  | 1.47  | ns    |

| HSTL18_II     | HSTL_18 class II, VCCIO = 1.8 V                        | 0.89  | 1.00  | 1.11  | ns    |

| HSTL18D_I     | Differential HSTL 18 class I 8 mA drive                | 1.20  | 1.34  | 1.47  | ns    |

| HSTL18D_II    | Differential HSTL 18 class II                          | 0.89  | 1.00  | 1.11  | ns    |

| HSTL15_I      | HSTL_15 class I 4 mA drive, VCCIO = 1.5 V              | 1.67  | 1.83  | 1.99  | ns    |

| HSTL15D_I     | Differential HSTL 15 class I 4 mA drive                | 1.67  | 1.83  | 1.99  | ns    |

| SSTL33_I      | SSTL_3 class I, VCCIO = 3.3 V                          | 1.12  | 1.17  | 1.21  | ns    |

| SSTL33_II     | SSTL_3 class II, VCCIO = 3.3 V                         | 1.08  | 1.12  | 1.15  | ns    |

| SSTL33D_I     | Differential SSTL_3 class I                            | 1.12  | 1.17  | 1.21  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II                           | 1.08  | 1.12  | 1.15  | ns    |

| SSTL25_I      | SSTL_2 class I 8 mA drive, VCCIO = 2.5 V               | 1.06  | 1.19  | 1.31  | ns    |

| SSTL25_II     | SSTL_2 class II 16 mA drive, VCCIO = 2.5 V             | 1.04  | 1.17  | 1.31  | ns    |

| SSTL25D_I     | Differential SSTL_2 class I 8 mA drive                 | 1.06  | 1.19  | 1.31  | ns    |

| SSTL25D_II    | Differential SSTL_2 class II 16 mA drive               | 1.04  | 1.17  | 1.31  | ns    |

| SSTL18_I      | SSTL_1.8 class I, VCCIO = 1.8 V                        | 0.70  | 0.84  | 0.97  | ns    |

| SSTL18_II     | SSTL_1.8 class II 8 mA drive, VCCIO = 1.8 V            | 0.70  | 0.84  | 0.97  | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I                          | 0.70  | 0.84  | 0.97  | ns    |

| SSTL18D_II    | Differential SSTL_1.8 class II 8 mA drive              | 0.70  | 0.84  | 0.97  | ns    |

| SSTL15        | SSTL_1.5, VCCIO = 1.5 V                                | 1.22  | 1.35  | 1.48  | ns    |

| SSTL15D       | Differential SSTL_15                                   | 1.22  | 1.35  | 1.48  | ns    |

| LVTTL33_4mA   | LVTTL 4 mA drive, VCCIO = 3.3V                         | 0.25  | 0.24  | 0.23  | ns    |

| LVTTL33_8mA   | LVTTL 8 mA drive, VCCIO = 3.3V                         | -0.06 | -0.06 | -0.07 | ns    |

| LVTTL33_12mA  | LVTTL 12 mA drive, VCCIO = 3.3V                        | -0.01 | -0.02 | -0.02 | ns    |

| LVTTL33_16mA  | LVTTL 16 mA drive, VCCIO = 3.3V                        | -0.07 | -0.07 | -0.08 | ns    |

| LVTTL33_20mA  | LVTTL 20 mA drive, VCCIO = 3.3V                        | -0.12 | -0.13 | -0.14 | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4 mA drive, fast slew rate                  | 0.25  | 0.24  | 0.23  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8 mA drive, fast slew rate                  | -0.06 | -0.06 | -0.07 | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12 mA drive, fast slew rate                 | -0.01 | -0.02 | -0.02 | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16 mA drive, fast slew rate                 | -0.07 | -0.07 | -0.08 | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20 mA drive, fast slew rate                 | -0.12 | -0.13 | -0.14 | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4 mA drive, fast slew rate                  | 0.12  | 0.10  | 0.09  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8 mA drive, fast slew rate                  | -0.05 | -0.06 | -0.07 | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12 mA drive, fast slew rate                 | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16 mA drive, fast slew rate                 | -0.12 | -0.13 | -0.14 | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20 mA drive, fast slew rate                 | -0.12 | -0.13 | -0.14 | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4 mA drive, fast slew rate                  | 0.11  | 0.12  | 0.14  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8 mA drive, fast slew rate                  | 0.11  | 0.12  | 0.14  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12 mA drive, fast slew rate                 | -0.04 | -0.03 | -0.03 | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16 mA drive, fast slew rate                 | -0.04 | -0.03 | -0.03 | ns    |

### **Over Recommended Commercial Operating Conditions**

# LatticeECP3 Maximum I/O Buffer Speed <sup>1, 2, 3, 4, 5, 6</sup>

### **Over Recommended Operating Conditions**

| Buffer                                | Description                                    | Max. | Units |

|---------------------------------------|------------------------------------------------|------|-------|

| Maximum Input Frequency               |                                                |      |       |

| LVDS25                                | LVDS, $V_{CCIO} = 2.5 V$                       | 400  | MHz   |

| MLVDS25                               | MLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V     | 400  | MHz   |

| BLVDS25                               | BLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V     | 400  | MHz   |

| PPLVDS                                | Point-to-Point LVDS                            | 400  | MHz   |

| TRLVDS                                | Transition-Reduced LVDS                        | 612  | MHz   |

| Mini LVDS                             | Mini LVDS                                      | 400  | MHz   |

| LVPECL33                              | LVPECL, Emulated, V <sub>CCIO</sub> = 3.3 V    | 400  | MHz   |

| HSTL18 (all supported classes)        | HSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V | 400  | MHz   |

| HSTL15                                | HSTL_15 class I, V <sub>CCIO</sub> = 1.5 V     | 400  | MHz   |

| SSTL33 (all supported classes)        | SSTL_3 class I, II, V <sub>CCIO</sub> = 3.3 V  | 400  | MHz   |

| SSTL25 (all supported classes)        | SSTL_2 class I, II, V <sub>CCIO</sub> = 2.5 V  | 400  | MHz   |

| SSTL18 (all supported classes)        | SSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V | 400  | MHz   |

| LVTTL33                               | LVTTL, V <sub>CCIO</sub> = 3.3 V               | 166  | MHz   |

| LVCMOS33                              | LVCMOS, V <sub>CCIO</sub> = 3.3 V              | 166  | MHz   |

| LVCMOS25                              | LVCMOS, V <sub>CCIO</sub> = 2.5 V              | 166  | MHz   |

| LVCMOS18                              | LVCMOS, V <sub>CCIO</sub> = 1.8 V              | 166  | MHz   |

| LVCMOS15                              | LVCMOS 1.5, V <sub>CCIO</sub> = 1.5 V          | 166  | MHz   |

| LVCMOS12                              | LVCMOS 1.2, V <sub>CCIO</sub> = 1.2 V          | 166  | MHz   |

| PCI33                                 | PCI, V <sub>CCIO</sub> = 3.3 V                 | 66   | MHz   |

| Maximum Output Frequency              |                                                |      |       |

| LVDS25E                               | LVDS, Emulated, V <sub>CCIO</sub> = 2.5 V      | 300  | MHz   |

| LVDS25                                | LVDS, $V_{CCIO} = 2.5 V$                       | 612  | MHz   |

| MLVDS25                               | MLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V     | 300  | MHz   |

| RSDS25                                | RSDS, Emulated, V <sub>CCIO</sub> = 2.5 V      | 612  | MHz   |

| BLVDS25                               | BLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V     | 300  | MHz   |

| PPLVDS                                | Point-to-point LVDS                            | 612  | MHz   |

| LVPECL33                              | LVPECL, Emulated, V <sub>CCIO</sub> = 3.3 V    | 612  | MHz   |

| Mini-LVDS                             | Mini LVDS                                      | 612  | MHz   |

| HSTL18 (all supported classes)        | HSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V | 200  | MHz   |

| HSTL15 (all supported classes)        | HSTL_15 class I, V <sub>CCIO</sub> = 1.5 V     | 200  | MHz   |

| SSTL33 (all supported classes)        | SSTL_3 class I, II, V <sub>CCIO</sub> = 3.3 V  | 233  | MHz   |

| SSTL25 (all supported classes)        | SSTL_2 class I, II, V <sub>CCIO</sub> = 2.5 V  | 233  | MHz   |

| SSTL18 (all supported classes)        | SSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V | 266  | MHz   |

| LVTTL33                               | LVTTL, V <sub>CCIO</sub> = 3.3 V               | 166  | MHz   |

| LVCMOS33 (For all drives)             | LVCMOS, 3.3 V                                  | 166  | MHz   |

| LVCMOS25 (For all drives)             | LVCMOS, 2.5 V                                  | 166  | MHz   |

| LVCMOS18 (For all drives)             | LVCMOS, 1.8 V                                  | 166  | MHz   |

| LVCMOS15 (For all drives)             | LVCMOS, 1.5 V                                  | 166  | MHz   |

| LVCMOS12 (For all drives except 2 mA) | LVCMOS, V <sub>CCIO</sub> = 1.2 V              | 166  | MHz   |

| LVCMOS12 (2 mA drive)                 | LVCMOS, V <sub>CCIO</sub> = 1.2 V              | 100  | MHz   |

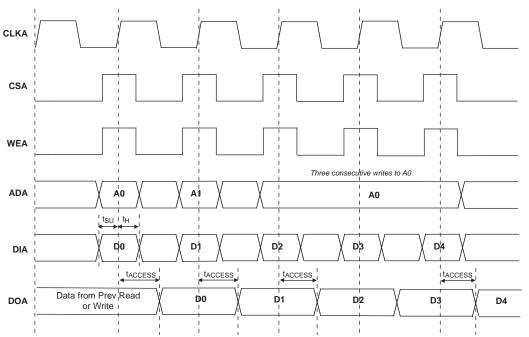

# SERDES/PCS Block Latency

Table 3-8 describes the latency of each functional block in the transmitter and receiver. Latency is given in parallel clock cycles. Figure 3-12 shows the location of each block.

Table 3-8. SERDES/PCS Latency Breakdown

| Item    | Description                                          | Min. | Avg. | Max. | Fixed         | Bypass | Units    |

|---------|------------------------------------------------------|------|------|------|---------------|--------|----------|

| Transmi | it Data Latency <sup>1</sup>                         |      |      |      |               |        | 1        |

|         | FPGA Bridge - Gearing disabled with different clocks | 1    | 3    | 5    | —             | 1      | word clk |

| T1      | FPGA Bridge - Gearing disabled with same clocks      | _    |      |      | 3             | 1      | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1    | 3    | 5    | —             | —      | word clk |

| T2      | 8b10b Encoder                                        | _    |      |      | 2             | 1      | word clk |

| Т3      | SERDES Bridge transmit                               | _    |      |      | 2             | 1      | word clk |

| Т4      | Serializer: 8-bit mode                               | _    |      |      | 15 + Δ1       | —      | UI + ps  |

| 14      | Serializer: 10-bit mode                              |      |      |      | 18 + ∆1       | —      | UI + ps  |

| T5      | Pre-emphasis ON                                      | _    |      |      | <b>1</b> + ∆2 | —      | UI + ps  |

| 15      | Pre-emphasis OFF                                     |      |      |      | 0 + ∆3        | —      | UI + ps  |

| Receive | Data Latency <sup>2</sup>                            |      |      |      | •             | •      |          |

| R1      | Equalization ON                                      | _    |      |      | Δ1            | —      | UI + ps  |

| ΠI      | Equalization OFF                                     |      |      |      | Δ2            | —      | UI + ps  |

| R2      | Deserializer: 8-bit mode                             |      |      |      | 10 + ∆3       | —      | UI + ps  |

| ΠZ      | Deserializer: 10-bit mode                            |      |      |      | 12 + ∆3       | —      | UI + ps  |

| R3      | SERDES Bridge receive                                | _    | —    | —    | 2             | —      | word clk |

| R4      | Word alignment                                       | 3.1  |      | 4    | —             | —      | word clk |

| R5      | 8b10b decoder                                        |      |      |      | 1             | —      | word clk |

| R6      | Clock Tolerance Compensation                         | 7    | 15   | 23   | 1             | 1      | word clk |

|         | FPGA Bridge - Gearing disabled with different clocks | 1    | 3    | 5    | —             | 1      | word clk |

| R7      | FPGA Bridge - Gearing disabled with same clocks      | —    | —    | —    | 3             | 1      | word clk |

|         | FPGA Bridge - Gearing enabled                        | 1    | 3    | 5    | —             | —      | word clk |

1.  $\Delta 1 = -245 \text{ ps}, \Delta 2 = +88 \text{ ps}, \Delta 3 = +112 \text{ ps}.$

2.  $\Delta 1 = +118 \text{ ps}, \Delta 2 = +132 \text{ ps}, \Delta 3 = +700 \text{ ps}.$

# **SERDES High Speed Data Receiver**

#### Table 3-9. Serial Input Data Specifications

| Symbol                 | Description                                                  |         | Min. | Тур.      | Max.                               | Units   |

|------------------------|--------------------------------------------------------------|---------|------|-----------|------------------------------------|---------|

|                        |                                                              | 3.125 G | —    | _         | 136                                |         |

|                        |                                                              | 2.5 G   | —    | _         | 144                                |         |

| RX-CID <sub>S</sub>    | Stream of nontransitions <sup>1</sup>                        | 1.485 G | —    | _         | 160                                | Bits    |

| HA-CIDS                | (CID = Consecutive Identical Digits) @ 10 <sup>-12</sup> BER | 622 M   | —    | _         | 204                                | Dits    |

|                        |                                                              | 270 M   | —    | _         | 228                                |         |

|                        |                                                              | 150 M   | —    |           | 296                                |         |

| V <sub>RX-DIFF-S</sub> | Differential input sensitivity                               |         | 150  | _         | 1760                               | mV, p-p |

| V <sub>RX-IN</sub>     | Input levels                                                 |         | 0    | _         | V <sub>CCA</sub> +0.5 <sup>4</sup> | V       |

| V <sub>RX-CM-DC</sub>  | Input common mode range (DC coupled)                         |         | 0.6  | _         | V <sub>CCA</sub>                   | V       |

| V <sub>RX-CM-AC</sub>  | Input common mode range (AC coupled) <sup>3</sup>            |         | 0.1  | _         | V <sub>CCA</sub> +0.2              | V       |

| T <sub>RX-RELOCK</sub> | SCDR re-lock time <sup>2</sup>                               |         | —    | 1000      | —                                  | Bits    |

| Z <sub>RX-TERM</sub>   | Input termination 50/75 Ohm/High Z                           |         | -20% | 50/75/HiZ | +20%                               | Ohms    |

| RL <sub>RX-RL</sub>    | Return loss (without package)                                |         | 10   | _         | —                                  | dB      |

1. This is the number of bits allowed without a transition on the incoming data stream when using DC coupling.

2. This is the typical number of bit times to re-lock to a new phase or frequency within +/- 300 ppm, assuming 8b10b encoded data.

3. AC coupling is used to interface to LVPECL and LVDS. LVDS interfaces are found in laser drivers and Fibre Channel equipment. LVDS interfaces are generally found in 622 Mbps SERDES devices.

4. Up to 1.76 V.

### Input Data Jitter Tolerance

A receiver's ability to tolerate incoming signal jitter is very dependent on jitter type. High speed serial interface standards have recognized the dependency on jitter type and have specifications to indicate tolerance levels for different jitter types as they relate to specific protocols. Sinusoidal jitter is considered to be a worst case jitter type.

| Description   | Frequency  | Condition               | Min. | Тур. | Max. | Units   |

|---------------|------------|-------------------------|------|------|------|---------|

| Deterministic |            | 600 mV differential eye | —    | —    | 0.47 | UI, p-p |

| Random        | 3.125 Gbps | 600 mV differential eye | —    | —    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | —    | —    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | —    | —    | 0.47 | UI, p-p |

| Random        | 2.5 Gbps   | 600 mV differential eye | —    | —    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | —    | —    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | —    | —    | 0.47 | UI, p-p |

| Random        | 1.25 Gbps  | 600 mV differential eye | —    | —    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | —    | —    | 0.65 | UI, p-p |

| Deterministic |            | 600 mV differential eye | —    | —    | 0.47 | UI, p-p |

| Random        | 622 Mbps   | 600 mV differential eye | —    | —    | 0.18 | UI, p-p |

| Total         |            | 600 mV differential eye | —    | —    | 0.65 | UI, p-p |

Table 3-10. Receiver Total Jitter Tolerance Specification

Note: Values are measured with CJPAT, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal, room temperature.

# **PCI Express Electrical and Timing Characteristics**

# AC and DC Characteristics

| Symbol                                   | Description                                                                           | <b>Test Conditions</b>                                 | Min               | Тур  | Max                    | Units |

|------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------|------|------------------------|-------|

| Transmit <sup>1</sup>                    |                                                                                       | •                                                      |                   |      |                        |       |

| UI                                       | Unit interval                                                                         |                                                        | 399.88            | 400  | 400.12                 | ps    |

| V <sub>TX-DIFF_P-P</sub>                 | Differential peak-to-peak output voltage                                              |                                                        | 0.8               | 1.0  | 1.2                    | V     |

| V <sub>TX-DE-RATIO</sub>                 | De-emphasis differential output voltage ratio                                         |                                                        | -3                | -3.5 | -4                     | dB    |

| V <sub>TX-CM-AC_P</sub>                  | RMS AC peak common-mode output voltage                                                |                                                        | —                 | _    | 20                     | mV    |

| V <sub>TX-RCV-DETECT</sub>               | Amount of voltage change allowed dur-<br>ing receiver detection                       |                                                        | _                 | _    | 600                    | mV    |

| V <sub>TX-DC-CM</sub>                    | Tx DC common mode voltage                                                             |                                                        | 0                 |      | V <sub>CCOB</sub> + 5% | V     |

| I <sub>TX-SHORT</sub>                    | Output short circuit current                                                          | V <sub>TX-D+</sub> =0.0 V<br>V <sub>TX-D-</sub> =0.0 V | —                 | _    | 90                     | mA    |

| Z <sub>TX-DIFF-DC</sub>                  | Differential output impedance                                                         |                                                        | 80                | 100  | 120                    | Ohms  |

| RL <sub>TX-DIFF</sub>                    | Differential return loss                                                              |                                                        | 10                | _    | —                      | dB    |

| RL <sub>TX-CM</sub>                      | Common mode return loss                                                               |                                                        | 6.0               | _    | —                      | dB    |

| T <sub>TX-RISE</sub>                     | Tx output rise time                                                                   | 20 to 80%                                              | 0.125             | _    | —                      | UI    |

| T <sub>TX-FALL</sub>                     | Tx output fall time                                                                   | 20 to 80%                                              | 0.125             | _    | —                      | UI    |

| L <sub>TX-SKEW</sub>                     | Lane-to-lane static output skew for all lanes in port/link                            |                                                        | _                 | _    | 1.3                    | ns    |

| T <sub>TX-EYE</sub>                      | Transmitter eye width                                                                 |                                                        | 0.75              | _    | —                      | UI    |

| T <sub>TX-EYE-MEDIAN-TO-MAX-JITTER</sub> | Maximum time between jitter median and maximum deviation from median                  |                                                        | _                 | _    | 0.125                  | UI    |

| Receive <sup>1, 2</sup>                  |                                                                                       | •                                                      |                   |      |                        |       |

| UI                                       | Unit Interval                                                                         |                                                        | 399.88            | 400  | 400.12                 | ps    |

| V <sub>RX-DIFF_P-P</sub>                 | Differential peak-to-peak input voltage                                               |                                                        | 0.34 <sup>3</sup> | —    | 1.2                    | V     |

| V <sub>RX-IDLE-DET-DIFF_P-P</sub>        | Idle detect threshold voltage                                                         |                                                        | 65                | —    | 340 <sup>3</sup>       | mV    |

| V <sub>RX-CM-AC_P</sub>                  | Receiver common mode voltage for AC coupling                                          |                                                        | —                 | _    | 150                    | mV    |

| Z <sub>RX-DIFF-DC</sub>                  | DC differential input impedance                                                       |                                                        | 80                | 100  | 120                    | Ohms  |

| Z <sub>RX-DC</sub>                       | DC input impedance                                                                    |                                                        | 40                | 50   | 60                     | Ohms  |

| Z <sub>RX-HIGH-IMP-DC</sub>              | Power-down DC input impedance                                                         |                                                        | 200K              | _    | —                      | Ohms  |

| RL <sub>RX-DIFF</sub>                    | Differential return loss                                                              |                                                        | 10                | —    | —                      | dB    |

| RL <sub>RX-CM</sub>                      | Common mode return loss                                                               |                                                        | 6.0               | —    | —                      | dB    |

| T <sub>RX-IDLE-DET-DIFF-ENTERTIME</sub>  | Maximum time required for receiver to recognize and signal an unexpected idle on link |                                                        | _                 |      | _                      | ms    |

1. Values are measured at 2.5 Gbps.

2. Measured with external AC-coupling on the receiver.

3.Not in compliance with PCI Express 1.1 standard.

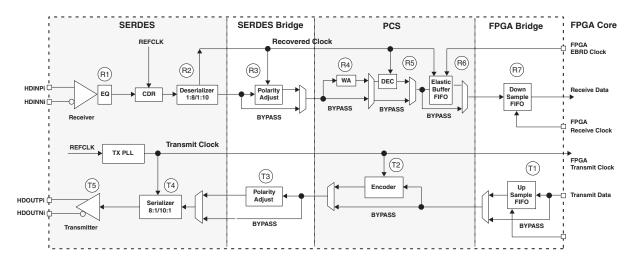

### Figure 3-18. XAUI Sinusoidal Jitter Tolerance Mask

Note: The sinusoidal jitter tolerance is measured with at least 0.37 UIpp of Deterministic jitter (Dj) and the sum of Dj and Rj (random jitter) is at least 0.55 UIpp. Therefore, the sum of Dj, Rj and Sj (sinusoidal jitter) is at least 0.65 UIpp (Dj = 0.37, Rj = 0.18, Sj = 0.1).

# LatticeECP3 sysCONFIG Port Timing Specifications (Continued)

**Over Recommended Operating Conditions**

| Parameter         | Description                              | Min. | Max. | Units |

|-------------------|------------------------------------------|------|------|-------|

| t <sub>SSCL</sub> | CCLK Minimum Low Pulse                   | 5    | _    | ns    |

| t <sub>HLCH</sub> | HOLDN Low Setup Time (Relative to CCLK)  | 5    | _    | ns    |

| t <sub>CHHH</sub> | HOLDN Low Hold Time (Relative to CCLK)   | 5    | _    | ns    |

| Master and        | Slave SPI (Continued)                    |      |      |       |

| t <sub>CHHL</sub> | HOLDN High Hold Time (Relative to CCLK)  | 5    | _    | ns    |

| t <sub>HHCH</sub> | HOLDN High Setup Time (Relative to CCLK) | 5    | _    | ns    |

| t <sub>HLQZ</sub> | HOLDN to Output High-Z                   | —    | 9    | ns    |

| t <sub>HHQX</sub> | HOLDN to Output Low-Z                    | —    | 9    | ns    |

1. Re-toggling the PROGRAMN pin is not permitted until the INITN pin is high. Avoid consecutive toggling of the PROGRAMN.

| Parameter              | Min.                 | Max.                 | Units |  |

|------------------------|----------------------|----------------------|-------|--|

| Master Clock Frequency | Selected value - 15% | Selected value + 15% | MHz   |  |

| Duty Cycle             | 40                   | 60                   | %     |  |

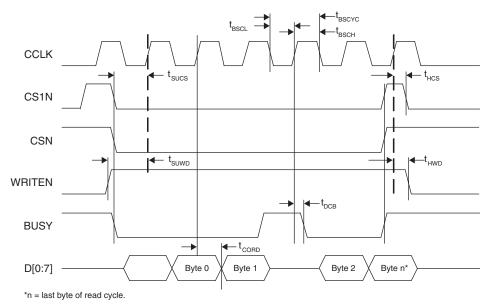

#### Figure 3-20. sysCONFIG Parallel Port Read Cycle

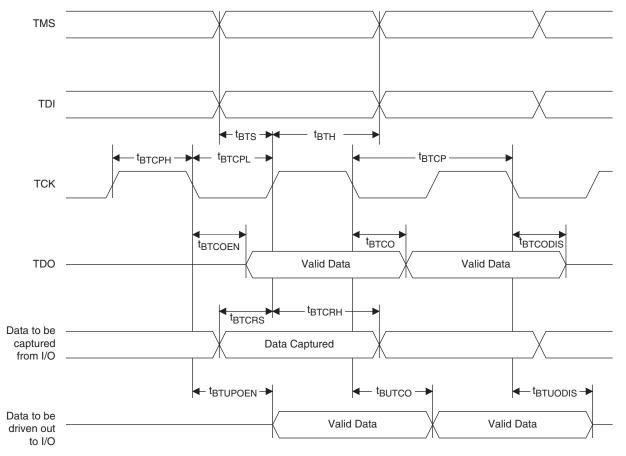

# **JTAG Port Timing Specifications**

#### **Over Recommended Operating Conditions**

| Symbol               | Parameter                                                          | Min | Max | Units |

|----------------------|--------------------------------------------------------------------|-----|-----|-------|

| f <sub>MAX</sub>     | TCK clock frequency                                                |     | 25  | MHz   |

| t <sub>BTCP</sub>    | TCK [BSCAN] clock pulse width                                      | 40  | —   | ns    |

| t <sub>BTCPH</sub>   | TCK [BSCAN] clock pulse width high                                 | 20  | —   | ns    |

| t <sub>BTCPL</sub>   | TCK [BSCAN] clock pulse width low                                  | 20  | —   | ns    |

| t <sub>BTS</sub>     | TCK [BSCAN] setup time                                             | 10  |     | ns    |

| t <sub>BTH</sub>     | TCK [BSCAN] hold time                                              | 8   | —   | ns    |

| t <sub>BTRF</sub>    | TCK [BSCAN] rise/fall time                                         | 50  | —   | mV/ns |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to valid output               | —   | 10  | ns    |

| t <sub>BTCODIS</sub> | TAP controller falling edge of clock to valid disable              | —   | 10  | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to valid enable               | —   | 10  | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                             | 8   | —   | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                              | 25  | —   | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to valid output  | —   | 25  | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to valid disable | —   | 25  | ns    |

| t <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  | —   | 25  | ns    |

### Figure 3-32. JTAG Port Timing Waveforms

# Signal Descriptions (Cont.)

| Signal Name                            | I/O      | Description                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [LOC]DQS[num]                          | I/O      | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQS, num = ball function number.                                                                                                                                                                                                                                                                         |

| [LOC]DQ[num]                           | I/O      | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQ, associated DQS number.                                                                                                                                                                                                                                                                               |

| Test and Programming (Dedicated        | l Pins)  |                                                                                                                                                                                                                                                                                                                                                                          |

| TMS                                    | I        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                                                                                                                               |

| тск                                    | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                                                                                                                        |

| TDI                                    | I        | Test Data in pin. Used to load data into device using 1149.1 state machine.<br>After power-up, this TAP port can be activated for configuration by sending<br>appropriate command. (Note: once a configuration port is selected it is<br>locked. Another configuration port cannot be selected until the power-up<br>sequence). Pull-up is enabled during configuration. |

| TDO                                    | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.                                                                                                                                                                                                                                                                                           |

| VCCJ                                   | —        | Power supply pin for JTAG Test Access Port.                                                                                                                                                                                                                                                                                                                              |

| <b>Configuration Pads (Used During</b> | sysCONFI | Ġ)                                                                                                                                                                                                                                                                                                                                                                       |

| CFG[2:0]                               | I        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled. These are dedicated pins.                                                                                                                                                                                                               |

| INITN                                  | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled. It is a dedicated pin.                                                                                                                                                                                                                                         |

| PROGRAMN                               | I        | Initiates configuration sequence when asserted low. This pin always has an active pull-up. It is a dedicated pin.                                                                                                                                                                                                                                                        |

| DONE                                   | I/O      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress. It is a dedicated pin.                                                                                                                                                                                                                                   |

| CCLK                                   | I        | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. It is a dedicated pin.                                                                                                                                                                                                                                                            |

| MCLK                                   | I/O      | Output Configuration Clock for configuring an FPGA in SPI, SPIm, and Master configuration modes.                                                                                                                                                                                                                                                                         |

| BUSY/SISPI                             | 0        | Parallel configuration mode busy indicator. SPI/SPIm mode data output.                                                                                                                                                                                                                                                                                                   |

| CSN/SN/OEN                             | I/O      | Parallel configuration mode active-low chip select. Slave SPI chip select.<br>Parallel burst Flash output enable.                                                                                                                                                                                                                                                        |

| CS1N/HOLDN/RDY                         | I        | Parallel configuration mode active-low chip select. Slave SPI hold input.                                                                                                                                                                                                                                                                                                |

| WRITEN                                 | I        | Write enable for parallel configuration modes.                                                                                                                                                                                                                                                                                                                           |

| DOUT/CSON/CSSPI1N                      | 0        | Serial data output. Chip select output. SPI/SPIm mode chip select.                                                                                                                                                                                                                                                                                                       |

|                                        |          | sysCONFIG Port Data I/O for Parallel mode. Open drain during configuration.                                                                                                                                                                                                                                                                                              |

| D[0]/SPIFASTN                          | I/O      | sysCONFIG Port Data I/O for SPI or SPIm. When using the SPI or SPIm mode, this pin should either be tied high or low, must not be left floating. Open drain during configuration.                                                                                                                                                                                        |

| D1                                     | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D2                                     | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D3/SI                                  | I/O      | Parallel configuration I/O. Slave SPI data input. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                  |

| D4/SO                                  | I/O      | Parallel configuration I/O. Slave SPI data output. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                 |

| D5                                     | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D6/SPID1                               | I/O      | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                   |

# LatticeECP3 Family Data Sheet Supplemental Information

#### February 2014

#### Data Sheet DS1021

### **For Further Information**

A variety of technical notes for the LatticeECP3 family are available on the Lattice website at <u>www.latticesemi.com</u>.

- TN1169, LatticeECP3 sysCONFIG Usage Guide

- TN1176, LatticeECP3 SERDES/PCS Usage Guide

- TN1177, LatticeECP3 sysIO Usage Guide

- TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide

- TN1179, LatticeECP3 Memory Usage Guide

- TN1180, LatticeECP3 High-Speed I/O Interface

- TN1181, Power Consumption and Management for LatticeECP3 Devices

- TN1182, LatticeECP3 sysDSP Usage Guide

- TN1184, LatticeECP3 Soft Error Detection (SED) Usage Guide

- TN1189, LatticeECP3 Hardware Checklist

- TN1215, LatticeECP2MS and LatticeECP2S Devices

- TN1216, LatticeECP2/M and LatticeECP3 Dual Boot Feature Advanced Security Encryption Key Programming Guide for LatticeECP3

- TN1222, LatticeECP3 Slave SPI Port User's Guide

For further information on interface standards refer to the following websites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: www.pcisig.com

© 2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Date          | Version                             | Section                                                                                                                                                                                                                                                                                   | Change Summary                                                                                                                                         |

|---------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                     |                                                                                                                                                                                                                                                                                           | LatticeECP3 Maximum I/O Buffer Speed table – Description column, references to VCCIO = 3.0V changed to 3.3V.                                           |

|               |                                     |                                                                                                                                                                                                                                                                                           | Updated SERDES External Reference Clock Waveforms.                                                                                                     |

|               |                                     |                                                                                                                                                                                                                                                                                           | Transmitter and Receiver Latency Block Diagram – Updated sections of the diagram to match descriptions on the SERDES/PCS Latency Break-<br>down table. |

|               |                                     | Pinout Information                                                                                                                                                                                                                                                                        | "Logic Signal Connections" section heading renamed "Package Pinout<br>Information". Software menu selections within this section have been<br>updated. |

|               |                                     |                                                                                                                                                                                                                                                                                           | Signal Descriptions table – Updated description for V <sub>CCA</sub> signal.                                                                           |

| April 2012    | 02.2EA                              | Architecture                                                                                                                                                                                                                                                                              | Updated first paragraph of Output Register Block section.                                                                                              |

|               |                                     |                                                                                                                                                                                                                                                                                           | Updated the information about sysIO buffer pairs below Figure 2-38.                                                                                    |

|               |                                     |                                                                                                                                                                                                                                                                                           | Updated the information relating to migration between devices in the Density Shifting section.                                                         |

|               |                                     | DC and Switching<br>Characteristics                                                                                                                                                                                                                                                       | Corrected the Definitions in the sysCLOCK PLL Timing table for $\ensuremath{t_{RST}}$                                                                  |

|               |                                     | Ordering Information                                                                                                                                                                                                                                                                      | Updated topside marks with new logos in the Ordering Information sec-<br>tion.                                                                         |

| February 2012 | 02.1EA                              | All                                                                                                                                                                                                                                                                                       | Updated document with new corporate logo.                                                                                                              |

| November 2011 | 02.0EA                              | Introduction                                                                                                                                                                                                                                                                              | Added information for LatticeECP3-17EA, 328-ball csBGA package.                                                                                        |

|               | Architecture                        | Added information for LatticeECP3-17EA, 328-ball csBGA package.                                                                                                                                                                                                                           |                                                                                                                                                        |

|               | DC and Switching<br>Characteristics | Updated LatticeECP3 Supply Current table power numbers.                                                                                                                                                                                                                                   |                                                                                                                                                        |

|               |                                     | Typical Building Block Function Performance table, LatticeECP3 Exter-<br>nal Switching Characteristics table, LatticeECP3 Internal Switching<br>Characteristics table and LatticeECP3 Family Timing Adders: Added<br>speed grade -9 and updated speed grade -8, -7 and -6 timing numbers. |                                                                                                                                                        |

|               |                                     | Pinout Information                                                                                                                                                                                                                                                                        | Added information for LatticeECP3-17EA, 328-ball csBGA package.                                                                                        |

|               |                                     | Ordering Information                                                                                                                                                                                                                                                                      | Added information for LatticeECP3-17EA, 328-ball csBGA package.                                                                                        |

|               |                                     |                                                                                                                                                                                                                                                                                           | Added ordering information for low power devices and -9 speed grade devices.                                                                           |

| July 2011     | 01.9EA                              | DC and Switching<br>Characteristics                                                                                                                                                                                                                                                       | Removed ESD Performance table and added reference to LatticeECP3<br>Product Family Qualification Summary document.                                     |

|               |                                     |                                                                                                                                                                                                                                                                                           | sysCLOCK PLL TIming table, added footnote 4.                                                                                                           |

|               |                                     |                                                                                                                                                                                                                                                                                           | External Reference Clock Specification table – removed reference to<br>VREF-CM-AC and removed footnote for VREF-CM-AC.                                 |

|               |                                     | Pinout Information                                                                                                                                                                                                                                                                        | Pin Information Summary table: Corrected VCCIO Bank8 data for LatticeECP3-17EA 256-ball ftBGA package and LatticeECP-35EA 256-ball ftBGA package.      |

| April 2011    | 01.8EA                              | Architecture                                                                                                                                                                                                                                                                              | Updated Secondary Clock/Control Sources text section.                                                                                                  |

|               |                                     | DC and Switching<br>Characteristics                                                                                                                                                                                                                                                       | Added data for 150 Mbps to SERDES Power Supply Requirements table.                                                                                     |

|               |                                     |                                                                                                                                                                                                                                                                                           | Updated Frequencies in Table 3-6 Serial Output Timing and Levels                                                                                       |

|               |                                     |                                                                                                                                                                                                                                                                                           | Added Data for 150 Mbps to Table 3-7 Channel Output Jitter                                                                                             |

|               |                                     |                                                                                                                                                                                                                                                                                           | Corrected External Switching Characteristics table, Description for DDR3 Clock Timing, $t_{JIT}$ .                                                     |

|               |                                     |                                                                                                                                                                                                                                                                                           | Corrected Internal Switching Characteristics table, Description for EBR Timing, t <sub>SUWREN_EBR</sub> and t <sub>HWREN_EBR</sub> .                   |

|               |                                     |                                                                                                                                                                                                                                                                                           | Added footnote 1 to sysConfig Port Timing Specifications table.                                                                                        |

|               |                                     |                                                                                                                                                                                                                                                                                           | Updated description for RX-CIDs to 150M in Table 3-9 Serial Input Data Specifications                                                                  |

| Date                | Version | Section                                                                                                       | Change Summary                                                                                                                                                              |

|---------------------|---------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2009 01.4 | 01.4    | Architecture                                                                                                  | Corrected link in sysMEM Memory Block section.                                                                                                                              |

|                     |         |                                                                                                               | Updated information for On-Chip Programmable Termination and modi-<br>fied corresponding figure.                                                                            |

|                     |         | Added footnote 2 to On-Chip Programmable Termination Options for Input Modes table.                           |                                                                                                                                                                             |

|                     |         | Corrected Per Quadrant Primary Clock Selection figure.                                                        |                                                                                                                                                                             |

|                     |         | DC and Switching<br>Characteristics                                                                           | Modified -8 Timing data for 1024x18 True-Dual Port RAM (Read-Before-<br>Write, EBR Output Registers)                                                                        |

|                     |         |                                                                                                               | Added ESD Performance table.                                                                                                                                                |

|                     |         |                                                                                                               | LatticeECP3 External Switching Characteristics table - updated data for<br>t <sub>DIBGDDR</sub> , t <sub>W_PRI</sub> , t <sub>W_EDGE</sub> and t <sub>SKEW_EDGE_DQS</sub> . |

|                     |         | LatticeECP3 Internal Switching Characteristics table - updated data for $t_{COO\ PIO}$ and added footnote #4. |                                                                                                                                                                             |

|                     |         |                                                                                                               | sysCLOCK PLL Timing table - updated data for f <sub>OUT</sub> .                                                                                                             |

|                     |         |                                                                                                               | External Reference Clock Specification (refclkp/refclkn) table - updated data for $V_{REF\text{-}IN\text{-}SE}$ and $V_{REF\text{-}IN\text{-}DIFF}$                         |

|                     |         |                                                                                                               | LatticeECP3 sysCONFIG Port Timing Specifications table - updated data for t <sub>MWC</sub> .                                                                                |

|                     |         |                                                                                                               | Added TRLVDS DC Specification table and diagram.                                                                                                                            |

|                     |         |                                                                                                               | Updated Mini LVDS table.                                                                                                                                                    |

| August 2009         | 01.3    | DC and Switching<br>Characteristics                                                                           | Corrected truncated numbers for $V_{CCIB}$ and $V_{CCOB}$ in Recommended Operating Conditions table.                                                                        |

| July 2009 01.2      | 01.2    | Multiple                                                                                                      | Changed references of "multi-boot" to "dual-boot" throughout the data sheet.                                                                                                |

|                     |         | Architecture                                                                                                  | Updated On-Chip Programmable Termination bullets.                                                                                                                           |