## E. Lattice Semiconductor Corporation - LFE3-70EA-7LFN484C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 8375                                                                          |

| Number of Logic Elements/Cells | 67000                                                                         |

| Total RAM Bits                 | 4526080                                                                       |

| Number of I/O                  | 295                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 484-BBGA                                                                      |

| Supplier Device Package        | 484-FPBGA (23x23)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70ea-7lfn484c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

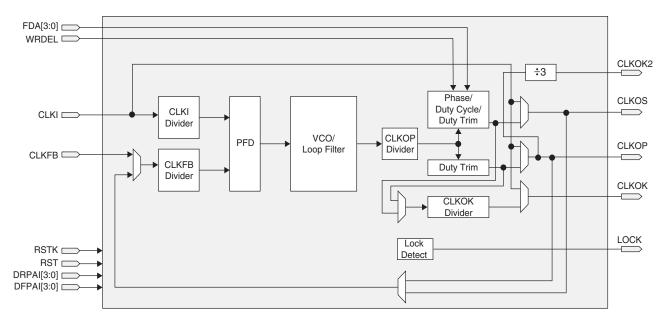

Figure 2-4. General Purpose PLL Diagram

Table 2-4 provides a description of the signals in the PLL blocks.

Table 2-4. PLL Blocks Signal Descriptions

| Signal     | I/O | Description                                                               |

|------------|-----|---------------------------------------------------------------------------|

| CLKI       | I   | Clock input from external pin or routing                                  |

| CLKFB      | I   | PLL feedback input from CLKOP, CLKOS, or from a user clock (pin or logic) |

| RST        | I   | "1" to reset PLL counters, VCO, charge pumps and M-dividers               |

| RSTK       | I   | "1" to reset K-divider                                                    |

| WRDEL      | I   | DPA Fine Delay Adjust input                                               |

| CLKOS      | 0   | PLL output to clock tree (phase shifted/duty cycle changed)               |

| CLKOP      | 0   | PLL output to clock tree (no phase shift)                                 |

| CLKOK      | 0   | PLL output to clock tree through secondary clock divider                  |

| CLKOK2     | 0   | PLL output to clock tree (CLKOP divided by 3)                             |

| LOCK       | 0   | "1" indicates PLL LOCK to CLKI                                            |

| FDA [3:0]  | I   | Dynamic fine delay adjustment on CLKOS output                             |

| DRPAI[3:0] | I   | Dynamic coarse phase shift, rising edge setting                           |

| DFPAI[3:0] | I   | Dynamic coarse phase shift, falling edge setting                          |

### Delay Locked Loops (DLL)

In addition to PLLs, the LatticeECP3 family of devices has two DLLs per device.

CLKI is the input frequency (generated either from the pin or routing) for the DLL. CLKI feeds into the output muxes block to bypass the DLL, directly to the DELAY CHAIN block and (directly or through divider circuit) to the reference input of the Phase Detector (PD) input mux. The reference signal for the PD can also be generated from the Delay Chain signals. The feedback input to the PD is generated from the CLKFB pin or from a tapped signal from the Delay chain.

The PD produces a binary number proportional to the phase and frequency difference between the reference and feedback signals. Based on these inputs, the ALU determines the correct digital control codes to send to the delay

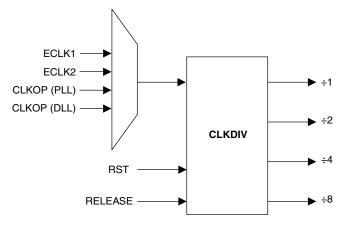

#### Figure 2-8. Clock Divider Connections

## **Clock Distribution Network**

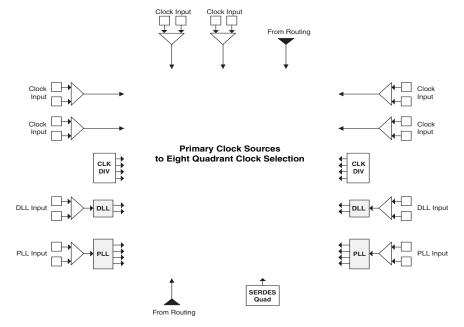

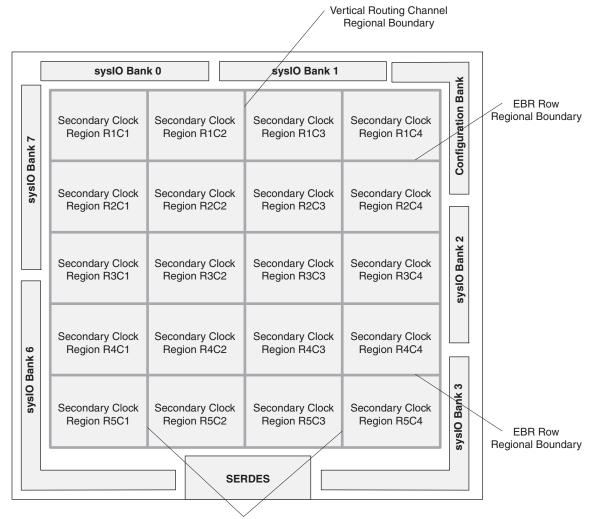

LatticeECP3 devices have eight quadrant-based primary clocks and eight secondary clock/control sources. Two high performance edge clocks are available on the top, left, and right edges of the device to support high speed interfaces. These clock sources are selected from external I/Os, the sysCLOCK PLLs, DLLs or routing. These clock sources are fed throughout the chip via a clock distribution system.

#### **Primary Clock Sources**

LatticeECP3 devices derive clocks from six primary source types: PLL outputs, DLL outputs, CLKDIV outputs, dedicated clock inputs, routing and SERDES Quads. LatticeECP3 devices have two to ten sysCLOCK PLLs and two DLLs, located on the left and right sides of the device. There are six dedicated clock inputs: two on the top side, two on the left side and two on the right side of the device. Figures 2-9, 2-10 and 2-11 show the primary clock sources for LatticeECP3 devices.

#### Figure 2-9. Primary Clock Sources for LatticeECP3-17

Note: Clock inputs can be configured in differential or single-ended mode.

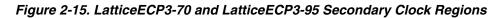

#### Table 2-6. Secondary Clock Regions

| Device   | Number of Secondary Clock<br>Regions |

|----------|--------------------------------------|

| ECP3-17  | 16                                   |

| ECP3-35  | 16                                   |

| ECP3-70  | 20                                   |

| ECP3-95  | 20                                   |

| ECP3-150 | 36                                   |

Spine Repeaters

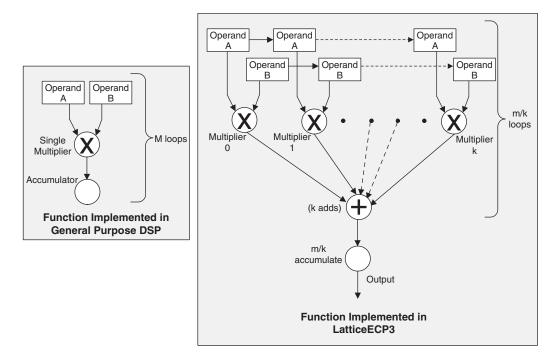

This allows designers to use highly parallel implementations of DSP functions. Designers can optimize DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2-23 compares the fully serial implementation to the mixed parallel and serial implementation.

#### Figure 2-23. Comparison of General DSP and LatticeECP3 Approaches

## LatticeECP3 sysDSP Slice Architecture Features

The LatticeECP3 sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The LatticeECP3 sysDSP Slice supports many functions that include the following:

- Multiply (one 18 x 36, two 18 x 18 or four 9 x 9 Multiplies per Slice)

- Multiply (36 x 36 by cascading across two sysDSP slices)

- Multiply Accumulate (up to 18 x 36 Multipliers feeding an Accumulator that can have up to 54-bit resolution)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18 x 18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such

as, overflow, underflow and convergent rounding, etc.

- Flexible cascading across slices to get larger functions

- RTL Synthesis friendly synchronous reset on all registers, while still supporting asynchronous reset for legacy users

- Dynamic MUX selection to allow Time Division Multiplexing (TDM) of resources for applications that require processor-like flexibility that enables different functions for each clock cycle

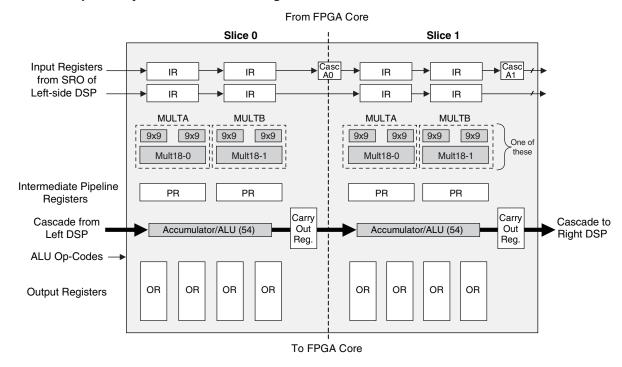

For most cases, as shown in Figure 2-24, the LatticeECP3 DSP slice is backwards-compatible with the LatticeECP2<sup>™</sup> sysDSP block, such that, legacy applications can be targeted to the LatticeECP3 sysDSP slice. The functionality of one LatticeECP2 sysDSP Block can be mapped into two adjacent LatticeECP3 sysDSP slices, as shown in Figure 2-25.

Figure 2-24. Simplified sysDSP Slice Block Diagram

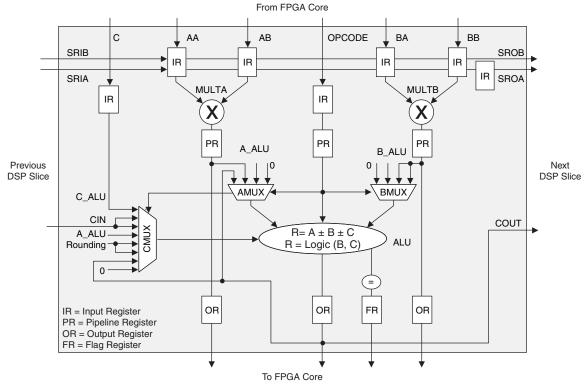

#### Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | x9                    | x18 | x36 |

|-------------------|-----------------------|-----|-----|

| MULT              | 4                     | 2   | 1/2 |

| MAC               | 1                     | 1   | _   |

| MULTADDSUB        | 2                     | 1   | _   |

| MULTADDSUBSUM     | <b>1</b> <sup>1</sup> | 1/2 | _   |

1. One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

#### ALU Flags

The sysDSP slice provides a number of flags from the ALU including:

- Equal to zero (EQZ)

- Equal to zero with mask (EQZM)

- Equal to one with mask (EQOM)

- Equal to pattern with mask (EQPAT)

- Equal to bit inverted pattern with mask (EQPATB)

- Accumulator Overflow (OVER)

- Accumulator Underflow (UNDER)

- Either over or under flow supporting LatticeECP2 legacy designs (OVERUNDER)

#### **Clock, Clock Enable and Reset Resources**

Global Clock, Clock Enable and Reset signals from routing are available to every sysDSP slice. From four clock sources (CLK0, CLK1, CLK2, and CLK3) one clock is selected for each input register, pipeline register and output register. Similarly Clock Enable (CE) and Reset (RST) are selected at each input register, pipeline register and output register.

#### **Resources Available in the LatticeECP3 Family**

Table 2-9 shows the maximum number of multipliers for each member of the LatticeECP3 family. Table 2-10 shows the maximum available EBR RAM Blocks in each LatticeECP3 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

| Device   | DSP Slices | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|----------|------------|----------------|------------------|------------------|

| ECP3-17  | 12         | 48             | 24               | 6                |

| ECP3-35  | 32         | 128            | 64               | 16               |

| ECP3-70  | 64         | 256            | 128              | 32               |

| ECP3-95  | 64         | 256            | 128              | 32               |

| ECP3-150 | 160        | 640            | 320              | 80               |

Table 2-9. Maximum Number of DSP Slices in the LatticeECP3 Family

Table 2-10. Embedded SRAM in the LatticeECP3 Family

| Device   | EBR SRAM Block | Total EBR SRAM<br>(Kbits) |

|----------|----------------|---------------------------|

| ECP3-17  | 38             | 700                       |

| ECP3-35  | 72             | 1327                      |

| ECP3-70  | 240            | 4420                      |

| ECP3-95  | 240            | 4420                      |

| ECP3-150 | 372            | 6850                      |

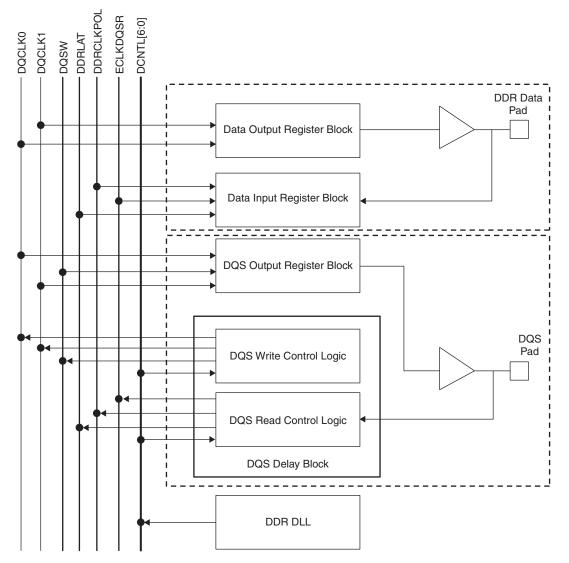

Input signals are fed from the sysl/O buffer to the input register block (as signal DI). If desired, the input signal can bypass the register and delay elements and be used directly as a combinatorial signal (INDD), a clock (INCK) and, in selected blocks, the input to the DQS delay block. If an input delay is desired, designers can select either a fixed delay or a dynamic delay DEL[3:0]. The delay, if selected, reduces input register hold time requirements when using a global clock.

The input block allows three modes of operation. In single data rate (SDR) the data is registered with the system clock by one of the registers in the single data rate sync register block.

In DDR mode, two registers are used to sample the data on the positive and negative edges of the modified DQS (ECLKDQSR) in the DDR Memory mode or ECLK signal when using DDR Generic mode, creating two data streams. Before entering the core, these two data streams are synchronized to the system clock to generate two data streams.

A gearbox function can be implemented in each of the input registers on the left and right sides. The gearbox function takes a double data rate signal applied to PIOA and converts it as four data streams, INA, IPA, INB and IPB. The two data streams from the first set of DDR registers are synchronized to the edge clock and then to the system clock before entering the core. Figure 2-30 provides further information on the use of the gearbox function.

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures adequate timing when data is transferred to the system clock domain from the ECLKDQSR (DDR Memory Interface mode) or ECLK (DDR Generic mode). The DDRLAT signal is used to ensure the data transfer from the synchronization registers to the clock transfer and gearbox registers.

The ECLKDQSR, DDRCLKPOL and DDRLAT signals are generated in the DQS Read Control Logic Block. See Figure 2-37 for an overview of the DQS read control logic.

Further discussion about using the DQS strobe in this module is discussed in the DDR Memory section of this data sheet.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on this topic.

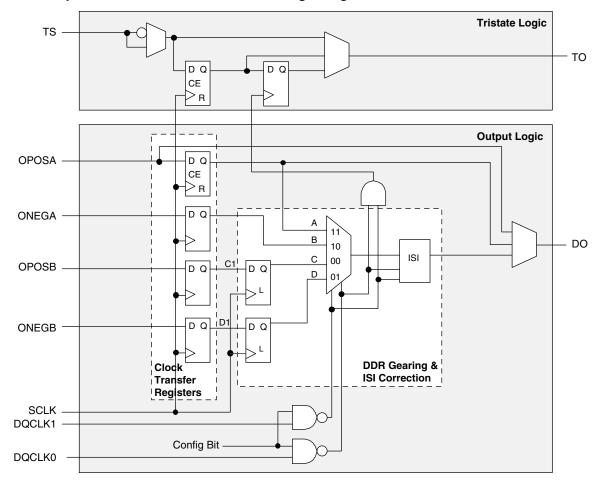

Figure 2-34. Output and Tristate Block for Left and Right Edges

#### Tristate Register Block

The tristate register block registers tri-state control signals from the core of the device before they are passed to the sysl/O buffers. The block contains a register for SDR operation and an additional register for DDR operation.

In SDR and non-gearing DDR modes, TS input feeds one of the flip-flops that then feeds the output. In DDRX2 mode, the register TS input is fed into another register that is clocked using the DQCLK0 and DQCLK1 signals. The output of this register is used as a tristate control.

#### **ISI** Calibration

The setting for Inter-Symbol Interference (ISI) cancellation occurs in the output register block. ISI correction is only available in the DDRX2 modes. ISI calibration settings exist once per output register block, so each I/O in a DQS-12 group may have a different ISI calibration setting.

The ISI block extends output signals at certain times, as a function of recent signal history. So, if the output pattern consists of a long strings of 0's to long strings of 1's, there are no delays on output signals. However, if there are quick, successive transitions from 010, the block will stretch out the binary 1. This is because the long trail of 0's will cause these symbols to interfere with the logic 1. Likewise, if there are quick, successive transitions from 101, the block will stretch out the binary 0. This block is controlled by a 3-bit delay control that can be set in the DQS control logic block.

For more information about this topic, please see the list of technical documentation at the end of this data sheet.

#### Figure 2-37. DQS Local Bus

#### **Polarity Control Logic**

In a typical DDR Memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the READ cycle) is unknown. The LatticeECP3 family contains dedicated circuits to transfer data between these domains. A clock polarity selector is used to prevent set-up and hold violations at the domain transfer between DQS (delayed) and the system clock. This changes the edge on which the data is registered in the synchronizing registers in the input register block. This requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects the first DQS rising edge after the preamble state. This signal is used to control the polarity of the clock to the synchronizing registers.

#### DDR3 Memory Support

LatticeECP3 supports the read and write leveling required for DDR3 memory interfaces.

Read leveling is supported by the use of the DDRCLKPOL and the DDRLAT signals generated in the DQS Read Control logic block. These signals dynamically control the capture of the data with respect to the DQS at the input register block.

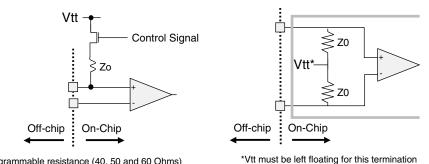

#### **On-Chip Programmable Termination**

The LatticeECP3 supports a variety of programmable on-chip terminations options, including:

- Dynamically switchable Single-Ended Termination with programmable resistor values of 40, 50, or 60 Ohms. External termination to Vtt should be used for DDR2 and DDR3 memory controller implementation.

- Common mode termination of 80, 100, 120 Ohms for differential inputs

#### Figure 2-39. On-Chip Termination

Programmable resistance (40, 50 and 60 Ohms)

Parallel Single-Ended Input

Differential Input

See Table 2-12 for termination options for input modes.

#### Table 2-12. On-Chip Termination Options for Input Modes

| IO_TYPE    | TERMINATE to VTT <sup>1, 2</sup> | DIFFERENTIAL TERMINATION RESISTOR <sup>1</sup> |

|------------|----------------------------------|------------------------------------------------|

| LVDS25     | þ                                | 80, 100, 120                                   |

| BLVDS25    | þ                                | 80, 100, 120                                   |

| MLVDS      | þ                                | 80, 100, 120                                   |

| HSTL18_I   | 40, 50, 60                       | þ                                              |

| HSTL18_II  | 40, 50, 60                       | þ                                              |

| HSTL18D_I  | 40, 50, 60                       | þ                                              |

| HSTL18D_II | 40, 50, 60                       | þ                                              |

| HSTL15_I   | 40, 50, 60                       | þ                                              |

| HSTL15D_I  | 40, 50, 60                       | þ                                              |

| SSTL25_I   | 40, 50, 60                       | þ                                              |

| SSTL25_II  | 40, 50, 60                       | þ                                              |

| SSTL25D_I  | 40, 50, 60                       | þ                                              |

| SSTL25D_II | 40, 50, 60                       | þ                                              |

| SSTL18_I   | 40, 50, 60                       | þ                                              |

| SSTL18_II  | 40, 50, 60                       | þ                                              |

| SSTL18D_I  | 40, 50, 60                       | þ                                              |

| SSTL18D_II | 40, 50, 60                       | þ                                              |

| SSTL15     | 40, 50, 60                       | þ                                              |

| SSTL15D    | 40, 50, 60                       |                                                |

1. TERMINATE to VTT and DIFFRENTIAL TERMINATION RESISTOR when turned on can only have one setting per bank. Only left and right banks have this feature. Use of TERMINATE to VTT and DIFFRENTIAL TERMINATION RESISTOR are mutually exclusive in

an I/O bank.

On-chip termination tolerance +/- 20%

2. External termination to VTT should be used when implementing DDR2 and DDR3 memory controller.

#### **Enhanced Configuration Options**

LatticeECP3 devices have enhanced configuration features such as: decryption support, TransFR™ I/O and dualboot image support.

#### 1. TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. See TN1087, Minimizing System Interruption During Configuration Using TransFR Technology for details.

#### 2. Dual-Boot Image Support

Dual-boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the LatticeECP3 can be re-booted from this new configuration file. If there is a problem, such as corrupt data during download or incorrect version number with this new boot image, the LatticeECP3 device can revert back to the original backup golden configuration and try again. This all can be done without power cycling the system. For more information, please see TN1169, LatticeECP3 sysCONFIG Usage Guide.

#### Soft Error Detect (SED) Support

LatticeECP3 devices have dedicated logic to perform Cycle Redundancy Code (CRC) checks. During configuration, the configuration data bitstream can be checked with the CRC logic block. In addition, the LatticeECP3 device can also be programmed to utilize a Soft Error Detect (SED) mode that checks for soft errors in configuration SRAM. The SED operation can be run in the background during user mode. If a soft error occurs, during user mode (normal operation) the device can be programmed to generate an error signal.

For further information on SED support, please see TN1184, LatticeECP3 Soft Error Detection (SED) Usage Guide.

#### **External Resistor**

LatticeECP3 devices require a single external, 10 kOhm  $\pm$ 1% value between the XRES pin and ground. Device configuration will not be completed if this resistor is missing. There is no boundary scan register on the external resistor pad.

#### **On-Chip Oscillator**

Every LatticeECP3 device has an internal CMOS oscillator which is used to derive a Master Clock (MCCLK) for configuration. The oscillator and the MCCLK run continuously and are available to user logic after configuration is completed. The software default value of the MCCLK is nominally 2.5 MHz. Table 2-16 lists all the available MCCLK frequencies. When a different Master Clock is selected during the design process, the following sequence takes place:

- 1. Device powers up with a nominal Master Clock frequency of 3.1 MHz.

- 2. During configuration, users select a different master clock frequency.

- 3. The Master Clock frequency changes to the selected frequency once the clock configuration bits are received.

- 4. If the user does not select a master clock frequency, then the configuration bitstream defaults to the MCCLK frequency of 2.5 MHz.

This internal 130 MHz +/- 15% CMOS oscillator is available to the user by routing it as an input clock to the clock tree. For further information on the use of this oscillator for configuration or user mode, please see TN1169, LatticeECP3 sysCONFIG Usage Guide.

# LatticeECP3 Family Data Sheet DC and Switching Characteristics

#### April 2014

Data Sheet DS1021

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Supply Voltage V_{CC}                                                         |

|-------------------------------------------------------------------------------|

| Supply Voltage V_{CCAUX} $\ldots \ldots \ldots \ldots -0.5$ V to 3.75 V       |

| Supply Voltage V_{CCJ} $\ldots \ldots \ldots \ldots \ldots -0.5$ V to 3.75 V  |

| Output Supply Voltage V_{CCIO} –0.5 V to 3.75 V                               |

| Input or I/O Tristate Voltage Applied $^4.$ –0.5 V to 3.75 V                  |

| Storage Temperature (Ambient) $\ldots \ldots -65$ V to 150 $^{\circ}\text{C}$ |

| Junction Temperature $(T_J)$                                                  |

<sup>1.</sup> Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

## **Recommended Operating Conditions**<sup>1</sup>

| Symbol                             | Parameter                                                                      | Min.  | Max.   | Units |

|------------------------------------|--------------------------------------------------------------------------------|-------|--------|-------|

| V <sub>CC<sup>2</sup></sub>        | Core Supply Voltage                                                            | 1.14  | 1.26   | V     |

| V <sub>CCAUX</sub> <sup>2, 4</sup> | Auxiliary Supply Voltage, Terminating Resistor Switching Power Supply (SERDES) | 3.135 | 3.465  | V     |

| V <sub>CCPLL</sub>                 | PLL Supply Voltage                                                             | 3.135 | 3.465  | V     |

| V <sub>CCIO<sup>2, 3</sup></sub>   | I/O Driver Supply Voltage                                                      | 1.14  | 3.465  | V     |

| V <sub>CCJ<sup>2</sup></sub>       | Supply Voltage for IEEE 1149.1 Test Access Port                                | 1.14  | 3.465  | V     |

| $V_{REF1}$ and $V_{REF2}$          | Input Reference Voltage                                                        | 0.5   | 1.7    | V     |

| V <sub>TT</sub> ⁵                  | Termination Voltage                                                            | 0.5   | 1.3125 | V     |

| t <sub>јсом</sub>                  | Junction Temperature, Commercial Operation                                     | 0     | 85     | °C    |

| t <sub>JIND</sub>                  | Junction Temperature, Industrial Operation                                     | -40   | 100    | °C    |

| SERDES External P                  | ower Supply <sup>6</sup>                                                       | •     | •      |       |

|                                    | Input Buffer Power Supply (1.2 V)                                              | 1.14  | 1.26   | V     |

| V <sub>CCIB</sub>                  | Input Buffer Power Supply (1.5 V)                                              | 1.425 | 1.575  | V     |

|                                    | Output Buffer Power Supply (1.2 V)                                             | 1.14  | 1.26   | V     |

| V <sub>CCOB</sub>                  | Output Buffer Power Supply (1.5 V)                                             | 1.425 | 1.575  | V     |

| V <sub>CCA</sub>                   | Transmit, Receive, PLL and Reference Clock Buffer Power Supply                 | 1.14  | 1.26   | V     |

1. For correct operation, all supplies except V<sub>REF</sub> and V<sub>TT</sub> must be held in their valid operation range. This is true independent of feature usage.

2. If  $V_{CCIO}$  or  $V_{CCJ}$  is set to 1.2 V, they must be connected to the same power supply as  $V_{CC.}$  If  $V_{CCIO}$  or  $V_{CCJ}$  is set to 3.3 V, they must be connected to the same power supply as  $V_{CCAUX}$ .

3. See recommended voltages by I/O standard in subsequent table.

4. V<sub>CCAUX</sub> ramp rate must not exceed 30 mV/µs during power-up when transitioning between 0 V and 3.3 V.

5. If not used, V<sub>TT</sub> should be left floating.

6. See TN1176, LatticeECP3 SERDES/PCS Usage Guide for information on board considerations for SERDES power supplies.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### Register-to-Register Performance<sup>1, 2, 3</sup>

| Function                                             | –8 Timing | Units |

|------------------------------------------------------|-----------|-------|

| 18x18 Multiply/Accumulate (Input & Output Registers) | 200       | MHz   |

| 18x18 Multiply-Add/Sub (All Registers)               | 400       | MHz   |

1. These timing numbers were generated using ispLEVER tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

3. For details on -9 speed grade devices, please contact your Lattice Sales Representative.

## **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond and ispLEVER design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond and ispLEVER design tools can provide logic timing numbers at a particular temperature and voltage.

## LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                       |                                 |                             | _        | -8                   | -7      |                       | 6      |          |                 |

|-----------------------|---------------------------------|-----------------------------|----------|----------------------|---------|-----------------------|--------|----------|-----------------|

| Parameter             | Description                     | Device                      | Min.     | Max.                 | Min.    | Max.                  | Min.   | Max.     | Units           |

| f <sub>MAX GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA              | _        | 250                  | _       | 250                   |        | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-35EA                   | 683      | _                    | 688     | _                     | 690    | _        | ps              |

| tDVAGDDR              | Data Valid After CLK            | ECP3-35EA                   | 683      | _                    | 688     | _                     | 690    | _        | ps              |

| fMAX GDDR             | DDRX1 Clock Frequency           | ECP3-35EA                   |          | 250                  |         | 250                   |        | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-17EA                   | 683      |                      | 688     |                       | 690    |          | ps              |

|                       | Data Valid After CLK            | ECP3-17EA                   | 683      | <u> </u>             | 688     | —                     | 690    | <u> </u> | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-17EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Dutput with Clock and Data Alig | ned at Pin (GDDRX1_TX.S     | SCLK.Ali | igned) <sup>10</sup> |         |                       |        |          |                 |

|                       | Data Invalid Before Clock       | ECP3-150EA                  |          | 335                  |         | 338                   |        | 341      | ps              |

|                       | Data Invalid After Clock        | ECP3-150EA                  |          | 335                  |         | 338                   | _      | 341      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA                  |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-70EA/95EA              |          | 339                  |         | 343                   |        | 347      | ps              |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-70EA/95EA              |          | 339                  | _       | 343                   |        | 347      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA              |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-35EA                   |          | 322                  |         | 320                   |        | 321      | ps              |

|                       | Data Invalid After Clock        | ECP3-35EA                   |          | 322                  |         | 320                   | _      | 321      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                   |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-17EA                   | _        | 322                  | _       | 320                   | _      | 321      | ps              |

|                       | Data Invalid After Clock        | ECP3-17EA                   |          | 322                  |         | 320                   | _      | 321      | ps              |

| fMAX GDDR             | DDRX1 Clock Frequency           | ECP3-17EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

| -                     | Dutput with Clock and Data (<10 | ) Bits Wide) Centered at P  | in (GDD  | RX1_TX.              | DQS.Cer | ntered) <sup>10</sup> |        |          |                 |

| Left and Right Si     |                                 |                             | -        |                      |         | -                     |        |          |                 |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-150EA                  | 670      | —                    | 670     | _                     | 670    | —        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-150EA                  | 670      | _                    | 670     | _                     | 670    | _        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA                  |          | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-70EA/95EA              | 657      | _                    | 652     | _                     | 650    | _        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-70EA/95EA              | 657      | _                    | 652     | _                     | 650    | _        | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-70EA/95EA              |          | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-35EA                   | 670      | —                    | 675     | _                     | 676    | —        | ps              |

|                       | Data Valid After CLK            | ECP3-35EA                   | 670      | _                    | 675     | _                     | 676    | _        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-17EA                   | 670      | —                    | 670     | _                     | 670    | —        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-17EA                   | 670      | _                    | 670     | _                     | 670    | _        | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-17EA                   |          | 250                  | _       | 250                   | _      | 250      | MHz             |

| -                     | Dutput with Clock and Data (>10 | ) Bits Wide) Aligned at Pir | n (GDDR  | X2_TX.A              | ligned) |                       |        |          | 1               |

| Left and Right Si     | des                             |                             |          |                      |         |                       |        |          |                 |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | All ECP3EA Devices          |          | 200                  |         | 210                   |        | 220      | ps              |

| tDIAGDDR              | Data Invalid After Clock        | All ECP3EA Devices          |          | 200                  |         | 210                   | _      | 220      | ps              |

| f <sub>MAX</sub> GDDR | DDRX2 Clock Frequency           | All ECP3EA Devices          | _        | 500                  | _       | 420                   |        | 375      | MHz             |

| -                     | Dutput with Clock and Data (>10 | ) Bits Wide) Centered at P  | in Using | g DQSDL              | L (GDDF | X2_TX.D               | QSDLL. | Centered | ) <sup>11</sup> |

| Left and Right Si     | des                             |                             |          |                      |         |                       |        |          |                 |

|                       | Data Valid Before CLK           | All ECP3EA Devices          | 400      | —                    | 400     | —                     | 431    | —        | ps              |

| tDVAGDDR              | Data Valid After CLK            | All ECP3EA Devices          | 400      | _                    | 400     |                       | 432    | —        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX2 Clock Frequency           | All ECP3EA Devices          | _        | 400                  |         | 400                   | _      | 375      | MHz             |

#### **Over Recommended Commercial Operating Conditions**

## **Timing Diagrams**

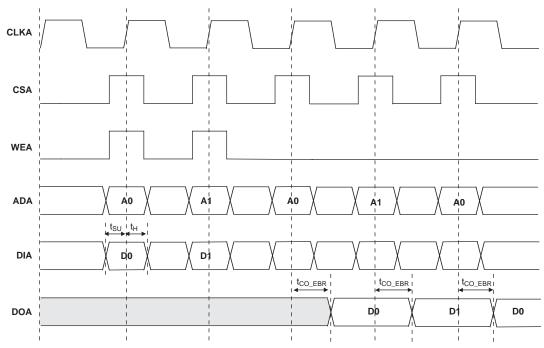

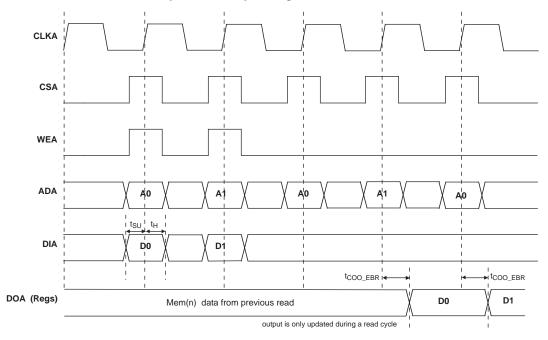

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

Figure 3-10. Read/Write Mode with Input and Output Registers

## sysCLOCK PLL Timing

| Parameter                      | Descriptions                                         | Conditions                           | Clock                      | Min.    | Тур. | Max.  | Units       |

|--------------------------------|------------------------------------------------------|--------------------------------------|----------------------------|---------|------|-------|-------------|

| £                              | Input clock frequency (CLKI,                         |                                      | Edge clock                 | 2       | _    | 500   | MHz         |

| f <sub>IN</sub>                | CLKFB)                                               |                                      | Primary clock <sup>4</sup> | 2       | _    | 420   | MHz         |

| 4                              | Output clock frequency (CLKOP,                       |                                      | Edge clock                 | 4       | _    | 500   | MHz         |

| fout                           | CLKOS)                                               |                                      | Primary clock <sup>4</sup> | 4       | _    | 420   | MHz         |

| f <sub>OUT1</sub>              | K-Divider output frequency                           | CLKOK                                |                            | 0.03125 | _    | 250   | MHz         |

| f <sub>OUT2</sub>              | K2-Divider output frequency                          | CLKOK2                               |                            | 0.667   | -    | 166   | MHz         |

| f <sub>VCO</sub>               | PLL VCO frequency                                    |                                      |                            | 500     | _    | 1000  | MHz         |

| f <sub>PFD</sub> ³             | Phase detector input frequency                       |                                      | Edge clock                 | 2       | -    | 500   | MHz         |

|                                |                                                      |                                      | Primary clock <sup>4</sup> | 2       | _    | 420   | MHz         |

| AC Charac                      | teristics                                            |                                      |                            |         |      | 1     |             |

| t <sub>PA</sub>                | Programmable delay unit                              |                                      |                            | 65      | 130  | 260   | ps          |

|                                |                                                      |                                      | Edge clock                 | 45      | 50   | 55    | %           |

| t <sub>DT</sub>                | Output clock duty cycle<br>(CLKOS, at 50% setting)   | f <sub>OUT</sub> ≤ 250 MHz           | Primary clock              | 45      | 50   | 55    | %           |

|                                |                                                      | f <sub>OUT</sub> > 250 MHz           | Primary clock              | 30      | 50   | 70    | %           |

| t <sub>CPA</sub>               | Coarse phase shift error<br>(CLKOS, at all settings) |                                      |                            | -5      | 0    | +5    | % of period |

| t <sub>OPW</sub>               | Output clock pulse width high or<br>low<br>(CLKOS)   |                                      |                            | 1.8     |      | _     | ns          |

|                                | Output clock period jitter                           | f <sub>OUT</sub> ≥ 420 MHz           |                            | _       |      | 200   | ps          |

| t <sub>OPJIT</sub> 1           |                                                      | 420 MHz > f <sub>OUT</sub> ≥ 100 MHz |                            | _       | _    | 250   | ps          |

|                                |                                                      | f <sub>OUT</sub> < 100 MHz           |                            | _       | _    | 0.025 | UIPP        |

| t <sub>SK</sub>                | Input clock to output clock skew when N/M = integer  |                                      |                            | _       |      | 500   | ps          |

| . 2                            |                                                      | 2 to 25 MHz                          |                            |         | _    | 200   | us          |

| t <sub>LOCK</sub> <sup>2</sup> | Lock time                                            | 25 to 500 MHz                        |                            | _       | _    | 50    | us          |

| t <sub>UNLOCK</sub>            | Reset to PLL unlock time to ensure fast reset        |                                      |                            | _       | _    | 50    | ns          |

| t <sub>HI</sub>                | Input clock high time                                | 90% to 90%                           |                            | 0.5     | _    | _     | ns          |

| t <sub>LO</sub>                | Input clock low time                                 | 10% to 10%                           |                            | 0.5     | _    | —     | ns          |

| t <sub>IPJIT</sub>             | Input clock period jitter                            |                                      |                            | —       | _    | 400   | ps          |

|                                | Reset signal pulse width high,<br>RSTK               |                                      |                            | 10      |      | _     | ns          |

| t <sub>RST</sub>               | Reset signal pulse width high,<br>RST                |                                      |                            | 500     | _    | -     | ns          |

#### **Over Recommended Operating Conditions**

1. Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock with no additional I/O toggling.

2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

3. Period jitter and cycle-to-cycle jitter numbers are guaranteed for  $f_{PFD} > 4$  MHz. For  $f_{PFD} < 4$  MHz, the jitter numbers may not be met in certain conditions. Please contact the factory for  $f_{PFD} < 4$  MHz.

4. When using internal feedback, maximum can be up to 500 MHz.

# HDMI (High-Definition Multimedia Interface) Electrical and Timing Characteristics

#### AC and DC Characteristics

#### Table 3-22. Transmit and Receive<sup>1, 2</sup>

|                                |                                                    | Spec. Co   |            |       |

|--------------------------------|----------------------------------------------------|------------|------------|-------|

| Symbol                         | Description                                        | Min. Spec. | Max. Spec. | Units |

| Transmit                       |                                                    | •          | 1          |       |

| Intra-pair Skew                |                                                    | —          | 75         | ps    |

| Inter-pair Skew                |                                                    | —          | 800        | ps    |

| TMDS Differential Clock Jitter |                                                    | —          | 0.25       | UI    |

| Receive                        | •                                                  |            | •          |       |

| R <sub>T</sub>                 | Termination Resistance                             | 40         | 60         | Ohms  |

| V <sub>ICM</sub>               | Input AC Common Mode Voltage (50-Ohm Set-<br>ting) | -          | 50         | mV    |

| TMDS Clock Jitter              | Clock Jitter Tolerance                             | —          | 0.25       | UI    |

1. Output buffers must drive a translation device. Max. speed is 2 Gbps. If translation device does not modify rise/fall time, the maximum speed is 1.5 Gbps.

2. Input buffers must be AC coupled in order to support the 3.3 V common mode. Generally, HDMI inputs are terminated by an external cable equalizer before data/clock is forwarded to the LatticeECP3 device.

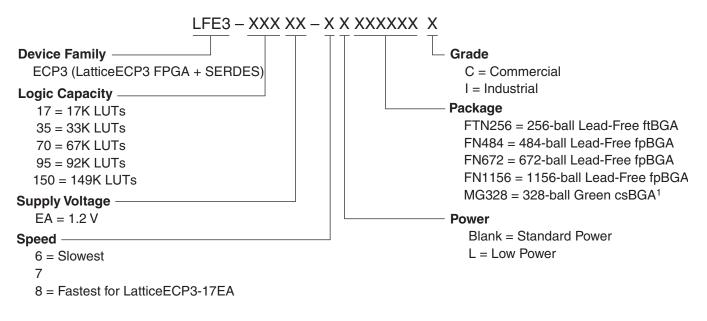

## LatticeECP3 Family Data Sheet Ordering Information

April 2014

Data Sheet DS1021

## LatticeECP3 Part Number Description

1. Green = Halogen free and lead free.

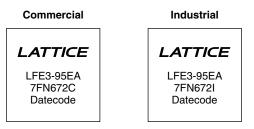

## **Ordering Information**

LatticeECP3 devices have top-side markings, for commercial and industrial grades, as shown below:

Note: See PCN 05A-12 for information regarding a change to the top-side mark logo.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.