# E. Attice Semiconductor Corporation - LFE3-70EA-8LFN1156C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                         |

|--------------------------------|--------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 8375                                                                           |

| Number of Logic Elements/Cells | 67000                                                                          |

| Total RAM Bits                 | 4526080                                                                        |

| Number of I/O                  | 490                                                                            |

| Number of Gates                | -                                                                              |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                  |

| Mounting Type                  | Surface Mount                                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                |

| Package / Case                 | 1156-BBGA                                                                      |

| Supplier Device Package        | 1156-FPBGA (35x35)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70ea-8lfn1156c |

|                                |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The edge clocks on the top, left, and right sides of the device can drive the secondary clocks or general routing resources of the device. The left and right side edge clocks also can drive the primary clock network through the clock dividers (CLKDIV).

# sysMEM Memory

LatticeECP3 devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of an 18-Kbit RAM with memory core, dedicated input registers and output registers with separate clock and clock enable. Each EBR includes functionality to support true dual-port, pseudo dual-port, single-port RAM, ROM and FIFO buffers (via external PFUs).

# sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as shown in Table 2-7. FIFOs can be implemented in sysMEM EBR blocks by implementing support logic with PFUs. The EBR block facilitates parity checking by supporting an optional parity bit for each data byte. EBR blocks provide byte-enable support for configurations with18-bit and 36-bit data widths. For more information, please see TN1179, LatticeECP3 Memory Usage Guide.

### Table 2-7. sysMEM Block Configurations

| Memory Mode      | Configurations                                                              |

|------------------|-----------------------------------------------------------------------------|

| Single Port      | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

| True Dual Port   | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18             |

| Pseudo Dual Port | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

# Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

# **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

# Memory Cascading

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

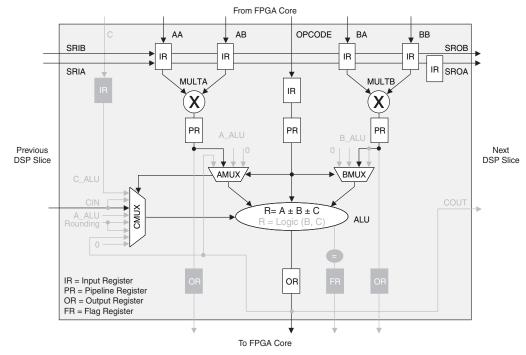

### Figure 2-31. MULTADDSUBSUM Slice 1

# Advanced sysDSP Slice Features

### Cascading

The LatticeECP3 sysDSP slice has been enhanced to allow cascading. Adder trees are implemented fully in sys-DSP slices, improving the performance. Cascading of slices uses the signals CIN, COUT and C Mux of the slice.

# Addition

The LatticeECP3 sysDSP slice allows for the bypassing of multipliers and cascading of adder logic. High performance adder functions are implemented without the use of LUTs. The maximum width adders that can be implemented are 54-bit.

# Rounding

The rounding operation is implemented in the ALU and is done by adding a constant followed by a truncation operation. The rounding methods supported are:

- Rounding to zero (RTZ)

- Rounding to infinity (RTI)

- Dynamic rounding

- Random rounding

- Convergent rounding

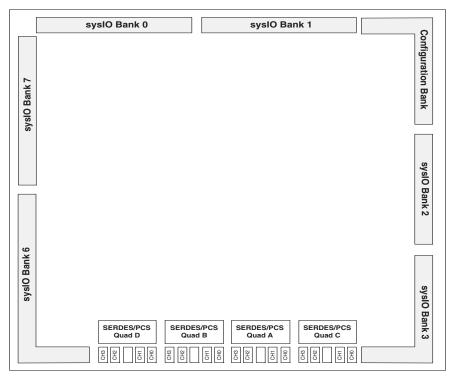

Figure 2-40. SERDES/PCS Quads (LatticeECP3-150)

### Table 2-13. LatticeECP3 SERDES Standard Support

| Standard                                                                     | Data Rate<br>(Mbps)                                             | Number of<br>General/Link Width | Encoding Style |

|------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|----------------|

| PCI Express 1.1                                                              | 2500                                                            | x1, x2, x4                      | 8b10b          |

| Gigabit Ethernet                                                             | 1250, 2500                                                      | x1                              | 8b10b          |

| SGMII                                                                        | 1250                                                            | x1                              | 8b10b          |

| XAUI                                                                         | 3125                                                            | x4                              | 8b10b          |

| Serial RapidIO Type I,<br>Serial RapidIO Type II,<br>Serial RapidIO Type III | 1250,<br>2500,<br>3125                                          | x1, x4                          | 8b10b          |

| CPRI-1,<br>CPRI-2,<br>CPRI-3,<br>CPRI-4                                      | 614.4,<br>1228.8,<br>2457.6,<br>3072.0                          | x1                              | 8b10b          |

| SD-SDI<br>(259M, 344M)                                                       | 143 <sup>1</sup> ,<br>177 <sup>1</sup> ,<br>270,<br>360,<br>540 | x1                              | NRZI/Scrambled |

| HD-SDI<br>(292M)                                                             | 1483.5,<br>1485                                                 | x1                              | NRZI/Scrambled |

| 3G-SDI<br>(424M)                                                             | 2967,<br>2970                                                   | x1                              | NRZI/Scrambled |

| SONET-STS-3 <sup>2</sup>                                                     | 155.52                                                          | x1                              | N/A            |

| SONET-STS-12 <sup>2</sup>                                                    | 622.08                                                          | x1                              | N/A            |

| SONET-STS-48 <sup>2</sup>                                                    | 2488                                                            | x1                              | N/A            |

1. For slower rates, the SERDES are bypassed and CML signals are directly connected to the FPGA routing.

2. The SONET protocol is supported in 8-bit SERDES mode. See TN1176 Lattice ECP3 SERDES/PCS Usage Guide for more information.

There are some restrictions to be aware of when using spread spectrum. When a quad shares a PCI Express x1 channel with a non-PCI Express channel, ensure that the reference clock for the quad is compatible with all protocols within the quad. For example, a PCI Express spread spectrum reference clock is not compatible with most Gigabit Ethernet applications because of tight CTC ppm requirements.

While the LatticeECP3 architecture will allow the mixing of a PCI Express channel and a Gigabit Ethernet, Serial RapidIO or SGMII channel within the same quad, using a PCI Express spread spectrum clocking as the transmit reference clock will cause a violation of the Gigabit Ethernet, Serial RapidIO and SGMII transmit jitter specifications.

For further information on SERDES, please see TN1176, LatticeECP3 SERDES/PCS Usage Guide.

# IEEE 1149.1-Compliant Boundary Scan Testability

All LatticeECP3 devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port has its own supply voltage  $V_{CCJ}$  and can operate with LVCMOS3.3, 2.5, 1.8, 1.5 and 1.2 standards.

For more information, please see TN1169, LatticeECP3 sysCONFIG Usage Guide.

# **Device Configuration**

All LatticeECP3 devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration, and the sysCONFIG port, support dual-byte, byte and serial configuration. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. The sysCONFIG port includes seven I/Os used as dedicated pins with the remaining pins used as dual-use pins. See TN1169, LatticeECP3 sysCONFIG Usage Guide for more information about using the dual-use pins as general purpose I/Os.

There are various ways to configure a LatticeECP3 device:

- 1. JTAG

- 2. Standard Serial Peripheral Interface (SPI and SPIm modes) interface to boot PROM memory

- 3. System microprocessor to drive a x8 CPU port (PCM mode)

- 4. System microprocessor to drive a serial slave SPI port (SSPI mode)

- 5. Generic byte wide flash with a MachXO<sup>™</sup> device, providing control and addressing

On power-up, the FPGA SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port.

LatticeECP3 devices also support the Slave SPI Interface. In this mode, the FPGA behaves like a SPI Flash device (slave mode) with the SPI port of the FPGA to perform read-write operations.

# LatticeECP3 Family Data Sheet DC and Switching Characteristics

#### April 2014

Data Sheet DS1021

# Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Supply Voltage V_{CC}                                                         |

|-------------------------------------------------------------------------------|

| Supply Voltage V_{CCAUX} $\ldots \ldots \ldots \ldots -0.5$ V to 3.75 V       |

| Supply Voltage V_{CCJ} $\ldots \ldots \ldots \ldots \ldots -0.5$ V to 3.75 V  |

| Output Supply Voltage V_{CCIO} –0.5 V to 3.75 V                               |

| Input or I/O Tristate Voltage Applied $^4.$ –0.5 V to 3.75 V                  |

| Storage Temperature (Ambient) $\ldots \ldots -65$ V to 150 $^{\circ}\text{C}$ |

| Junction Temperature $(T_J)$                                                  |

<sup>1.</sup> Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

# **Recommended Operating Conditions**<sup>1</sup>

| Symbol                             | Parameter                                                                      | Min.  | Max.   | Units |

|------------------------------------|--------------------------------------------------------------------------------|-------|--------|-------|

| V <sub>CC<sup>2</sup></sub>        | Core Supply Voltage                                                            | 1.14  | 1.26   | V     |

| V <sub>CCAUX</sub> <sup>2, 4</sup> | Auxiliary Supply Voltage, Terminating Resistor Switching Power Supply (SERDES) | 3.135 | 3.465  | V     |

| V <sub>CCPLL</sub>                 | PLL Supply Voltage                                                             | 3.135 | 3.465  | V     |

| V <sub>CCIO<sup>2, 3</sup></sub>   | I/O Driver Supply Voltage                                                      | 1.14  | 3.465  | V     |

| V <sub>CCJ<sup>2</sup></sub>       | Supply Voltage for IEEE 1149.1 Test Access Port                                | 1.14  | 3.465  | V     |

| $V_{REF1}$ and $V_{REF2}$          | Input Reference Voltage                                                        | 0.5   | 1.7    | V     |

| V <sub>TT</sub> ⁵                  | Termination Voltage                                                            | 0.5   | 1.3125 | V     |

| t <sub>јсом</sub>                  | Junction Temperature, Commercial Operation                                     | 0     | 85     | °C    |

| t <sub>JIND</sub>                  | Junction Temperature, Industrial Operation                                     | -40   | 100    | °C    |

| SERDES External P                  | ower Supply <sup>6</sup>                                                       | •     | •      |       |

|                                    | Input Buffer Power Supply (1.2 V)                                              | 1.14  | 1.26   | V     |

| V <sub>CCIB</sub>                  | Input Buffer Power Supply (1.5 V)                                              | 1.425 | 1.575  | V     |

|                                    | Output Buffer Power Supply (1.2 V)                                             | 1.14  | 1.26   | V     |

| V <sub>CCOB</sub>                  | Output Buffer Power Supply (1.5 V)                                             | 1.425 | 1.575  | V     |

| V <sub>CCA</sub>                   | Transmit, Receive, PLL and Reference Clock Buffer Power Supply                 | 1.14  | 1.26   | V     |

1. For correct operation, all supplies except V<sub>REF</sub> and V<sub>TT</sub> must be held in their valid operation range. This is true independent of feature usage.

If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 1.2 V, they must be connected to the same power supply as V<sub>CC.</sub> If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 3.3 V, they must be connected to the same power supply as V<sub>CCAUX</sub>.

3. See recommended voltages by I/O standard in subsequent table.

4. V<sub>CCAUX</sub> ramp rate must not exceed 30 mV/µs during power-up when transitioning between 0 V and 3.3 V.

5. If not used, V<sub>TT</sub> should be left floating.

6. See TN1176, LatticeECP3 SERDES/PCS Usage Guide for information on board considerations for SERDES power supplies.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# LatticeECP3 External Switching Characteristics <sup>1, 2, 3, 13</sup>

|                            |                                                                   |                     |           |                 |      |            | 1    | -6         |       |

|----------------------------|-------------------------------------------------------------------|---------------------|-----------|-----------------|------|------------|------|------------|-------|

| Parameter                  | Description                                                       | Device              | Min.      | -8<br>Max.      | Min. | -7<br>Max. | Min. | -о<br>Max. | Units |

| Clocks                     | Description                                                       | Device              | Min.      | wax.            | win. | wax.       | MIN. | wax.       | Units |

| Primary Clock <sup>6</sup> |                                                                   |                     |           |                 |      |            |      |            |       |

|                            | Frequency for Primary Clock Tree                                  | ECP3-150EA          | _         | 500             |      | 420        | _    | 375        | MHz   |

| t <sub>MAX_PRI</sub>       | Clock Pulse Width for Primary                                     |                     |           | 000             |      | 420        |      | 0/0        |       |

| t <sub>W_PRI</sub>         | Clock                                                             | ECP3-150EA          | 0.8       | —               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-150EA          | -         | 300             | —    | 330        | —    | 360        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-150EA          | _         | 250             | —    | 280        | —    | 300        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-70EA/95EA      | -         | 500             | —    | 420        | -    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-70EA/95EA      | 0.8       | —               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-70EA/95EA      | _         | 360             | _    | 370        | _    | 380        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-70EA/95EA      | —         | 310             | —    | 320        | —    | 330        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-35EA           | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-35EA           | 0.8       | —               | 0.9  |            | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-35EA           | -         | 300             | —    | 330        | _    | 360        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-35EA           | _         | 250             | —    | 280        | —    | 300        | ps    |

| f <sub>MAX_PRI</sub>       | Frequency for Primary Clock Tree                                  | ECP3-17EA           | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_PRI</sub>         | Pulse Width for Primary Clock                                     | ECP3-17EA           | 0.8       | _               | 0.9  | —          | 1.0  | —          | ns    |

| t <sub>SKEW_PRI</sub>      | Primary Clock Skew Within a<br>Device                             | ECP3-17EA           | _         | 310             | —    | 340        | —    | 370        | ps    |

| t <sub>SKEW_PRIB</sub>     | Primary Clock Skew Within a Bank                                  | ECP3-17EA           | _         | 220             | —    | 230        | —    | 240        | ps    |

| Edge Clock <sup>6</sup>    | •                                                                 |                     | •         |                 |      | •          | •    | •          |       |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-150EA          | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-150EA          | 0.9       | —               | 1.0  | —          | 1.2  | —          | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device                      | ECP3-150EA          | -         | 200             | —    | 210        | _    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-70EA/95EA      | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-70EA/95EA      | 0.9       | _               | 1.0  | —          | 1.2  | —          | ns    |

| t <sub>SKEW_EDGE_DQS</sub> | Edge Clock Skew Within an Edge of the Device                      | ECP3-70EA/95EA      | _         | 200             | _    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-35EA           | _         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-35EA           | 0. 9      | —               | 1.0  | —          | 1.2  | —          | ns    |

| <sup>t</sup> skew_edge_dqs | Edge Clock Skew Within an Edge of the Device                      | ECP3-35EA           | _         | 200             | _    | 210        | —    | 220        | ps    |

| f <sub>MAX_EDGE</sub>      | Frequency for Edge Clock                                          | ECP3-17EA           | —         | 500             | —    | 420        | —    | 375        | MHz   |

| t <sub>W_EDGE</sub>        | Clock Pulse Width for Edge Clock                                  | ECP3-17EA           | 0. 9      | —               | 1.0  | —          | 1.2  | —          | ns    |

| tskew_edge_dqs             | Edge Clock Skew Within an Edge of the Device                      | ECP3-17EA           | _         | 200             | _    | 210        | —    | 220        | ps    |

| Generic SDR                | •                                                                 |                     | •         | •               |      | •          | •    | •          | ·     |

| General I/O Pin Pa         | arameters Using Dedicated Clock In                                | put Primary Clock V | Vithout P | LL <sup>2</sup> |      |            |      |            |       |

| t <sub>CO</sub>            | Clock to Output - PIO Output<br>Register                          | ECP3-150EA          | _         | 3.9             | —    | 4.3        | —    | 4.7        | ns    |

| t <sub>SU</sub>            | Clock to Data Setup - PIO Input<br>Register                       | ECP3-150EA          | 0.0       | _               | 0.0  |            | 0.0  | _          | ns    |

| t <sub>H</sub>             | Clock to Data Hold - PIO Input<br>Register                        | ECP3-150EA          | 1.5       | _               | 1.7  |            | 2.0  |            | ns    |

| t <sub>SU_DEL</sub>        | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | ECP3-150EA          | 1.3       | —               | 1.5  | _          | 1.7  |            | ns    |

# **Over Recommended Commercial Operating Conditions**

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5, 7</sup>

| Buffer Type      | Description                     | -8    | -7    | -6    | Units |

|------------------|---------------------------------|-------|-------|-------|-------|

| Input Adjusters  |                                 | L     |       | •     |       |

| LVDS25E          | LVDS, Emulated, VCCIO = 2.5 V   | 0.03  | -0.01 | -0.03 | ns    |

| LVDS25           | LVDS, VCCIO = 2.5 V             | 0.03  | 0.00  | -0.04 | ns    |

| BLVDS25          | BLVDS, Emulated, VCCIO = 2.5 V  | 0.03  | 0.00  | -0.04 | ns    |

| MLVDS25          | MLVDS, Emulated, VCCIO = 2.5 V  | 0.03  | 0.00  | -0.04 | ns    |

| RSDS25           | RSDS, VCCIO = 2.5 V             | 0.03  | -0.01 | -0.03 | ns    |

| PPLVDS           | Point-to-Point LVDS             | 0.03  | -0.01 | -0.03 | ns    |

| TRLVDS           | Transition-Reduced LVDS         | 0.03  | 0.00  | -0.04 | ns    |

| Mini MLVDS       | Mini LVDS                       | 0.03  | -0.01 | -0.03 | ns    |

| LVPECL33         | LVPECL, Emulated, VCCIO = 3.3 V | 0.17  | 0.23  | 0.28  | ns    |

| HSTL18_I         | HSTL_18 class I, VCCIO = 1.8 V  | 0.20  | 0.17  | 0.13  | ns    |

| HSTL18_II        | HSTL_18 class II, VCCIO = 1.8 V | 0.20  | 0.17  | 0.13  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I    | 0.20  | 0.17  | 0.13  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II   | 0.20  | 0.17  | 0.13  | ns    |

| HSTL15_I         | HSTL_15 class I, VCCIO = 1.5 V  | 0.10  | 0.12  | 0.13  | ns    |

| HSTL15D_I        | Differential HSTL 15 class I    | 0.10  | 0.12  | 0.13  | ns    |

| SSTL33_I         | SSTL_3 class I, VCCIO = 3.3 V   | 0.17  | 0.23  | 0.28  | ns    |

| SSTL33_II        | SSTL_3 class II, VCCIO = 3.3 V  | 0.17  | 0.23  | 0.28  | ns    |

| SSTL33D_I        | Differential SSTL_3 class I     | 0.17  | 0.23  | 0.28  | ns    |

| SSTL33D_II       | Differential SSTL_3 class II    | 0.17  | 0.23  | 0.28  | ns    |

| SSTL25_I         | SSTL_2 class I, VCCIO = 2.5 V   | 0.12  | 0.14  | 0.16  | ns    |

| SSTL25_II        | SSTL_2 class II, VCCIO = 2.5 V  | 0.12  | 0.14  | 0.16  | ns    |

| SSTL25D_I        | Differential SSTL_2 class I     | 0.12  | 0.14  | 0.16  | ns    |

| SSTL25D_II       | Differential SSTL_2 class II    | 0.12  | 0.14  | 0.16  | ns    |

| SSTL18_I         | SSTL_18 class I, VCCIO = 1.8 V  | 0.08  | 0.06  | 0.04  | ns    |

| SSTL18_II        | SSTL_18 class II, VCCIO = 1.8 V | 0.08  | 0.06  | 0.04  | ns    |

| SSTL18D_I        | Differential SSTL_18 class I    | 0.08  | 0.06  | 0.04  | ns    |

| SSTL18D_II       | Differential SSTL_18 class II   | 0.08  | 0.06  | 0.04  | ns    |

| SSTL15           | SSTL_15, VCCIO = 1.5 V          | 0.087 | 0.059 | 0.032 | ns    |

| SSTL15D          | Differential SSTL_15            | 0.087 | 0.059 | 0.032 | ns    |

| LVTTL33          | LVTTL, VCCIO = 3.3 V            | 0.07  | 0.07  | 0.07  | ns    |

| LVCMOS33         | LVCMOS, VCCIO = 3.3 V           | 0.07  | 0.07  | 0.07  | ns    |

| LVCMOS25         | LVCMOS, VCCIO = 2.5 V           | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS18         | LVCMOS, VCCIO = 1.8 V           | -0.13 | -0.13 | -0.13 | ns    |

| LVCMOS15         | LVCMOS, VCCIO = 1.5 V           | -0.07 | -0.07 | -0.07 | ns    |

| LVCMOS12         | LVCMOS, VCCIO = 1.2 V           | -0.20 | -0.19 | -0.19 | ns    |

| PCI33            | PCI, VCCIO = 3.3 V              | 0.07  | 0.07  | 0.07  | ns    |

| Output Adjusters | 1                               | I     | I     | 1     | 1     |

| LVDS25E          | LVDS, Emulated, VCCIO = 2.5 V   | 1.02  | 1.14  | 1.26  | ns    |

| LVDS25           | LVDS, VCCIO = 2.5 V             | -0.11 | -0.07 | -0.03 | ns    |

| BLVDS25          | BLVDS, Emulated, VCCIO = 2.5 V  | 1.01  | 1.13  | 1.25  | ns    |

| MLVDS25          | MLVDS, Emulated, VCCIO = 2.5 V  | 1.01  | 1.13  | 1.25  | ns    |

### **Over Recommended Commercial Operating Conditions**

# sysCLOCK PLL Timing

| Parameter                      | Descriptions                                         | Conditions                           | Clock                      | Min.    | Тур. | Max.  | Units       |

|--------------------------------|------------------------------------------------------|--------------------------------------|----------------------------|---------|------|-------|-------------|

|                                | Input clock frequency (CLKI,                         |                                      | Edge clock                 | 2       | _    | 500   | MHz         |

| f <sub>IN</sub>                | CLKFB)                                               |                                      | Primary clock <sup>4</sup> | 2       | _    | 420   | MHz         |

|                                | Output clock frequency (CLKOP,                       |                                      | Edge clock                 | 4       | _    | 500   | MHz         |

| fout                           | CLKOS)                                               |                                      | Primary clock <sup>4</sup> | 4       | _    | 420   | MHz         |

| f <sub>OUT1</sub>              | K-Divider output frequency                           | CLKOK                                |                            | 0.03125 | _    | 250   | MHz         |

| f <sub>OUT2</sub>              | K2-Divider output frequency                          | CLKOK2                               |                            | 0.667   | -    | 166   | MHz         |

| f <sub>VCO</sub>               | PLL VCO frequency                                    |                                      |                            | 500     | _    | 1000  | MHz         |

| f <sub>PFD</sub> <sup>3</sup>  | Phase detector input frequency                       |                                      | Edge clock                 | 2       | -    | 500   | MHz         |

|                                |                                                      |                                      | Primary clock <sup>4</sup> | 2       | _    | 420   | MHz         |

| AC Charac                      | teristics                                            |                                      |                            |         |      | 1     |             |

| t <sub>PA</sub>                | Programmable delay unit                              |                                      |                            | 65      | 130  | 260   | ps          |

|                                |                                                      |                                      | Edge clock                 | 45      | 50   | 55    | %           |

| t <sub>DT</sub>                | Output clock duty cycle<br>(CLKOS, at 50% setting)   | f <sub>OUT</sub> ≤ 250 MHz           | Primary clock              | 45      | 50   | 55    | %           |

|                                | (CERCS, at 50 % setting)                             | f <sub>OUT</sub> > 250 MHz           | Primary clock              | 30      | 50   | 70    | %           |

| t <sub>CPA</sub>               | Coarse phase shift error<br>(CLKOS, at all settings) |                                      |                            | -5      | 0    | +5    | % of period |

| t <sub>OPW</sub>               | Output clock pulse width high or<br>low<br>(CLKOS)   |                                      |                            | 1.8     |      | _     | ns          |

|                                |                                                      | f <sub>OUT</sub> ≥ 420 MHz           |                            | _       |      | 200   | ps          |

| t <sub>OPJIT</sub> 1           | Output clock period jitter                           | 420 MHz > f <sub>OUT</sub> ≥ 100 MHz |                            | _       | _    | 250   | ps          |

|                                |                                                      | f <sub>OUT</sub> < 100 MHz           |                            | _       |      | 0.025 | UIPP        |

| t <sub>SK</sub>                | Input clock to output clock skew when N/M = integer  |                                      |                            | _       |      | 500   | ps          |

| . 2                            |                                                      | 2 to 25 MHz                          |                            |         | _    | 200   | us          |

| t <sub>LOCK</sub> <sup>2</sup> | Lock time                                            | 25 to 500 MHz                        |                            | _       | _    | 50    | us          |

| t <sub>UNLOCK</sub>            | Reset to PLL unlock time to<br>ensure fast reset     |                                      |                            | _       | _    | 50    | ns          |

| t <sub>HI</sub>                | Input clock high time                                | 90% to 90%                           |                            | 0.5     | _    | —     | ns          |

| t <sub>LO</sub>                | Input clock low time                                 | 10% to 10%                           |                            | 0.5     | _    | —     | ns          |

| t <sub>IPJIT</sub>             | Input clock period jitter                            |                                      |                            | —       | _    | 400   | ps          |

|                                | Reset signal pulse width high,<br>RSTK               |                                      |                            | 10      |      | _     | ns          |

| t <sub>RST</sub>               | Reset signal pulse width high,<br>RST                |                                      |                            | 500     | _    | _     | ns          |

### **Over Recommended Operating Conditions**

1. Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock with no additional I/O toggling.

2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

3. Period jitter and cycle-to-cycle jitter numbers are guaranteed for  $f_{PFD} > 4$  MHz. For  $f_{PFD} < 4$  MHz, the jitter numbers may not be met in certain conditions. Please contact the factory for  $f_{PFD} < 4$  MHz.

4. When using internal feedback, maximum can be up to 500 MHz.

# **DLL** Timing

# **Over Recommended Operating Conditions**

| Parameter                      | Description                                                                                                    | Condition               | Min. | Тур. | Max.   | Units  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------|------|------|--------|--------|

| f <sub>REF</sub>               | Input reference clock frequency (on-chip or off-chip)                                                          |                         | 133  | _    | 500    | MHz    |

| f <sub>FB</sub>                | Feedback clock frequency (on-chip or off-chip)                                                                 |                         | 133  |      | 500    | MHz    |

| f <sub>CLKOP</sub> 1           | Output clock frequency, CLKOP                                                                                  |                         | 133  |      | 500    | MHz    |

| f <sub>CLKOS<sup>2</sup></sub> | Output clock frequency, CLKOS                                                                                  |                         | 33.3 |      | 500    | MHz    |

| t <sub>PJIT</sub>              | Output clock period jitter (clean input)                                                                       |                         |      |      | 200    | ps p-p |

|                                | Output clock duty cycle (at 50% levels, 50% duty                                                               | Edge Clock              | 40   |      | 60     | %      |

| t <sub>DUTY</sub>              | cycle input clock, 50% duty cycle circuit turned off, time reference delay mode)                               | Primary Clock           | 30   |      | 70     | %      |

|                                | Output clock duty cycle (at 50% levels, arbitrary                                                              | Primary Clock < 250 MHz | 45   |      | 55     | %      |

| t <sub>DUTYTRD</sub>           | duty cycle input clock, 50% duty cycle circuit                                                                 | Primary Clock ≥ 250 MHz | 30   |      | 70     | %      |

|                                | enabled, time reference delay mode)                                                                            | Edge Clock              | 45   |      | 55     | %      |

|                                | Output clock duty cycle (at 50% levels, arbitrary                                                              | Primary Clock < 250 MHz | 40   |      | 60     | %      |

| t <sub>DUTYCIR</sub>           | duty cycle input clock, 50% duty cycle circuit<br>enabled, clock injection removal mode) with DLL<br>cascading | Primary Clock ≥ 250 MHz | 30   |      | 70     | %      |

|                                |                                                                                                                | Edge Clock              | 45   |      | 55     | %      |

| t <sub>SKEW</sub> <sup>3</sup> | Output clock to clock skew between two outputs with the same phase setting                                     |                         | _    | —    | 100    | ps     |

| t <sub>PHASE</sub>             | Phase error measured at device pads between off-chip reference clock and feedback clocks                       |                         | _    | _    | +/-400 | ps     |

| t <sub>PWH</sub>               | Input clock minimum pulse width high (at 80% level)                                                            |                         | 550  | _    | _      | ps     |

| t <sub>PWL</sub>               | Input clock minimum pulse width low (at 20% level)                                                             |                         | 550  | _    | _      | ps     |

| t <sub>INSTB</sub>             | Input clock period jitter                                                                                      |                         | _    |      | 500    | ps     |

| t <sub>LOCK</sub>              | DLL lock time                                                                                                  |                         | 8    | —    | 8200   | cycles |

| t <sub>RSWD</sub>              | Digital reset minimum pulse width (at 80% level)                                                               |                         | 3    |      |        | ns     |

| t <sub>DEL</sub>               | Delay step size                                                                                                |                         | 27   | 45   | 70     | ps     |

| t <sub>RANGE1</sub>            | Max. delay setting for single delay block (64 taps)                                                            |                         | 1.9  | 3.1  | 4.4    | ns     |

| t <sub>RANGE4</sub>            | Max. delay setting for four chained delay blocks                                                               |                         | 7.6  | 12.4 | 17.6   | ns     |

1. CLKOP runs at the same frequency as the input clock.

2. CLKOS minimum frequency is obtained with divide by 4.

3. This is intended to be a "path-matching" design guideline and is not a measurable specification.

### Table 3-11. Periodic Receiver Jitter Tolerance Specification

| Description | Frequency  | Condition               | Min. | Тур. | Max. | Units   |

|-------------|------------|-------------------------|------|------|------|---------|

| Periodic    | 2.97 Gbps  | 600 mV differential eye | —    |      | 0.24 | UI, p-p |

| Periodic    | 2.5 Gbps   | 600 mV differential eye | —    | _    | 0.22 | UI, p-p |

| Periodic    | 1.485 Gbps | 600 mV differential eye | —    |      | 0.24 | UI, p-p |

| Periodic    | 622 Mbps   | 600 mV differential eye | —    |      | 0.15 | UI, p-p |

| Periodic    | 150 Mbps   | 600 mV differential eye | _    |      | 0.5  | UI, p-p |

Note: Values are measured with PRBS 2<sup>7</sup>–1, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal, room temperature.

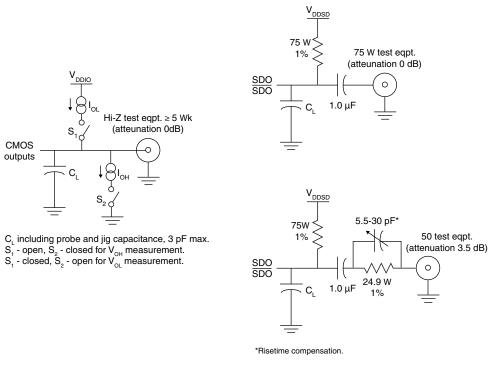

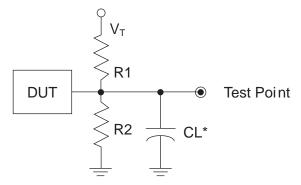

### Figure 3-19. Test Loads

Test Loads

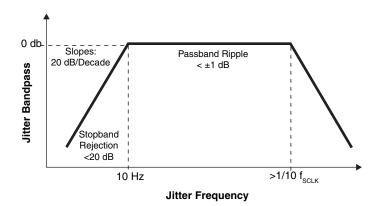

#### **Timing Jitter Bandpass**

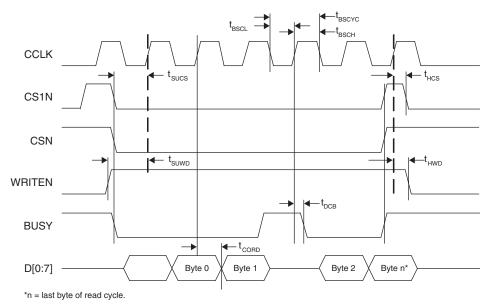

# LatticeECP3 sysCONFIG Port Timing Specifications (Continued)

**Over Recommended Operating Conditions**

| Parameter         | Description                              | Min. | Max. | Units |

|-------------------|------------------------------------------|------|------|-------|

| t <sub>SSCL</sub> | CCLK Minimum Low Pulse                   | 5    | _    | ns    |

| t <sub>HLCH</sub> | HOLDN Low Setup Time (Relative to CCLK)  | 5    | _    | ns    |

| t <sub>CHHH</sub> | HOLDN Low Hold Time (Relative to CCLK)   | 5    | _    | ns    |

| Master and        | Slave SPI (Continued)                    |      |      |       |

| t <sub>CHHL</sub> | HOLDN High Hold Time (Relative to CCLK)  | 5    | _    | ns    |

| t <sub>HHCH</sub> | HOLDN High Setup Time (Relative to CCLK) | 5    | _    | ns    |

| t <sub>HLQZ</sub> | HOLDN to Output High-Z                   | —    | 9    | ns    |

| t <sub>HHQX</sub> | HOLDN to Output Low-Z                    | —    | 9    | ns    |

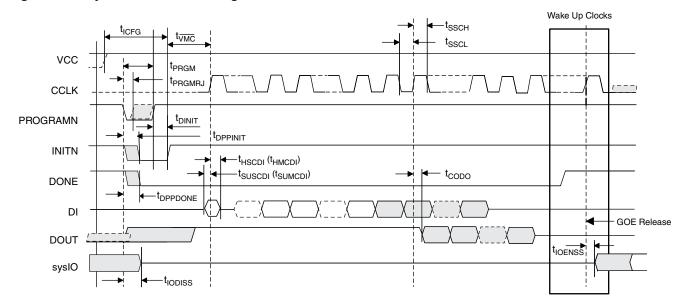

1. Re-toggling the PROGRAMN pin is not permitted until the INITN pin is high. Avoid consecutive toggling of the PROGRAMN.

| Parameter              | Min.                 | Max.                 | Units |

|------------------------|----------------------|----------------------|-------|

| Master Clock Frequency | Selected value - 15% | Selected value + 15% | MHz   |

| Duty Cycle             | 40                   | 60                   | %     |

### Figure 3-20. sysCONFIG Parallel Port Read Cycle

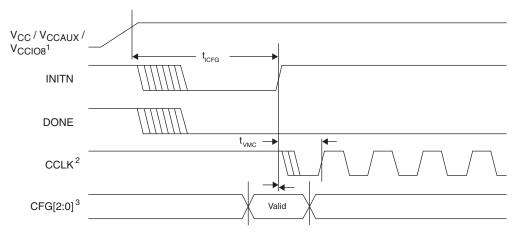

### Figure 3-24. Power-On-Reset (POR) Timing

Time taken from V<sub>CC</sub>, V<sub>CCAUX</sub> or V<sub>CCIO8</sub>, whichever is the last to cross the POR trip point.

Device is in a Master Mode (SPI, SPIm).

The CFG pins are normally static (hard wired).

### Figure 3-25. sysCONFIG Port Timing

# **Switching Test Conditions**

Figure 3-33 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-23.

### Figure 3-33. Output Test Load, LVTTL and LVCMOS Standards

\*CL Includes Test Fixture and Probe Capacitance

| Test Condition                                   | R <sub>1</sub>                         | R <sub>2</sub> | CL   | Timing Ref.                       | V <sub>T</sub>    |

|--------------------------------------------------|----------------------------------------|----------------|------|-----------------------------------|-------------------|

|                                                  | 8                                      | ×              | 0 pF | LVCMOS 3.3 = 1.5V                 | —                 |

|                                                  |                                        |                |      | LVCMOS 2.5 = $V_{CCIO}/2$         | —                 |

| LVTTL and other LVCMOS settings (L -> H, H -> L) |                                        |                |      | LVCMOS 1.8 = V <sub>CCIO</sub> /2 | —                 |

|                                                  |                                        |                |      | LVCMOS 1.5 = V <sub>CCIO</sub> /2 | —                 |

|                                                  |                                        |                |      | LVCMOS 1.2 = V <sub>CCIO</sub> /2 | —                 |

| LVCMOS 2.5 I/O (Z -> H)                          | x                                      | 1MΩ            | 0 pF | V <sub>CCIO</sub> /2              | —                 |

| LVCMOS 2.5 I/O (Z -> L)                          | 1 MΩ                                   | $\infty$       | 0 pF | V <sub>CCIO</sub> /2              | V <sub>CCIO</sub> |

| LVCMOS 2.5 I/O (H -> Z)                          | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 100            | 0 pF | V <sub>OH</sub> - 0.10            | —                 |

| LVCMOS 2.5 I/O (L -> Z)                          | 100                                    | $\infty$       | 0 pF | V <sub>OL</sub> + 0.10            | V <sub>CCIO</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

# Signal Descriptions (Cont.)

| Signal Name                     | I/O      | Description                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [LOC]DQS[num]                   | I/O      | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQS, num = ball function number.                                                                                                                                                                                                                                                                         |

| [LOC]DQ[num]                    | I/O      | DQ input/output pads: T (top), R (right), B (bottom), L (left), DQ, associated DQS number.                                                                                                                                                                                                                                                                               |

| Test and Programming (Dedicated | Pins)    |                                                                                                                                                                                                                                                                                                                                                                          |

| TMS                             | I        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                                                                                                                               |

| тск                             | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                                                                                                                        |

| TDI                             | I        | Test Data in pin. Used to load data into device using 1149.1 state machine.<br>After power-up, this TAP port can be activated for configuration by sending<br>appropriate command. (Note: once a configuration port is selected it is<br>locked. Another configuration port cannot be selected until the power-up<br>sequence). Pull-up is enabled during configuration. |

| TDO                             | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.                                                                                                                                                                                                                                                                                           |

| VCCJ                            | _        | Power supply pin for JTAG Test Access Port.                                                                                                                                                                                                                                                                                                                              |

| Configuration Pads (Used During | sysCONFI | Ġ)                                                                                                                                                                                                                                                                                                                                                                       |

| CFG[2:0]                        | I        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled. These are dedicated pins.                                                                                                                                                                                                               |

| INITN                           | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled. It is a dedicated pin.                                                                                                                                                                                                                                         |

| PROGRAMN                        | I        | Initiates configuration sequence when asserted low. This pin always has an active pull-up. It is a dedicated pin.                                                                                                                                                                                                                                                        |

| DONE                            | I/O      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress. It is a dedicated pin.                                                                                                                                                                                                                                   |

| CCLK                            | I        | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. It is a dedicated pin.                                                                                                                                                                                                                                                            |

| MCLK                            | I/O      | Output Configuration Clock for configuring an FPGA in SPI, SPIm, and Master configuration modes.                                                                                                                                                                                                                                                                         |

| BUSY/SISPI                      | 0        | Parallel configuration mode busy indicator. SPI/SPIm mode data output.                                                                                                                                                                                                                                                                                                   |

| CSN/SN/OEN                      | I/O      | Parallel configuration mode active-low chip select. Slave SPI chip select.<br>Parallel burst Flash output enable.                                                                                                                                                                                                                                                        |

| CS1N/HOLDN/RDY                  | I        | Parallel configuration mode active-low chip select. Slave SPI hold input.                                                                                                                                                                                                                                                                                                |

| WRITEN                          | I        | Write enable for parallel configuration modes.                                                                                                                                                                                                                                                                                                                           |

| DOUT/CSON/CSSPI1N               | 0        | Serial data output. Chip select output. SPI/SPIm mode chip select.                                                                                                                                                                                                                                                                                                       |

|                                 |          | sysCONFIG Port Data I/O for Parallel mode. Open drain during configuration.                                                                                                                                                                                                                                                                                              |

| D[0]/SPIFASTN                   | I/O      | sysCONFIG Port Data I/O for SPI or SPIm. When using the SPI or SPIm mode, this pin should either be tied high or low, must not be left floating. Open drain during configuration.                                                                                                                                                                                        |

| D1                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D2                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D3/SI                           | I/O      | Parallel configuration I/O. Slave SPI data input. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                  |

| D4/SO                           | I/O      | Parallel configuration I/O. Slave SPI data output. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                 |

| D5                              | I/O      | Parallel configuration I/O. Open drain during configuration.                                                                                                                                                                                                                                                                                                             |

| D6/SPID1                        | I/O      | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura-<br>tion.                                                                                                                                                                                                                                                                                   |

# **Signal Descriptions (Cont.)**

| I/O | Description                                                                            |

|-----|----------------------------------------------------------------------------------------|

| I/O | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura-<br>tion. |

| I/O | Serial data input for slave serial mode. SPI/SPIm mode chip select.                    |

|     |                                                                                        |

| I   | High-speed input, negative channel m                                                   |

| 0   | High-speed output, negative channel m                                                  |

| I   | Negative Reference Clock Input                                                         |

| I   | High-speed input, positive channel m                                                   |

| 0   | High-speed output, positive channel m                                                  |

| I   | Positive Reference Clock Input                                                         |

| —   | Output buffer power supply, channel m (1.2V/1.5)                                       |

|     | Input buffer power supply, channel m (1.2V/1.5V)                                       |

|     | I/O<br>I/O<br>I<br>I<br>I<br>I<br>I<br>I                                               |

1. When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

2. These pins are dedicated inputs or can be used as general purpose I/O.

3. m defines the associated channel in the quad.

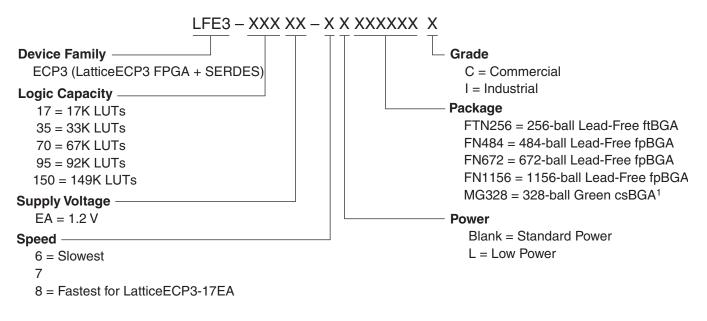

# LatticeECP3 Family Data Sheet Ordering Information

April 2014

Data Sheet DS1021

# LatticeECP3 Part Number Description

1. Green = Halogen free and lead free.

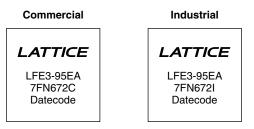

# **Ordering Information**

LatticeECP3 devices have top-side markings, for commercial and industrial grades, as shown below:

Note: See PCN 05A-12 for information regarding a change to the top-side mark logo.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Part Number          | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|----------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-150EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 149      |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number                        | Voltage | Grade | Power | Package         | Pins | Temp. | LUTs (K) |

|------------------------------------|---------|-------|-------|-----------------|------|-------|----------|

| LFE3-150EA-6FN672ITW <sup>1</sup>  | 1.2 V   | -6    | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-7FN672ITW <sup>1</sup>  | 1.2 V   | -7    | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-8FN672ITW <sup>1</sup>  | 1.2 V   | -8    | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-6FN1156ITW <sup>1</sup> | 1.2 V   | -6    | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-7FN1156ITW <sup>1</sup> | 1.2 V   | -7    | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-8FN1156ITW <sup>1</sup> | 1.2 V   | -8    | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

1. Specifications for the LFE3-150EA-*sp*FN*pkg*CTW and LFE3-150EA-*sp*FN*pkg*ITW devices, (where *sp* is the speed and *pkg* is the package), are the same as the LFE3-150EA-*sp*FN*pkg*C and LFE3-150EA-*sp*FN*pkg*I devices respectively, except as specified below.

• The CTC (Clock Tolerance Circuit) inside the SERDES hard PCS in the TW device is not functional but it can be bypassed and implemented in soft IP.

• The SERDES XRES pin on the TW device passes CDM testing at 250V.

# LatticeECP3 Family Data Sheet Revision History

March 2015

Data Sheet DS1021

| Date           | Version                                    | Section                             | Change Summary                                                                                                                                                                                                                                                  |

|----------------|--------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2015     | March 2015 2.8EA Pinout Information<br>All |                                     | Updated Package Pinout Information section. Changed reference to http://www.latticesemi.com/Products/FPGAandCPLD/LatticeECP3.                                                                                                                                   |

|                |                                            |                                     | Minor style/formatting changes.                                                                                                                                                                                                                                 |

| April 2014     | April 2014 02.7EA                          |                                     | Updated LatticeECP3 Supply Current (Standby) table power numbers.                                                                                                                                                                                               |

|                |                                            | Characteristics                     | Removed speed grade -9 timing numbers in the following sections:<br>— Typical Building Block Function Performance<br>— LatticeECP3 External Switching Characteristics<br>— LatticeECP3 Internal Switching Characteristics<br>— LatticeECP3 Family Timing Adders |

|                |                                            | Ordering Information                | Removed ordering information for -9 speed grade devices.                                                                                                                                                                                                        |

| March 2014     | 02.6EA                                     | DC and Switching<br>Characteristics | Added information to the sysl/O Single-Ended DC Electrical Character-<br>istics section footnote.                                                                                                                                                               |

| February 2014  | 02.5EA                                     | DC and Switching<br>Characteristics | Updated Hot Socketing Specifications table. Changed $I_{PW}$ to $I_{PD}$ in footnote 3.                                                                                                                                                                         |

|                |                                            |                                     | Updated the following figures:<br>— Figure 3-25, sysCONFIG Port Timing<br>— Figure 3-27, Wake-Up Timing                                                                                                                                                         |

|                |                                            | Supplemental<br>Information         | Added technical note references.                                                                                                                                                                                                                                |

| September 2013 | 02.4EA                                     | DC and Switching                    | Updated the Wake-Up Timing Diagram                                                                                                                                                                                                                              |

|                |                                            | Characteristics                     | Added the following figures:<br>— Master SPI POR Waveforms<br>— SPI Configuration Waveforms<br>— Slave SPI HOLDN Waveforms                                                                                                                                      |

|                |                                            |                                     | Added tIODISS and tIOENSS parameters in LatticeECP3 sysCONFIG Port Timing Specifications table.                                                                                                                                                                 |

| June 2013      | June 2013 02.3EA Architecture              |                                     | sysl/O Buffer Banks text section – Updated description of "Top (Bank 0<br>and Bank 1) and Bottom syslO Buffer Pairs (Single-Ended Outputs<br>Only)" for hot socketing information.                                                                              |

|                |                                            |                                     | sysl/O Buffer Banks text section – Updated description of "Configuration<br>Bank sysl/O Buffer Pairs (Single-Ended Outputs, Only on Shared Pins<br>When Not Used by Configuration)" for PCI clamp information.                                                  |

|                |                                            |                                     | On-Chip Oscillator section – clarified the speed of the internal CMOS oscillator (130 MHz +/- 15%).                                                                                                                                                             |

|                |                                            |                                     | Architecture Overview section – Added information on the state of the register on power up and after configuration.                                                                                                                                             |

|                |                                            | DC and Switching<br>Characteristics | sysl/O Recommended Operating Conditions table – Removed reference to footnote 1 from RSDS standard.                                                                                                                                                             |

|                |                                            |                                     | sysl/O Single-Ended DC Electrical Characteristics table – Modified foot-<br>note 1.                                                                                                                                                                             |

|                |                                            |                                     | Added Oscillator Output Frequency table.                                                                                                                                                                                                                        |

|                |                                            |                                     | LatticeECP3 sysCONFIG Port Timing Specifications table – Updated min. column for t <sub>CODO</sub> parameter.                                                                                                                                                   |

|                |                                            |                                     | LatticeECP3 Family Timing Adders table – Description column, references to VCCIO = 3.0V changed to 3.3V. For PPLVDS, description changed from emulated to True LVDS and VCCIO = 2.5V changed to VCCIO = 2.5V or 3.3V.                                           |

© 2015 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                           |

|---------------|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                                     | Updated Simplified Channel Block Diagram for SERDES/PCS Block diagram.                                                                                                                                                                                                                                                                                   |

|               |         |                                     | Updated Device Configuration text section.                                                                                                                                                                                                                                                                                                               |

|               |         |                                     | Corrected software default value of MCCLK to be 2.5 MHz.                                                                                                                                                                                                                                                                                                 |

|               |         | DC and Switching<br>Characteristics | Updated VCCOB Min/Max data in Recommended Operating Conditions table.                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Corrected footnote 2 in sysIO Recommended Operating Conditions table.                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Added added footnote 7 for t <sub>SKEW_PRIB</sub> to External Switching Characteristics table.                                                                                                                                                                                                                                                           |

|               |         |                                     | Added 2-to-1 Gearing text section and table.                                                                                                                                                                                                                                                                                                             |

|               |         |                                     | Updated External Reference Clock Specification (refclkp/refclkn) table.                                                                                                                                                                                                                                                                                  |

|               |         |                                     | LatticeECP3 sysCONFIG Port Timing Specifications - updated t <sub>DINIT</sub> information.                                                                                                                                                                                                                                                               |