# E.J. Lattice Semiconductor Corporation - LFE3-70EA-9FN484C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Not For New Designs                                                          |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 8375                                                                         |

| Number of Logic Elements/Cells | 67000                                                                        |

| Total RAM Bits                 | 4526080                                                                      |

| Number of I/O                  | 295                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 484-BBGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-70ea-9fn484c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **ROM Mode**

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information, please refer to TN1179, LatticeECP3 Memory Usage Guide.

# Routing

There are many resources provided in the LatticeECP3 devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The LatticeECP3 family has an enhanced routing architecture that produces a compact design. The Diamond and ispLEVER design software tool suites take the output of the synthesis tool and places and routes the design.

# sysCLOCK PLLs and DLLs

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The devices in the LatticeECP3 family support two to ten full-featured General Purpose PLLs.

## **General Purpose PLL**

The architecture of the PLL is shown in Figure 2-4. A description of the PLL functionality follows.

CLKI is the reference frequency (generated either from the pin or from routing) for the PLL. CLKI feeds into the Input Clock Divider block. The CLKFB is the feedback signal (generated from CLKOP, CLKOS or from a user clock pin/logic). This signal feeds into the Feedback Divider. The Feedback Divider is used to multiply the reference frequency.

Both the input path and feedback signals enter the Phase Frequency Detect Block (PFD) which detects first for the frequency, and then the phase, of the CLKI and CLKFB are the same which then drives the Voltage Controlled Oscillator (VCO) block. In this block the difference between the input path and feedback signals is used to control the frequency and phase of the oscillator. A LOCK signal is generated by the VCO to indicate that the VCO has locked onto the input clock signal. In dynamic mode, the PLL may lose lock after a dynamic delay adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied.

The output of the VCO then enters the CLKOP divider. The CLKOP divider allows the VCO to operate at higher frequencies than the clock output (CLKOP), thereby increasing the frequency range. The Phase/Duty Cycle/Duty Trim block adjusts the phase and duty cycle of the CLKOS signal. The phase/duty cycle setting can be pre-programmed or dynamically adjusted. A secondary divider takes the CLKOP or CLKOS signal and uses it to derive lower frequency outputs (CLKOK).

The primary output from the CLKOP divider (CLKOP) along with the outputs from the secondary dividers (CLKOK and CLKOK2) and Phase/Duty select (CLKOS) are fed to the clock distribution network.

The PLL allows two methods for adjusting the phase of signal. The first is referred to as Fine Delay Adjustment. This inserts up to 16 nominal 125 ps delays to be applied to the secondary PLL output. The number of steps may be set statically or from the FPGA logic. The second method is referred to as Coarse Phase Adjustment. This allows the phase of the rising and falling edge of the secondary PLL output to be adjusted in 22.5 degree steps. The number of steps may be set statically or from the FPGA logic.

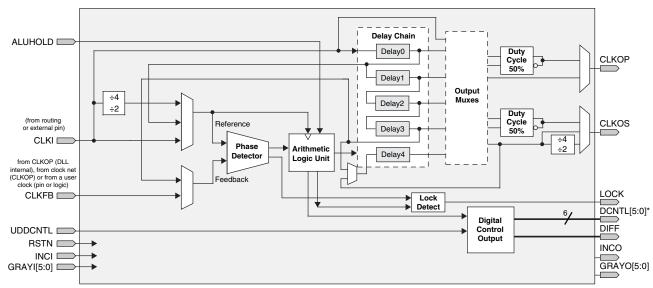

chain in order to better match the reference and feedback signals. This digital code from the ALU is also transmitted via the Digital Control bus (DCNTL) bus to its associated Slave Delay lines (two per DLL). The ALUHOLD input allows the user to suspend the ALU output at its current value. The UDDCNTL signal allows the user to latch the current value on the DCNTL bus.

The DLL has two clock outputs, CLKOP and CLKOS. These outputs can individually select one of the outputs from the tapped delay line. The CLKOS has optional fine delay shift and divider blocks to allow this output to be further modified, if required. The fine delay shift block allows the CLKOS output to phase shifted a further 45, 22.5 or 11.25 degrees relative to its normal position. Both the CLKOS and CLKOP outputs are available with optional duty cycle correction. Divide by two and divide by four frequencies are available at CLKOS. The LOCK output signal is asserted when the DLL is locked. Figure 2-5 shows the DLL block diagram and Table 2-5 provides a description of the DLL inputs and outputs.

The user can configure the DLL for many common functions such as time reference delay mode and clock injection removal mode. Lattice provides primitives in its design tools for these functions.

Figure 2-5. Delay Locked Loop Diagram (DLL)

\* This signal is not user accessible. This can only be used to feed the slave delay line.

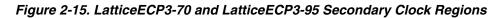

#### Table 2-6. Secondary Clock Regions

| Device   | Number of Secondary Clock<br>Regions |

|----------|--------------------------------------|

| ECP3-17  | 16                                   |

| ECP3-35  | 16                                   |

| ECP3-70  | 20                                   |

| ECP3-95  | 20                                   |

| ECP3-150 | 36                                   |

Spine Repeaters

### Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports the following forms of write behavior for single port or dual port operation:

- 1. **Normal** Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- 3. **Read-Before-Write (EA devices only)** When new data is written, the old content of the address appears at the output. This mode is supported for x9, x18, and x36 data widths.

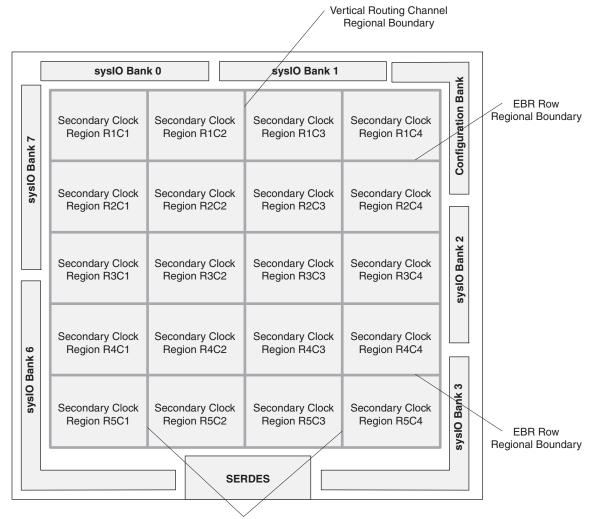

### Memory Core Reset

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal can reset both ports. The output data latches and associated resets for both ports are as shown in Figure 2-22.

#### Figure 2-22. Memory Core Reset

For further information on the sysMEM EBR block, please see the list of technical documentation at the end of this data sheet.

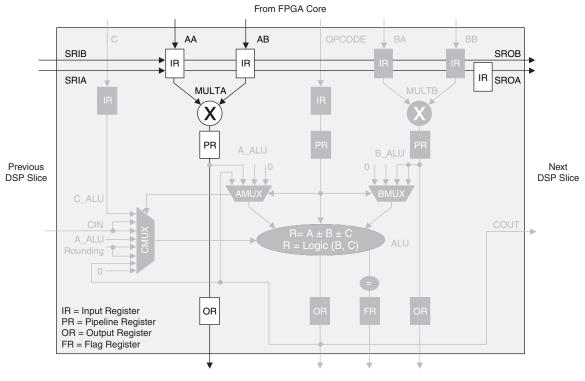

# sysDSP<sup>™</sup> Slice

The LatticeECP3 family provides an enhanced sysDSP architecture, making it ideally suited for low-cost, high-performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters, Fast Fourier Transforms (FFT) functions, Correlators, Reed-Solomon/Turbo/Convolution encoders and decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

## sysDSP Slice Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeECP3, on the other hand, has many DSP slices that support different data widths.

For further information, please refer to TN1182, LatticeECP3 sysDSP Usage Guide.

## **MULT DSP Element**

This multiplier element implements a multiply with no addition or accumulator nodes. The two operands, AA and AB, are multiplied and the result is available at the output. The user can enable the input/output and pipeline registers. Figure 2-26 shows the MULT sysDSP element.

#### Figure 2-26. MULT sysDSP Element

To FPGA Core

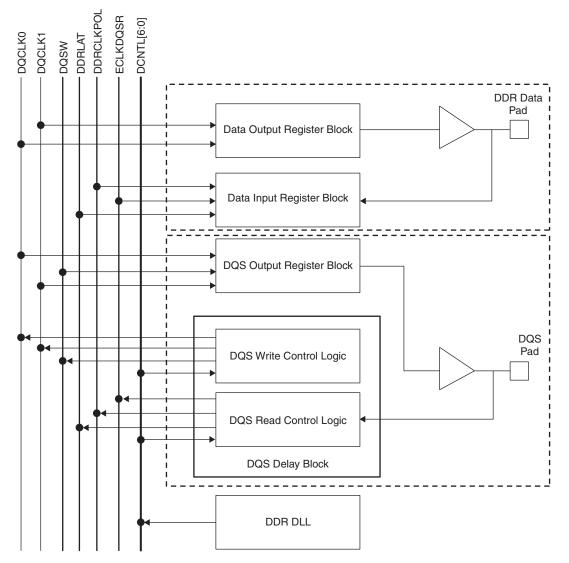

#### Figure 2-37. DQS Local Bus

# **Polarity Control Logic**

In a typical DDR Memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the READ cycle) is unknown. The LatticeECP3 family contains dedicated circuits to transfer data between these domains. A clock polarity selector is used to prevent set-up and hold violations at the domain transfer between DQS (delayed) and the system clock. This changes the edge on which the data is registered in the synchronizing registers in the input register block. This requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects the first DQS rising edge after the preamble state. This signal is used to control the polarity of the clock to the synchronizing registers.

## DDR3 Memory Support

LatticeECP3 supports the read and write leveling required for DDR3 memory interfaces.

Read leveling is supported by the use of the DDRCLKPOL and the DDRLAT signals generated in the DQS Read Control logic block. These signals dynamically control the capture of the data with respect to the DQS at the input register block.

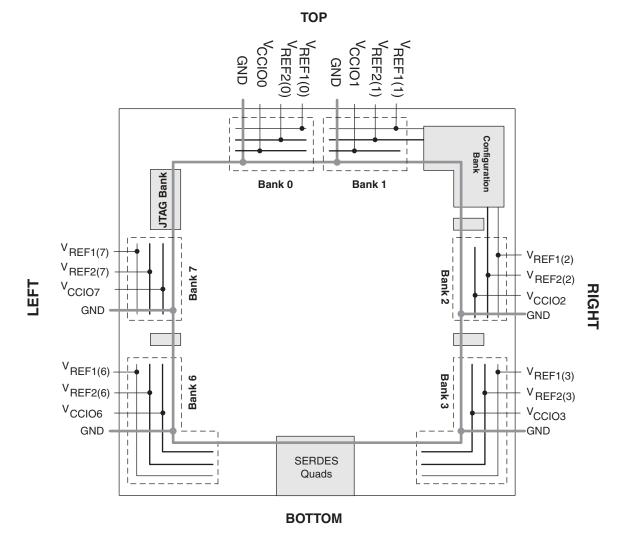

## Figure 2-38. LatticeECP3 Banks

LatticeECP3 devices contain two types of sysI/O buffer pairs.

#### 1. Top (Bank 0 and Bank 1) and Bottom sysIO Buffer Pairs (Single-Ended Outputs Only)

The sysl/O buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be configured as a differential input. Only the top edge buffers have a programmable PCI clamp.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

The top and bottom sides are ideal for general purpose I/O, PCI, and inputs for LVDS (LVDS outputs are only allowed on the left and right sides). The top side can be used for the DDR3 ADDR/CMD signals.

The I/O pins located on the top and bottom sides of the device (labeled PTxxA/B or PBxxA/B) are fully hot socketable. Note that the pads in Banks 3, 6 and 8 are wrapped around the corner of the device. In these banks, only the pads located on the top or bottom of the device are hot socketable. The top and bottom side pads can be identified by the Lattice Diamond tool.

| Package    | ECP3-17    | ECP3-35 | ECP3-70 | ECP3-95 | ECP3-150 |

|------------|------------|---------|---------|---------|----------|

| 256 ftBGA  | 1          | 1       | —       | —       | —        |

| 328 csBGA  | 2 channels | —       | —       | —       | _        |

| 484 fpBGA  | 1          | 1       | 1       | 1       |          |

| 672 fpBGA  | —          | 1       | 2       | 2       | 2        |

| 1156 fpBGA | —          | —       | 3       | 3       | 4        |

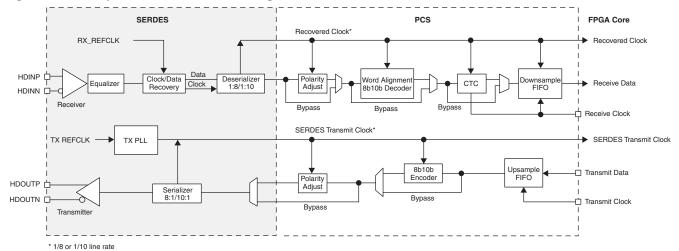

## SERDES Block

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2-41 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCOB and VCCIB).

Figure 2-41. Simplified Channel Block Diagram for SERDES/PCS Block

# PCS

As shown in Figure 2-41, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic.

There are some restrictions to be aware of when using spread spectrum. When a quad shares a PCI Express x1 channel with a non-PCI Express channel, ensure that the reference clock for the quad is compatible with all protocols within the quad. For example, a PCI Express spread spectrum reference clock is not compatible with most Gigabit Ethernet applications because of tight CTC ppm requirements.

While the LatticeECP3 architecture will allow the mixing of a PCI Express channel and a Gigabit Ethernet, Serial RapidIO or SGMII channel within the same quad, using a PCI Express spread spectrum clocking as the transmit reference clock will cause a violation of the Gigabit Ethernet, Serial RapidIO and SGMII transmit jitter specifications.

For further information on SERDES, please see TN1176, LatticeECP3 SERDES/PCS Usage Guide.

# IEEE 1149.1-Compliant Boundary Scan Testability

All LatticeECP3 devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port has its own supply voltage  $V_{CCJ}$  and can operate with LVCMOS3.3, 2.5, 1.8, 1.5 and 1.2 standards.

For more information, please see TN1169, LatticeECP3 sysCONFIG Usage Guide.

# **Device Configuration**

All LatticeECP3 devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration, and the sysCONFIG port, support dual-byte, byte and serial configuration. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. The sysCONFIG port includes seven I/Os used as dedicated pins with the remaining pins used as dual-use pins. See TN1169, LatticeECP3 sysCONFIG Usage Guide for more information about using the dual-use pins as general purpose I/Os.

There are various ways to configure a LatticeECP3 device:

- 1. JTAG

- 2. Standard Serial Peripheral Interface (SPI and SPIm modes) interface to boot PROM memory

- 3. System microprocessor to drive a x8 CPU port (PCM mode)

- 4. System microprocessor to drive a serial slave SPI port (SSPI mode)

- 5. Generic byte wide flash with a MachXO<sup>™</sup> device, providing control and addressing

On power-up, the FPGA SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port.

LatticeECP3 devices also support the Slave SPI Interface. In this mode, the FPGA behaves like a SPI Flash device (slave mode) with the SPI port of the FPGA to perform read-write operations.

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5, 7</sup>

| Buffer Type      | Description                     | -8    | -7    | -6    | Units |  |

|------------------|---------------------------------|-------|-------|-------|-------|--|

| Input Adjusters  |                                 | L     |       | •     |       |  |

| LVDS25E          | LVDS, Emulated, VCCIO = 2.5 V   | 0.03  | -0.01 | -0.03 | ns    |  |

| LVDS25           | LVDS, VCCIO = 2.5 V             | 0.03  | 0.00  | -0.04 | ns    |  |

| BLVDS25          | BLVDS, Emulated, VCCIO = 2.5 V  | 0.03  | 0.00  | -0.04 | ns    |  |

| MLVDS25          | MLVDS, Emulated, VCCIO = 2.5 V  | 0.03  | 0.00  | -0.04 | ns    |  |

| RSDS25           | RSDS, VCCIO = 2.5 V             | 0.03  | -0.01 | -0.03 | ns    |  |

| PPLVDS           | Point-to-Point LVDS             | 0.03  | -0.01 | -0.03 | ns    |  |

| TRLVDS           | Transition-Reduced LVDS         | 0.03  | 0.00  | -0.04 | ns    |  |

| Mini MLVDS       | Mini LVDS                       | 0.03  | -0.01 | -0.03 | ns    |  |

| LVPECL33         | LVPECL, Emulated, VCCIO = 3.3 V | 0.17  | 0.23  | 0.28  | ns    |  |

| HSTL18_I         | HSTL_18 class I, VCCIO = 1.8 V  | 0.20  | 0.17  | 0.13  | ns    |  |

| HSTL18_II        | HSTL_18 class II, VCCIO = 1.8 V | 0.20  | 0.17  | 0.13  | ns    |  |

| HSTL18D_I        | Differential HSTL 18 class I    | 0.20  | 0.17  | 0.13  | ns    |  |

| HSTL18D_II       | Differential HSTL 18 class II   | 0.20  | 0.17  | 0.13  | ns    |  |

| HSTL15_I         | HSTL_15 class I, VCCIO = 1.5 V  | 0.10  | 0.12  | 0.13  | ns    |  |

| HSTL15D_I        | Differential HSTL 15 class I    | 0.10  | 0.12  | 0.13  | ns    |  |

| SSTL33_I         | SSTL_3 class I, VCCIO = 3.3 V   | 0.17  | 0.23  | 0.28  | ns    |  |

| SSTL33_II        | SSTL_3 class II, VCCIO = 3.3 V  | 0.17  | 0.23  | 0.28  | ns    |  |

| SSTL33D_I        | Differential SSTL_3 class I     | 0.17  | 0.23  | 0.28  | ns    |  |

| SSTL33D_II       | Differential SSTL_3 class II    | 0.17  | 0.23  | 0.28  | ns    |  |

| SSTL25_I         | SSTL_2 class I, VCCIO = 2.5 V   | 0.12  | 0.14  | 0.16  | ns    |  |

| SSTL25_II        | SSTL_2 class II, VCCIO = 2.5 V  | 0.12  | 0.14  | 0.16  | ns    |  |

| SSTL25D_I        | Differential SSTL_2 class I     | 0.12  | 0.14  | 0.16  | ns    |  |

| SSTL25D_II       | Differential SSTL_2 class II    | 0.12  | 0.14  | 0.16  | ns    |  |

| SSTL18_I         | SSTL_18 class I, VCCIO = 1.8 V  | 0.08  | 0.06  | 0.04  | ns    |  |

| SSTL18_II        | SSTL_18 class II, VCCIO = 1.8 V | 0.08  | 0.06  | 0.04  | ns    |  |

| SSTL18D_I        | Differential SSTL_18 class I    | 0.08  | 0.06  | 0.04  | ns    |  |

| SSTL18D_II       | Differential SSTL_18 class II   | 0.08  | 0.06  | 0.04  | ns    |  |

| SSTL15           | SSTL_15, VCCIO = 1.5 V          | 0.087 | 0.059 | 0.032 | ns    |  |

| SSTL15D          | Differential SSTL_15            | 0.087 | 0.059 | 0.032 | ns    |  |

| LVTTL33          | LVTTL, VCCIO = 3.3 V            | 0.07  | 0.07  | 0.07  | ns    |  |

| LVCMOS33         | LVCMOS, VCCIO = 3.3 V           | 0.07  | 0.07  | 0.07  | ns    |  |

| LVCMOS25         | LVCMOS, VCCIO = 2.5 V           | 0.00  | 0.00  | 0.00  | ns    |  |

| LVCMOS18         | LVCMOS, VCCIO = 1.8 V           | -0.13 | -0.13 | -0.13 | ns    |  |

| LVCMOS15         | LVCMOS, VCCIO = 1.5 V           | -0.07 | -0.07 | -0.07 | ns    |  |

| LVCMOS12         | LVCMOS, VCCIO = 1.2 V           | -0.20 | -0.19 | -0.19 | ns    |  |

| PCI33            | PCI, VCCIO = 3.3 V              | 0.07  | 0.07  | 0.07  | ns    |  |

| Output Adjusters | 1                               | I     | I     | 1     | 1     |  |

| LVDS25E          | LVDS, Emulated, VCCIO = 2.5 V   | 1.02  | 1.14  | 1.26  | ns    |  |

| LVDS25           | LVDS, VCCIO = 2.5 V             | -0.11 | -0.07 | -0.03 | ns    |  |

| BLVDS25          | BLVDS, Emulated, VCCIO = 2.5 V  | 1.01  | 1.13  | 1.25  | ns    |  |

| MLVDS25          | MLVDS, Emulated, VCCIO = 2.5 V  | 1.01  | 1.13  | 1.25  | ns    |  |

#### **Over Recommended Commercial Operating Conditions**

# LatticeECP3 Family Timing Adders<sup>1, 2, 3, 4, 5, 7</sup> (Continued)

| Buffer Type   | Description                                            | -8    | -7    | -6    | Units |

|---------------|--------------------------------------------------------|-------|-------|-------|-------|

| RSDS25        | RSDS, VCCIO = 2.5 V                                    | -0.07 | -0.04 | -0.01 | ns    |

| PPLVDS        | Point-to-Point LVDS, True LVDS, VCCIO = 2.5 V or 3.3 V | -0.22 | -0.19 | -0.16 | ns    |

| LVPECL33      | LVPECL, Emulated, VCCIO = 3.3 V                        | 0.67  | 0.76  | 0.86  | ns    |

| HSTL18_I      | HSTL_18 class I 8mA drive, VCCIO = 1.8 V               | 1.20  | 1.34  | 1.47  | ns    |

| HSTL18_II     | HSTL_18 class II, VCCIO = 1.8 V                        | 0.89  | 1.00  | 1.11  | ns    |

| HSTL18D_I     | Differential HSTL 18 class I 8 mA drive                | 1.20  | 1.34  | 1.47  | ns    |

| HSTL18D_II    | Differential HSTL 18 class II                          | 0.89  | 1.00  | 1.11  | ns    |

| HSTL15_I      | HSTL_15 class I 4 mA drive, VCCIO = 1.5 V              | 1.67  | 1.83  | 1.99  | ns    |

| HSTL15D_I     | Differential HSTL 15 class I 4 mA drive                | 1.67  | 1.83  | 1.99  | ns    |

| SSTL33_I      | SSTL_3 class I, VCCIO = 3.3 V                          | 1.12  | 1.17  | 1.21  | ns    |

| SSTL33_II     | SSTL_3 class II, VCCIO = 3.3 V                         | 1.08  | 1.12  | 1.15  | ns    |

| SSTL33D_I     | Differential SSTL_3 class I                            | 1.12  | 1.17  | 1.21  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II                           | 1.08  | 1.12  | 1.15  | ns    |

| SSTL25_I      | SSTL_2 class I 8 mA drive, VCCIO = 2.5 V               | 1.06  | 1.19  | 1.31  | ns    |

| SSTL25_II     | SSTL_2 class II 16 mA drive, VCCIO = 2.5 V             | 1.04  | 1.17  | 1.31  | ns    |

| SSTL25D_I     | Differential SSTL_2 class I 8 mA drive                 | 1.06  | 1.19  | 1.31  | ns    |

| SSTL25D_II    | Differential SSTL_2 class II 16 mA drive               | 1.04  | 1.17  | 1.31  | ns    |

| SSTL18_I      | SSTL_1.8 class I, VCCIO = 1.8 V                        | 0.70  | 0.84  | 0.97  | ns    |

| SSTL18_II     | SSTL_1.8 class II 8 mA drive, VCCIO = 1.8 V            | 0.70  | 0.84  | 0.97  | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I                          | 0.70  | 0.84  | 0.97  | ns    |

| SSTL18D_II    | Differential SSTL_1.8 class II 8 mA drive              | 0.70  | 0.84  | 0.97  | ns    |

| SSTL15        | SSTL_1.5, VCCIO = 1.5 V                                | 1.22  | 1.35  | 1.48  | ns    |

| SSTL15D       | Differential SSTL_15                                   | 1.22  | 1.35  | 1.48  | ns    |

| LVTTL33_4mA   | LVTTL 4 mA drive, VCCIO = 3.3V                         | 0.25  | 0.24  | 0.23  | ns    |

| LVTTL33_8mA   | LVTTL 8 mA drive, VCCIO = 3.3V                         | -0.06 | -0.06 | -0.07 | ns    |

| LVTTL33_12mA  | LVTTL 12 mA drive, VCCIO = 3.3V                        | -0.01 | -0.02 | -0.02 | ns    |

| LVTTL33_16mA  | LVTTL 16 mA drive, VCCIO = 3.3V                        | -0.07 | -0.07 | -0.08 | ns    |

| LVTTL33_20mA  | LVTTL 20 mA drive, VCCIO = 3.3V                        | -0.12 | -0.13 | -0.14 | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4 mA drive, fast slew rate                  | 0.25  | 0.24  | 0.23  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8 mA drive, fast slew rate                  | -0.06 | -0.06 | -0.07 | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12 mA drive, fast slew rate                 | -0.01 | -0.02 | -0.02 | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16 mA drive, fast slew rate                 | -0.07 | -0.07 | -0.08 | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20 mA drive, fast slew rate                 | -0.12 | -0.13 | -0.14 | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4 mA drive, fast slew rate                  | 0.12  | 0.10  | 0.09  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8 mA drive, fast slew rate                  | -0.05 | -0.06 | -0.07 | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12 mA drive, fast slew rate                 | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16 mA drive, fast slew rate                 | -0.12 | -0.13 | -0.14 | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20 mA drive, fast slew rate                 | -0.12 | -0.13 | -0.14 | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4 mA drive, fast slew rate                  | 0.11  | 0.12  | 0.14  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8 mA drive, fast slew rate                  | 0.11  | 0.12  | 0.14  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12 mA drive, fast slew rate                 | -0.04 | -0.03 | -0.03 | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16 mA drive, fast slew rate                 | -0.04 | -0.03 | -0.03 | ns    |

## **Over Recommended Commercial Operating Conditions**

# **DLL** Timing

## **Over Recommended Operating Conditions**

| Parameter                      | Description                                                                                       | Condition               | Min. | Тур. | Max.   | Units  |

|--------------------------------|---------------------------------------------------------------------------------------------------|-------------------------|------|------|--------|--------|

| f <sub>REF</sub>               | Input reference clock frequency (on-chip or off-chip)                                             |                         | 133  | _    | 500    | MHz    |

| f <sub>FB</sub>                | Feedback clock frequency (on-chip or off-chip)                                                    |                         | 133  |      | 500    | MHz    |

| f <sub>CLKOP</sub> 1           | Output clock frequency, CLKOP                                                                     |                         | 133  |      | 500    | MHz    |

| f <sub>CLKOS<sup>2</sup></sub> | Output clock frequency, CLKOS                                                                     |                         | 33.3 |      | 500    | MHz    |

| t <sub>PJIT</sub>              | Output clock period jitter (clean input)                                                          |                         |      |      | 200    | ps p-p |

|                                | Output clock duty cycle (at 50% levels, 50% duty                                                  | Edge Clock              | 40   |      | 60     | %      |

| t <sub>DUTY</sub>              | cycle input clock, 50% duty cycle circuit turned off, time reference delay mode)                  | Primary Clock           | 30   |      | 70     | %      |

|                                | Output clock duty cycle (at 50% levels, arbitrary                                                 | Primary Clock < 250 MHz | 45   |      | 55     | %      |

| t <sub>DUTYTRD</sub>           | duty cycle input clock, 50% duty cycle circuit                                                    | Primary Clock ≥ 250 MHz | 30   |      | 70     | %      |

|                                | enabled, time reference delay mode)                                                               | Edge Clock              | 45   |      | 55     | %      |

|                                | Output clock duty cycle (at 50% levels, arbitrary                                                 | Primary Clock < 250 MHz | 40   |      | 60     | %      |

| t <sub>DUTYCIR</sub>           | duty cycle input clock, 50% duty cycle circuit<br>enabled, clock injection removal mode) with DLL | Primary Clock ≥ 250 MHz | 30   |      | 70     | %      |

|                                | cascading                                                                                         | Edge Clock              | 45   |      | 55     | %      |

| t <sub>SKEW</sub> <sup>3</sup> | Output clock to clock skew between two outputs with the same phase setting                        |                         | _    | _    | 100    | ps     |

| t <sub>PHASE</sub>             | Phase error measured at device pads between off-chip reference clock and feedback clocks          |                         | _    | _    | +/-400 | ps     |

| t <sub>PWH</sub>               | Input clock minimum pulse width high (at 80% level)                                               |                         | 550  | _    | _      | ps     |

| t <sub>PWL</sub>               | Input clock minimum pulse width low (at 20% level)                                                |                         | 550  | _    | _      | ps     |

| t <sub>INSTB</sub>             | Input clock period jitter                                                                         |                         | _    |      | 500    | ps     |

| t <sub>LOCK</sub>              | DLL lock time                                                                                     |                         | 8    | —    | 8200   | cycles |

| t <sub>RSWD</sub>              | Digital reset minimum pulse width (at 80% level)                                                  |                         | 3    |      |        | ns     |

| t <sub>DEL</sub>               | Delay step size                                                                                   |                         | 27   | 45   | 70     | ps     |

| t <sub>RANGE1</sub>            | Max. delay setting for single delay block (64 taps)                                               |                         | 1.9  | 3.1  | 4.4    | ns     |

| t <sub>RANGE4</sub>            | Max. delay setting for four chained delay blocks                                                  |                         | 7.6  | 12.4 | 17.6   | ns     |

1. CLKOP runs at the same frequency as the input clock.

2. CLKOS minimum frequency is obtained with divide by 4.

3. This is intended to be a "path-matching" design guideline and is not a measurable specification.

# SERDES High-Speed Data Transmitter<sup>1</sup>

## Table 3-6. Serial Output Timing and Levels

| Symbol                                 | Description                                                  | Frequency          | Min.                       | Тур.                       | Max.                       | Units   |

|----------------------------------------|--------------------------------------------------------------|--------------------|----------------------------|----------------------------|----------------------------|---------|

| V <sub>TX-DIFF-P-P-1.44</sub>          | Differential swing (1.44 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1150                       | 1440                       | 1730                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.35</sub>          | Differential swing (1.35 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1080                       | 1350                       | 1620                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.26</sub>          | Differential swing (1.26 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 1000                       | 1260                       | 1510                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.13</sub>          | Differential swing (1.13 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 840                        | 1130                       | 1420                       | mV, p-p |

| V <sub>TX-DIFF-P-P-1.04</sub>          | Differential swing (1.04 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 780                        | 1040                       | 1300                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.92</sub>          | Differential swing (0.92 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 690                        | 920                        | 1150                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.87</sub>          | Differential swing (0.87 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 650                        | 870                        | 1090                       | mV, p-p |

| V <sub>TX-DIFF-P-P-0.78</sub>          | Differential swing (0.78 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 585                        | 780                        | 975                        | mV, p-p |

| V <sub>TX-DIFF-P-P-0.64</sub>          | Differential swing (0.64 V setting) <sup>1, 2</sup>          | 0.15 to 3.125 Gbps | 480                        | 640                        | 800                        | mV, p-p |

| V <sub>OCM</sub>                       | Output common mode voltage                                   | _                  | V <sub>CCOB</sub><br>-0.75 | V <sub>CCOB</sub><br>-0.60 | V <sub>CCOB</sub><br>-0.45 | V       |

| T <sub>TX-R</sub>                      | Rise time (20% to 80%)                                       | —                  | 145                        | 185                        | 265                        | ps      |

| T <sub>TX-F</sub>                      | Fall time (80% to 20%)                                       | —                  | 145                        | 185                        | 265                        | ps      |

| Z <sub>TX-OI-SE</sub>                  | Output Impedance 50/75/HiZ Ohms<br>(single ended)            | _                  | -20%                       | 50/75/<br>Hi Z             | +20%                       | Ohms    |

| R <sub>LTX-RL</sub>                    | Return loss (with package)                                   | —                  | 10                         |                            |                            | dB      |

| T <sub>TX-INTRASKEW</sub>              | Lane-to-lane TX skew within a SERDES quad block (intra-quad) | —                  | _                          | _                          | 200                        | ps      |

| T <sub>TX-INTERSKEW</sub> <sup>3</sup> | Lane-to-lane skew between SERDES quad blocks (inter-quad)    | —                  | _                          | _                          | 1UI +200                   | ps      |

1. All measurements are with 50 Ohm impedance.

2. See TN1176, LatticeECP3 SERDES/PCS Usage Guide for actual binary settings and the min-max range.

3. Inter-quad skew is between all SERDES channels on the device and requires the use of a low skew internal reference clock.

#### Table 3-11. Periodic Receiver Jitter Tolerance Specification

| Description | Frequency  | Condition               | Min. | Тур. | Max. | Units   |

|-------------|------------|-------------------------|------|------|------|---------|

| Periodic    | 2.97 Gbps  | 600 mV differential eye | —    |      | 0.24 | UI, p-p |

| Periodic    | 2.5 Gbps   | 600 mV differential eye | —    | _    | 0.22 | UI, p-p |

| Periodic    | 1.485 Gbps | 600 mV differential eye | —    | —    | 0.24 | UI, p-p |

| Periodic    | 622 Mbps   | 600 mV differential eye | —    |      | 0.15 | UI, p-p |

| Periodic    | 150 Mbps   | 600 mV differential eye |      | —    | 0.5  | UI, p-p |

Note: Values are measured with PRBS 2<sup>7</sup>–1, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal, room temperature.

# LatticeECP3 Family Data Sheet Ordering Information

April 2014

Data Sheet DS1021

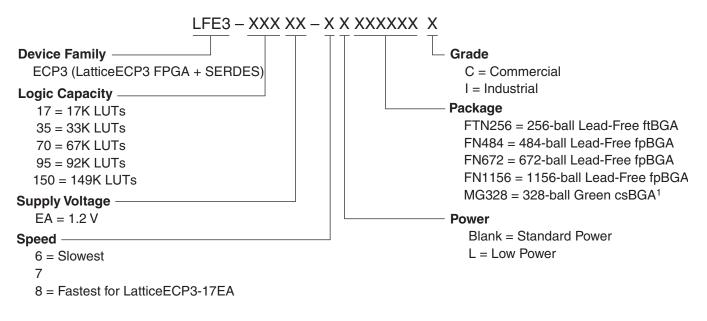

# LatticeECP3 Part Number Description

1. Green = Halogen free and lead free.

# **Ordering Information**

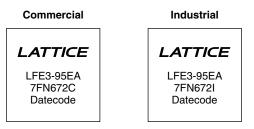

LatticeECP3 devices have top-side markings, for commercial and industrial grades, as shown below:

Note: See PCN 05A-12 for information regarding a change to the top-side mark logo.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Date          | Version                             | Section                                                                                                                                 | Change Summary                                                                                                                                                      |

|---------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                     |                                                                                                                                         | Updated Frequency to 150 Mbps in Table 3-11 Periodic Receiver Jitter Tolerance Specification                                                                        |

| December 2010 | 01.7EA                              | Multiple                                                                                                                                | Data sheet made final. Removed "preliminary" headings.                                                                                                              |

|               |                                     |                                                                                                                                         | Removed data for 70E and 95E devices. A separate data sheet is available for these specific devices.                                                                |

|               |                                     |                                                                                                                                         | Updated for Lattice Diamond design software.                                                                                                                        |

|               |                                     | Introduction                                                                                                                            | Corrected number of user I/Os                                                                                                                                       |

|               |                                     | Architecture                                                                                                                            | Corrected the package type in Table 2-14 Available SERDES Quad per LatticeECP3 Devices.                                                                             |

|               |                                     |                                                                                                                                         | Updated description of General Purpose PLL                                                                                                                          |

|               |                                     | Added additional information in the Flexible Quad SERDES Architecture section.                                                          |                                                                                                                                                                     |

|               |                                     | Added footnotes and corrected the information in Table 2-16 Selectable master Clock (MCCLK) Frequencies During Configuration (Nominal). |                                                                                                                                                                     |

|               |                                     |                                                                                                                                         | Updated Figure 2-16, Per Region Secondary Clock Selection.                                                                                                          |

|               |                                     |                                                                                                                                         | Updated description for On-Chip Programmable Termination.                                                                                                           |

|               |                                     |                                                                                                                                         | Added information about number of rows of DSP slices.                                                                                                               |

|               |                                     | Updated footnote 2 for Table 2-12, On-Chip Termination<br>Input Modes.                                                                  | Updated footnote 2 for Table 2-12, On-Chip Termination Options for Input Modes.                                                                                     |

|               |                                     |                                                                                                                                         | Updated information for sysIO buffer pairs.                                                                                                                         |

|               |                                     |                                                                                                                                         | Corrected minimum number of General Purpose PLLs (was 4, now 2).                                                                                                    |

|               | DC and Switching<br>Characteristics | Regenerated sysCONFIG Port Timing figure.                                                                                               |                                                                                                                                                                     |

|               |                                     | Added $t_{\rm W}$ (clock pulse width) in External Switching Characteristics table.                                                      |                                                                                                                                                                     |

|               |                                     |                                                                                                                                         | Corrected units, revised and added data, and corrected footnote 1 in External Switching Characteristics table.                                                      |

|               |                                     |                                                                                                                                         | Added Jitter Transfer figures in SERDES External Reference Clock section.                                                                                           |

|               |                                     |                                                                                                                                         | Corrected capacitance information in the DC Electrical Characteristics table.                                                                                       |

|               |                                     |                                                                                                                                         | Corrected data in the Register-to-Register Performance table.                                                                                                       |

|               |                                     |                                                                                                                                         | Corrected GDDR Parameter name HOGDDR.                                                                                                                               |

|               |                                     |                                                                                                                                         | Corrected RSDS25 -7 data in Family Timing Adders table.                                                                                                             |

|               |                                     |                                                                                                                                         | Added footnotes 10-12 to DDR data information in the External Switching Characteristics table.                                                                      |

|               |                                     |                                                                                                                                         | Corrected titles for Figures 3-7 (DDR/DDR2/DDR3 Parameters) and 3-8 (Generic DDR/DDRX2 Parameters).                                                                 |

|               |                                     |                                                                                                                                         | Updated titles for Figures 3-5 (MLVDS25 (Multipoint Low Voltage Differ-<br>ential Signaling)) and 3-6 (Generic DDRX1/DDRX2 (With Clock and<br>Data Edges Aligned)). |

|               |                                     |                                                                                                                                         | Updated Supply Current table.                                                                                                                                       |

|               |                                     |                                                                                                                                         | Added GDDR interface information to the External Switching and Characteristics table.                                                                               |

|               |                                     |                                                                                                                                         | Added footnote to sysIO Recommended Operating Conditions table.                                                                                                     |

|               |                                     |                                                                                                                                         | Added footnote to LVDS25 table.                                                                                                                                     |

|               |                                     |                                                                                                                                         | Corrected DDR section footnotes and references.                                                                                                                     |

|               |                                     |                                                                                                                                         | Corrected Hot Socketing support from "top and bottom banks" to "top and bottom I/O pins".                                                                           |

|               | ľ                                   | Pinout Information                                                                                                                      | Updated description for VTTx.                                                                                                                                       |

| Date          | Version | Section                             | Change Summary                                                                                                      |

|---------------|---------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| March 2010    | 01.6    | Architecture                        | Added Read-Before-Write information.                                                                                |

|               |         | DC and Switching                    | Added footnote #6 to Maximum I/O Buffer Speed table.                                                                |

|               |         | Characteristics                     | Corrected minimum operating conditions for input and output differential voltages in the Point-to-Point LVDS table. |

|               |         | Pinout Information                  | Added pin information for the LatticeECP3-70EA and LatticeECP3-<br>95EA devices.                                    |

|               |         | Ordering Information                | Added ordering part numbers for the LatticeECP3-70EA and LatticeECP3-95EA devices.                                  |

|               |         |                                     | Removed dual mark information.                                                                                      |

| November 2009 | 01.5    | Introduction                        | Updated Embedded SERDES features.                                                                                   |

|               |         |                                     | Added SONET/SDH to Embedded SERDES protocols.                                                                       |

|               |         | Architecture                        | Updated Figure 2-4, General Purpose PLL Diagram.                                                                    |

|               |         |                                     | Updated SONET/SDH to SERDES and PCS protocols.                                                                      |

|               |         |                                     | Updated Table 2-13, SERDES Standard Support to include SONET/<br>SDH and updated footnote 2.                        |

|               |         | DC and Switching<br>Characterisitcs | Added footnote to ESD Performance table.                                                                            |

|               |         |                                     | Updated SERDES Power Supply Requirements table and footnotes.                                                       |

|               |         |                                     | Updated Maximum I/O Buffer Speed table.                                                                             |

|               |         |                                     | Updated Pin-to-Pin Peformance table.                                                                                |

|               |         |                                     | Updated sysCLOCK PLL Timing table.                                                                                  |

|               |         |                                     | Updated DLL timing table.                                                                                           |

|               |         |                                     | Updated High-Speed Data Transmitter tables.                                                                         |

|               |         |                                     | Updated High-Speed Data Receiver table.                                                                             |

|               |         |                                     | Updated footnote for Receiver Total Jitter Tolerance Specification table.                                           |

|               |         |                                     | Updated Periodic Receiver Jitter Tolerance Specification table.                                                     |

|               |         |                                     | Updated SERDES External Reference Clock Specification table.                                                        |

|               |         |                                     | Updated PCI Express Electrical and Timing AC and DC Characteristics.                                                |

|               |         |                                     | Deleted Reference Clock table for PCI Express Electrical and Timing AC and DC Characteristics.                      |

|               |         |                                     | Updated SMPTE AC/DC Characteristics Transmit table.                                                                 |

|               |         |                                     | Updated Mini LVDS table.                                                                                            |

|               |         |                                     | Updated RSDS table.                                                                                                 |

|               |         |                                     | Added Supply Current (Standby) table for EA devices.                                                                |

|               |         |                                     | Updated Internal Switching Characteristics table.                                                                   |

|               |         |                                     | Updated Register-to-Register Performance table.                                                                     |

|               |         |                                     | Added HDMI Electrical and Timing Characteristics data.                                                              |

|               |         |                                     | Updated Family Timing Adders table.                                                                                 |

|               |         |                                     | Updated sysCONFIG Port Timing Specifications table.                                                                 |

|               |         |                                     | Updated Recommended Operating Conditions table.                                                                     |

|               |         |                                     | Updated Hot Socket Specifications table.                                                                            |

|               |         |                                     | Updated Single-Ended DC table.                                                                                      |

|               |         |                                     | Updated TRLVDS table and figure.                                                                                    |

|               |         |                                     | Updated Serial Data Input Specifications table.                                                                     |

|               |         |                                     | Updated HDMI Transmit and Receive table.                                                                            |

|               |         | Ordering Information                | Added LFE3-150EA "TW" devices and footnotes to the Commercial and Industrial tables.                                |

| Date           | Version | Section                             | Change Summary                                                                                                                                                              |

|----------------|---------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2009 | 01.4    | Architecture                        | Corrected link in sysMEM Memory Block section.                                                                                                                              |

|                |         |                                     | Updated information for On-Chip Programmable Termination and modi-<br>fied corresponding figure.                                                                            |

|                |         |                                     | Added footnote 2 to On-Chip Programmable Termination Options for Input Modes table.                                                                                         |

|                |         |                                     | Corrected Per Quadrant Primary Clock Selection figure.                                                                                                                      |

|                | -       | DC and Switching<br>Characteristics | Modified -8 Timing data for 1024x18 True-Dual Port RAM (Read-Before-<br>Write, EBR Output Registers)                                                                        |

|                |         |                                     | Added ESD Performance table.                                                                                                                                                |

|                |         |                                     | LatticeECP3 External Switching Characteristics table - updated data for<br>t <sub>DIBGDDR</sub> , t <sub>W_PRI</sub> , t <sub>W_EDGE</sub> and t <sub>SKEW_EDGE_DQS</sub> . |

|                |         |                                     | LatticeECP3 Internal Switching Characteristics table - updated data for $t_{COO\ PIO}$ and added footnote #4.                                                               |

|                |         |                                     | sysCLOCK PLL Timing table - updated data for f <sub>OUT</sub> .                                                                                                             |

|                |         |                                     | External Reference Clock Specification (refclkp/refclkn) table - updated data for $V_{REF\text{-}IN\text{-}SE}$ and $V_{REF\text{-}IN\text{-}DIFF}$                         |

|                |         |                                     | LatticeECP3 sysCONFIG Port Timing Specifications table - updated data for t <sub>MWC</sub> .                                                                                |

|                |         |                                     | Added TRLVDS DC Specification table and diagram.                                                                                                                            |

|                |         |                                     | Updated Mini LVDS table.                                                                                                                                                    |

| August 2009    | 01.3    | DC and Switching<br>Characteristics | Corrected truncated numbers for $V_{CCIB}$ and $V_{CCOB}$ in Recommended Operating Conditions table.                                                                        |

| July 2009      | 01.2    | Multiple                            | Changed references of "multi-boot" to "dual-boot" throughout the data sheet.                                                                                                |

|                |         | Architecture                        | Updated On-Chip Programmable Termination bullets.                                                                                                                           |

|                |         |                                     | Updated On-Chip Termination Options for Input Modes table.                                                                                                                  |

|                |         |                                     | Updated On-Chip Termination figure.                                                                                                                                         |

|                |         | DC and Switching<br>Characteristics | Changed min/max data for FREF_PPM and added footnote 4 in SERDES External Reference Clock Specification table.                                                              |

|                |         |                                     | Updated SERDES minimum frequency.                                                                                                                                           |

|                |         | Pinout Information                  | Corrected MCLK to be I/O and CCLK to be I in Signal Descriptions table                                                                                                      |

| May 2009       | 01.1    | All                                 | Removed references to Parallel burst mode Flash.                                                                                                                            |

|                |         | Introduction                        | Features - Changed 250 Mbps to 230 Mbps in Embedded SERDES bul-<br>leted section and added a footnote to indicate 230 Mbps applies to<br>8b10b and 10b12b applications.     |

|                |         |                                     | Updated data for ECP3-17 in LatticeECP3 Family Selection Guide table.                                                                                                       |

|                |         |                                     | Changed embedded memory from 552 to 700 Kbits in LatticeECP3<br>Family Selection Guide table.                                                                               |

|                | •       | Architecture                        | Updated description for CLKFB in General Purpose PLL Diagram.                                                                                                               |

|                |         |                                     | Corrected Primary Clock Sources text section.                                                                                                                               |

|                |         |                                     | Corrected Secondary Clock/Control Sources text section.                                                                                                                     |

|                |         |                                     | Corrected Secondary Clock Regions table.                                                                                                                                    |

|                |         |                                     | Corrected note below Detailed sysDSP Slice Diagram.                                                                                                                         |

|                |         |                                     | Corrected Clock, Clock Enable, and Reset Resources text section.                                                                                                            |

|                |         |                                     | Corrected ECP3-17 EBR number in Embedded SRAM in the LatticeECP3 Family table.                                                                                              |

|                |         |                                     | Added On-Chip Termination Options for Input Modes table.                                                                                                                    |

|                |         |                                     | Updated Available SERDES Quads per LatticeECP3 Devices table.                                                                                                               |

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                           |

|---------------|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |         |                                     | Updated Simplified Channel Block Diagram for SERDES/PCS Block diagram.                                                                                                                                                                                                                                                                                   |

|               |         |                                     | Updated Device Configuration text section.                                                                                                                                                                                                                                                                                                               |

|               |         |                                     | Corrected software default value of MCCLK to be 2.5 MHz.                                                                                                                                                                                                                                                                                                 |

|               |         | DC and Switching<br>Characteristics | Updated VCCOB Min/Max data in Recommended Operating Conditions table.                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Corrected footnote 2 in sysIO Recommended Operating Conditions table.                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Added added footnote 7 for t <sub>SKEW_PRIB</sub> to External Switching Characteristics table.                                                                                                                                                                                                                                                           |

|               |         |                                     | Added 2-to-1 Gearing text section and table.                                                                                                                                                                                                                                                                                                             |

|               |         |                                     | Updated External Reference Clock Specification (refclkp/refclkn) table.                                                                                                                                                                                                                                                                                  |

|               |         |                                     | LatticeECP3 sysCONFIG Port Timing Specifications - updated t <sub>DINIT</sub> information.                                                                                                                                                                                                                                                               |

|               |         |                                     | Added sysCONFIG Port Timing waveform.                                                                                                                                                                                                                                                                                                                    |

|               |         |                                     | Serial Input Data Specifications table, delete Typ data for V <sub>RX-DIFF-S</sub> .                                                                                                                                                                                                                                                                     |

|               |         |                                     | Added footnote 4 to sysCLOCK PLL Timing table for t <sub>PFD</sub> .                                                                                                                                                                                                                                                                                     |