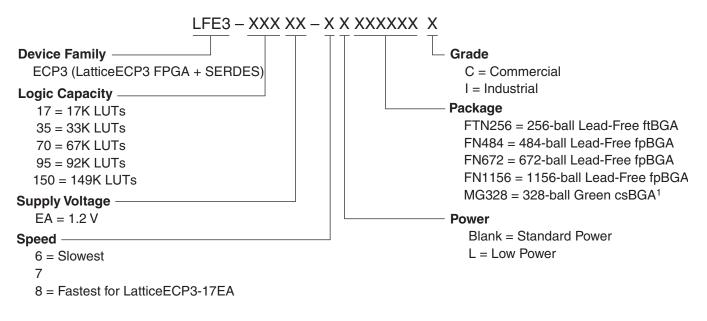

# E: Lattice Semiconductor Corporation - LFE3-95EA-6LFN672I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 11500                                                                         |

| Number of Logic Elements/Cells | 92000                                                                         |

| Total RAM Bits                 | 4526080                                                                       |

| Number of I/O                  | 380                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

| Package / Case                 | 672-BBGA                                                                      |

| Supplier Device Package        | 672-FPBGA (27x27)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-95ea-6lfn672i |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

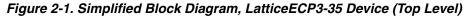

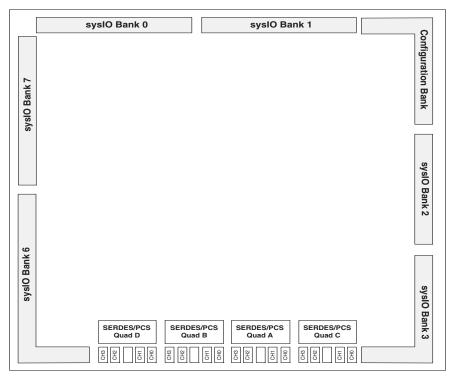

Note: There is no Bank 4 or Bank 5 in LatticeECP3 devices.

# **PFU Blocks**

The core of the LatticeECP3 device consists of PFU blocks, which are provided in two forms, the PFU and PFF. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic and ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

Each PFU block consists of four interconnected slices numbered 0-3 as shown in Figure 2-2. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

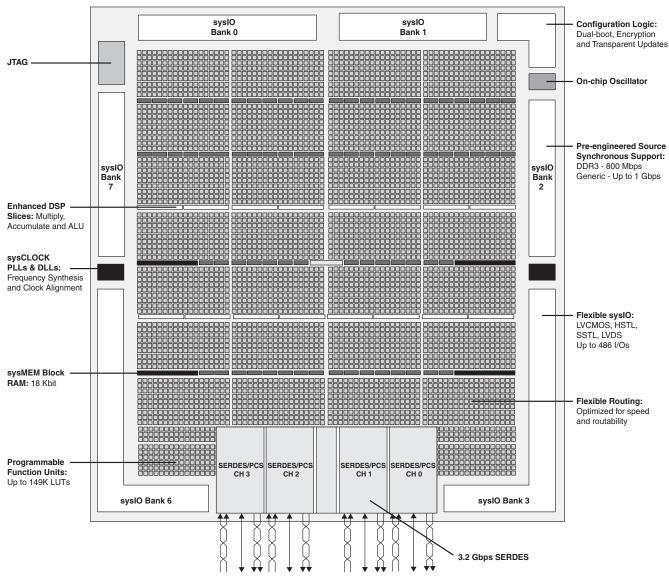

#### Figure 2-8. Clock Divider Connections

## **Clock Distribution Network**

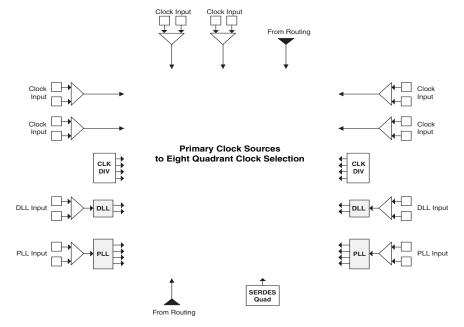

LatticeECP3 devices have eight quadrant-based primary clocks and eight secondary clock/control sources. Two high performance edge clocks are available on the top, left, and right edges of the device to support high speed interfaces. These clock sources are selected from external I/Os, the sysCLOCK PLLs, DLLs or routing. These clock sources are fed throughout the chip via a clock distribution system.

#### **Primary Clock Sources**

LatticeECP3 devices derive clocks from six primary source types: PLL outputs, DLL outputs, CLKDIV outputs, dedicated clock inputs, routing and SERDES Quads. LatticeECP3 devices have two to ten sysCLOCK PLLs and two DLLs, located on the left and right sides of the device. There are six dedicated clock inputs: two on the top side, two on the left side and two on the right side of the device. Figures 2-9, 2-10 and 2-11 show the primary clock sources for LatticeECP3 devices.

#### Figure 2-9. Primary Clock Sources for LatticeECP3-17

Note: Clock inputs can be configured in differential or single-ended mode.

#### Figure 2-31. MULTADDSUBSUM Slice 1

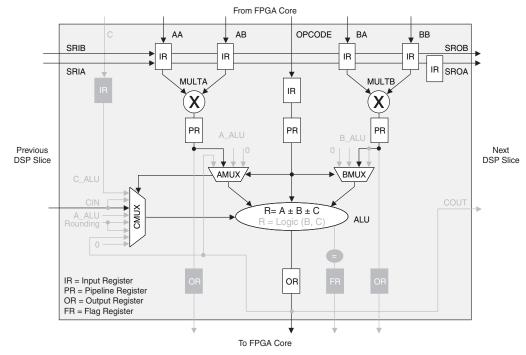

## Advanced sysDSP Slice Features

#### Cascading

The LatticeECP3 sysDSP slice has been enhanced to allow cascading. Adder trees are implemented fully in sys-DSP slices, improving the performance. Cascading of slices uses the signals CIN, COUT and C Mux of the slice.

#### Addition

The LatticeECP3 sysDSP slice allows for the bypassing of multipliers and cascading of adder logic. High performance adder functions are implemented without the use of LUTs. The maximum width adders that can be implemented are 54-bit.

#### Rounding

The rounding operation is implemented in the ALU and is done by adding a constant followed by a truncation operation. The rounding methods supported are:

- Rounding to zero (RTZ)

- Rounding to infinity (RTI)

- Dynamic rounding

- Random rounding

- Convergent rounding

Note: Simplified diagram does not show CE/SET/REST details.

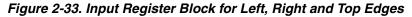

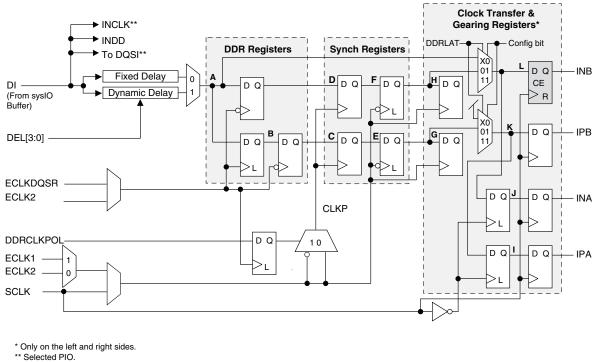

#### Output Register Block

The output register block registers signals from the core of the device before they are passed to the sysl/O buffers. The blocks on the left and right PIOs contain registers for SDR and full DDR operation. The topside PIO block is the same as the left and right sides except it does not support ODDRX2 gearing of output logic. ODDRX2 gearing is used in DDR3 memory interfaces. The PIO blocks on the bottom contain the SDR registers but do not support generic DDR.

Figure 2-34 shows the Output Register Block for PIOs on the left and right edges.

In SDR mode, OPOSA feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a Dtype or latch. In DDR mode, two of the inputs are fed into registers on the positive edge of the clock. At the next clock cycle, one of the registered outputs is also latched.

A multiplexer running off the same clock is used to switch the mux between the 11 and 01 inputs that will then feed the output.

A gearbox function can be implemented in the output register block that takes four data streams: OPOSA, ONEGA, OPOSB and ONEGB. All four data inputs are registered on the positive edge of the system clock and two of them are also latched. The data is then output at a high rate using a multiplexer that runs off the DQCLK0 and DQCLK1 clocks. DQCLK0 and DQCLK1 are used in this case to transfer data from the system clock to the edge clock domain. These signals are generated in the DQS Write Control Logic block. See Figure 2-37 for an overview of the DQS write control logic.

Please see TN1180, LatticeECP3 High-Speed I/O Interface for more information on this topic.

Further discussion on using the DQS strobe in this module is discussed in the DDR Memory section of this data sheet.

Figure 2-40. SERDES/PCS Quads (LatticeECP3-150)

#### Table 2-13. LatticeECP3 SERDES Standard Support

| Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Data Rate<br>(Mbps)                    | Number of<br>General/Link Width | Encoding Style |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|----------------|

| PCI Express 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2500                                   | x1, x2, x4                      | 8b10b          |

| Gigabit Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1250, 2500                             | x1                              | 8b10b          |

| SGMII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1250                                   | x1                              | 8b10b          |

| XAUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3125                                   | x4                              | 8b10b          |

| Serial RapidIO Type I,<br>Serial RapidIO Type II,<br>Serial RapidIO Type III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1250,<br>2500,<br>3125                 | x1, x4                          | 8b10b          |

| CPRI-1,<br>CPRI-2,<br>CPRI-3,<br>CPRI-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 614.4,<br>1228.8,<br>2457.6,<br>3072.0 | x1                              | 8b10b          |

| SD-SDI<br>(259M, 344M)<br>(259M, 344M)<br>(250M, 344M |                                        | x1                              | NRZI/Scrambled |

| HD-SDI<br>(292M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ID-SDI 1483.5,                         |                                 | NRZI/Scrambled |

| 3G-SDI<br>(424M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2967,<br>2970                          | x1                              | NRZI/Scrambled |

| SONET-STS-3 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 155.52                                 | x1                              | N/A            |

| SONET-STS-12 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 622.08                                 | x1                              | N/A            |

| SONET-STS-48 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2488                                   | x1                              | N/A            |

1. For slower rates, the SERDES are bypassed and CML signals are directly connected to the FPGA routing.

2. The SONET protocol is supported in 8-bit SERDES mode. See TN1176 Lattice ECP3 SERDES/PCS Usage Guide for more information.

| MCCLK (MHz)      | MCCLK (MHz)     |

|------------------|-----------------|

|                  | 10              |

| 2.5 <sup>1</sup> | 13              |

| 4.3              | 15 <sup>2</sup> |

| 5.4              | 20              |

| 6.9              | 26              |

| 8.1              | 33 <sup>3</sup> |

| 9.2              |                 |

Table 2-16. Selectable Master Clock (MCCLK) Frequencies During Configuration (Nominal)

1. Software default MCCLK frequency. Hardware default is 3.1 MHz.

2. Maximum MCCLK with encryption enabled.

3. Maximum MCCLK without encryption.

## **Density Shifting**

The LatticeECP3 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the LatticeECP3 Pin Migration Tables and Diamond software for specific restrictions and limitations.

# **DC Electrical Characteristics**

| Symbol                          | Parameter                                | Condition                                                                                                                                                   | Min.           | Тур. | Max.                  | Units |

|---------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-----------------------|-------|

| $I_{\rm IL}, I_{\rm IH}^{1, 4}$ | Input or I/O Low Leakage                 | $0 \le V_{IN} \le (V_{CCIO} - 0.2 \text{ V})$                                                                                                               | —              |      | 10                    | μΑ    |

| I <sub>IH</sub> <sup>1, 3</sup> | Input or I/O High Leakage                | $(V_{CCIO} - 0.2 \text{ V}) < V_{IN} \le 3.6 \text{ V}$                                                                                                     | —              | _    | 150                   | μA    |

| I <sub>PU</sub>                 | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                                                                                             | -30            |      | -210                  | μΑ    |

| I <sub>PD</sub>                 | I/O Active Pull-down Current             | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{CCIO}$                                                                                                                  | 30             |      | 210                   | μΑ    |

| I <sub>BHLS</sub>               | Bus Hold Low Sustaining Current          | $V_{IN} = V_{IL} (MAX)$                                                                                                                                     | 30             |      | —                     | μΑ    |

| I <sub>BHHS</sub>               | Bus Hold High Sustaining Current         | $V_{IN} = 0.7 V_{CCIO}$                                                                                                                                     | -30            | _    | —                     | μΑ    |

| I <sub>BHLO</sub>               | Bus Hold Low Overdrive Current           | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | —              | _    | 210                   | μΑ    |

| I <sub>BHHO</sub>               | Bus Hold High Overdrive Current          | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | —              | _    | -210                  | μA    |

| V <sub>BHT</sub>                | Bus Hold Trip Points                     | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                                                                                             | $V_{IL}$ (MAX) | —    | V <sub>IH</sub> (MIN) | V     |

| C1                              | I/O Capacitance <sup>2</sup>             |                                                                                                                                                             | —              | 5    | 8                     | pf    |

| C2                              | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | —              | 5    | 7                     | pf    |

#### **Over Recommended Operating Conditions**

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

3. Applicable to general purpose I/Os in top and bottom banks. 4. When used as  $V_{REF}$  maximum leakage= 25  $\mu$ A.

# LatticeECP3 Supply Current (Standby)<sup>1, 2, 3, 4, 5, 6</sup>

|                    |                                                                   |             | Турі          | ical       |       |

|--------------------|-------------------------------------------------------------------|-------------|---------------|------------|-------|

| Symbol             | Parameter                                                         | Device      | -6L, -7L, -8L | -6, -7, -8 | Units |

|                    |                                                                   | ECP-17EA    | 29.8          | 49.4       | mA    |

|                    |                                                                   | ECP3-35EA   | 53.7          | 89.4       | mA    |

| I <sub>CC</sub>    | Core Power Supply Current                                         | ECP3-70EA   | 137.3         | 230.7      | mA    |

|                    |                                                                   | ECP3-95EA   | 137.3         | 230.7      | mA    |

|                    |                                                                   | ECP3-150EA  | 219.5         | 370.9      | mA    |

|                    |                                                                   | ECP-17EA    | 18.3          | 19.4       | mA    |

|                    |                                                                   | ECP3-35EA   | 19.6          | 23.1       | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current                                    | ECP3-70EA   | 26.5          | 32.4       | mA    |

|                    |                                                                   | ECP3-95EA   | 26.5          | 32.4       | mA    |

|                    |                                                                   | ECP3-150EA  | 37.0          | 45.7       | mA    |

|                    | PLL Power Supply Current (Per PLL)                                | ECP-17EA    | 0.0           | 0.0        | mA    |

|                    |                                                                   | ECP3-35EA   | 0.1           | 0.1        | mA    |

| I <sub>CCPLL</sub> |                                                                   | ECP3-70EA   | 0.1           | 0.1        | mA    |

|                    |                                                                   | ECP3-95EA   | 0.1           | 0.1        | mA    |

|                    |                                                                   | ECP3-150EA  | 0.1           | 0.1        | mA    |

|                    |                                                                   | ECP-17EA    | 1.3           | 1.4        | mA    |

|                    |                                                                   | ECP3-35EA   | 1.3           | 1.4        | mA    |

| I <sub>CCIO</sub>  | Bank Power Supply Current (Per Bank)                              | ECP3-70EA   | 1.4           | 1.5        | mA    |

|                    |                                                                   | ECP3-95EA   | 1.4           | 1.5        | mA    |

|                    |                                                                   | ECP3-150EA  | 1.4           | 1.5        | mA    |

| I <sub>CCJ</sub>   | JTAG Power Supply Current                                         | All Devices | 2.5           | 2.5        | mA    |

|                    |                                                                   | ECP-17EA    | 6.1           | 6.1        | mA    |

|                    |                                                                   | ECP3-35EA   | 6.1           | 6.1        | mA    |

| I <sub>CCA</sub>   | Transmit, Receive, PLL and<br>Reference Clock Buffer Power Supply | ECP3-70EA   | 18.3          | 18.3       | mA    |

|                    |                                                                   | ECP3-95EA   | 18.3          | 18.3       | mA    |

|                    |                                                                   | ECP3-150EA  | 24.4          | 24.4       | mA    |

#### **Over Recommended Operating Conditions**

1. For further information on supply current, please see the list of technical documentation at the end of this data sheet.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the  $V_{\mbox{CCIO}}$  or GND.

3. Frequency 0 MHz.

4. Pattern represents a "blank" configuration data file.

5.  $T_J = 85$  °C, power supplies at nominal voltage.

6. To determine the LatticeECP3 peak start-up current data, use the Power Calculator tool.

### Register-to-Register Performance<sup>1, 2, 3</sup>

| Function                                             | –8 Timing | Units |

|------------------------------------------------------|-----------|-------|

| 18x18 Multiply/Accumulate (Input & Output Registers) | 200       | MHz   |

| 18x18 Multiply-Add/Sub (All Registers)               | 400       | MHz   |

1. These timing numbers were generated using ispLEVER tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

3. For details on -9 speed grade devices, please contact your Lattice Sales Representative.

# **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond and ispLEVER design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond and ispLEVER design tools can provide logic timing numbers at a particular temperature and voltage.

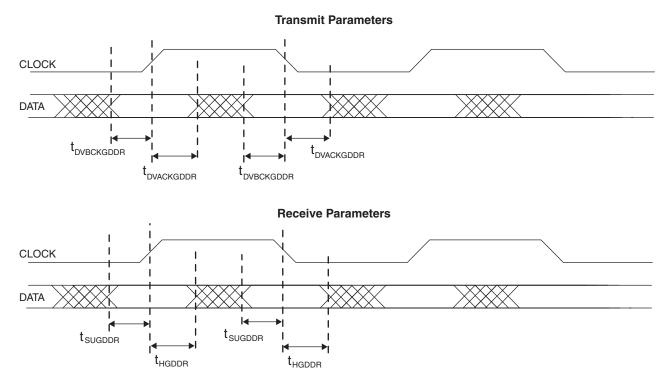

#### Figure 3-8. Generic DDRX1/DDRX2 (With Clock Center on Data Window)

#### Table 3-11. Periodic Receiver Jitter Tolerance Specification

| Description | Frequency  | Condition               | Min. | Тур. | Max. | Units   |

|-------------|------------|-------------------------|------|------|------|---------|

| Periodic    | 2.97 Gbps  | 600 mV differential eye | —    |      | 0.24 | UI, p-p |

| Periodic    | 2.5 Gbps   | 600 mV differential eye | —    | _    | 0.22 | UI, p-p |

| Periodic    | 1.485 Gbps | 600 mV differential eye | —    |      | 0.24 | UI, p-p |

| Periodic    | 622 Mbps   | 600 mV differential eye | —    |      | 0.15 | UI, p-p |

| Periodic    | 150 Mbps   | 600 mV differential eye | _    |      | 0.5  | UI, p-p |

Note: Values are measured with PRBS 2<sup>7</sup>–1, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal, room temperature.

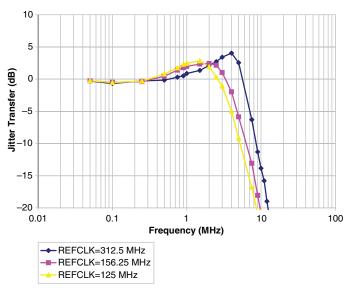

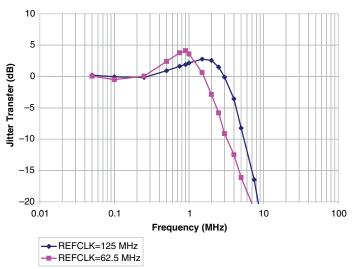

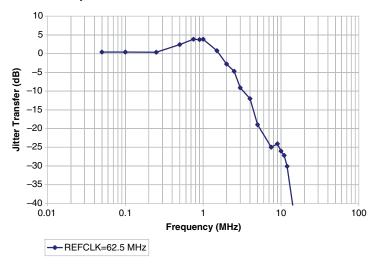

#### Figure 3-14. Jitter Transfer – 3.125 Gbps

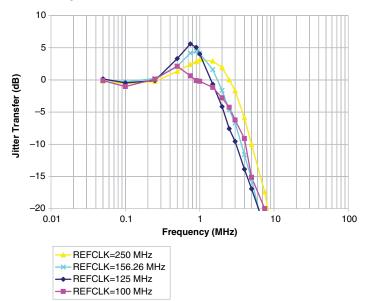

Figure 3-15. Jitter Transfer – 2.5 Gbps

#### Figure 3-16. Jitter Transfer – 1.25 Gbps

Figure 3-17. Jitter Transfer – 622 Mbps

# XAUI/Serial Rapid I/O Type 3/CPRI LV E.30 Electrical and Timing Characteristics

#### **AC and DC Characteristics**

Table 3-13. Transmit

#### **Over Recommended Operating Conditions**

| Symbol                                   | Description                      | <b>Test Conditions</b> | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|------------------------|------|------|------|-------|

| T <sub>RF</sub>                          | Differential rise/fall time      | 20%-80%                |      | 80   | _    | ps    |

| 17_0111_00                               | Differential impedance           |                        | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>2, 3, 4</sup>   | Output data deterministic jitter |                        | _    | _    | 0.17 | UI    |

| J <sub>TX_TJ</sub> <sup>1, 2, 3, 4</sup> | Total output data jitter         |                        | _    | _    | 0.35 | UI    |

1. Total jitter includes both deterministic jitter and random jitter.

2. Jitter values are measured with each CML output AC coupled into a 50-Ohm impedance (100-Ohm differential impedance).

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

4. Values are measured at 2.5 Gbps.

#### Table 3-14. Receive and Jitter Tolerance

#### **Over Recommended Operating Conditions**

| Symbol                                | Description                                   | Test Conditions              | Min. | Тур. | Max. | Units |

|---------------------------------------|-----------------------------------------------|------------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                 | Differential return loss                      | From 100 MHz<br>to 3.125 GHz | 10   | _    | _    | dB    |

| RL <sub>RX_CM</sub>                   | Common mode return loss                       | From 100 MHz<br>to 3.125 GHz | 6    | —    | —    | dB    |

| Z <sub>RX_DIFF</sub>                  | Differential termination resistance           |                              | 80   | 100  | 120  | Ohms  |

| J <sub>RX_DJ</sub> <sup>1, 2, 3</sup> | Deterministic jitter tolerance (peak-to-peak) |                              | —    | —    | 0.37 | UI    |

| J <sub>RX_RJ</sub> <sup>1, 2, 3</sup> | Random jitter tolerance (peak-to-peak)        |                              | —    | —    | 0.18 | UI    |

| J <sub>RX_SJ</sub> <sup>1, 2, 3</sup> | Sinusoidal jitter tolerance (peak-to-peak)    |                              | —    | —    | 0.10 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3</sup> | Total jitter tolerance (peak-to-peak)         |                              | —    | _    | 0.65 | UI    |

| T <sub>RX_EYE</sub>                   | Receiver eye opening                          |                              | 0.35 | —    | —    | UI    |

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-18.

2. Jitter values are measured with each high-speed input AC coupled into a 50-Ohm impedance.

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

4. Jitter tolerance parameters are characterized when Full Rx Equalization is enabled.

5. Values are measured at 2.5 Gbps.

# **Switching Test Conditions**

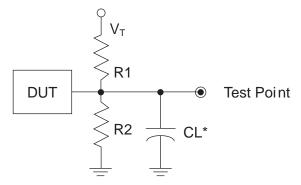

Figure 3-33 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-23.

#### Figure 3-33. Output Test Load, LVTTL and LVCMOS Standards

\*CL Includes Test Fixture and Probe Capacitance

| Test Condition                                   | R <sub>1</sub>                         | R <sub>2</sub> | CL   | Timing Ref.                       | V <sub>T</sub>    |

|--------------------------------------------------|----------------------------------------|----------------|------|-----------------------------------|-------------------|

|                                                  |                                        |                |      | LVCMOS 3.3 = 1.5V                 | —                 |

|                                                  |                                        |                |      | LVCMOS 2.5 = $V_{CCIO}/2$         | —                 |

| LVTTL and other LVCMOS settings (L -> H, H -> L) | $\infty$                               | $\infty$       | 0 pF | LVCMOS 1.8 = V <sub>CCIO</sub> /2 | —                 |

|                                                  |                                        |                |      | LVCMOS 1.5 = V <sub>CCIO</sub> /2 | —                 |

|                                                  |                                        |                |      | LVCMOS 1.2 = V <sub>CCIO</sub> /2 | —                 |

| LVCMOS 2.5 I/O (Z -> H)                          | x                                      | 1MΩ            | 0 pF | V <sub>CCIO</sub> /2              | —                 |

| LVCMOS 2.5 I/O (Z -> L)                          | 1 MΩ                                   | $\infty$       | 0 pF | V <sub>CCIO</sub> /2              | V <sub>CCIO</sub> |

| LVCMOS 2.5 I/O (H -> Z)                          | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 100            | 0 pF | V <sub>OH</sub> - 0.10            | —                 |

| LVCMOS 2.5 I/O (L -> Z)                          | 100                                    | $\infty$       | 0 pF | V <sub>OL</sub> + 0.10            | V <sub>CCIO</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

# LatticeECP3 Family Data Sheet Pinout Information

March 2015

Data Sheet DS1021

# **Signal Descriptions**

| Signal Name                               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                           |     | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                                                                                                                                             |

| P[Edge] [Row/Column Number]_[A/B]         | I/O | [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or B (Bottom), only need to specify Column Number. When Edge is L (Left) or R (Right), only need to specify Row Number.                                                                                                                                                                                                                                                            |

|                                           | 10  | [A/B] indicates the PIO within the PIC to which the pad is connected. Some of these user-programmable pins are shared with special function pins. These pins, when not used as special purpose pins, can be programmed as I/Os for user logic. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration. |

| P[Edge][Row Number]E_[A/B/C/D]            | I   | These general purpose signals are input-only pins and are located near the PLLs.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GSRN                                      | Ι   | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NC                                        |     | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RESERVED                                  |     | This pin is reserved and should not be connected to anything on the board.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND                                       |     | Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>CC</sub>                           | _   | Power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CCAUX</sub>                        |     | Auxiliary power supply pin. This dedicated pin powers all the differential and referenced input buffers.                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>CCIOx</sub>                        | _   | Dedicated power supply pins for I/O bank x.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>CCA</sub>                          | _   | SERDES, transmit, receive, PLL and reference clock buffer power supply. All $V_{CCA}$ supply pins must always be powered to the recommended operating voltage range. If no SERDES channels are used, connect $V_{CCA}$ to $V_{CC}$ .                                                                                                                                                                                                                                                                   |

| V <sub>CCPLL_[LOC]</sub>                  |     | General purpose PLL supply pins where LOC=L (left) or R (right).                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>REF1_x</sub> , V <sub>REF2_x</sub> |     | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{REF}$ inputs. When not used, they may be used as I/O pins.                                                                                                                                                                                                                                                                                                                                                  |

| VTTx                                      |     | Power supply for on-chip termination of I/Os.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XRES <sup>1</sup>                         | _   | 10 kOhm +/-1% resistor must be connected between this pad and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PLL, DLL and Clock Functions              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [LOC][num]_GPLL[T, C]_IN_[index]          | Ι   | General Purpose PLL (GPLL) input pads: LUM, LLM, RUM, RLM, num = row from center, T = true and C = complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                                |

| [LOC][num]_GPLL[T, C]_FB_[index]          | Ι   | Optional feedback GPLL input pads: LUM, LLM, RUM, RLM, num = row from center, T = true and C = complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                                    |

| [LOC]0_GDLLT_IN_[index] <sup>2</sup>      | I/O | General Purpose DLL (GDLL) input pads where LOC=RUM or LUM, T is True Complement, index is A or B.                                                                                                                                                                                                                                                                                                                                                                                                     |

| [LOC]0_GDLLT_FB_[index] <sup>2</sup>      | I/O | Optional feedback GDLL input pads where LOC=RUM or LUM, T is True Complement, index is A or B.                                                                                                                                                                                                                                                                                                                                                                                                         |

| PCLK[T, C][n:0]_[3:0] <sup>2</sup>        | I/O | Primary Clock pads, $T =$ true and $C =$ complement, n per side, indexed by bank and 0, 1, 2, 3 within bank.                                                                                                                                                                                                                                                                                                                                                                                           |

<sup>© 2015</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Pin Information Summary (Cont.)

| Pin Information Summary<br>Pin Type                       |                      | ECP3-70EA |           |            |

|-----------------------------------------------------------|----------------------|-----------|-----------|------------|

|                                                           |                      | 484 fpBGA | 672 fpBGA | 1156 fpBGA |

| Emulated Differential<br>I/O per Bank                     | Bank 0               | 21        | 30        | 43         |

|                                                           | Bank 1               | 18        | 24        | 39         |

|                                                           | Bank 2               | 8         | 12        | 13         |

|                                                           | Bank 3               | 20        | 23        | 33         |

|                                                           | Bank 6               | 22        | 25        | 33         |

|                                                           | Bank 7               | 11        | 16        | 18         |

|                                                           | Bank 8               | 12        | 12        | 12         |

| High-Speed Differential I/<br>O per Bank                  | Bank 0               | 0         | 0         | 0          |

|                                                           | Bank 1               | 0         | 0         | 0          |

|                                                           | Bank 2               | 6         | 9         | 9          |

|                                                           | Bank 3               | 9         | 12        | 16         |

|                                                           | Bank 6               | 11        | 14        | 16         |

|                                                           | Bank 7               | 9         | 12        | 13         |

|                                                           | Bank 8               | 0         | 0         | 0          |

| Total Single-Ended/<br>Total Differential I/O<br>per Bank | Bank 0               | 42/21     | 60/30     | 86/43      |

|                                                           | Bank 1               | 36/18     | 48/24     | 78/39      |

|                                                           | Bank 2               | 28/14     | 42/21     | 44/22      |

|                                                           | Bank 3               | 58/29     | 71/35     | 98/49      |

|                                                           | Bank 6               | 67/33     | 78/39     | 98/49      |

|                                                           | Bank 7               | 40/20     | 56/28     | 62/31      |

|                                                           | Bank 8               | 24/12     | 24/12     | 24/12      |

| DDR Groups Bonded<br>per Bank <sup>1</sup>                | Bank 0               | 3         | 5         | 7          |

|                                                           | Bank 1               | 3         | 4         | 7          |

|                                                           | Bank 2               | 2         | 3         | 3          |

|                                                           | Bank 3               | 3         | 4         | 5          |

|                                                           | Bank 6               | 4         | 4         | 5          |

|                                                           | Bank 7               | 3         | 4         | 4          |

|                                                           | Configuration Bank 8 | 0         | 0         | 0          |

| SERDES Quads                                              |                      | 1         | 2         | 3          |

1. Some DQS groups may not support DQS-12. Refer to the device pinout (.csv) file.

# **Package Pinout Information**