# E. Lattice Semiconductor Corporation - <u>LFE3-95EA-7FN1156I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 11500                                                                         |

| Number of Logic Elements/Cells | 92000                                                                         |

| Total RAM Bits                 | 4526080                                                                       |

| Number of I/O                  | 490                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

| Package / Case                 | 1156-BBGA                                                                     |

| Supplier Device Package        | 1156-FPBGA (35x35)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-95ea-7fn1156i |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeECP3 Family Data Sheet Architecture

June 2013

Data Sheet DS1021

## **Architecture Overview**

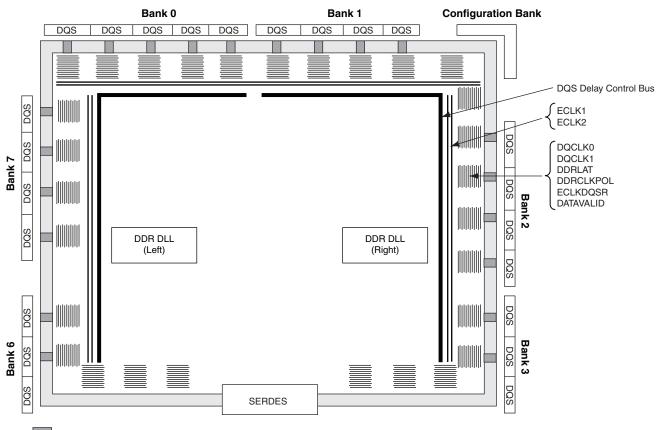

Each LatticeECP3 device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM<sup>™</sup> Embedded Block RAM (EBR) and rows of sys-DSP<sup>™</sup> Digital Signal Processing slices, as shown in Figure 2-1. The LatticeECP3-150 has four rows of DSP slices; all other LatticeECP3 devices have two rows of DSP slices. In addition, the LatticeECP3 family contains SERDES Quads on the bottom of the device.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional Unit without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

The LatticeECP3 devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large, dedicated 18Kbit fast memory blocks. Each sysMEM block can be configured in a variety of depths and widths as RAM or ROM. In addition, LatticeECP3 devices contain up to two rows of DSP slices. Each DSP slice has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

The LatticeECP3 devices feature up to 16 embedded 3.2 Gbps SERDES (Serializer / Deserializer) channels. Each SERDES channel contains independent 8b/10b encoding / decoding, polarity adjust and elastic buffer logic. Each group of four SERDES channels, along with its Physical Coding Sub-layer (PCS) block, creates a quad. The functionality of the SERDES/PCS quads can be controlled by memory cells set during device configuration or by registers that are addressable during device operation. The registers in every quad can be programmed via the SERDES Client Interface (SCI). These quads (up to four) are located at the bottom of the devices.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysl/O buffers. The sysl/O buffers of the LatticeECP3 devices are arranged in seven banks, allowing the implementation of a wide variety of I/O standards. In addition, a separate I/O bank is provided for the programming interfaces. 50% of the PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as XGMII, 7:1 LVDS, along with memory interfaces including DDR3.

The LatticeECP3 registers in PFU and sysI/O can be configured to be SET or RESET. After power up and the device is configured, it enters into user mode with these registers SET/RESET according to the configuration setting, allowing the device entering to a known state for predictable system function.

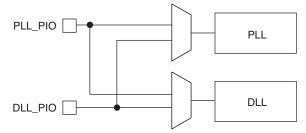

Other blocks provided include PLLs, DLLs and configuration functions. The LatticeECP3 architecture provides two Delay Locked Loops (DLLs) and up to ten Phase Locked Loops (PLLs). The PLL and DLL blocks are located at the end of the EBR/DSP rows.

The configuration block that supports features such as configuration bit-stream decryption, transparent updates and dual-boot support is located toward the center of this EBR row. Every device in the LatticeECP3 family supports a sysCONFIG<sup>™</sup> port located in the corner between banks one and two, which allows for serial or parallel device configuration.

In addition, every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detect capability. The LatticeECP3 devices use 1.2 V as their core voltage.

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### PLL/DLL Cascading

LatticeECP3 devices have been designed to allow certain combinations of PLL and DLL cascading. The allowable combinations are:

- PLL to PLL supported

- PLL to DLL supported

The DLLs in the LatticeECP3 are used to shift the clock in relation to the data for source synchronous inputs. PLLs are used for frequency synthesis and clock generation for source synchronous interfaces. Cascading PLL and DLL blocks allows applications to utilize the unique benefits of both DLLs and PLLs.

For further information about the DLL, please see the list of technical documentation at the end of this data sheet.

### **PLL/DLL PIO Input Pin Connections**

All LatticeECP3 devices contains two DLLs and up to ten PLLs, arranged in quadrants. If a PLL and a DLL are next to each other, they share input pins as shown in the Figure 2-7.

#### Figure 2-7. Sharing of PIO Pins by PLLs and DLLs in LatticeECP3 Devices

Note: Not every PLL has an associated DLL.

## **Clock Dividers**

LatticeECP3 devices have two clock dividers, one on the left side and one on the right side of the device. These are intended to generate a slower-speed system clock from a high-speed edge clock. The block operates in a ÷2, ÷4 or ÷8 mode and maintains a known phase relationship between the divided down clock and the high-speed clock based on the release of its reset signal. The clock dividers can be fed from selected PLL/DLL outputs, the Slave Delay lines, routing or from an external clock input. The clock divider outputs serve as primary clock sources and feed into the clock distribution network. The Reset (RST) control signal resets input and asynchronously forces all outputs to low. The RELEASE signal releases outputs synchronously to the input clock. For further information on clock dividers, please see TN1178, LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide. Figure 2-8 shows the clock divider connections.

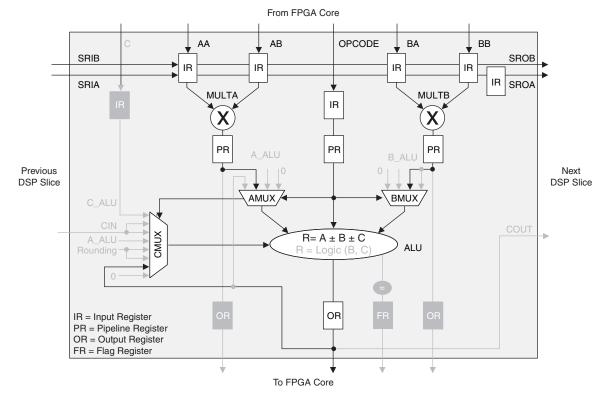

#### MMAC DSP Element

The LatticeECP3 supports a MAC with two multipliers. This is called Multiply Multiply Accumulate or MMAC. In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value and with the result of the multiplier operation of operands BA and BB. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-28 shows the MMAC sysDSP element.

#### Figure 2-28. MMAC sysDSP Element

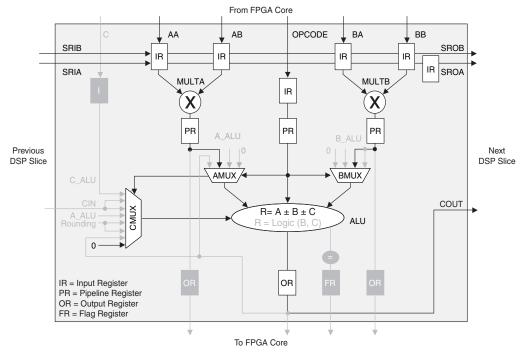

#### MULTADDSUBSUM DSP Element

In this case, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 0. Additionally, the operands AA and AB are multiplied and the result is added/subtracted with the result of the multiplier operation of operands BA and BB of Slice 1. The results of both addition/subtractions are added by the second ALU following the slice cascade path. The user can enable the input, output and pipeline registers. Figure 2-30 and Figure 2-31 show the MULTADDSUBSUM sysDSP element.

#### Figure 2-30. MULTADDSUBSUM Slice 0

#### Figure 2-36. Edge Clock, DLL Calibration and DQS Local Bus Distribution

DQS Strobe and Transition Detect Logic

#### I/O Ring

\*Includes shared configuration I/Os and dedicated configuration I/Os.

# 2. Left and Right (Banks 2, 3, 6 and 7) sysl/O Buffer Pairs (50% Differential and 100% Single-Ended Outputs)

The sysl/O buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. One of the referenced input buffers can also be configured as a differential input. In these banks the two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp (complementary) pad is associated with the negative side of the differential I/O.

In addition, programmable on-chip input termination (parallel or differential, static or dynamic) is supported on these sides, which is required for DDR3 interface. However, there is no support for hot-socketing for the I/O pins located on the left and right side of the device as the PCI clamp is always enabled on these pins.

LVDS, RSDS, PPLVDS and Mini-LVDS differential output drivers are available on 50% of the buffer pairs on the left and right banks.

# 3. Configuration Bank sysl/O Buffer Pairs (Single-Ended Outputs, Only on Shared Pins When Not Used by Configuration)

The sysl/O buffers in the Configuration Bank consist of ratioed single-ended output drivers and single-ended input buffers. This bank does not support PCI clamp like the other banks on the top, left, and right sides.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Programmable PCI clamps are only available on the top banks. PCI clamps are used primarily on inputs and bidirectional pads to reduce ringing on the receiving end.

### Typical sysI/O I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$ ,  $V_{CCIO8}$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all other  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. For more information about controlling the output logic state with valid input logic levels during power-up in LatticeECP3 devices, see the list of technical documentation at the end of this data sheet.

The V<sub>CC</sub> and V<sub>CCAUX</sub> supply the power to the FPGA core fabric, whereas the V<sub>CCIO</sub> supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, it is recommended that the I/O buffers be powered-up prior to the FPGA core fabric. V<sub>CCIO</sub> supplies should be powered-up before or together with the V<sub>CC</sub> and V<sub>CCAUX</sub> supplies.

### Supported sysl/O Standards

The LatticeECP3 sysl/O buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2 V, 1.5 V, 1.8 V, 2.5 V and 3.3 V standards. In the LVCMOS and LVTTL modes, the buffer has individual configuration options for drive strength, slew rates, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL and HSTL. Differential standards supported include LVDS, BLVDS, LVPECL, MLVDS, RSDS, Mini-LVDS, PPLVDS (point-to-point LVDS), TRLVDS (Transition Reduced LVDS), differential SSTL and differential HSTL. For further information on utilizing the sysl/O buffer to support a variety of standards please see TN1177, LatticeECP3 syslO Usage Guide.

Please see TN1177, LatticeECP3 sysIO Usage Guide for on-chip termination usage and value ranges.

### **Equalization Filter**

Equalization filtering is available for single-ended inputs on both true and complementary I/Os, and for differential inputs on the true I/Os on the left, right, and top sides. Equalization is required to compensate for the difficulty of sampling alternating logic transitions with a relatively slow slew rate. It is considered the most useful for the Input DDRX2 modes, used in DDR3 memory, LVDS, or TRLVDS signaling. Equalization filter acts as a tunable filter with settings to determine the level of correction. In the LatticeECP3 devices, there are four settings available: 0 (none), 1, 2 and 3. The default setting is 0. The equalization logic resides in the sysI/O buffers, the two bits of setting is set uniquely in each input IOLOGIC block. Therefore, each sysI/O can have a unique equalization setting within a DQS-12 group.

#### Hot Socketing

LatticeECP3 devices have been carefully designed to ensure predictable behavior during power-up and powerdown. During power-up and power-down sequences, the I/Os remain in tri-state until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled within specified limits. Please refer to the Hot Socketing Specifications in the DC and Switching Characteristics in this data sheet.

## SERDES and PCS (Physical Coding Sublayer)

LatticeECP3 devices feature up to 16 channels of embedded SERDES/PCS arranged in quads at the bottom of the devices supporting up to 3.2Gbps data rate. Figure 2-40 shows the position of the quad blocks for the LatticeECP3-150 devices. Table 2-14 shows the location of available SERDES Quads for all devices.

The LatticeECP3 SERDES/PCS supports a range of popular serial protocols, including:

- PCI Express 1.1

- Ethernet (XAUI, GbE 1000 Base CS/SX/LX and SGMII)

- Serial RapidIO

- SMPTE SDI (3G, HD, SD)

- CPRI

- SONET/SDH (STS-3, STS-12, STS-48)

Each quad contains four dedicated SERDES for high speed, full duplex serial data transfer. Each quad also has a PCS block that interfaces to the SERDES channels and contains protocol specific digital logic to support the standards listed above. The PCS block also contains interface logic to the FPGA fabric. All PCS logic for dedicated protocol support can also be bypassed to allow raw 8-bit or 10-bit interfaces to the FPGA fabric.

Even though the SERDES/PCS blocks are arranged in quads, multiple baud rates can be supported within a quad with the use of dedicated, per channel  $\div$ 1,  $\div$ 2 and  $\div$ 11 rate dividers. Additionally, multiple quads can be arranged together to form larger data pipes.

For information on how to use the SERDES/PCS blocks to support specific protocols, as well on how to combine multiple protocols and baud rates within a device, please refer to TN1176, LatticeECP3 SERDES/PCS Usage Guide.

| MCCLK (MHz)      | MCCLK (MHz)     |

|------------------|-----------------|

|                  | 10              |

| 2.5 <sup>1</sup> | 13              |

| 4.3              | 15 <sup>2</sup> |

| 5.4              | 20              |

| 6.9              | 26              |

| 8.1              | 33 <sup>3</sup> |

| 9.2              |                 |

Table 2-16. Selectable Master Clock (MCCLK) Frequencies During Configuration (Nominal)

1. Software default MCCLK frequency. Hardware default is 3.1 MHz.

2. Maximum MCCLK with encryption enabled.

3. Maximum MCCLK without encryption.

## **Density Shifting**

The LatticeECP3 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the LatticeECP3 Pin Migration Tables and Diamond software for specific restrictions and limitations.

## Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol  | Parameter                                     | Condition                                 | Min. | Тур. | Max. | Units |

|---------|-----------------------------------------------|-------------------------------------------|------|------|------|-------|

| IDK_HS⁴ | Input or I/O Leakage Current                  | $0 \le V_{IN} \le V_{IH}$ (Max.)          |      |      | +/-1 | mA    |

| IDK⁵    | JK <sup>o</sup> Linput or I/O Leakage Current | $0 \le V_{IN} < V_{CCIO}$                 |      |      | +/-1 | mA    |

|         |                                               | $V_{CCIO} \le V_{IN} \le V_{CCIO} + 0.5V$ | _    | 18   | _    | mA    |

1.  $V_{CC},\,V_{CCAUX}$  and  $V_{CCIO}$  should rise/fall monotonically.

2.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ .

3. LVCMOS and LVTTL only.

4. Applicable to general purpose I/O pins located on the top and bottom sides of the device.

5. Applicable to general purpose I/O pins located on the left and right sides of the device.

## Hot Socketing Requirements<sup>1, 2</sup>

| Description                                                                     | Min. | Тур. | Max. | Units |

|---------------------------------------------------------------------------------|------|------|------|-------|

| Input current per SERDES I/O pin when device is powered down and inputs driven. | _    | -    | 8    | mA    |

1. Assumes the device is powered down, all supplies grounded, both P and N inputs driven by CML driver with maximum allowed VCCOB (1.575 V), 8b10b data, internal AC coupling.

2. Each P and N input must have less than the specified maximum input current. For a 16-channel device, the total input current would be 8 mA\*16 channels \*2 input pins per channel = 256 mA

## **ESD** Performance

Please refer to the LatticeECP3 Product Family Qualification Summary for complete qualification data, including ESD performance.

# SERDES Power Supply Requirements<sup>1, 2, 3</sup>

| Symbol               | Description                            | Тур. | Max. | Units |

|----------------------|----------------------------------------|------|------|-------|

| Standby (Power I     | Down)                                  | •    |      |       |

| I <sub>CCA-SB</sub>  | V <sub>CCA</sub> current (per channel) | 3    | 5    | mA    |

| I <sub>CCIB-SB</sub> | Input buffer current (per channel)     | —    | —    | mA    |

| I <sub>CCOB-SB</sub> | Output buffer current (per channel)    | —    | —    | mA    |

| Operating (Data F    | Rate = 3.2 Gbps)                       |      |      | •     |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 68   | 77   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 5    | 7    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 19   | 25   | mA    |

| Operating (Data F    | Rate = 2.5 Gbps)                       |      |      | •     |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 66   | 76   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 15   | 18   | mA    |

| Operating (Data F    | Rate = 1.25 Gbps)                      |      |      | •     |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 62   | 72   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 15   | 18   | mA    |

| Operating (Data I    | Rate = 250 Mbps)                       | •    |      |       |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 55   | 65   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 14   | 17   | mA    |

| Operating (Data F    | Rate = 150 Mbps)                       | •    | •    | •     |

| I <sub>CCA-OP</sub>  | V <sub>CCA</sub> current (per channel) | 55   | 65   | mA    |

| I <sub>CCIB-OP</sub> | Input buffer current (per channel)     | 4    | 5    | mA    |

| I <sub>CCOB-OP</sub> | Output buffer current (per channel)    | 14   | 17   | mA    |

1. Equalization enabled, pre-emphasis disabled.

2. One quarter of the total quad power (includes contribution from common circuits, all channels in the quad operating, pre-emphasis disabled, equalization enabled).

3. Pre-emphasis adds 20 mA to ICCA-OP data.

## **Typical Building Block Function Performance**

## Pin-to-Pin Performance (LVCMOS25 12 mA Drive)<sup>1, 2, 3</sup>

| Function        | –8 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions | ł         |       |

| 16-bit Decoder  | 4.7       | ns    |

| 32-bit Decoder  | 4.7       | ns    |

| 64-bit Decoder  | 5.7       | ns    |

| 4:1 MUX         | 4.1       | ns    |

| 8:1 MUX         | 4.3       | ns    |

| 16:1 MUX        | 4.7       | ns    |

| 32:1 MUX        | 4.8       | ns    |

1. These functions were generated using the ispLEVER design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond or ispLEVER software.

#### Register-to-Register Performance<sup>1, 2, 3</sup>

| Function                                                                   | –8 Timing | Units |

|----------------------------------------------------------------------------|-----------|-------|

| Basic Functions                                                            |           |       |

| 16-bit Decoder                                                             | 500       | MHz   |

| 32-bit Decoder                                                             | 500       | MHz   |

| 64-bit Decoder                                                             | 500       | MHz   |

| 4:1 MUX                                                                    | 500       | MHz   |

| 8:1 MUX                                                                    | 500       | MHz   |

| 16:1 MUX                                                                   | 500       | MHz   |

| 32:1 MUX                                                                   | 445       | MHz   |

| 8-bit adder                                                                | 500       | MHz   |

| 16-bit adder                                                               | 500       | MHz   |

| 64-bit adder                                                               | 305       | MHz   |

| 16-bit counter                                                             | 500       | MHz   |

| 32-bit counter                                                             | 460       | MHz   |

| 64-bit counter                                                             | 320       | MHz   |

| 64-bit accumulator                                                         | 315       | MHz   |

| Embedded Memory Functions                                                  | · · ·     |       |

| 512x36 Single Port RAM, EBR Output Registers                               | 340       | MHz   |

| 1024x18 True-Dual Port RAM (Write Through or Normal, EBR Output Registers) | 340       | MHz   |

| 1024x18 True-Dual Port RAM (Read-Before-Write, EBR Output Registers        | 130       | MHz   |

| 1024x18 True-Dual Port RAM (Write Through or Normal, PLC Output Registers) | 245       | MHz   |

| Distributed Memory Functions                                               | <b>i</b>  |       |

| 16x4 Pseudo-Dual Port RAM (One PFU)                                        | 500       | MHz   |

| 32x4 Pseudo-Dual Port RAM                                                  | 500       | MHz   |

| 64x8 Pseudo-Dual Port RAM                                                  | 400       | MHz   |

| DSP Function                                                               | · · ·     |       |

| 18x18 Multiplier (All Registers)                                           | 400       | MHz   |

| 9x9 Multiplier (All Registers)                                             | 400       | MHz   |

| 36x36 Multiply (All Registers)                                             | 260       | MHz   |

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                         |                                                 |                                  | _          | -8       | -        | -7        | _        | 6         |           |

|-------------------------|-------------------------------------------------|----------------------------------|------------|----------|----------|-----------|----------|-----------|-----------|

| Parameter               | Description                                     | Device                           | Min.       | Max.     | Min.     | Max.      | Min.     | Max.      | Units     |

|                         | nputs with Clock and Data (>10bi                | its wide) are Aligned at I       | Pin (GDD   | RX2_RX   | ECLK.A   | ligned)   |          |           |           |

| (No CLKDIV)             | des Using DLLCLKPIN for Clock                   | Innut                            |            |          |          |           |          |           |           |

|                         | Data Setup Before CLK                           | ECP3-150EA                       | _          | 0.225    | _        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVACLKGDDR</sub> | Data Hold After CLK                             | ECP3-150EA                       | 0.775      | 0.225    | 0.775    | 0.225     | 0.775    | 0.225     | UI        |

|                         | DDRX2 Clock Frequency                           | ECP3-150EA                       | 0.775      | 460      | 0.775    | 385       | 0.775    | 345       | MHz       |

| <sup>†</sup> MAX_GDDR   | Data Setup Before CLK                           |                                  | _          |          | _        |           | _        |           | UI        |

|                         | -                                               | ECP3-70EA/95EA                   | 0.775      | 0.225    |          | 0.225     |          | 0.225     |           |

| <sup>I</sup> DVECLKGDDR | Data Hold After CLK                             | ECP3-70EA/95EA<br>ECP3-70EA/95EA | 0.775      |          | 0.775    |           | 0.775    |           | UI<br>MHz |

| fMAX_GDDR               | DDRX2 Clock Frequency                           |                                  | —          | 460      |          | 385       | —        | 311       |           |

|                         | Data Setup Before CLK                           | ECP3-35EA                        | - 700      | 0.210    | -        | 0.210     | -        | 0.210     |           |

|                         | Data Hold After CLK                             | ECP3-35EA                        | 0.790      | -        | 0.790    | -         | 0.790    | _         | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-35EA                        | _          | 460      | _        | 385       | _        | 311       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK<br>(Left and Right Sides) | ECP3-17EA                        | _          | 0.210    | _        | 0.210     | _        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-17EA                        | 0.790      | —        | 0.790    | —         | 0.790    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-17EA                        | _          | 460      |          | 385       |          | 311       | MHz       |

| Top Side Using P        | CLK Pin for Clock Input                         |                                  |            |          |          |           |          |           |           |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-150EA                       |            | 0.225    | —        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-150EA                       | 0.775      | —        | 0.775    | —         | 0.775    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-150EA                       | _          | 235      | —        | 170       | _        | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-70EA/95EA                   | _          | 0.225    |          | 0.225     |          | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-70EA/95EA                   | 0.775      |          | 0.775    |           | 0.775    |           | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-70EA/95EA                   | _          | 235      |          | 170       |          | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-35EA                        |            | 0.210    | —        | 0.210     | _        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-35EA                        | 0.790      | —        | 0.790    | —         | 0.790    | _         | UI        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-35EA                        | _          | 235      | —        | 170       | _        | 130       | MHz       |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | ECP3-17EA                        | _          | 0.210    | —        | 0.210     | —        | 0.210     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | ECP3-17EA                        | 0.790      | _        | 0.790    | _         | 0.790    | —         | UI        |

| f <sub>MAX GDDR</sub>   | DDRX2 Clock Frequency                           | ECP3-17EA                        | _          | 235      | _        | 170       |          | 130       | MHz       |

| -                       | nputs with Clock and Data (<10 E                | Bits Wide) Centered at Pi        | in (GDDF   | X2_RX.   | DQS.Cen  | tered) U  | sing DQ  | S Pin for | Clock     |

| Left and Right Sid      | des                                             |                                  |            |          |          |           |          |           |           |

| t <sub>SUGDDR</sub>     | Data Setup Before CLK                           | All ECP3EA Devices               | 330        | _        | 330      | _         | 352      |           | ps        |

| t <sub>HOGDDR</sub>     | Data Hold After CLK                             | All ECP3EA Devices               | 330        | _        | 330      | —         | 352      | _         | ps        |

| f <sub>MAX_GDDR</sub>   | DDRX2 Clock Frequency                           | All ECP3EA Devices               | _          | 400      | _        | 400       | _        | 375       | MHz       |

|                         | nputs with Clock and Data (<10 E                | Bits Wide) Aligned at Pin        | (GDDR)     | (2 RX.D0 | QS.Align | ed) Usin  | g DQS Pi | n for Clo | ck Input  |

| Left and Right Sid      |                                                 | <b>J J J J J J J J J J</b>       | <b>1</b> - | _        | <b>J</b> | . ,       | <b>J</b> |           |           |

| t <sub>DVACLKGDDR</sub> | Data Setup Before CLK                           | All ECP3EA Devices               | —          | 0.225    | —        | 0.225     | _        | 0.225     | UI        |

| t <sub>DVECLKGDDR</sub> | Data Hold After CLK                             | All ECP3EA Devices               | 0.775      | _        | 0.775    | _         | 0.775    | —         | UI        |

| f <sub>MAX GDDR</sub>   | DDRX2 Clock Frequency                           | All ECP3EA Devices               | _          | 400      | _        | 400       | _        | 375       | MHz       |

|                         | Output with Clock and Data (>10 I               | Bits Wide) Centered at P         | in (GDD    | RX1_TX.  | SCLK.Ce  | ntered)10 | )        |           | 1         |

| t <sub>DVBGDDR</sub>    | Data Valid Before CLK                           | ECP3-150EA                       | 670        | —        | 670      | _         | 670      |           | ps        |

| t <sub>DVAGDDR</sub>    | Data Valid After CLK                            | ECP3-150EA                       | 670        |          | 670      |           | 670      |           | ps        |

| f <sub>MAX_GDDR</sub>   | DDRX1 Clock Frequency                           | ECP3-150EA                       |            | 250      |          | 250       |          | 250       | MHz       |

|                         |                                                 |                                  | 666        |          | CCE      |           | 664      |           |           |

| t <sub>DVBGDDR</sub>    | Data Valid Before CLK                           | ECP3-70EA/95EA                   | 666        |          | 665      |           | 664      |           | ps        |

## Over Recommended Commercial Operating Conditions

# LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                       |                                 |                             | _        | -8                   | -       | -7                    |        | 6        |                 |

|-----------------------|---------------------------------|-----------------------------|----------|----------------------|---------|-----------------------|--------|----------|-----------------|

| Parameter             | Description                     | Device                      | Min.     | Max.                 | Min.    | Max.                  | Min.   | Max.     | Units           |

| f <sub>MAX GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA              | _        | 250                  | _       | 250                   |        | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-35EA                   | 683      | _                    | 688     | _                     | 690    | _        | ps              |

| tDVAGDDR              | Data Valid After CLK            | ECP3-35EA                   | 683      | _                    | 688     | _                     | 690    | _        | ps              |

| fMAX GDDR             | DDRX1 Clock Frequency           | ECP3-35EA                   |          | 250                  |         | 250                   |        | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-17EA                   | 683      |                      | 688     |                       | 690    |          | ps              |

|                       | Data Valid After CLK            | ECP3-17EA                   | 683      | <u> </u>             | 688     | —                     | 690    | <u> </u> | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-17EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Dutput with Clock and Data Alig | ned at Pin (GDDRX1_TX.S     | SCLK.Ali | igned) <sup>10</sup> |         |                       |        |          |                 |

|                       | Data Invalid Before Clock       | ECP3-150EA                  |          | 335                  |         | 338                   |        | 341      | ps              |

|                       | Data Invalid After Clock        | ECP3-150EA                  |          | 335                  |         | 338                   | _      | 341      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA                  |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-70EA/95EA              |          | 339                  |         | 343                   |        | 347      | ps              |

| t <sub>DIAGDDR</sub>  | Data Invalid After Clock        | ECP3-70EA/95EA              |          | 339                  | _       | 343                   |        | 347      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-70EA/95EA              |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-35EA                   |          | 322                  |         | 320                   |        | 321      | ps              |

|                       | Data Invalid After Clock        | ECP3-35EA                   |          | 322                  |         | 320                   | _      | 321      | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                   |          | 250                  |         | 250                   | _      | 250      | MHz             |

|                       | Data Invalid Before Clock       | ECP3-17EA                   | _        | 322                  | _       | 320                   | _      | 321      | ps              |

|                       | Data Invalid After Clock        | ECP3-17EA                   |          | 322                  |         | 320                   | _      | 321      | ps              |

| fMAX GDDR             | DDRX1 Clock Frequency           | ECP3-17EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

| -                     | Dutput with Clock and Data (<10 | ) Bits Wide) Centered at P  | in (GDD  | RX1_TX.              | DQS.Cer | ntered) <sup>10</sup> |        |          |                 |

| Left and Right Si     |                                 |                             | -        |                      |         | -                     |        |          |                 |

| t <sub>DVBGDDR</sub>  | Data Valid Before CLK           | ECP3-150EA                  | 670      | —                    | 670     | _                     | 670    | —        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-150EA                  | 670      | _                    | 670     | _                     | 670    | _        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-150EA                  |          | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-70EA/95EA              | 657      | _                    | 652     | _                     | 650    | _        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-70EA/95EA              | 657      | _                    | 652     | _                     | 650    | _        | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-70EA/95EA              |          | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-35EA                   | 670      | —                    | 675     | _                     | 676    | —        | ps              |

|                       | Data Valid After CLK            | ECP3-35EA                   | 670      | _                    | 675     | _                     | 676    | _        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX1 Clock Frequency           | ECP3-35EA                   | _        | 250                  | _       | 250                   | _      | 250      | MHz             |

|                       | Data Valid Before CLK           | ECP3-17EA                   | 670      | —                    | 670     | _                     | 670    | —        | ps              |

| t <sub>DVAGDDR</sub>  | Data Valid After CLK            | ECP3-17EA                   | 670      | _                    | 670     | _                     | 670    | _        | ps              |

| f <sub>MAX</sub> GDDR | DDRX1 Clock Frequency           | ECP3-17EA                   |          | 250                  | _       | 250                   | _      | 250      | MHz             |

| -                     | Dutput with Clock and Data (>10 | ) Bits Wide) Aligned at Pir | n (GDDR  | X2_TX.A              | ligned) |                       |        |          | 1               |

| Left and Right Si     | des                             |                             |          |                      |         |                       |        |          |                 |

| t <sub>DIBGDDR</sub>  | Data Invalid Before Clock       | All ECP3EA Devices          |          | 200                  |         | 210                   |        | 220      | ps              |

| tDIAGDDR              | Data Invalid After Clock        | All ECP3EA Devices          |          | 200                  |         | 210                   | _      | 220      | ps              |

| f <sub>MAX</sub> GDDR | DDRX2 Clock Frequency           | All ECP3EA Devices          | _        | 500                  | _       | 420                   |        | 375      | MHz             |

| -                     | Dutput with Clock and Data (>10 | ) Bits Wide) Centered at P  | in Using | g DQSDL              | L (GDDF | X2_TX.D               | QSDLL. | Centered | ) <sup>11</sup> |

| Left and Right Si     | des                             |                             |          |                      |         |                       |        |          |                 |

|                       | Data Valid Before CLK           | All ECP3EA Devices          | 400      | —                    | 400     | —                     | 431    | —        | ps              |

| tDVAGDDR              | Data Valid After CLK            | All ECP3EA Devices          | 400      | _                    | 400     |                       | 432    | —        | ps              |

| f <sub>MAX_GDDR</sub> | DDRX2 Clock Frequency           | All ECP3EA Devices          | _        | 400                  |         | 400                   | _      | 375      | MHz             |

### **Over Recommended Commercial Operating Conditions**

## Serial Rapid I/O Type 2/CPRI LV E.24 Electrical and Timing Characteristics

### **AC and DC Characteristics**

#### Table 3-15. Transmit

| Symbol                                   | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|----------------------------------|-----------------|------|------|------|-------|

| T <sub>RF</sub> <sup>1</sup>             | Differential rise/fall time      | 20%-80%         |      | 80   | —    | ps    |

| Z <sub>TX_DIFF_DC</sub>                  | Differential impedance           |                 | 80   | 100  | 120  | Ohms  |

| J <sub>TX_DDJ</sub> <sup>3, 4, 5</sup>   | Output data deterministic jitter |                 |      | —    | 0.17 | UI    |

| J <sub>TX_TJ</sub> <sup>2, 3, 4, 5</sup> | Total output data jitter         |                 | _    | —    | 0.35 | UI    |

1. Rise and Fall times measured with board trace, connector and approximately 2.5pf load.

2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

3. Jitter values are measured with each CML output AC coupled into a 50-Ohm impedance (100-Ohm differential impedance).

4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

5. Values are measured at 2.5 Gbps.

#### Table 3-16. Receive and Jitter Tolerance

| Symbol                                      | Description                                   | Test Conditions         | Min. | Тур. | Max. | Units |

|---------------------------------------------|-----------------------------------------------|-------------------------|------|------|------|-------|

| RL <sub>RX_DIFF</sub>                       | Differential return loss                      | From 100 MHz to 2.5 GHz | 10   | _    | _    | dB    |

| RL <sub>RX_CM</sub>                         | Common mode return loss                       | From 100 MHz to 2.5 GHz | 6    | _    | _    | dB    |

| Z <sub>RX_DIFF</sub>                        | Differential termination resistance           |                         | 80   | 100  | 120  | Ohms  |

| J <sub>RX_DJ</sub> <sup>2, 3, 4, 5</sup>    | Deterministic jitter tolerance (peak-to-peak) |                         | _    | _    | 0.37 | UI    |

| J <sub>RX_RJ</sub> <sup>2, 3, 4, 5</sup>    | Random jitter tolerance (peak-to-peak)        |                         | _    | _    | 0.18 | UI    |

| J <sub>RX_SJ</sub> <sup>2, 3, 4, 5</sup>    | Sinusoidal jitter tolerance (peak-to-peak)    |                         | _    | _    | 0.10 | UI    |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4, 5</sup> | Total jitter tolerance (peak-to-peak)         |                         | _    | —    | 0.65 | UI    |

| T <sub>RX_EYE</sub>                         | Receiver eye opening                          |                         | 0.35 | _    | —    | UI    |

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter. The sinusoidal jitter tolerance mask is shown in Figure 3-18.

2. Jitter values are measured with each high-speed input AC coupled into a 50-Ohm impedance.

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

5. Values are measured at 2.5 Gbps.

## **Signal Descriptions (Cont.)**

| I/O | Description                                                                            |

|-----|----------------------------------------------------------------------------------------|

| I/O | Parallel configuration I/O. SPI/SPIm data input. Open drain during configura-<br>tion. |

| I/O | Serial data input for slave serial mode. SPI/SPIm mode chip select.                    |

|     |                                                                                        |

| I   | High-speed input, negative channel m                                                   |

| 0   | High-speed output, negative channel m                                                  |

| I   | Negative Reference Clock Input                                                         |

| I   | High-speed input, positive channel m                                                   |

| 0   | High-speed output, positive channel m                                                  |

| I   | Positive Reference Clock Input                                                         |

| —   | Output buffer power supply, channel m (1.2V/1.5)                                       |

|     | Input buffer power supply, channel m (1.2V/1.5V)                                       |

|     | I/O<br>I/O<br>I<br>I<br>I<br>I<br>I<br>I                                               |

1. When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

2. These pins are dedicated inputs or can be used as general purpose I/O.

3. m defines the associated channel in the quad.

## **Pin Information Summary**

| Pin Information                            | Summary | E            | CP3-17E      | A            | E            | CP3-35E      | A            | E            | CP3-70E      | A             |

|--------------------------------------------|---------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Pin Tyr                                    | De      | 256<br>ftBGA | 328<br>csBGA | 484<br>fpBGA | 256<br>ftBGA | 484<br>fpBGA | 672<br>fpBGA | 484<br>fpBGA | 672<br>fpBGA | 1156<br>fpBGA |

|                                            | Bank 0  | 26           | 20           | 36           | 26           | 42           | 48           | 42           | 60           | 86            |

|                                            | Bank 1  | 14           | 10           | 24           | 14           | 36           | 36           | 36           | 48           | 78            |

|                                            | Bank 2  | 6            | 7            | 12           | 6            | 24           | 24           | 24           | 34           | 36            |

| General Purpose<br>Inputs/Outputs per Bank | Bank 3  | 18           | 12           | 44           | 16           | 54           | 59           | 54           | 59           | 86            |

|                                            | Bank 6  | 20           | 11           | 44           | 18           | 63           | 61           | 63           | 67           | 86            |

|                                            | Bank 7  | 19           | 26           | 32           | 19           | 36           | 42           | 36           | 48           | 54            |

|                                            | Bank 8  | 24           | 24           | 24           | 24           | 24           | 24           | 24           | 24           | 24            |

|                                            | Bank 0  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 1  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 2  | 2            | 2            | 2            | 2            | 4            | 4            | 4            | 8            | 8             |

| General Purpose Inputs per Bank            | Bank 3  | 0            | 0            | 0            | 2            | 4            | 4            | 4            | 12           | 12            |

| per Darik                                  | Bank 6  | 0            | 0            | 0            | 2            | 4            | 4            | 4            | 12           | 12            |

|                                            | Bank 7  | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 8            | 8             |

|                                            | Bank 8  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 0  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 1  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 2  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| General Purpose Out-                       | Bank 3  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| puts per Bank                              | Bank 6  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 7  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

|                                            | Bank 8  | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0             |

| Total Single-Ended User                    | I/O     | 133          | 116          | 222          | 133          | 295          | 310          | 295          | 380          | 490           |

| VCC                                        |         | 6            | 16           | 16           | 6            | 16           | 32           | 16           | 32           | 32            |

| VCCAUX                                     |         | 4            | 5            | 8            | 4            | 8            | 12           | 8            | 12           | 16            |

| VTT                                        |         | 4            | 7            | 4            | 4            | 4            | 4            | 4            | 4            | 8             |

| VCCA                                       |         | 4            | 6            | 4            | 4            | 4            | 8            | 4            | 8            | 16            |

| VCCPLL                                     |         | 2            | 2            | 4            | 2            | 4            | 4            | 4            | 4            | 4             |

|                                            | Bank 0  | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 1  | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 2  | 2            | 2            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

| VCCIO                                      | Bank 3  | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 6  | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 7  | 2            | 3            | 2            | 2            | 2            | 4            | 2            | 4            | 4             |

|                                            | Bank 8  | 1            | 2            | 2            | 1            | 2            | 2            | 2            | 2            | 2             |

| VCCJ                                       |         | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1             |

| TAP                                        |         | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 4            | 4             |

| GND, GNDIO                                 |         | 51           | 126          | 98           | 51           | 98           | 139          | 98           | 139          | 233           |

| NC                                         |         | 0            | 0            | 73           | 0            | 0            | 96           | 0            | 0            | 238           |

| Reserved <sup>1</sup>                      |         | 0            | 0            | 2            | 0            | 2            | 2            | 2            | 2            | 2             |

| SERDES                                     |         | 26           | 18           | 26           | 26           | 26           | 26           | 26           | 52           | 78            |

| Miscellaneous Pins                         |         | 8            | 8            | 8            | 8            | 8            | 8            | 8            | 8            | 8             |

| Total Bonded Pins                          |         | 256          | 328          | 484          | 256          | 484          | 672          | 484          | 672          | 1156          |

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-7FN484C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-8FN484C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-6LFN484C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-7LFN484C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-8LFN484C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | COM   | 67       |

| LFE3-70EA-6FN672C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-7FN672C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-8FN672C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-6LFN672C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-7LFN672C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-8LFN672C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | COM   | 67       |

| LFE3-70EA-6FN1156C  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-7FN1156C  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-8FN1156C  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-6LFN1156C | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-7LFN1156C | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

| LFE3-70EA-8LFN1156C | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 67       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-7FN484C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-8FN484C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-6LFN484C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-7LFN484C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-8LFN484C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | COM   | 92       |

| LFE3-95EA-6FN672C   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-7FN672C   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-8FN672C   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-6LFN672C  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-7LFN672C  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-8LFN672C  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | COM   | 92       |

| LFE3-95EA-6FN1156C  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-7FN1156C  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-8FN1156C  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-6LFN1156C | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-7LFN1156C | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

| LFE3-95EA-8LFN1156C | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | COM   | 92       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

#### Industrial

The following devices may have associated errata. Specific devices with associated errata will be notated with a footnote.

| Part Number         | Voltage | Grade | Power | Package <sup>1</sup> | Pins | Temp. | LUTs (K) |

|---------------------|---------|-------|-------|----------------------|------|-------|----------|

| LFE3-17EA-6FTN256I  | 1.2 V   | -6    | STD   | Lead-Free ftBGA      | 256  | IND   | 17       |

| LFE3-17EA-7FTN256I  | 1.2 V   | -7    | STD   | Lead-Free ftBGA      | 256  | IND   | 17       |

| LFE3-17EA-8FTN256I  | 1.2 V   | -8    | STD   | Lead-Free ftBGA      | 256  | IND   | 17       |

| LFE3-17EA-6LFTN256I | 1.2 V   | -6    | LOW   | Lead-Free ftBGA      | 256  | IND   | 17       |

| LFE3-17EA-7LFTN256I | 1.2 V   | -7    | LOW   | Lead-Free ftBGA      | 256  | IND   | 17       |

| LFE3-17EA-8LFTN256I | 1.2 V   | -8    | LOW   | Lead-Free ftBGA      | 256  | IND   | 17       |

| LFE3-17EA-6MG328I   | 1.2 V   | -6    | STD   | Lead-Free csBGA      | 328  | IND   | 17       |

| LFE3-17EA-7MG328I   | 1.2 V   | -7    | STD   | Lead-Free csBGA      | 328  | IND   | 17       |

| LFE3-17EA-8MG328I   | 1.2 V   | -8    | STD   | Lead-Free csBGA      | 328  | IND   | 17       |

| LFE3-17EA-6LMG328I  | 1.2 V   | -6    | LOW   | Green csBGA          | 328  | IND   | 17       |

| LFE3-17EA-7LMG328I  | 1.2 V   | -7    | LOW   | Green csBGA          | 328  | IND   | 17       |

| LFE3-17EA-8LMG328I  | 1.2 V   | -8    | LOW   | Green csBGA          | 328  | IND   | 17       |

| LFE3-17EA-6FN484I   | 1.2 V   | -6    | STD   | Lead-Free fpBGA      | 484  | IND   | 17       |

| LFE3-17EA-7FN484I   | 1.2 V   | -7    | STD   | Lead-Free fpBGA      | 484  | IND   | 17       |

| LFE3-17EA-8FN484I   | 1.2 V   | -8    | STD   | Lead-Free fpBGA      | 484  | IND   | 17       |

| LFE3-17EA-6LFN484I  | 1.2 V   | -6    | LOW   | Lead-Free fpBGA      | 484  | IND   | 17       |

| LFE3-17EA-7LFN484I  | 1.2 V   | -7    | LOW   | Lead-Free fpBGA      | 484  | IND   | 17       |

| LFE3-17EA-8LFN484I  | 1.2 V   | -8    | LOW   | Lead-Free fpBGA      | 484  | IND   | 17       |

1. Green = Halogen free and lead free.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-35EA-6FTN256I  | 1.2 V   | -6                 | STD   | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-7FTN256I  | 1.2 V   | -7                 | STD   | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-8FTN256I  | 1.2 V   | -8                 | STD   | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-6LFTN256I | 1.2 V   | -6                 | LOW   | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-7LFTN256I | 1.2 V   | -7                 | LOW   | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-8LFTN256I | 1.2 V   | -8                 | LOW   | Lead-Free ftBGA | 256  | IND   | 33       |

| LFE3-35EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 33       |

| LFE3-35EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 33       |

| LFE3-35EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 33       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-70EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 67       |

| LFE3-70EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 67       |

| LFE3-70EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

| LFE3-70EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 67       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number         | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|---------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-95EA-6FN484I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7FN484I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8FN484I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6LFN484I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-7LFN484I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-8LFN484I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 484  | IND   | 92       |

| LFE3-95EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 92       |

| LFE3-95EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

| LFE3-95EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 92       |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number          | Voltage | Grade <sup>1</sup> | Power | Package         | Pins | Temp. | LUTs (K) |

|----------------------|---------|--------------------|-------|-----------------|------|-------|----------|

| LFE3-150EA-6FN672I   | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-7FN672I   | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-8FN672I   | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-6LFN672I  | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-7LFN672I  | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-8LFN672I  | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-6FN1156I  | 1.2 V   | -6                 | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-7FN1156I  | 1.2 V   | -7                 | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-8FN1156I  | 1.2 V   | -8                 | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-6LFN1156I | 1.2 V   | -6                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-7LFN1156I | 1.2 V   | -7                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-8LFN1156I | 1.2 V   | -8                 | LOW   | Lead-Free fpBGA | 1156 | IND   | 149      |

1. For ordering information on -9 speed grade devices, please contact your Lattice Sales Representative.

| Part Number                        | Voltage | Grade | Power | Package         | Pins | Temp. | LUTs (K) |

|------------------------------------|---------|-------|-------|-----------------|------|-------|----------|

| LFE3-150EA-6FN672ITW <sup>1</sup>  | 1.2 V   | -6    | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-7FN672ITW <sup>1</sup>  | 1.2 V   | -7    | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-8FN672ITW <sup>1</sup>  | 1.2 V   | -8    | STD   | Lead-Free fpBGA | 672  | IND   | 149      |

| LFE3-150EA-6FN1156ITW <sup>1</sup> | 1.2 V   | -6    | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-7FN1156ITW <sup>1</sup> | 1.2 V   | -7    | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

| LFE3-150EA-8FN1156ITW <sup>1</sup> | 1.2 V   | -8    | STD   | Lead-Free fpBGA | 1156 | IND   | 149      |

1. Specifications for the LFE3-150EA-*sp*FN*pkg*CTW and LFE3-150EA-*sp*FN*pkg*ITW devices, (where *sp* is the speed and *pkg* is the package), are the same as the LFE3-150EA-*sp*FN*pkg*C and LFE3-150EA-*sp*FN*pkg*I devices respectively, except as specified below.

• The CTC (Clock Tolerance Circuit) inside the SERDES hard PCS in the TW device is not functional but it can be bypassed and implemented in soft IP.

• The SERDES XRES pin on the TW device passes CDM testing at 250V.