# E.J. Lattice Semiconductor Corporation - LFE3-95EA-9FN484C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Not For New Designs                                                          |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 11500                                                                        |

| Number of Logic Elements/Cells | 92000                                                                        |

| Total RAM Bits                 | 4526080                                                                      |

| Number of I/O                  | 295                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 484-BBGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe3-95ea-9fn484c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

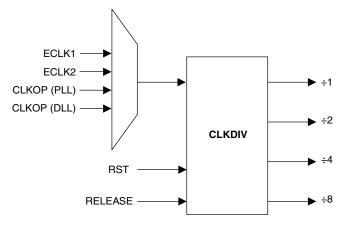

### Figure 2-8. Clock Divider Connections

### **Clock Distribution Network**

LatticeECP3 devices have eight quadrant-based primary clocks and eight secondary clock/control sources. Two high performance edge clocks are available on the top, left, and right edges of the device to support high speed interfaces. These clock sources are selected from external I/Os, the sysCLOCK PLLs, DLLs or routing. These clock sources are fed throughout the chip via a clock distribution system.

### **Primary Clock Sources**

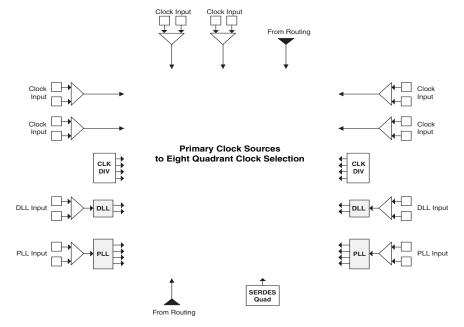

LatticeECP3 devices derive clocks from six primary source types: PLL outputs, DLL outputs, CLKDIV outputs, dedicated clock inputs, routing and SERDES Quads. LatticeECP3 devices have two to ten sysCLOCK PLLs and two DLLs, located on the left and right sides of the device. There are six dedicated clock inputs: two on the top side, two on the left side and two on the right side of the device. Figures 2-9, 2-10 and 2-11 show the primary clock sources for LatticeECP3 devices.

### Figure 2-9. Primary Clock Sources for LatticeECP3-17

Note: Clock inputs can be configured in differential or single-ended mode.

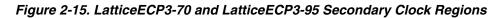

### Table 2-6. Secondary Clock Regions

| Device   | Number of Secondary Clock<br>Regions |

|----------|--------------------------------------|

| ECP3-17  | 16                                   |

| ECP3-35  | 16                                   |

| ECP3-70  | 20                                   |

| ECP3-95  | 20                                   |

| ECP3-150 | 36                                   |

Spine Repeaters

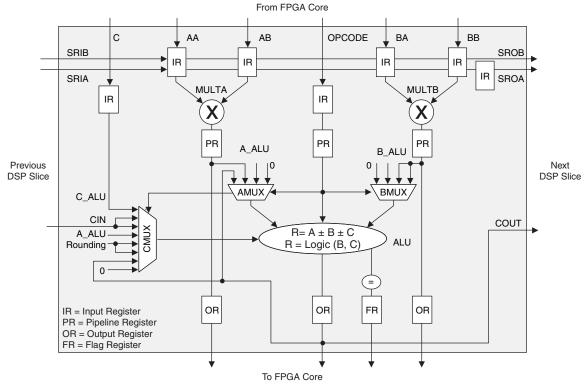

### Figure 2-25. Detailed sysDSP Slice Diagram

Note: A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. See TN1182, LatticeECP3 sysDSP Usage Guide, for further information.

The LatticeECP2 sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2-8 shows the capabilities of each of the LatticeECP3 slices versus the above functions.

Table 2-8. Maximum Number of Elements in a Slice

| Width of Multiply | x9                    | x18 | x36 |

|-------------------|-----------------------|-----|-----|

| MULT              | 4                     | 2   | 1/2 |

| MAC               | 1                     | 1   | _   |

| MULTADDSUB        | 2                     | 1   | _   |

| MULTADDSUBSUM     | <b>1</b> <sup>1</sup> | 1/2 | _   |

1. One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

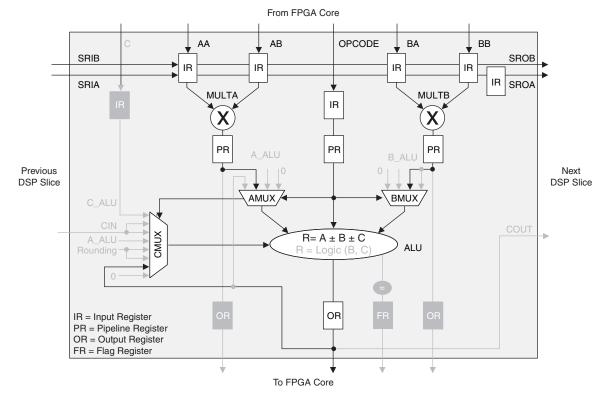

### MMAC DSP Element

The LatticeECP3 supports a MAC with two multipliers. This is called Multiply Multiply Accumulate or MMAC. In this case, the two operands, AA and AB, are multiplied and the result is added with the previous accumulated value and with the result of the multiplier operation of operands BA and BB. This accumulated value is available at the output. The user can enable the input and pipeline registers, but the output register is always enabled. The output register is used to store the accumulated value. The ALU is configured as the accumulator in the sysDSP slice. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-28 shows the MMAC sysDSP element.

### Figure 2-28. MMAC sysDSP Element

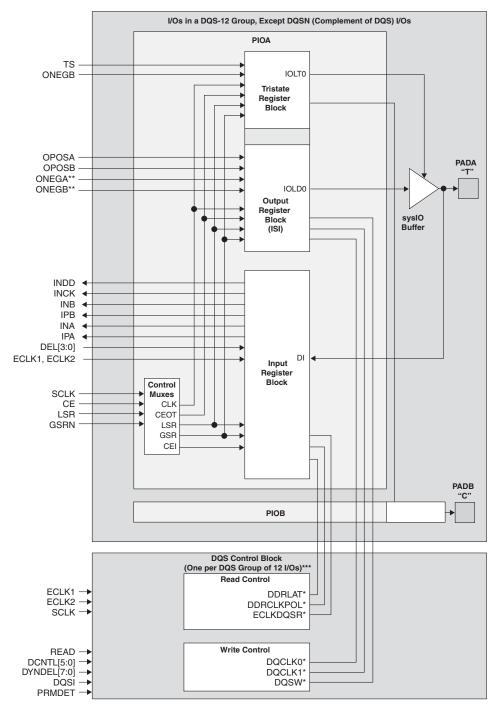

## Programmable I/O Cells (PIC)

Each PIC contains two PIOs connected to their respective sysl/O buffers as shown in Figure 2-32. The PIO Block supplies the output data (DO) and the tri-state control signal (TO) to the sysl/O buffer and receives input from the buffer. Table 2-11 provides the PIO signal list.

### Figure 2-32. PIC Diagram

\* Signals are available on left/right/top edges only.

\*\* Signals are available on the left and right sides only

\*\*\* Selected PIO.

| MCCLK (MHz)      | MCCLK (MHz)     |

|------------------|-----------------|

|                  | 10              |

| 2.5 <sup>1</sup> | 13              |

| 4.3              | 15 <sup>2</sup> |

| 5.4              | 20              |

| 6.9              | 26              |

| 8.1              | 33 <sup>3</sup> |

| 9.2              |                 |

Table 2-16. Selectable Master Clock (MCCLK) Frequencies During Configuration (Nominal)

1. Software default MCCLK frequency. Hardware default is 3.1 MHz.

2. Maximum MCCLK with encryption enabled.

3. Maximum MCCLK without encryption.

### **Density Shifting**

The LatticeECP3 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the LatticeECP3 Pin Migration Tables and Diamond software for specific restrictions and limitations.

## **DC Electrical Characteristics**

| Symbol                          | Parameter                                | Condition                                                                                                                                                   | Min.           | Тур. | Max.                  | Units |

|---------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-----------------------|-------|

| $I_{\rm IL}, I_{\rm IH}^{1, 4}$ | Input or I/O Low Leakage                 | $0 \le V_{IN} \le (V_{CCIO} - 0.2 \text{ V})$                                                                                                               | —              |      | 10                    | μA    |

| I <sub>IH</sub> <sup>1, 3</sup> | Input or I/O High Leakage                | $(V_{CCIO} - 0.2 \text{ V}) < V_{IN} \le 3.6 \text{ V}$                                                                                                     | —              | _    | 150                   | μA    |

| I <sub>PU</sub>                 | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                                                                                             | -30            |      | -210                  | μΑ    |

| I <sub>PD</sub>                 | I/O Active Pull-down Current             | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{CCIO}$                                                                                                                  | 30             |      | 210                   | μΑ    |

| I <sub>BHLS</sub>               | Bus Hold Low Sustaining Current          | $V_{IN} = V_{IL} (MAX)$                                                                                                                                     | 30             |      | —                     | μΑ    |

| I <sub>BHHS</sub>               | Bus Hold High Sustaining Current         | $V_{IN} = 0.7 V_{CCIO}$                                                                                                                                     | -30            | _    | —                     | μΑ    |

| I <sub>BHLO</sub>               | Bus Hold Low Overdrive Current           | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | —              | _    | 210                   | μΑ    |

| I <sub>BHHO</sub>               | Bus Hold High Overdrive Current          | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                 | —              | _    | -210                  | μA    |

| V <sub>BHT</sub>                | Bus Hold Trip Points                     | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                                                                                             | $V_{IL}$ (MAX) | —    | V <sub>IH</sub> (MIN) | V     |

| C1                              | I/O Capacitance <sup>2</sup>             |                                                                                                                                                             | —              | 5    | 8                     | pf    |

| C2                              | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | —              | 5    | 7                     | pf    |

### **Over Recommended Operating Conditions**

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

3. Applicable to general purpose I/Os in top and bottom banks. 4. When used as  $V_{REF}$  maximum leakage= 25  $\mu$ A.

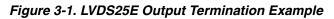

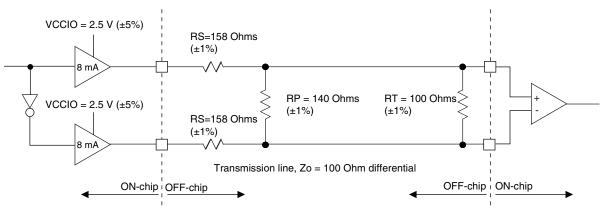

### LVDS25E

The top and bottom sides of LatticeECP3 devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3-1 is one possible solution for point-to-point signals.

### Table 3-1. LVDS25E DC Conditions

| Parameter         | Description                      | Typical | Units |

|-------------------|----------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 20      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 158     | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%) | 140     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)     | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.43    | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 1.07    | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.35    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.25    | V     |

| Z <sub>BACK</sub> | Back Impedance                   | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                | 6.03    | mA    |

### LVCMOS33D

All I/O banks support emulated differential I/O using the LVCMOS33D I/O type. This option, along with the external resistor network, provides the system designer the flexibility to place differential outputs on an I/O bank with 3.3 V V<sub>CCIO</sub>. The default drive current for LVCMOS33D output is 12 mA with the option to change the device strength to 4 mA, 8 mA, 16 mA or 20 mA. Follow the LVCMOS33 specifications for the DC characteristics of the LVCMOS33D.

## LatticeECP3 External Switching Characteristics (Continued)<sup>1, 2, 3, 13</sup>

|                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                               | ·8                                                             | _                                                                                                           | -7                                                  | _                                                                                                       | -6                                                                      |                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min.                                                                            | Max.                                                           | Min.                                                                                                        | Max.                                                | Min.                                                                                                    | Max.                                                                    | Units                                                                                     |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                          | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.7                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                     | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.6                                                                             |                                                                | 1.8                                                                                                         |                                                     | 2.0                                                                                                     |                                                                         | ns                                                                                        |

|                                                                                                                                                                                                                                                                                            | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-70EA/95EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.0                                                                             |                                                                | 0.0                                                                                                         |                                                     | 0.0                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>COPLL</sub>                                                                                                                                                                                                                                                                         | Clock to Output - PIO Output<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                               | 3.2                                                            | _                                                                                                           | 3.4                                                 | _                                                                                                       | 3.6                                                                     | ns                                                                                        |

| t <sub>SUPLL</sub>                                                                                                                                                                                                                                                                         | Clock to Data Setup - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                          | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3                                                                             | _                                                              | 0.3                                                                                                         | _                                                   | 0.4                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                     | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.6                                                                             |                                                                | 1.7                                                                                                         |                                                     | 1.8                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>H_DELPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-35EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0                                                                             |                                                                | 0.0                                                                                                         |                                                     | 0.0                                                                                                     |                                                                         | ns                                                                                        |

| t <sub>COPLL</sub>                                                                                                                                                                                                                                                                         | Clock to Output - PIO Output<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                               | 3.0                                                            | _                                                                                                           | 3.3                                                 | _                                                                                                       | 3.5                                                                     | ns                                                                                        |

| t <sub>SUPLL</sub>                                                                                                                                                                                                                                                                         | Clock to Data Setup - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6                                                                             | _                                                              | 0.7                                                                                                         | _                                                   | 0.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>HPLL</sub>                                                                                                                                                                                                                                                                          | Clock to Data Hold - PIO Input<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.3                                                                             | _                                                              | 0.3                                                                                                         | _                                                   | 0.4                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                     | Clock to Data Setup - PIO Input<br>Register with Data Input Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.6                                                                             | _                                                              | 1.7                                                                                                         | _                                                   | 1.8                                                                                                     | _                                                                       | ns                                                                                        |

| t <sub>H_DELPLL</sub>                                                                                                                                                                                                                                                                      | Clock to Data Hold - PIO Input<br>Register with Input Data Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECP3-17EA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.0                                                                             | _                                                              | 0.0                                                                                                         | _                                                   | 0.0                                                                                                     | _                                                                       | ns                                                                                        |

| Input                                                                                                                                                                                                                                                                                      | Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             | _                                                              | 480                                                                                                         | _                                                   | 480                                                                                                     | _                                                                       | ns                                                                                        |

|                                                                                                                                                                                                                                                                                            | Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             | _                                                              | 480                                                                                                         | _                                                   | 480                                                                                                     | _                                                                       | ps                                                                                        |

| tHOGDDR                                                                                                                                                                                                                                                                                    | Data Hald After OLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 480                                                                             |                                                                | 400                                                                                                         |                                                     |                                                                                                         |                                                                         |                                                                                           |

|                                                                                                                                                                                                                                                                                            | Data Hold After CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 400                                                                             |                                                                | 480                                                                                                         | —                                                   | 480                                                                                                     |                                                                         | · ·                                                                                       |

| fMAX GDDB                                                                                                                                                                                                                                                                                  | Data Hold After CLK<br>DDRX1 Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 400                                                                             | 250                                                            | 480                                                                                                         | <br>250                                             | 480                                                                                                     | —<br>250                                                                | ps<br>MHz                                                                                 |

| Clock Input                                                                                                                                                                                                                                                                                | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | All ECP3EA Devices<br>s Wide) Aligned at Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                               |                                                                | —                                                                                                           |                                                     | —                                                                                                       |                                                                         | ps<br>MHz                                                                                 |

| Generic DDRX1  <br>Clock Input                                                                                                                                                                                                                                                             | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                               | (1_RX.S0                                                       | —                                                                                                           | Aligned)                                            | —                                                                                                       | LLCLKIN                                                                 | ps<br>MHz<br>Pin for                                                                      |

| Generic DDRX1  <br>Clock Input                                                                                                                                                                                                                                                             | DDRX1 Clock Frequency Inputs with Clock and Data (>10 Bit and Top Sides and Clock Left and Data Setup Before CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br>(GDDR)<br>                                                                  |                                                                | —<br>CLK.PLL.                                                                                               | <b>Aligned)</b><br>0.225                            | Using P                                                                                                 |                                                                         | ps<br>MHz<br>Pin for                                                                      |

| Generic DDRX1  <br>Clock Input<br>Data Left, Right,                                                                                                                                                                                                                                        | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and<br>Data Setup Before CLK<br>Data Hold After CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices<br>All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                               | 0.225                                                          | —                                                                                                           | Aligned) 0.225                                      | —                                                                                                       | 0.225                                                                   | ps<br>MHz<br>Pin for                                                                      |

| Generic DDRX1 I<br>Clock Input<br>Data Left, Right,<br><sup>t</sup> DVACLKGDDR<br><sup>t</sup> DVECLKGDDR<br>f <sub>MAX_GDDR</sub>                                                                                                                                                         | DDRX1 Clock Frequency<br>nputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and<br>Data Setup Before CLK<br>Data Hold After CLK<br>DDRX1 Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices<br>All ECP3EA Devices<br>All ECP3EA Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (GDDR)                                                                          | 0.225<br>                                                      | —<br>CLK.PLL.<br>—<br>0.775<br>—                                                                            | Aligned) 0.225 250                                  | —<br>Using P<br>—<br>0.775<br>—                                                                         | 0.225<br>—<br>250                                                       | ps<br>MHz<br>Pin for<br>UI<br>UI<br>UI                                                    |

| Generic DDRX1 I<br>Clock Input<br>Data Left, Right,<br><sup>t</sup> DVACLKGDDR<br><sup>t</sup> DVECLKGDDR<br>f <sub>MAX_GDDR</sub><br>Generic DDRX1 I<br>Clock Input                                                                                                                       | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and<br>Data Setup Before CLK<br>Data Hold After CLK<br>DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices<br>All ECP3EA Devices<br>All ECP3EA Devices<br>s Wide) Aligned at Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (GDDR)                                                                          | 0.225<br>                                                      | —<br>CLK.PLL.<br>—<br>0.775<br>—                                                                            | Aligned) 0.225 250                                  | —<br>Using P<br>—<br>0.775<br>—                                                                         | 0.225<br>—<br>250                                                       | ps<br>MHz<br>Pin for<br>UI<br>UI<br>UI                                                    |

| Generic DDRX1 I<br>Clock Input<br>Data Left, Right,<br><sup>t</sup> DVACLKGDDR<br><sup>t</sup> DVECLKGDDR<br>f <sub>MAX_GDDR</sub><br>Generic DDRX1 I<br>Clock Input                                                                                                                       | DDRX1 Clock Frequency<br>nputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and<br>Data Setup Before CLK<br>Data Hold After CLK<br>DDRX1 Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices<br>All ECP3EA Devices<br>All ECP3EA Devices<br>s Wide) Aligned at Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (GDDR)                                                                          | 0.225<br>                                                      | —<br>CLK.PLL.<br>—<br>0.775<br>—                                                                            | Aligned) 0.225 250                                  | —<br>Using P<br>—<br>0.775<br>—                                                                         | 0.225<br>—<br>250                                                       | ps<br>MHz<br>Pin for<br>UI<br>UI<br>UI                                                    |

| Generic DDRX1 I<br>Clock Input<br>Data Left, Right,<br><sup>t</sup> DVACLKGDDR<br>tDVECLKGDDR<br>fMAX_GDDR<br>Generic DDRX1 I<br>Clock Input                                                                                                                                               | DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit<br>and Top Sides and Clock Left and<br>Data Setup Before CLK<br>Data Hold After CLK<br>DDRX1 Clock Frequency<br>Inputs with Clock and Data (>10 Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All ECP3EA Devices<br>s Wide) Aligned at Pin<br>Right Sides<br>All ECP3EA Devices<br>All ECP3EA Devices<br>All ECP3EA Devices<br>s Wide) Aligned at Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (GDDR)                                                                          | 0.225<br>                                                      | —<br>CLK.PLL.<br>—<br>0.775<br>—                                                                            | Aligned) 0.225 250                                  | —<br>Using P<br>—<br>0.775<br>—                                                                         | 0.225<br>—<br>250                                                       | ps<br>MHz<br>Pin for<br>UI<br>UI<br>UI                                                    |