Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | LCD, POR, PWM, Voltage Detect, WDT                                               |

| Number of I/O              | 88                                                                               |

| Program Memory Size        | 64KB (64K × 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 20x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP                                                                         |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f2l3a8cnfp-31 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 7.5.5 Timer RC Pin Select Register 0 (TRCPSR0)

| Ado     | Address 0182h                    |        |              |            |           |                    |          |    |            |  |

|---------|----------------------------------|--------|--------------|------------|-----------|--------------------|----------|----|------------|--|

|         | Bit                              | b7     | b6           | b5         | b4        | b3                 | b2       | b1 | b0         |  |

| Sy      | mbol                             |        | —            | TRCIOBSEL1 | TRCIOBSEI | L0 —               | —        | _  | TRCIOASEL0 |  |

| After F | Reset                            | 0      | 0            | 0          | 0         | 0                  | 0        | 0  | 0          |  |

| Bit     | S                                | mbol   |              | Bit Name   |           |                    | Function |    | R/W        |  |

|         |                                  |        |              |            |           |                    |          |    | -          |  |

| b0      | TRCIOASEL0 TRCIOA pin select bit |        |              |            |           | D: TRCIOA pir      |          |    | R/W        |  |

|         |                                  |        |              |            | 1         | 1: TRCIOA pin used |          |    |            |  |

| b1      |                                  | _      | Reserved bit | S          | 5         | Set to 0.          |          |    |            |  |

| b2      |                                  | _      |              |            |           |                    |          |    |            |  |

| b3      |                                  | _      |              |            |           |                    |          |    |            |  |

| b4      | TRCI                             | OBSEL0 | TRCIOB pin   | select bit |           | b5 b4              |          |    |            |  |

| b5      | TRCI                             | OBSEL1 |              |            |           | 0 0: TRCIOB        | -        |    | R/W        |  |

|         |                                  | 000000 |              |            |           | 0 1: P4_5 ass      | signed   |    |            |  |

|         |                                  |        |              |            |           | 1 0: P4_6 ass      | sianed   |    |            |  |

|         |                                  |        |              |            |           | 1 1: P4_7 assigned |          |    |            |  |

| b6      |                                  | _      | Reserved bit | S          | 5         | Set to 0.          |          |    |            |  |

| b7      |                                  | _      |              |            |           |                    |          |    |            |  |

The TRCPSR0 register selects whether to use the timer RC input. To use the input pins for timer RC, set this register.

Set the TRCPSR0 register before setting the timer RC associated registers. Also, do not change the setting value of this register during timer RC operation.

| Address 018Eh<br>Bit b7 b6 b5 b4 b3<br>Symbol INT7SEL0 INT6SEL0 INT5SEL0 INT4SEL0 INT3SEL0 |                           |          |

|--------------------------------------------------------------------------------------------|---------------------------|----------|

|                                                                                            | NT2SEL0 INT1SEL0 INT0SEL0 |          |

| Symbol INT7SEL0 INT6SEL0 INT5SEL0 INT4SEL0 INT3SEL0                                        |                           |          |

|                                                                                            |                           |          |

| After Reset 0 0 0 0 0                                                                      | 0 0 0                     |          |

|                                                                                            |                           |          |

| Bit Symbol Bit Name                                                                        | Function                  | R/W      |

| b0 INT0SEL0 INT0 pin select bit 0: P3_0 assi                                               | ined                      | R/W      |

| 1: P11_0 ass                                                                               | gned                      |          |

| b1 INT1SEL0 INT1 pin select bit 0: P3_1 assi                                               |                           | R/W      |

| 1: P11_1 ass                                                                               | -                         |          |

| b2 INT2SEL0 INT2 pin select bit 0: P3_2 assi                                               |                           | R/W      |

| 1: P11_2 ass                                                                               |                           | <b>.</b> |

| b3 INT3SEL0 INT3 pin select bit 0: P3_3 assi                                               |                           | R/W      |

| b4         INT4SEL0         INT4 pin select bit         0: P3_4 assi                       | •                         | R/W      |

| b4 INT4SEL0 INT4 pin select bit 0: P3_4 assi<br>1: P11_4 ass                               |                           | N/ W     |

| b5         INT5SEL0         INT5 pin select bit         0: P3_5 assisted as a select bit   | -                         | R/W      |

| 1: P11_5 ass                                                                               |                           |          |

| b6 INT6SEL0 INT6 pin select bit 0: P3_6 assi                                               | -                         | R/W      |

| 1: P11_6 ass                                                                               |                           |          |

| b7 INT7SEL0 INT7 pin select bit 0: P3_7 assi                                               | ned                       | R/W      |

| 1: P11_7 ass                                                                               | gned                      |          |

# 7.5.16 INT Interrupt Input Pin Select Register (INTSR)

The INTSR register selects which pin is assigned as the  $\overline{\text{INTi}}$  (i = 0 to 7) input. To use the  $\overline{\text{INTi}}$ , set this register. Set the INTSR register before setting the  $\overline{\text{INTi}}$  associated registers. Also, do not change the setting values in this register during  $\overline{\text{INTi}}$  operation.

#### 11. Protection

# 11. Protection

The protection function protects important registers from being easily overwritten if a program runs out of control. The registers protected by the PRCR register are as follows:

- Registers protected by PRC0 bit: Registers CM0, CM1, CM3, OCD, FRA0, FRA1, FRA2, and FRA3

- Registers protected by PRC1 bit: Registers PM0 and PM1

- Registers protected by PRC3 bit: Registers OCVREFCR, VCA2, VD1LS, VW0C, VW1C, and VW2C

#### 11.1 Register

#### **Protect Register (PRCR)** 11.1.1

Address 000Ah

| Bit         | b7 | b6 | b5 | b4 | b3   | b2 | b1   | b0   |

|-------------|----|----|----|----|------|----|------|------|

| Symbol      | _  | —  | _  | _  | PRC3 | _  | PRC1 | PRC0 |

| After Reset | 0  | 0  | 0  | 0  | 0    | 0  | 0    | 0    |

| Bit | Symbol | Bit Name                  | Function                                                                                                                                | R/W |

|-----|--------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | PRC0   | Protect bit 0             | Enables writing to registers CM0, CM1, CM3, OCD, FRA0,<br>FRA1, FRA2, and FRA3.<br>0: Write disabled<br>1: Write enabled <sup>(1)</sup> | R/W |

| b1  | PRC1   | Protect bit 1             | Enables writing to registers PM0 and PM1.<br>0: Write disabled<br>1: Write enabled <sup>(1)</sup>                                       | R/W |

| b2  | —      | Reserved bit              | Set to 0.                                                                                                                               | R/W |

| b3  | PRC3   | Protect bit 3             | Enables writing to registers OCVREFCR, VCA2, VD1LS,<br>VW0C, VW1C, and VW2C.<br>0: Write disabled<br>1: Write enabled <sup>(1)</sup>    | R/W |

| b4  | —      | Reserved bits             | Set to 0.                                                                                                                               | R/W |

| b5  | —      |                           |                                                                                                                                         |     |

| b6  | —      |                           |                                                                                                                                         |     |

| b7  | —      | Nothing is assigned. If n | ecessary, set to 0. When read, the content is 0.                                                                                        | —   |

Note:

1. Bits PRC0, PRC1, and PRC3 are not set to 0 even after setting them to 1 (write enabled) and writing to the SFR areas. Set these bits to 0 by a program.

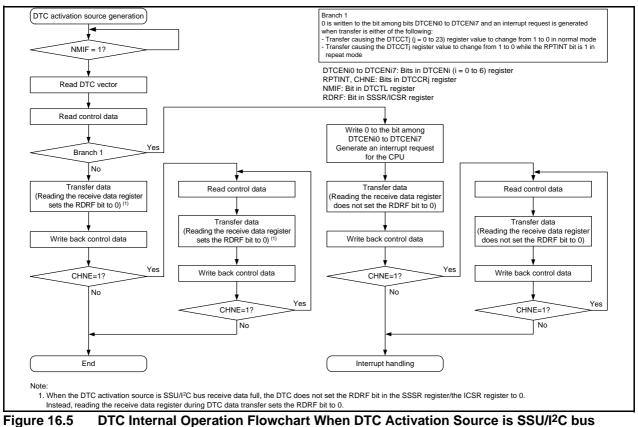

#### 16. DTC

# 16.2.1 DTC Control Register j (DTCCRj) (j = 0 to 23)

| Address     | See Table | e 16.4 Cont | trol Data A | llocation / | Addresses |       |        |      |

|-------------|-----------|-------------|-------------|-------------|-----------|-------|--------|------|

| Bit         | b7        | b6          | b5          | b4          | b3        | b2    | b1     | b0   |

| Symbol      |           | —           | RPTINT      | CHNE        | DAMOD     | SAMOD | RPTSEL | MODE |

| After Reset | Х         | Х           | Х           | Х           | Х         | Х     | Х      | Х    |

| Bit | Symbol | Bit Name                                        | Function                                                                                                     | R/W |

|-----|--------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|

| b0  | MODE   | Transfer mode select bit                        | 0: Normal mode<br>1: Repeat mode                                                                             | R/W |

| b1  | RPTSEL | Repeat area select bit <sup>(1)</sup>           | <ul><li>0: Transfer destination is the repeat area.</li><li>1: Transfer source is the repeat area.</li></ul> | R/W |

| b2  | SAMOD  | Source address control bit <sup>(2)</sup>       | 0: Fixed<br>1: Incremented                                                                                   | R/W |

| b3  | DAMOD  | Destination address control bit <sup>(2)</sup>  | 0: Fixed<br>1: Incremented                                                                                   | R/W |

| b4  | CHNE   | Chain transfer enable bit <sup>(3)</sup>        | 0: Chain transfers disabled<br>1: Chain transfers enabled                                                    | R/W |

| b5  | RPTINT | Repeat mode interrupt enable bit <sup>(1)</sup> | 0: Interrupt generation disabled<br>1: Interrupt generation enabled                                          | R/W |

| b6  | —      | Reserved bits                                   | Set to 0.                                                                                                    | R/W |

| b7  | —      |                                                 |                                                                                                              |     |

Notes:

- 1. This bit is valid when the MODE bit is 1 (repeat mode).

- 2. Settings of bits SAMOD and DAMOD are invalid for the repeat area.

- 3. Set the CHNE bit in the DTCCR23 register to 0 (chain transfers disabled).

## 16.2.2 DTC Block Size Register j (DTBLSj) (j = 0 to 23)

#### Address See Table 16.4 Control Data Allocation Addresses.

| Bit         | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|-------------|----|----|----|----|----|----|----|----|

| Symbol      | _  | —  | _  | —  | _  | _  | —  | —  |

| After Reset | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

| Bit      | Function                                                               | Setting Range  | R/W |

|----------|------------------------------------------------------------------------|----------------|-----|

| b7 to b0 | These bits specify the size of the data block to be transferred by one | 00h to FFh (1) | R/W |

|          | activation.                                                            |                |     |

Note:

1. When the DTBLS register is set to 00h, the block size is 256 bytes.

Receive Data Full

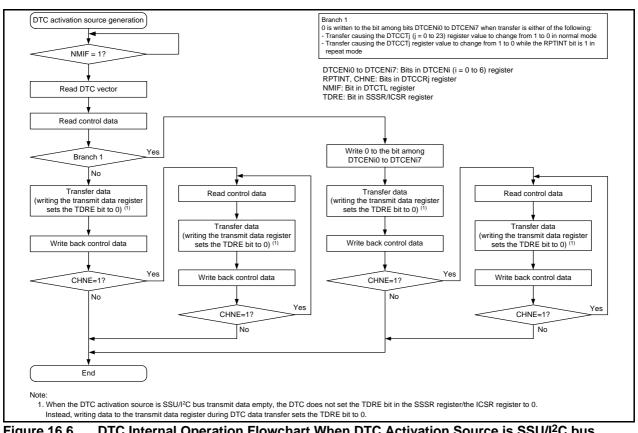

Figure 16.6 DTC Internal Operation Flowchart When DTC Activation Source is SSU/I<sup>2</sup>C bus Transmit Data Empty

RENESAS

# 21.4.11 Timer RD Control Register i (TRDCRi) (i = 0 or 1) for Output Compare Function

| Bit         b7         b6         b5         b4         b3         b2         b1         b0           Symbol         CCLR2         CCLR1         CCLR0         CKEG1         CKEG0         TCK2         TCK1         TCK0           After Reset         0         0         0         0         0         0         0         0         0           Bit         Symbol         Extension         Function         Function         R/W           b0         TCK0         Count source select bit         0         0         0         1         R/W           b1         TCK1         Count source select bit         0         0         1         1         R/W           b2         TCK2         Count source select bit         0         0         1         1         R/W           b1         TCK2         CKEG0         External clock edge select bit (3)         0         0         COUNt at the rising edge         R/W         R/W           b4         CKEG1         TRDi counter clear select bit         0         1         Count at the falling edge         1         R/W           b5         CCLR0         TRDi counter clear select bit         0         0         0 </th <th>Ad</th> <th colspan="11">Address 0140h (TRDCR0), 0150h (TRDCR1)</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ad      | Address 0140h (TRDCR0), 0150h (TRDCR1) |       |              |              |         |              |            |                          |                 |        |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------|-------|--------------|--------------|---------|--------------|------------|--------------------------|-----------------|--------|--|

| After Reset       0       0       0       0       0       0       0       0         Bit       Symbol       Bit Name       Function       R/W         b0       TCK0       Count source select bit       b2 b1 b0       R/W         b1       TCK1       0 0 0 : f1       R/W         b2       TCK2       0 1 0 : f4       R/W         b1       TCK2       0 1 0 : f4       R/W         b2       TCK2       0 1 0 : f4       R/W         b3       CKEG0       External clock edge select bit (3)       b4b3         b4       CKEG1       CCLR1       Function       R/W         b5       CCLR0       TRDi counter clear select bit       b7 b65       0 0 : Clear disabled (free-running operation)       0 1 : Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       0 1 0: Clear by compare match with the TRDGRAi register       R/W         0 1 0: Clear by compare match with the TRDGRBi register       0 1 1: Synchronous clear (clear simultaneously with other timer RDi counter) (4)       1 0 : O : Do not set.         b7       CCLR2       0 1 0: Clear by compare match with the TRDGRDi register       1 0 : Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | Bit                                    | b7    | b6           | b5           | b4      | b3           | b2         | b1                       | b0              |        |  |

| Bit       Symbol       Bit Name       Function       R/W         b0       TCK0       Count source select bit       0 0 0: f1       R/W         b1       TCK1       Count source select bit       0 0 0: f1       R/W         b2       TCK2       0 10: f4       R/W         b3       CKEG0       External clock edge select bit (3)       b4b3       00: Count at the rising edge       R/W         b4       CKEG1       TRDi counter clear select bit       b7 b6 b5       0 0: Clear disabled (free-running operation)       R/W         b6       CCLR1       TRDi counter clear select bit       b7 b6 b5       0 0: Clear by compare match with the TRDGRAi register       R/W         b1       TCL       1 1: Synchronous clear (clear simultaneously with other timer RDi counter) (4)       1 0: Clear by compare match with the TRDGRAi register       1 1: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Sy      | /mbol                                  | CCLR2 | CCLR1        | CCLR0        | CKEG1   | CKEG0        | TCK2       | TCK1                     | TCK0            |        |  |

| b0       TCK0       Count source select bit       b2b1 b0       R/W         b1       TCK1       0 0 0 : f1       0 0 0 : f1       0 0 1 : f2         b2       TCK2       0 1 0 : f4       0 1 1 : f8       1 0 0 : f32         1 0 1 : TRDCLK input <sup>(1)</sup> or fC2 <sup>(2)</sup> 1 1 0 : fOCO40M       1 1 : fOCO-F <sup>(5)</sup> b3       CKEG0       External clock edge select bit <sup>(3)</sup> b4 b3       0 0: Count at the falling edge       R/W         b4       CKEG1       TRDi counter clear select bit       0 0: Clear disabled (free-running operation)       R/W         b5       CCLR0       TRDi counter clear select bit       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       0 1: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       0 1: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       0 1 : Clear by compare match with the TRDGRAi register       1 0 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | After F | Reset                                  | 0     | 0            | 0            | 0       | 0            | 0          | 0                        | 0               |        |  |

| b0       TCK0       Count source select bit       b2b1 b0       R/W         b1       TCK1       0 0 0 : f1       0 0 0 : f1       0 0 1 : f2         b2       TCK2       0 1 0 : f4       0 1 1 : f8       1 0 0 : f32         1 0 1 : TRDCLK input <sup>(1)</sup> or fC2 <sup>(2)</sup> 1 1 0 : fOCO40M       1 1 : fOCO-F <sup>(5)</sup> b3       CKEG0       External clock edge select bit <sup>(3)</sup> b4 b3       0 0: Count at the falling edge       R/W         b4       CKEG1       TRDi counter clear select bit       0 0: Clear disabled (free-running operation)       R/W         b5       CCLR0       TRDi counter clear select bit       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       0 1: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       0 1: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       0 1 : Clear by compare match with the TRDGRAi register       1 0 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                        |       | <b>D</b> .:  | <b>N</b> I   | 'n      |              |            |                          |                 |        |  |

| b1       TCK1         b2       TCK2         b1       TCK1         b2       TCK2         b1       TCK2         b2       TCK2         b1       TCK2         b2       TCK2         b2       TCK2         b1       TCK2         b2       TCK2         b2       TCK2         b1       TCK2         b2       TCK2         b1       TCK2         b2       TCK2         b1       TCK2         b2       TCK2         b2       TCK2         b3       CKEG0         b4       CKEG1         b4       CKEG1         b5       CCLR0         b5       CCLR1         b6       CCLR1         b7       b65         b7       b65         cCLR2       TRDi counter clear select bit         b7       b65         cCLR1       R/W         b7       CCLR2         b7       CCLR2         b7       CCLR2         b7       CCLR2         b7       CCLR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | -                                      |       | -            |              |         |              |            | Function                 |                 |        |  |

| b2       TCK2       0 0 1 1 72       R/W         b2       TCK2       0 1 0 1 74       R/W         0 1 0 1 72       0 1 0 1 74       R/W         0 1 0 1 72       1 0 1 72       R/W         b3       CKEG0       External clock edge select bit (3)       b4b3         b4       CKEG1       External clock edge select bit (3)       0 0 Count at the rising edge       R/W         b4       CKEG1       TRDi counter clear select bit       0 0 Count at the falling edge       R/W         b5       CCLR0       TRDi counter clear select bit       b7 b6b       0 0 0 Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       0 1 0 Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       0 1 0 Clear by compare match with the TRDGRAi register       R/W         b1       Clear by compare match with the TRDGRBi register       0 1 1 Clear by compare match with the TRDGRCi register       1 1 0 Clear by compare match with the TRDGRCi register         0 1 0 Clear by compare match with the TRDGRDi register       1 1 0 Clear by compare match with the TRDGRDi register       1 1 0 Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                                        |       | nt source se | elect bit    |         |              |            |                          |                 | -      |  |

| b1       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01       01 <td< td=""><td>-</td><td></td><td></td><td></td><td></td><td></td><td>0 0 1: f2</td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -       |                                        |       |              |              |         | 0 0 1: f2    |            |                          |                 |        |  |

| b3CKEG0<br>b4External clock edge select bit (3)b4 b3<br>0 0: Count at the rising edge<br>0 0: Count at the falling edge<br>1 0: Count at the falling edge<br>1 0: Count at both edges<br>1 1: Do not set.R/W<br>R/Wb5CCLR0<br>b6TRDi counter clear select bitb7 b6 b5<br>0 00: Clear disabled (free-running operation)<br>0 01: Clear by compare match with the TRDGRAi<br>registerR/W<br>R/Wb7CCLR2TRDi counter clear select bitb7 b6 b5<br>0 00: Clear disabled (free-running operation)<br>0 01: Clear by compare match with the TRDGRAi<br>registerR/W<br>R/Wb7CCLR210: Clear by compare match with the TRDGRAi<br>registerR/W<br>R/Wb7CCLR211: Synchronous clear (clear simultaneously with<br>other timer RDi counter) (4)<br>1 0 0: Do not set.R/W<br>R/W10: Clear by compare match with the TRDGRCi<br>register11: Clear by compare match with the TRDGRDi<br>register11: 0: Clear by compare match with the TRDGRDi<br>register11: 0: Clear by compare match with the TRDGRDi<br>register10: Clear by compare match with the TRDGRDi<br>register11: 0: Clear by compare match with the TRDGRDi<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DZ      | ICK                                    | 2     |              |              |         |              |            |                          |                 | R/W    |  |

| b3       CKEG0       External clock edge select bit (3)       b4 b3       0 0: Count at the rising edge       R/W         b4       CKEG1       External clock edge select bit (3)       b4 b3       0 0: Count at the rising edge       R/W         b5       CCLR0       TRDi counter clear select bit       b7 b6 b5       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       0 1: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       0 1 0: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       0 1 0: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       D 1: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       D 1: Clear by compare match with the TRDGRBi register       R/W         D 1 0: Clear by compare match with the TRDGRDi register       D 1 1: Clear by compare match with the TRDGRDi register       D 1: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |                                        |       |              |              |         |              |            |                          |                 |        |  |

| b3       CKEG0       External clock edge select bit <sup>(3)</sup> b4 b3       0.0 Count at the rising edge       R/W         b4       CKEG1       External clock edge select bit <sup>(3)</sup> b4 b3       0.0 Count at the rising edge       R/W         b4       CKEG1       External clock edge select bit <sup>(3)</sup> b4 b3       0.0 Count at the rising edge       R/W         b5       CCLR0       TRDi counter clear select bit       b7 b6 b5       0.0 Clear disabled (free-running operation)       R/W         b6       CCLR1       CCLR2       V       TRDi counter clear select bit       b7 clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       CCLR2       V       0.1 Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       V       0.1 Clear by compare match with the TRDGRAi register       N       N         b7       CCLR2       V       1.0 Clear by compare match with the TRDGRDi register       N       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                        |       |              |              |         |              |            | 0                        |                 |        |  |

| b3       CKEG0       External clock edge select bit <sup>(3)</sup> b4 b3<br>0 0: Count at the rising edge<br>0 1: Count at the falling edge<br>1 0: Count at the falling edge<br>1 0: Count at both edges<br>1 1: Do not set.       R/W         b5       CCLR0       TRDi counter clear select bit       b7 b6 b5<br>0 0 0: Clear disabled (free-running operation)<br>0 0 1: Clear by compare match with the TRDGRAi<br>register       R/W         b7       CCLR2       V       R/W       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5<br>0 0 0: Clear disabled (free-running operation)<br>0 0 1: Clear by compare match with the TRDGRAi<br>register       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5<br>0 1 0: Clear by compare match with the TRDGRAi<br>register       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5<br>0 1 0: Clear by compare match with the TRDGRAi<br>register       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5<br>0 1 0: Clear by compare match with the TRDGRBi<br>register       R/W         b7       CCLR2       1 0 1: Clear by compare match with the TRDGRCi<br>register       1 1 0: Clear by compare match with the TRDGRDi<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                                        |       |              |              |         |              |            | <sup>1)</sup> or fC2 (2) | )               |        |  |

| b3       CKEG0       External clock edge select bit <sup>(3)</sup> b4 b3       0 0: Count at the rising edge       R/W         b4       CKEG1       External clock edge select bit <sup>(3)</sup> b4 b3       0 0: Count at the falling edge       0 1: Count at the falling edge       R/W         b5       CCLR0       TRDi counter clear select bit       b7 b6 b5       0 0: Clear disabled (free-running operation)       R/W         b6       CCLR1       TRDi counter clear select bit       b7 b6 b5       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       CCLR2       TRDi counter clear select bit       b7 b6 b5       0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5       0 1: Clear by compare match with the TRDGRAi register       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5       0 1 0: Clear by compare match with the TRDGRBi register       R/W         0 1 0: Clear by compare match with the TRDGRCi register       0 1 1: Synchronous clear (clear simultaneously with other timer RDi counter) <sup>(4)</sup> 1 0 0: Do not set.       1 0 1: Clear by compare match with the TRDGRDi register         1 1 0: Clear by compare match with the TRDGRDi register       1 0 0: Clear by compare match with the TRDGRDi register       1 0 0: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                                        |       |              |              |         |              |            |                          |                 |        |  |

| b3       CRECC       External clock edge select bit (6)       0: Count at the rising edge<br>01: Count at the falling edge<br>10: Count at the falling edge<br>10: Count at both edges<br>11: Do not set.       R/W         b5       CCLR0       TRDi counter clear select bit       b7 b6 b5<br>0 0 0: Clear disabled (free-running operation)<br>0 0 1: Clear by compare match with the TRDGRAi<br>register       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5<br>0 0 0: Clear disabled (free-running operation)<br>0 0 1: Clear by compare match with the TRDGRAi<br>register       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5<br>0 0 0: Clear disabled (free-running operation)<br>0 0 1: Clear by compare match with the TRDGRBi<br>register       R/W         b7       CCLR2       TRDi counter clear select bit       b7 b6 b5<br>0 0 0: Clear disabled (free-running operation)<br>0 1: Clear by compare match with the TRDGRBi<br>register       R/W         b7       CCLR2       TRDi counter clear select bit       1 1: Synchronous clear (clear simultaneously with<br>other timer RDi counter) (4)       1 0 0: Do not set.         1 0 1: Clear by compare match with the TRDGRCi<br>register       1 1 0: Clear by compare match with the TRDGRDi<br>register       1 1 0: Clear by compare match with the TRDGRDi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | h2      |                                        |       |              |              | 1 (2)   |              | -F (3)     |                          |                 |        |  |

| b5       CCLR0       TRDi counter clear select bit       b7 b6 b5       0 0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       CCLR2       0 1: Count at the falling edge       R/W         b7       CCLR2       CCLR2       b7 b6 b5       0 0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       CCLR2       D 1: Clear by compare match with the TRDGRAi register       R/W         0 1 0: Clear by compare match with the TRDGRBi register       0 1 1: Synchronous clear (clear simultaneously with other timer RDi counter) <sup>(4)</sup> R/W         1 0 0: Do not set.       1 0 1: Clear by compare match with the TRDGRCi register       1 1 0: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                        |       | rnal clock e | age select   | Dit (3) |              |            |                          |                 |        |  |

| b5       CCLR0       TRDi counter clear select bit       b7 b6 b5       R/W         b6       CCLR1       0 0 0: Clear disabled (free-running operation)       R/W         b7       CCLR2       0 1: Clear by compare match with the TRDGRAi register       R/W         0 1 0: Clear by compare match with the TRDGRBi register       0 1 1: Synchronous clear (clear simultaneously with other timer RDi counter) <sup>(4)</sup> R/W         1 0 0: Do not set.       1 0 1: Clear by compare match with the TRDGRCi register       1 1 0: Clear by compare match with the TRDGRCi register         1 1 0: Clear by compare match with the TRDGRDi register       1 1 0: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 04      | CREC                                   |       |              |              |         |              |            |                          |                 | r./ vv |  |

| b5       CCLR0       TRDi counter clear select bit       b7 b6 b5       R/W         b6       CCLR1       0 0 0: Clear disabled (free-running operation)       R/W       R/W         b7       CCLR2       0 1: Clear by compare match with the TRDGRAi register       R/W         0 1 0: Clear by compare match with the TRDGRBi register       0 1 1: Synchronous clear (clear simultaneously with other timer RDi counter) <sup>(4)</sup> R/W         1 0 0: Do not set.       1 0 1: Clear by compare match with the TRDGRCi register       1 1 0: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |                                        |       |              |              |         |              | •          | jes                      |                 |        |  |

| b3       CCLR0       INDECOMMENCION CONTRUCTION CONTRUCT |         |                                        |       |              |              |         |              | set.       |                          |                 |        |  |

| b6       CCLR1         b7       CCLR2         0 0 1: Clear by compare match with the TRDGRAi register         0 1 0: Clear by compare match with the TRDGRBi register         0 1 1: Synchronous clear (clear simultaneously with other timer RDi counter) <sup>(4)</sup> 1 0 0: Do not set.         1 0 1: Clear by compare match with the TRDGRCi register         1 1 0: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                                        |       | i counter cl | ear select l | bit     |              | disabled ( | free-runnin              | a operation)    |        |  |

| b7       CCLR2       register       R/W         010: Clear by compare match with the TRDGRBi register       011: Synchronous clear (clear simultaneously with other timer RDi counter) <sup>(4)</sup> 100: Do not set.       101: Clear by compare match with the TRDGRCi register         110: Clear by compare match with the TRDGRDi register       110: Clear by compare match with the TRDGRDi register       110: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                                        |       |              |              |         |              |            |                          |                 |        |  |

| register<br>0 1 1: Synchronous clear (clear simultaneously with<br>other timer RDi counter) <sup>(4)</sup><br>1 0 0: Do not set.<br>1 0 1: Clear by compare match with the TRDGRCi<br>register<br>1 1 0: Clear by compare match with the TRDGRDi<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D/      | COLF                                   | K2    |              |              |         | regist       | er         |                          |                 | R/W    |  |

| 0 1 1: Synchronous clear (clear simultaneously with<br>other timer RDi counter) <sup>(4)</sup><br>1 0 0: Do not set.<br>1 0 1: Clear by compare match with the TRDGRCi<br>register<br>1 1 0: Clear by compare match with the TRDGRDi<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                                        |       |              |              |         |              | •          | re match w               | vith the TRDGRB | i -    |  |

| other timer RDi counter) <sup>(4)</sup><br>1 0 0: Do not set.<br>1 0 1: Clear by compare match with the TRDGRCi<br>register<br>1 1 0: Clear by compare match with the TRDGRDi<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                        |       |              |              |         | 0            |            | <i>.</i> .               |                 |        |  |

| 1 0 0: Do not set.<br>1 0 1: Clear by compare match with the TRDGRCi<br>register<br>1 1 0: Clear by compare match with the TRDGRDi<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                        |       |              |              |         | -            |            |                          | -               | ith    |  |

| 1 0 1: Clear by compare match with the TRDGRCi<br>register<br>1 1 0: Clear by compare match with the TRDGRDi<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                                        |       |              |              |         |              |            | counter) (4              | )               |        |  |

| register<br>1 1 0: Clear by compare match with the TRDGRDi<br>register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                        |       |              |              |         |              |            | re match w               | vith the TRDGRC | 5      |  |

| 1 1 0: Clear by compare match with the TRDGRDi register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                        |       |              |              |         |              |            |                          |                 | ·      |  |

| register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                                        |       |              |              |         | •            |            | re match w               | ith the TRDGRD  | )i     |  |