#### Details

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | 870/C                                                                              |

| Core Size                  | 8-Bit                                                                              |

| Speed                      | 16MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                                                  |

| Peripherals                | PWM, WDT                                                                           |

| Number of I/O              | 56                                                                                 |

| Program Memory Size        | 60KB (60K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 16x10b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-BQFP                                                                            |

| Supplier Device Package    | 64-QFP (14x14)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/toshiba-semiconductor-and-storage/tmp86fs49fg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications.

Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The Toshiba products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).

These Toshiba products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of Toshiba products listed in this document shall be made at the customer's own risk.

The products described in this document may include products subject to the foreign exchange and foreign trade laws.

TOSHIBA products should not be embedded to the downstream products which are prohibited to be

produced and sold, under any law and regulations.

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

© 2004 TOSHIBA CORPORATION All Rights Reserved 12. 10-bit successive approximation type AD converter

Analog inputs: 16ch

- 13. Key On Wake Up : 4ch

- 14. Clock operation

Single clock mode

Dual clock mode

15. Low power consumption operation

STOP mode: Oscillation stops. (Battery/Capacitor back-up.)

SLOW1 mode: Low power consumption operation using low-frequency clock.(High-frequency clock stop.)

SLOW2 mode: Low power consumption operation using low-frequency clock.(High-frequency clock oscillate.)

IDLE0 mode: CPU stops, and only the Time-Based-Timer(TBT) on peripherals operate using high frequency clock. Release by falling edge of the source clock which is set by TBTCR<TBTCK>.

IDLE1 mode: CPU stops and peripherals operate using high frequency clock. Release by interruputs(CPU restarts).

IDLE2 mode: CPU stops and peripherals operate using high and low frequency clock. Release by interruputs. (CPU restarts).

SLEEP0 mode: CPU stops, and only the Time-Based-Timer(TBT) on peripherals operate using low frequency clock.Release by falling edge of the source clock which is set by TBTCR<TBTCK>.

SLEEP1 mode: CPU stops, and peripherals operate using low frequency clock. Release by interruput.(CPU restarts).

SLEEP2 mode: CPU stops and peripherals operate using high and low frequency clock. Release by interruput.

16. Wide operation voltage:

4.5 V~5.5 V at 16.0MHz /32.768 kHz 3.0 V~3.6 V at 8 MHz/32.768 kHz

# TOSHIBA

# 1.4 Pin Names and Functions

Table 1-1Pin Names and Functions (1/3)

| Pin Name       | Pin Number | Input/Output | Functions                                                         |

|----------------|------------|--------------|-------------------------------------------------------------------|

| P07            | 17         | IO           | PORT07                                                            |

| INT2           |            | I            | External interrupt 2 input                                        |

| Р06            | 16         | IO           | PORT06                                                            |

| <u>SCK1</u>    |            | IO           | Serial clock input/output 1                                       |

| P05            | 15         | 10           | PORT05                                                            |

| SO1            |            | 0            | Serial data output 1                                              |

| P04            | 14         | IO           | PORT04                                                            |

| SI1            |            | I            | Serial data input 1                                               |

| P03            | 13         | IO           | PORT03                                                            |

| INT1           |            | I            | External interrupt 1 input                                        |

| P02            | 12         | IO           | PORT02                                                            |

| TxD1           |            | O            | UART data output 1                                                |

| P01            | 11         | 10           | PORT01                                                            |

| RxD1           |            | 1            | UART data input 1                                                 |

| BOOT           |            | 1            | Serial PROM mode control input                                    |

| P00            | 10         | IO           | PORT00                                                            |

| INT0           |            | I            | External interrupt 0 input                                        |

| P17            | 51         | 10           | PORT17                                                            |

| TC6            |            | 1            | Timer counter 6 input                                             |

| PD06/PWM6/PPG6 |            | 0            | PDO6/PWM6/PPG6 output                                             |

| P16            | 50         | 10           | PORT16                                                            |

| TC5            |            | 1            | Timer counter 5 input                                             |

| PD05/PWM5      |            | 0            | PDO5/PWM5 output                                                  |

| P15            | 49         | IO           | PORT15                                                            |

| TC2            |            | I            | Timer counter 2 input                                             |

| INT3           |            | I            | External interrupt 3 input                                        |

| P14            | 48         | 10           | PORT14                                                            |

| TC4            |            | 1            | Timer counter 4 input                                             |

| PD04/PWM4/PPG4 |            | 0            | PDO4/PWM4/PPG4 output                                             |

| P13            | 47         | 10           | PORT13                                                            |

| TC3            |            | 1            | Timer counter 3 input                                             |

| PD03/PWM3      |            | 0            | PDO3/PWM3 output                                                  |

| P12            | 46         | IO           | PORT12                                                            |

| PPG            |            | I            | PPG Output                                                        |

| P11            | 45         | IO           | PORT11                                                            |

| DVO            |            | O            | Divider output                                                    |

| P10            | 44         | IO           | PORT10                                                            |

| TC1            |            | I            | Timer counter 1 input                                             |

| P22            | 7          | 10           | PORT22                                                            |

| XTOUT          |            | 0            | Resonator connecting pins(32.768kHz) for inputting external clock |

| P21            | 6          | IO           | PORT21                                                            |

| XTIN           |            | I            | Resonator connecting pins(32.768kHz) for inputting external clock |

| P20            | 9          | IO           | PORT20                                                            |

| INT5           |            | I            | External interrupt 5 input                                        |

| STOP           |            | I            | STOP mode release signal input                                    |

### Table 1-1 Pin Names and Functions (3/3)

| Pin Name | Pin Number | Input/Output | Functions                                                                                                                                             |

|----------|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| P61      | 21         | IO           | PORT61                                                                                                                                                |

| AIN01    |            | I            | AD converter analog input 1                                                                                                                           |

| P60      | 20         | IO           | PORT60                                                                                                                                                |

| AIN00    |            | I            | AD converter analog input 0                                                                                                                           |

| P77      | 35         | IO           | PORT77                                                                                                                                                |

| AIN17    |            | I            | AD converter analog input 17                                                                                                                          |

| P76      | 34         | IO           | PORT76                                                                                                                                                |

| AIN16    |            | I            | AD converter analog input 16                                                                                                                          |

| P75      | 33         | IO           | PORT75                                                                                                                                                |

| AIN15    |            | I            | AD converter analog input 15                                                                                                                          |

| P74      | 32         | IO           | PORT74                                                                                                                                                |

| AIN14    |            | I            | AD converter analog input 14                                                                                                                          |

| P73      | 31         | IO           | PORT73                                                                                                                                                |

| AIN13    |            | I            | AD converter analog input 13                                                                                                                          |

| P72      | 30         | IO           | PORT72                                                                                                                                                |

| AIN12    |            | I            | AD converter analog input 12                                                                                                                          |

| P71      | 29         | IO           | PORT71                                                                                                                                                |

| AIN11    |            | I            | AD converter analog input 11                                                                                                                          |

| P70      | 28         | IO           | PORT70                                                                                                                                                |

| AIN10    |            | I            | AD converter analog input 10                                                                                                                          |

| XIN      | 2          | I            | Resonator connecting pins for high-frequency clock                                                                                                    |

| XOUT     | 3          | 0            | Resonator connecting pins for high-frequency clock                                                                                                    |

| RESET    | 8          | I            | Reset signal input                                                                                                                                    |

| TEST     | 4          | I            | Test pin for out-going test and the Serial PROM mode control<br>pin. Usually fix to low level. Fix to high level when the Serial<br>PROM mode starts. |

| VAREF    | 18         | I            | Analog reference voltage input (High)                                                                                                                 |

| AVDD     | 19         | I            | AD circuit power supply                                                                                                                               |

| VDD      | 5          | I            | +5V                                                                                                                                                   |

| VSS      | 1          | I            | 0(GND)                                                                                                                                                |

# 2. Operational Description

# 2.1 CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller.

This section provides a description of the CPU core, the program memory, the data memory, and the reset circuit.

### 2.1.1 Memory Address Map

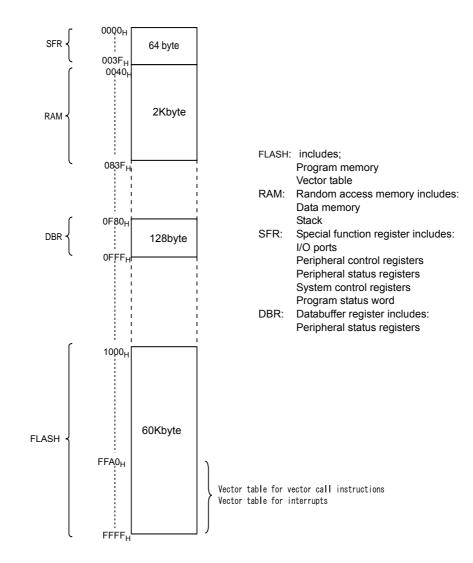

The TMP86FS49FG memory consists of 4 blocks: FLASH, RAM, DBR (Data buffer register) and SFR (Special function register). They are all mapped in 64-Kbyte address space. Figure 2-1 shows the TMP86FS49FG memory address map. The general-purpose registers are not assigned to the RAM address space.

Figure 2-1 Memory Address Map

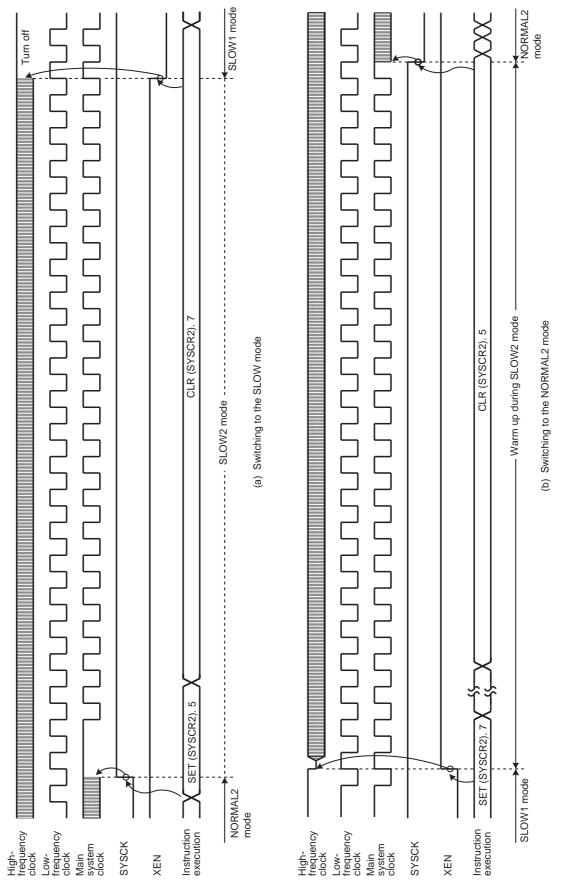

#### 2.2.1 Clock Generator

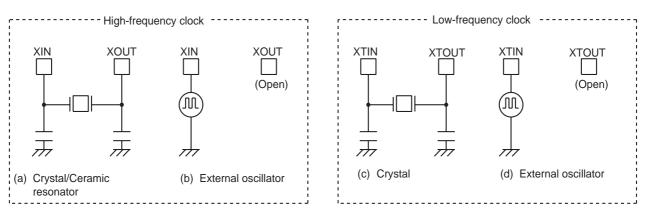

The clock generator generates the basic clock which provides the system clocks supplied to the CPU core and peripheral hardware. It contains two oscillation circuits: One for the high-frequency clock and one for the low-frequency clock. Power consumption can be reduced by switching of the standby controller to low-power operation based on the low-frequency clock.

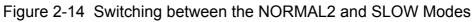

The high-frequency (fc) clocks and low-frequency (fs) clock can easily be obtained by connecting a resonator between the XIN/XOUT and XTIN/XTOUT pins respectively. Clock input from an external oscillator is also possible. In this case, external clock is applied to XIN/XTIN pin with XOUT/XTOUT pin not connected.

Figure 2-3 Examples of Resonator Connection

Note: The function to monitor the basic clock directly at external is not provided for hardware, however, with disabling all interrupts and watchdog timers, the oscillation frequency can be adjusted by monitoring the pulse which the fixed frequency is outputted to the port by the program. The system to require the adjustment of the oscillation frequency should create the program for the adjustment in advance.

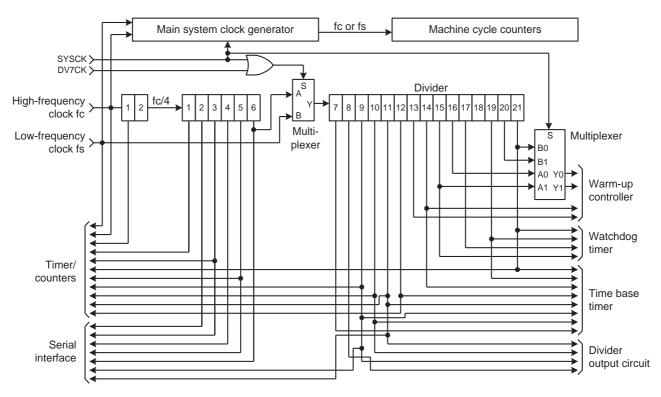

#### 2.2.2 Timing Generator

The timing generator generates the various system clocks supplied to the CPU core and peripheral hardware from the basic clock (fc or fs). The timing generator provides the following functions.

- 1. Generation of main system clock

- 2. Generation of divider output (DVO) pulses

- 3. Generation of source clocks for time base timer

- 4. Generation of source clocks for watchdog timer

- 5. Generation of internal source clocks for timer/counters

- 6. Generation of warm-up clocks for releasing STOP mode

#### 2.2.2.1 Configuration of timing generator

The timing generator consists of a 2-stage prescaler, a 21-stage divider, a main system clock generator, and machine cycle counters.

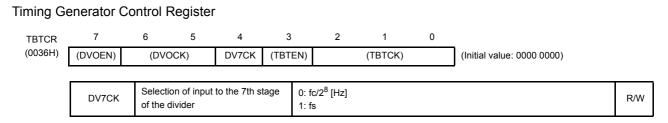

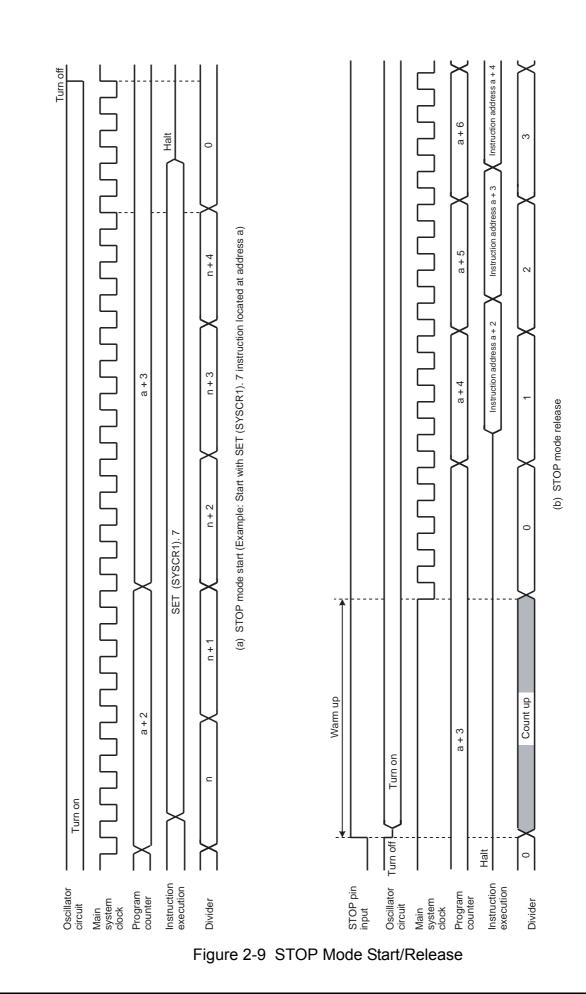

An input clock to the 7th stage of the divider depends on the operating mode, DV7CK (Bit4 in TBTCR), that is shown in Figure 1-5. As reset and STOP mode started/canceled, the prescaler and the divider are cleared to "0".

Figure 2-4 Configuration of Timing Generator

Note 1: In single clock mode, do not set DV7CK to "1".

Note 2: Do not set "1" on DV7CK while the low-frequency clock is not operated stably.

Note 3: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz], \*: Don't care

Note 4: In SLOW1/2 and SLEEP1/2 modes, the DV7CK setting is ineffective, and fs is input to the 7th stage of the divider.

Note 5: When STOP mode is entered from NORMAL1/2 mode, the DV7CK setting is ineffective during the warm-up period after release of STOP mode, and the 6th stage of the divider is input to the 7th stage during this period.

#### 2.2.2.2 Machine cycle

Instruction execution and peripheral hardware operation are synchronized with the main system clock.

The minimum instruction execution unit is called an "machine cycle". There are a total of 10 different types of instructions for the TLCS-870/C Series: Ranging from 1-cycle instructions which require one machine cycle for execution to 10-cycle instructions which require 10 machine cycles for execution. A machine cycle consists of 4 states (S0 to S3), and each state consists of one main system clock.

TENTATIVE

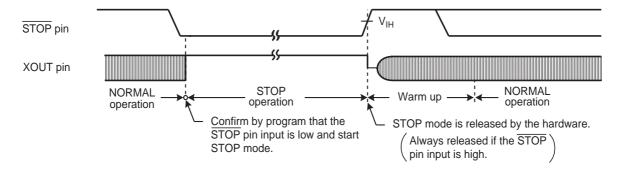

When the  $\overline{\text{STOP}}$  pin input is high, executing an instruction which starts STOP mode will not place in STOP mode but instead will immediately start the release sequence (Warm up). Thus, to start STOP mode in the level-sensitive release mode, it is necessary for the program to first confirm that the  $\overline{\text{STOP}}$  pin input is low. The following two methods can be used for confirmation.

- 1. Testing a port P20.

- 2. Using an external interrupt input INT5 (INT5 is a falling edge-sensitive input).

Example 1 :Starting STOP mode from NORMAL mode by testing a port P20.

|         | LD   | (SYSCR1), 01010000B | ; Sets up the level-sensitive release mode                         |

|---------|------|---------------------|--------------------------------------------------------------------|

| SSTOPH: | TEST | (P2PRD). 0          | ; Wait until the $\overline{\mbox{STOP}}$ pin input goes low level |

|         | JRS  | F, SSTOPH           |                                                                    |

|         | DI   |                     | ; IMF ← 0                                                          |

|         | SET  | (SYSCR1). 7         | ; Starts STOP mode                                                 |

Example 2 :Starting STOP mode from NORMAL mode with an INT5 interrupt.

Figure 2-7 Level-sensitive Release Mode

Note 1: In this case of changing to the level-sensitive mode from the edge-sensitive mode, the release mode is not switched until a rising edge of the STOP pin input is detected.

(2) Edge-sensitive release mode (RELM = "0")

In this mode, STOP mode is released by a rising edge of the  $\overline{\text{STOP}}$  pin input. This is used in applications where a relatively short program is executed repeatedly at periodic intervals. This periodic signal (for example, a clock from a low-power consumption oscillator) is input to the  $\overline{\text{STOP}}$  pin. In the edge-sensitive release mode, STOP mode is started even when the  $\overline{\text{STOP}}$  pin input is high level.

Example :Starting STOP mode from NORMAL mode

| DI |                     | ; IMF ← 0                                                   |

|----|---------------------|-------------------------------------------------------------|

| LD | (SYSCR1), 10010000B | ; Starts after specified to the edge-sensitive release mode |

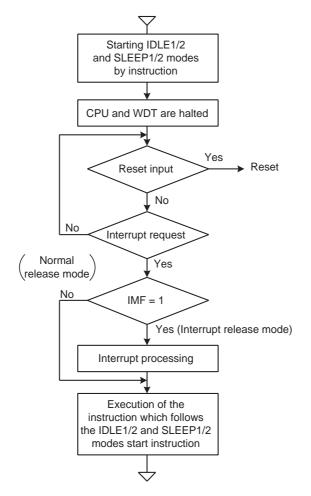

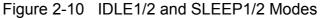

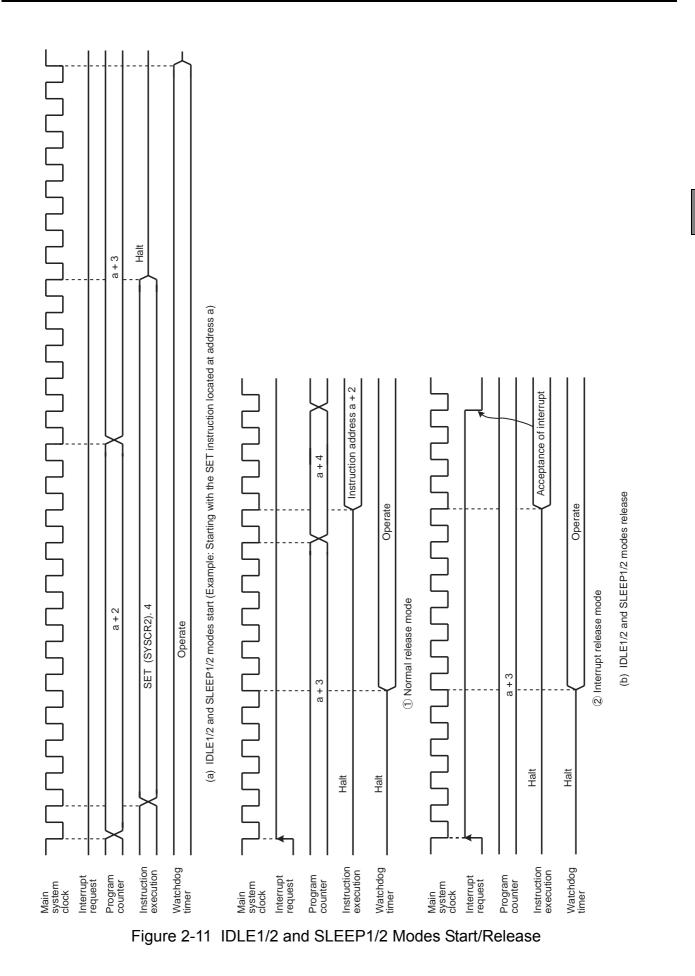

#### 2.2.4.2 IDLE1/2 mode and SLEEP1/2 mode

IDLE1/2 and SLEEP1/2 modes are controlled by the system control register 2 (SYSCR2) and maskable interrupts. The following status is maintained during these modes.

- 1. Operation of the CPU and watchdog timer (WDT) is halted. On-chip peripherals continue to operate.

- 2. The data memory, CPU registers, program status word and port output latches are all held in the status in effect before these modes were entered.

- 3. The program counter holds the address 2 ahead of the instruction which starts these modes.

#### (1) Start the IDLE1/2 and SLEEP1/2 modes

When IDLE1/2 and SLEEP1/2 modes start, set SYSCR2<IDLE> to "1". After IMF is set to "0", set the individual interrupt enable flag (EF) which releases IDLE1/2 and SLEEP1/2.

#### (2) Release the IDLE1/2 and SLEEP1/2 modes

IDLE1/2 and SLEEP1/2 modes include a normal release mode and an interrupt release mode. These modes are selected by interrupt master enable flag (IMF). After releasing IDLE1/2 and SLEEP1/2 modes, the SYSCR2<IDLE> is automatically cleared to "0" and the operation mode is returned to the mode preceding IDLE1/2 and SLEEP1/2 modes.

IDLE1/2 and SLEEP1/2 modes can also be released by inputting low level on the  $\overline{\text{RESET}}$  pin. After releasing reset, the operation mode is started from NORMAL1 mode.

#### (3) Normal release mode (IMF = "0")

IDLE1/2 and SLEEP1/2 modes are released by any interrupt source enabled by the individual interrupt enable flag (EF). After the interrupt is generated, the program operation is resumed from the instruction following the IDLE1/2 and SLEEP1/2 modes start instruction. Normally, the interrupt latches (IL) of the interrupt source used for releasing must be cleared to "0" by load instructions.

#### (4) Interrupt release mode (IMF = "1")

IDLE1/2 and SLEEP1/2 modes are released by any interrupt source enabled with the individual interrupt enable flag (EF) and the interrupt processing is started. After the interrupt is processed, the program operation is resumed from the instruction following the instruction, which starts IDLE1/2 and SLEEP1/2 modes.

Note: When a watchdog timer interrupts is generated immediately before IDLE1/2 and SLEEP1/2 mode are started, the watchdog timer interrupt will be processed but IDLE1/2 and SLEEP1/2 mode will not be started.

# TOSHIBA

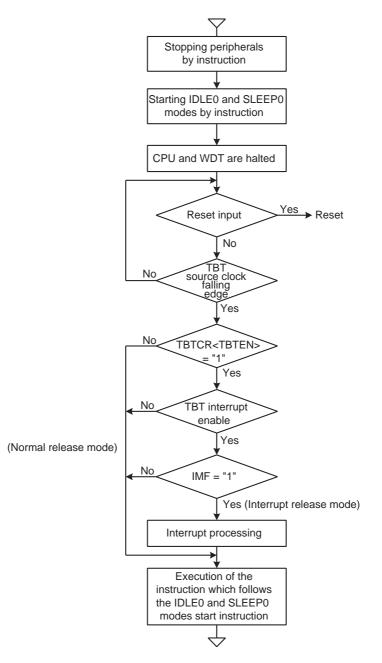

#### 2.2.4.3 IDLE0 and SLEEP0 modes (IDLE0, SLEEP0)

IDLE0 and SLEEP0 modes are controlled by the system control register 2 (SYSCR2) and the time base timer control register (TBTCR). The following status is maintained during IDLE0 and SLEEP0 modes.

- 1. Timing generator stops feeding clock to peripherals except TBT.

- 2. The data memory, CPU registers, program status word and port output latches are all held in the status in effect before IDLE0 and SLEEP0 modes were entered.

- 3. The program counter holds the address 2 ahead of the instruction which starts IDLE0 and SLEEP0 modes.

Note: Before starting IDLE0 or SLEEP0 mode, be sure to stop (Disable) peripherals.

(1) Start the IDLE0 and SLEEP0 modes

Stop (Disable) peripherals such as a timer counter.

TOSHIBA

# 22.2 Recommended Operating Conditions

The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

## 22.2.1 MCU mode (Flash Programming or erasing)

|                                   |                  |                         |                         | (V <sub>S</sub>     | <sub>S</sub> = 0 V, Topr = - <sup>-</sup> | 10 to 40°C) |

|-----------------------------------|------------------|-------------------------|-------------------------|---------------------|-------------------------------------------|-------------|

| Parameter                         | Symbol           | Pins                    | Ratings                 | Min                 | Max                                       | Unit        |

| Supply voltage                    | V <sub>DD</sub>  |                         | NORMAL1, 2 modes        | 4.5                 | 5.5                                       |             |

| Input high loval                  | V <sub>IH1</sub> | Except hysteresis input | V <sub>DD</sub> ≥ 4.5 V | $V_{DD} 	imes 0.70$ | V <sub>DD</sub>                           |             |

| Input high level V <sub>IH2</sub> | V <sub>IH2</sub> | Hysteresis input        | VDD ≥ 4.5 V             | $V_{DD} 	imes 0.75$ |                                           | V           |

|                                   | V <sub>IL1</sub> | Except hysteresis input | V <sub>DD</sub> ≥ 4.5 V | 0                   | $V_{DD} \times 0.30$                      |             |

| Input low level V <sub>IL2</sub>  | V <sub>IL2</sub> | Except hysteresis input | V <sub>DD</sub> ≥ 4.5 V | 0                   | $V_{DD} 	imes 0.25$                       |             |

| Clock frequency                   | fc               | XIN, XOUT               |                         | 1.0                 | 16.0                                      | MHz         |

22.2.2 MCU mode (Except Flash Programming or erasing)

| Parameter                       | Symbol           | Pins                    | F                                    | Ratings                                     | Min                  | Max                  | Unit |

|---------------------------------|------------------|-------------------------|--------------------------------------|---------------------------------------------|----------------------|----------------------|------|

|                                 |                  |                         | fc = 16 MHz                          | NORMAL1, 2 modes<br>IDLE0, 1, 2 modes       |                      |                      |      |

| Supply voltage (Condition 1)    |                  |                         | fs = 32.768 KHz                      | SLOW1, 2 modes<br>SLEEP0, 1, 2 modes        | 4.5                  | 5.5                  |      |

| N N                             | V <sub>DD</sub>  |                         | STOP mode                            | •                                           |                      |                      |      |

|                                 | ♥ DD             |                         | fc = 8 MHz                           | NORMAL1, 2 modes<br>IDLE0, 1, 2 modes       |                      |                      |      |

| Supply voltage<br>(Condition 2) |                  | fs = 32.768 KHz         | SLOW1, 2 modes<br>SLEEP0, 1, 2 modes | 3.0                                         | 3.6                  | V                    |      |

|                                 |                  |                         | STOP mode                            |                                             |                      |                      | •    |

|                                 | V <sub>IH1</sub> | Except hysteresis input | V <sub>DD</sub> ≥ 4.5 V              |                                             | $V_{DD} 	imes 0.70$  |                      |      |

| Input high level                | V <sub>IH2</sub> | Hysteresis input        | v <sub>DD</sub> ≥ 4.5 v              |                                             | $V_{DD} 	imes 0.75$  | V <sub>DD</sub>      |      |

|                                 | V <sub>IH3</sub> |                         | V <sub>DD</sub> < 4.5 V              |                                             | $V_{DD} \times 0.90$ |                      |      |

|                                 | V <sub>IL1</sub> | Except hysteresis input | N A E M                              |                                             |                      | $V_{DD} \times 0.30$ |      |

| Input low level                 | V <sub>IL2</sub> | Hysteresis input        | $V_{DD} \ge 4.5 V$                   |                                             | 0                    | $V_{DD} 	imes 0.25$  |      |

|                                 | V <sub>IL3</sub> |                         | V <sub>DD</sub> < 4.5 V              |                                             |                      | $V_{DD} 	imes 0.10$  |      |

|                                 | fc               | XIN, XOUT               | V <sub>DD</sub> = 3.0 to 3.6 \       | V <sub>DD</sub> = 3.0 to 3.6 V, 4.5 to 5.5V |                      | 8.0                  | MUL  |

| Clock frequency                 | fc               | XIN, XOUT               | $V_{DD}$ = 4.5 to 5.5 V              | /                                           | 1.0                  | 16.0                 | MHz  |

|                                 | fs               | XTIN, XTOUT             | V <sub>DD</sub> = 3.0 to 3.6 \       | /, 4.5 to 5.5V                              | 30.0                 | 34.0                 | kHz  |

$(V_{SS} = 0 V, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

Note 1: The Supply voltage ( $V_{DD}$ ) is divided into two different voltage areas. Do not change  $V_{DD}$  from Condition 1 to Condition 2 and vice versa while the MCU is operationg. If you wish to use  $V_{DD}$  in a continuous range of 3.0V to 5.5V without stopping the MCU, please contact your local Toshiba office.

# 22.2.3 Serial PROM mode

(V<sub>SS</sub> = 0 V, Topr = -10 to 40  $^{\circ}$ C)

| Parameter          | Symbol           | Pins                    | Condition                | Min                  | Max                  | Unit |

|--------------------|------------------|-------------------------|--------------------------|----------------------|----------------------|------|

| Supply voltage     | V <sub>DD</sub>  |                         | NORMAL1, 2 modes         | 4.5                  | 5.5                  |      |

| Input high voltage | V <sub>IH1</sub> | Except hysteresis input | V <sub>DD</sub> ≥ 4.5 V  | $V_{DD} \times 0.70$ | V <sub>DD</sub>      |      |

| Input high voltage | V <sub>IH2</sub> | Hysteresis input        | vDD ≃ <del>1</del> .0 v  | $V_{DD} \times 0.75$ | v DD                 | V    |

|                    | V <sub>IL1</sub> | Except hysteresis input | V <sub>DD</sub> ≥ 4.5 V  | 0                    | $V_{DD} \times 0.30$ |      |

| Input low voltage  | V <sub>IL2</sub> | Hysteresis input        | v DD ≤ <del>1</del> .0 v | 0                    | $V_{DD} \times 0.25$ |      |

| Clock frequency    | fc               | XIN, XOUT               |                          | 2.0                  | 16.0                 | MHz  |

# 22.4 AD Characteristics

#### (V\_{SS} = 0.0 V, 4.5 V $\leq$ V\_{DD} $\,\leq\,$ 5.5 V, Topr = -40 to 85 °C)

|                                                  |                   |                                                                     |                        | 88              | -                 |      |

|--------------------------------------------------|-------------------|---------------------------------------------------------------------|------------------------|-----------------|-------------------|------|

| Paramete                                         | Symbol            | Condition                                                           | Min                    | Тур.            | Max               | Unit |

| Analog reference voltage                         | V <sub>AREF</sub> |                                                                     | A <sub>VDD</sub> - 1.0 | -               | A <sub>VDD</sub>  |      |

| Power supply voltage of analog control circuit   | A <sub>VDD</sub>  |                                                                     |                        | V <sub>DD</sub> |                   | v    |

| Analog reference voltage range (Note 4)          | $\Delta V_{AREF}$ |                                                                     | 3.5                    | -               | -                 |      |

| Analog input voltage                             | V <sub>AIN</sub>  |                                                                     | V <sub>SS</sub>        | -               | V <sub>AREF</sub> | 1    |

| Power supply current of analog reference voltage | I <sub>REF</sub>  | $V_{DD} = A_{VDD} = V_{AREF} = 5.5 V$<br>$V_{SS} = A_{VSS} = 0.0 V$ | -                      | 0.6             | 1.0               | mA   |

| Non linearity error                              |                   |                                                                     | -                      | -               | ±2                |      |

| Zero point error                                 |                   | $V_{DD} = A_{VDD} = 5.0 V,$<br>$V_{SS} = A_{VSS} = 0.0 V$           | -                      | -               | ±2                | LSB  |

| Full scale error                                 |                   | $V_{\text{AREF}} = 5.0 \text{ V}$                                   | -                      | -               | ±2                | 130  |

| Total error                                      |                   |                                                                     | -                      | -               | ±2                |      |

(V\_{SS} = 0 V, 3.0 V  $\leq$  V\_{DD}  $\leq$  3.6 V, Topr = -40 to 85°C)

| Parameter                                        | Symbol                  | Condition                                                                | Min                    | Тур. | Max               | Unit |

|--------------------------------------------------|-------------------------|--------------------------------------------------------------------------|------------------------|------|-------------------|------|

| Analog reference voltage                         | V <sub>AREF</sub>       |                                                                          | A <sub>VDD</sub> - 1.0 | -    | A <sub>VDD</sub>  |      |

| Power supply voltage of analog control circuit   | A <sub>VDD</sub>        |                                                                          | V <sub>DD</sub>        |      |                   | v    |

| Analog reference voltage range (Note 4)          | $\DeltaV_{\text{AREF}}$ |                                                                          | 2.5                    | -    | -                 |      |

| Analog input voltage                             | V <sub>AIN</sub>        |                                                                          | V <sub>SS</sub>        | -    | V <sub>AREF</sub> |      |

| Power supply current of analog reference voltage | I <sub>REF</sub>        | $V_{DD} = A_{VDD} = V_{AREF} = 3.6 V$<br>$V_{SS} = A_{VSS} = 0.0 V$      | _                      | 0.5  | 0.8               | mA   |

| Non linearity error                              |                         |                                                                          | -                      | -    | ±2                |      |

| Zero point error                                 |                         | $V_{DD} = A_{VDD} = 3.0 V$ $V_{SS} = A_{VSS} = 0.0 V$ $V_{AREF} = 3.0 V$ | -                      | -    | ±2                | LSB  |

| Full scale error                                 |                         |                                                                          | -                      | -    | ±2                | LOD  |

| Total error                                      |                         | · · · ·                                                                  | -                      | -    | ±2                |      |

Note 1: The total error includes all errors except a quanitization error, and is defined as a maximum deviation from the ideal conversion line.

Note 2: Conversion time is defferent in recommended value by power supply voltage.

Note 3: The voltage to be input on the AIN input pin must not exceed the range between  $V_{AREF}$  and  $V_{SS}$ . If a voltage outside this range is input, conversion values will become unstable and conversion values of other channels will also be affected.

Note 4: Analog reference voltage range:  $\Delta V_{AREF} = V_{AREF} - V_{SS}$

Note 5: When AD converter is not used, fix the AVDD and VAREF pin on the  $\rm V_{\rm DD}$  level.

Machine cycle time

Low-level clock pulse width

High-level clock pulse width

Low-level clock pulse width

μS

# 22.5 AC Characteristics

#### $(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ V} \text{ to } 5.5 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$ Parameter Symbol Condition Min Тур. Max Unit NORMAL1, 2 modes 0.25 4 \_ IDLE0, 1, 2 modes tcy μs SLOW1, 2 modes 117.6 133.3 \_ SLEEP0, 1, 2 modes High-level clock pulse width t<sub>WCH</sub> For external clock operation (XIN input) 31.25 ns \_ fc = 16 MHz

$(V_{SS} = 0 \text{ V}, V_{DD} = 3.0 \text{ V} \text{ to } 3.6 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

15.26

|                              |                  |                                           | (155 0 1, 10 |       |       |      |

|------------------------------|------------------|-------------------------------------------|--------------|-------|-------|------|

| Paramete                     | Symbol           | Condition                                 | Min          | Тур.  | Max   | Unit |

| Machine cycle time           |                  | NORMAL1, 2 modes                          | 0.5          |       | 4     |      |

|                              | +                | IDLE0, 1, 2 modes                         | 0.5          | -     | 4     |      |

|                              | t <sub>cy</sub>  | SLOW1, 2 modes                            | 117.6        | -     | 133.3 | μs   |

|                              |                  | SLEEP0, 1, 2 modes                        | 117.0        |       |       |      |

| High-level clock pulse width | t <sub>WCH</sub> | For external clock operation (XIN input)  |              | 60 F  |       | 20   |

| Low-level clock pulse width  | t <sub>WCL</sub> | fc = 8 MHz                                | -            | 62.5  | -     | ns   |

| High-level clock pulse width | t <sub>WSH</sub> | For external clock operation (XTIN input) |              | 45.00 |       |      |

| Low-level clock pulse width  | t <sub>WSL</sub> | fs = 32.768 kHz                           | -            | 15.26 | _     | μS   |

For external clock operation (XTIN input)

fs = 32.768 kHz

# 22.6 Flash Characteristics

### 22.6.1 Write/Retention Characteristics

t<sub>WCL</sub>

t<sub>WSH</sub>

t<sub>WSL</sub>

$(V_{SS} = 0 V)$

|                                             |                                           |     |      |      | ,     |

|---------------------------------------------|-------------------------------------------|-----|------|------|-------|

| Paramete                                    | Condition                                 | Min | Тур. | Max. | Unit  |

| Number of guaranteed writes to flash memory | V <sub>SS</sub> = 0 V, Topr = -10 to 40°C | -   | -    | 100  | Times |

# 22.7 Recommended Oscillating Conditions

- Note 1: To ensure stable oscillation, the resonator position, load capacitance, etc. must be appropriate. Because these factors are greatly affected by board patterns, please be sure to evaluate operation on the board on which the device will actually be mounted.

- Note 2: The product numbers and specifications of the resonators by Murata Manufacturing Co., Ltd. are subject to change. For up-to-date information, please refer to the following URL: http://www.murata.co.jp/search/index.html

# 22.8 Handling Precaution

- The solderability test conditions for lead-free products (indicated by the suffix G in product name) are shown below.

- When using the Sn-63Pb solder bath Solder bath temperature = 230 °C Dipping time = 5 seconds Number of times = once R-type flux used

- 2. When using the Sn-3.0Ag-0.5Cu solder bath

Solder bath temperature = 245 °C Dipping time = 5 seconds Number of times = once

R-type flux used

Note: The pass criteron of the above test is as follows:

Solderability rate until forming  $\ge$  95 %

- When using the device (oscillator) in places exposed to high electric fields such as cathode-ray tubes, we recommend electrically shielding the package in order to maintain normal operating condition.