Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | F <sup>2</sup> MC-8FX                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I²C, SIO, UART/USART                                                            |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 59                                                                              |

| Program Memory Size        | 60KB (60K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | <u>.</u>                                                                        |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/12b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

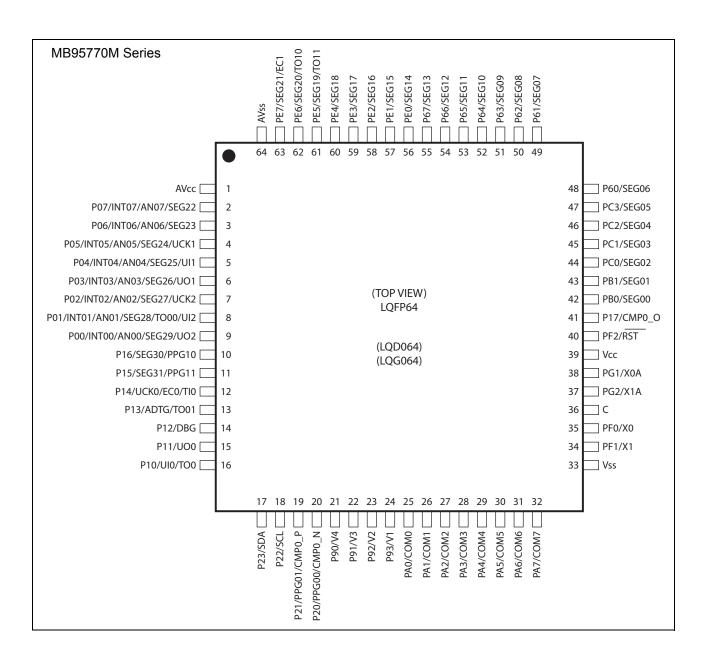

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy95f778jpmc2-g-une2 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         |          | I/O circuit | cuit                     | I/O type     |              |              |              |

|---------|----------|-------------|--------------------------|--------------|--------------|--------------|--------------|

| Pin no. | Pin name | type*1      | Function                 | Input        | Output       | <b>OD</b> *2 | <b>PU</b> *3 |

| 57      | PC5      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 57      | SEG07    | IVI         | LCDC SEG07 output pin    | TYSICICSIS   | LCD          |              | —            |

| 58      | PC6      | М           | General-purpose I/O port | Hyptoropia   | CMOS/        |              |              |

| 50      | SEG08    | IVI         | LCDC SEG08 output pin    | Hysteresis   | LCD          |              | _            |

| 59      | PC7      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 29      | SEG09    | IVI         | LCDC SEG09 output pin    | TYSICICSIS   | LCD          |              | _            |

| 60      | P60      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 00      | SEG10    | IVI         | LCDC SEG10 output pin    | TYSICICSIS   | LCD          |              | _            |

| 61      | P61      | М           | General-purpose I/O port | Hyptoropia   | CMOS/        |              |              |

| 01      | SEG11    | IVI         | LCDC SEG11 output pin    | Hysteresis   | LCD          |              |              |

| 62      | P62      | М           | General-purpose I/O port | Hyptoropia   | CMOS/        |              |              |

| 02      | SEG12    | IVI         | LCDC SEG12 output pin    | Hysteresis   | LCD          |              | _            |

| 63      | P63      | М           | General-purpose I/O port | Hysteresis   | CMOS/<br>LCD |              |              |

| 03      | SEG13    | IVI         | LCDC SEG13 output pin    | rysleiesis   |              |              |              |

| 64      | P64      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 04      | SEG14    | IVI         | LCDC SEG14 output pin    |              | LCD          |              | _            |

| 65      | P65      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 05      | SEG15    | IVI         | LCDC SEG15 output pin    |              | LCD          |              | _            |

| 66      | P66      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 00      | SEG16    | IVI         | LCDC SEG16 output pin    |              | LCD          |              | _            |

| 67      | P67      | М           | General-purpose I/O port | Hystoropia   | CMOS/        |              |              |

| 07      | SEG17    | IVI         | LCDC SEG17 output pin    | Hysteresis   | LCD          |              | _            |

| 68      | P43      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 00      | SEG18    | IVI         | LCDC SEG18 output pin    | rysleiesis   | LCD          |              | _            |

| 69      | P42      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 09      | SEG19    | IVI         | LCDC SEG19 output pin    | TYSICICSIS   | LCD          |              |              |

| 70      | P41      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 70      | SEG20    | IVI         | LCDC SEG20 output pin    | rysleiesis   | LCD          |              | _            |

| 71      | P40      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 7 1     | SEG21    | IVI         | LCDC SEG21 output pin    | rysleiesis   | LCD          |              | _            |

| 72      | PE0      | N/L         | General-purpose I/O port | Hystoresis   | CMOS/        |              |              |

| 12      | SEG22    | М           | LCDC SEG22 output pin    | Hysteresis   | LCD          |              |              |

| 73      | PE1      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| 13      | SEG23    | IVI         | LCDC SEG23 output pin    | 1 1951616515 | LCD          |              |              |

| 74      | PE2      | М           | General-purpose I/O port | Hysteresis   | CMOS/        |              |              |

| /4      | SEG24    | 171         | LCDC SEG24 output pin    | 1 1951010515 | LCD          |              |              |

| Dim me   | Pin no. Pin name 1/0 cire |                                  | Function                            |                     | I/O type               |              |                          |

|----------|---------------------------|----------------------------------|-------------------------------------|---------------------|------------------------|--------------|--------------------------|

| Pin no.  | Pinname                   | type                             |                                     | Input               | Output                 | <b>OD</b> *2 | <b>PU</b> * <sup>3</sup> |

|          | P90                       |                                  | General-purpose I/O port            | Hysteresis/         | CMOS/                  |              |                          |

| 21       | V4                        | R                                | LCD drive power supply pin          | LCD power<br>supply | LCD<br>power<br>supply | _            | —                        |

|          | P91                       |                                  | General-purpose I/O port            | Hysteresis/         | CMOS/                  |              |                          |

| 22       | V3                        | R                                | LCD drive power supply pin          | LCD power<br>supply | LCD<br>power<br>supply | —            | —                        |

|          | P92                       |                                  | General-purpose I/O port            | Hysteresis/         | CMOS/                  |              |                          |

| 23       | V2                        | R                                | LCD drive power supply pin          | LCD power<br>supply | LCD<br>power<br>supply |              | —                        |

|          | P93                       |                                  | General-purpose I/O port            | Hysteresis/         | CMOS/                  |              |                          |

| 24       | V1                        | R                                | LCD drive power supply pin          | LCD power<br>supply | LCD<br>power<br>supply |              | _                        |

| 25       | PA0                       | М                                | General-purpose I/O port            | Hysteresis          | CMOS/                  |              |                          |

| 20       | COM0                      | IVI                              | LCDC COM0 output pin                | Tysleresis          | LCD                    |              | _                        |

| 26       | PA1                       | М                                | General-purpose I/O port            | Hysteresis          | CMOS/<br>LCD           |              |                          |

| 20       | COM1                      | IVI                              | LCDC COM1 output pin                | TIYSLETESIS         |                        |              |                          |

| 27       | PA2                       | М                                | General-purpose I/O port            | Hysteresis          | CMOS/                  |              |                          |

| 21       | COM2                      | IVI                              | LCDC COM2 output pin                | Trysteresis         | LCD                    |              |                          |

| 28       | PA3                       | М                                | General-purpose I/O port            | Hysteresis          | CMOS/                  |              |                          |

| 20       | COM3                      | 171                              | LCDC COM3 output pin                | Tryotorcolo         | LCD                    |              |                          |

| 29       | PA4                       | М                                | General-purpose I/O port            | Hysteresis          | CMOS/                  | _            |                          |

|          | COM4                      |                                  | LCDC COM4 output pin                |                     | LCD                    |              |                          |

| 30       | PA5                       | М                                | General-purpose I/O port            | Hysteresis          | CMOS/                  |              |                          |

|          | COM5                      |                                  | LCDC COM5 output pin                |                     | LCD                    |              |                          |

| 31       | PA6                       | М                                | General-purpose I/O port            | Hysteresis          | CMOS/                  |              |                          |

|          | COM6                      |                                  | LCDC COM6 output pin                |                     | LCD                    |              |                          |

| 32       | PA7                       | М                                | General-purpose I/O port            | Hysteresis          | CMOS/                  |              |                          |

|          | COM7                      |                                  | LCDC COM7 output pin                | ,                   | LCD                    |              |                          |

| 33       | Vss                       |                                  | Power supply pin (GND)              | —                   | —                      |              |                          |

| 34       | PF1                       | В                                | General-purpose I/O port            | Hysteresis          | CMOS                   |              |                          |

| 01       | X1                        |                                  | Main clock I/O oscillation pin      | Tryotoroolo         | 01100                  |              |                          |

| 35       | PF0                       | В                                | General-purpose I/O port            | Hysteresis          | CMOS                   |              |                          |

|          | X0                        | Main clock input oscillation pin |                                     |                     |                        |              |                          |

| 36       | С                         |                                  | Decoupling capacitor connection pin |                     | <u> </u>               |              |                          |

| 37       | PG2                       | С                                | General-purpose I/O port            | Hysteresis          | CMOS                   |              | 0                        |

| <u> </u> | X1A                       | <u> </u>                         | Subclock I/O oscillation pin        | 1,900,000           |                        |              | V                        |

# 15. Areas For Specific Applications

The general-purpose register area and vector table area are used for the specific applications.

- General-purpose register area (Addresses: 0x0100 to 0x01FF)

- This area contains the auxiliary registers used for 8-bit arithmetic operations, transfer, etc.

- As this area forms part of the RAM area, it can also be used as conventional RAM.

- When the area is used as general-purpose registers, general-purpose register addressing enables high-speed access with short instructions.

- Non-volatile register data area (Addresses: 0xFFBB to 0xFFBF)

- The area from 0xFFBB to 0xFFBF is used to store data of the non-volatile register. For details, refer to "CHAPTER 28 NON-VOLATILE REGISTER (NVR) INTERFACE" in "New 8FX MB95710M/770M Series Hardware Manual"

- Vector table area (Addresses: 0xFFC0 to 0xFFFF)

- This area is used as the vector table for vector call instructions (CALLV), interrupts, and resets.

- The top of the Flash memory area is allocated to the vector table area. The start address of a service routine is set to an address in the vector table in the form of data.

"Interrupt Source Table" lists the vector table addresses corresponding to vector call instructions, interrupts, and resets.

For details, refer to "CHAPTER 4 RESET", "CHAPTER 5 INTERRUPTS", and "A.2 Special Instruction ■ Special Instruction ● CALLV #vct" in "APPENDIX" in "New 8FX MB95710M/770M Series Hardware Manual".

| Direct bank pointer (DP[2:0])       | Operand-specified dir | Access area       |  |

|-------------------------------------|-----------------------|-------------------|--|

| 0bXXX (It does not affect mapping.) | 0x0000 to 0x007F      | 0x0000 to 0x007F  |  |

| 0b000 (Initial value)               | 0x0090 to 0x00FF      | 0x0090 to 0x00FF  |  |

| 0b001                               |                       | 0x0100 to 0x017F  |  |

| 0b010                               |                       | 0x0180 to 0x01FF  |  |

| 0b011                               |                       | 0x0200 to 0x027F  |  |

| 0b100                               | 0x0080 to 0x00FF      | 0x0280 to 0x02FF* |  |

| 0b101                               |                       | 0x0300 to 0x037F  |  |

| 0b110                               |                       | 0x0380 to 0x03FF  |  |

| 0b111                               |                       | 0x0400 to 0x047F  |  |

· Direct bank pointer and access area

\*: Due to the memory size limit, the available access area is up to "0x028F" in MB95F714J/F714M/F774J/ F774M.

# 16. I/O Map (MB95710M Series)

| Address                | Register<br>abbreviation | Register name                                        | R/W | Initial value |

|------------------------|--------------------------|------------------------------------------------------|-----|---------------|

| 0x0000                 | PDR0                     | Port 0 data register                                 | R/W | 0b0000000     |

| 0x0001                 | DDR0                     | Port 0 direction register                            | R/W | 0b0000000     |

| 0x0002                 | PDR1                     | Port 1 data register                                 | R/W | 0b0000000     |

| 0x0003                 | DDR1                     | Port 1 direction register                            | R/W | 0b0000000     |

| 0x0004                 | —                        | (Disabled)                                           | —   | —             |

| 0x0005                 | WATR                     | Oscillation stabilization wait time setting register | R/W | 0b11111111    |

| 0x0006                 | PLLC                     | PLL control register                                 | R/W | 0b000X0000    |

| 0x0007                 | SYCC                     | System clock control register                        | R/W | 0bXXX11011    |

| 0x0008                 | STBC                     | Standby control register                             | R/W | 0b0000000     |

| 0x0009                 | RSRR                     | Reset source register                                | R/W | 0b000XXXXX    |

| 0x000A                 | TBTC                     | Time-base timer control register                     | R/W | 0b0000000     |

| 0x000B                 | WPCR                     | Watch prescaler control register                     | R/W | 0b0000000     |

| 0x000C                 | WDTC                     | Watchdog timer control register                      | R/W | 0b00XX0000    |

| 0x000D                 | SYCC2                    | System clock control register 2                      | R/W | 0bXXXX0011    |

| 0x000E                 | PDR2                     | Port 2 data register                                 | R/W | 0b0000000     |

| 0x000F                 | DDR2                     | Port 2 direction register                            | R/W | 0b0000000     |

| 0x0010,<br>0x0011      | —                        | (Disabled)                                           | _   | —             |

| 0x0012                 | PDR4                     | Port 4 data register                                 | R/W | 0b00000000    |

| 0x0013                 | DDR4                     | Port 4 direction register                            | R/W | 0b0000000     |

| 0x0014                 | PDR5                     | Port 5 data register                                 | R/W | 0b0000000     |

| 0x0015                 | DDR5                     | Port 5 direction register                            | R/W | 0b0000000     |

| 0x0016                 | PDR6                     | Port 6 data register                                 | R/W | 0b0000000     |

| 0x0017                 | DDR6                     | Port 6 direction register                            | R/W | 0b0000000     |

| 0x0018<br>to<br>0x001B | _                        | (Disabled)                                           | _   | _             |

| 0x001C                 | PDR9                     | Port 9 data register                                 | R/W | 0b0000000     |

| 0x001D                 | DDR9                     | Port 9 direction register                            | R/W | 0b0000000     |

| 0x001E                 | PDRA                     | Port A data register                                 | R/W | 0b0000000     |

| 0x001F                 | DDRA                     | Port A direction register                            | R/W | 0b0000000     |

| 0x0020                 | PDRB                     | Port B data register                                 | R/W | 0b0000000     |

| 0x0021                 | DDRB                     | Port B direction register                            | R/W | 0b0000000     |

| 0x0022                 | PDRC                     | Port C data register                                 | R/W | 0b0000000     |

| 0x0023                 | DDRC                     | Port C direction register                            | R/W | 0b0000000     |

| 0x0024,<br>0x0025      |                          | (Disabled)                                           | —   |               |

| Address                | Register abbreviation | Register name                                             | R/W | Initial value |

|------------------------|-----------------------|-----------------------------------------------------------|-----|---------------|

| 0x0026                 | PDRE                  | Port E data register                                      | R/W | 0b0000000     |

| 0x0027                 | DDRE                  | Port E direction register                                 | R/W | 0b0000000     |

| 0x0028                 | PDRF                  | Port F data register                                      | R/W | 0b0000000     |

| 0x0029                 | DDRF                  | Port F direction register                                 | R/W | 0b0000000     |

| 0x002A                 | PDRG                  | Port G data register                                      | R/W | 0b0000000     |

| 0x002B                 | DDRG                  | Port G direction register                                 | R/W | 0b0000000     |

| 0x002C                 | _                     | (Disabled)                                                | —   | —             |

| 0x002D                 | PUL1                  | Port 1 pull-up register                                   | R/W | 0b0000000     |

| 0x002E                 | PUL2                  | Port 2 pull-up register                                   | R/W | 0b0000000     |

| 0x002F,<br>0x0030      | —                     | (Disabled)                                                | _   | —             |

| 0x0031                 | PUL5                  | Port 5 pull-up register                                   | R/W | 0b0000000     |

| 0x0032<br>to<br>0x0034 | _                     | (Disabled)                                                | _   | _             |

| 0x0035                 | PULG                  | Port G pull-up register                                   | R/W | 0b0000000     |

| 0x0036                 | T01CR1                | 8/16-bit composite timer 01 status control register 1     | R/W | 0b0000000     |

| 0x0037                 | T00CR1                | 8/16-bit composite timer 00 status control register 1     | R/W | 0b0000000     |

| 0x0038                 | T11CR1                | 8/16-bit composite timer 11 status control register 1     | R/W | 0b0000000     |

| 0x0039                 | T10CR1                | 8/16-bit composite timer 10 status control register 1     | R/W | 0b0000000     |

| 0x003A                 | PC01                  | 8/16-bit PPG timer 01 control register                    | R/W | 0b0000000     |

| 0x003B                 | PC00                  | 8/16-bit PPG timer 00 control register                    | R/W | 0b0000000     |

| 0x003C                 | PC11                  | 8/16-bit PPG timer 11 control register                    | R/W | 0b0000000     |

| 0x003D                 | PC10                  | 8/16-bit PPG timer 10 control register                    | R/W | 0b0000000     |

| 0x003E                 | TMCSRH0               | 16-bit reload timer control status register (upper) ch. 0 | R/W | 0b0000000     |

| 0x003F                 | TMCSRL0               | 16-bit reload timer control status register (lower) ch. 0 | R/W | 0b0000000     |

| 0x0040<br>to<br>0x0047 | _                     | (Disabled)                                                |     | —             |

| 0x0048                 | EIC00                 | External interrupt circuit control register ch. 0/ch. 1   | R/W | 0b0000000     |

| 0x0049                 | EIC10                 | External interrupt circuit control register ch. 2/ch. 3   | R/W | 0b0000000     |

| 0x004A                 | EIC20                 | External interrupt circuit control register ch. 4/ch. 5   | R/W | 0b0000000     |

| 0x004B                 | EIC30                 | External interrupt circuit control register ch. 6/ch. 7   |     | 0b0000000     |

| 0x004C,<br>0x004D      |                       | (Disabled)                                                |     | _             |

| 0x004E                 | LVDC                  | LVD control register                                      | R/W | 0b00000100    |

| 0x004F                 | LCDCC2                | LCDC control register 2                                   | R/W | 0b00010100    |

| 0x0050                 | CMR0                  | Comparator control register ch. 0                         | R/W | 0b0000001     |

# 18. I/O Ports (MB95710M Series)

### · List of port registers

| Register name                      |       | Read/Write | Initial value |

|------------------------------------|-------|------------|---------------|

| Port 0 data register               | PDR0  | R, RM/W    | 0b0000000     |

| Port 0 direction register          | DDR0  | R/W        | 0b0000000     |

| Port 1 data register               | PDR1  | R, RM/W    | 0b0000000     |

| Port 1 direction register          | DDR1  | R/W        | 0b0000000     |

| Port 2 data register               | PDR2  | R, RM/W    | 0b0000000     |

| Port 2 direction register          | DDR2  | R/W        | 0b0000000     |

| Port 4 data register               | PDR4  | R, RM/W    | 0b0000000     |

| Port 4 direction register          | DDR4  | R/W        | 0b0000000     |

| Port 5 data register               | PDR5  | R, RM/W    | 0b0000000     |

| Port 5 direction register          | DDR5  | R/W        | 0b0000000     |

| Port 6 data register               | PDR6  | R, RM/W    | 0b0000000     |

| Port 6 direction register          | DDR6  | R/W        | 0b0000000     |

| Port 9 data register               | PDR9  | R, RM/W    | 0b0000000     |

| Port 9 direction register          | DDR9  | R/W        | 0b0000000     |

| Port A data register               | PDRA  | R, RM/W    | 0b0000000     |

| Port A direction register          | DDRA  | R/W        | 0b0000000     |

| Port B data register               | PDRB  | R, RM/W    | 0b0000000     |

| Port B direction register          | DDRB  | R/W        | 0b0000000     |

| Port C data register               | PDRC  | R, RM/W    | 0b0000000     |

| Port C direction register          | DDRC  | R/W        | 0b0000000     |

| Port E data register               | PDRE  | R, RM/W    | 0b0000000     |

| Port E direction register          | DDRE  | R/W        | 0b0000000     |

| Port F data register               | PDRF  | R, RM/W    | 0b0000000     |

| Port F direction register          | DDRF  | R/W        | 0b0000000     |

| Port G data register               | PDRG  | R, RM/W    | 0b0000000     |

| Port G direction register          | DDRG  | R/W        | 0b0000000     |

| Port 1 pull-up register            | PUL0  | R/W        | 0b0000000     |

| Port 2 pull-up register            | PUL1  | R/W        | 0b0000000     |

| Port 5 pull-up register            | PUL5  | R/W        | 0b0000000     |

| Port G pull-up register            | PULG  | R/W        | 0b0000000     |

| A/D input disable register (lower) | AIDRL | R/W        | 0b0000000     |

R/W : Readable/writable (The read value is the same as the write value.)

R, RM/W : Readable/writable (The read value is different from the write value. The write value is read by the readmodify-write (RMW) type of instruction.)

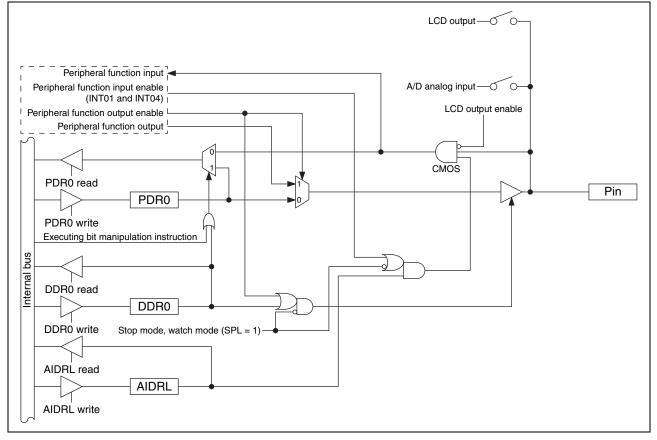

#### • Block diagram of P01/INT01/AN01/SEG36/UI2 and P04/INT04/AN04/SEG33/UI1

## 18.1.3 Port 0 registers

## Port 0 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                              |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|------------------------------------|--|--|--|--|

| PDR0                  | 0    | Pin state is "L" level. | PDR0 value is "0".                          | As output port, outputs "L" level. |  |  |  |  |

| FDRU                  | 1    | Pin state is "H" level. | PDR0 value is "1".                          | As output port, outputs "H" level. |  |  |  |  |

| DDR0                  | 0    |                         | Port input enabled                          | ł                                  |  |  |  |  |

| DDRU                  | 1    |                         | Port output enable                          | d                                  |  |  |  |  |

| AIDRL                 | 0    |                         | Analog input enabled                        |                                    |  |  |  |  |

| AIDRL                 | 1    |                         | Port input enabled                          |                                    |  |  |  |  |

### • Correspondence between registers and pins for port 0

|          |      | Correspondence between related register bits and pins |      |      |      |      |      |      |  |

|----------|------|-------------------------------------------------------|------|------|------|------|------|------|--|

| Pin name | P07  | P06                                                   | P05  | P04  | P03  | P02  | P01  | P00  |  |

| PDR0     |      |                                                       |      |      |      |      |      |      |  |

| DDR0     | bit7 | bit6                                                  | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |  |

| AIDRL    |      |                                                       |      |      |      |      |      |      |  |

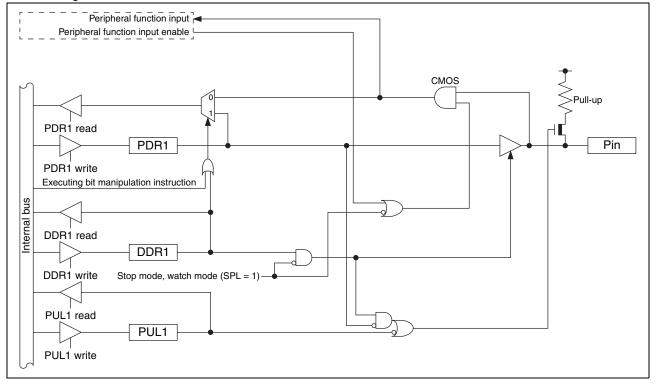

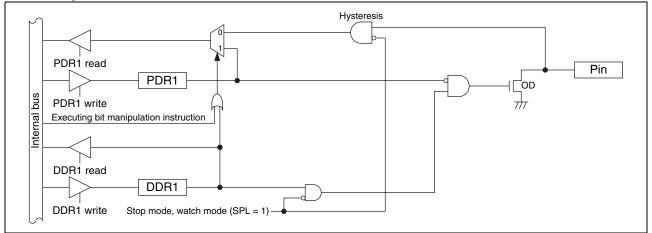

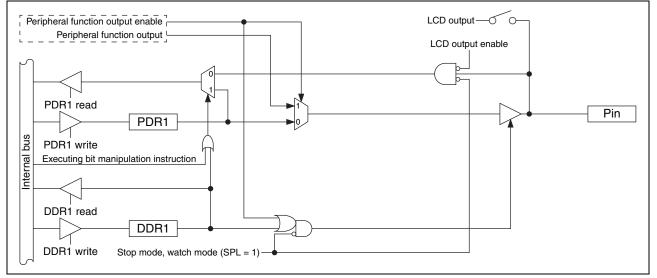

#### Block diagram of P10/UI0

• P12/DBG pin

This pin has the following peripheral function:

- DBG input pin (DBG)

- Block diagram of P12/DBG

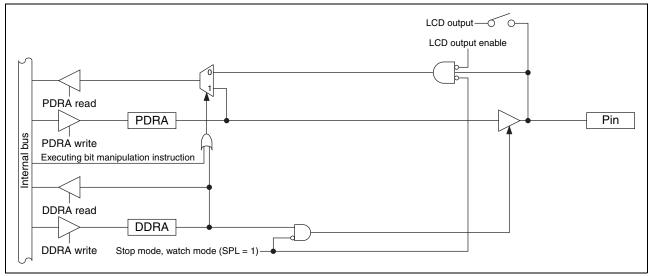

Block diagram of PA0/COM0, PA1/COM1, PA2/COM2, PA3/COM3, PA4/COM4, PA5/COM5, PA6/COM6 and PA7/COM7

# 18.8.3 Port A registers

Port A register functions

| Register abbreviation | Data | (RMW) instruction       |                     | Write                              |  |  |  |  |  |

|-----------------------|------|-------------------------|---------------------|------------------------------------|--|--|--|--|--|

| PDRA                  | 0    | Pin state is "L" level. | PDRA value is "0".  | As output port, outputs "L" level. |  |  |  |  |  |

| FDIA                  | 1    | Pin state is "H" level. | PDRA value is "1".  | As output port, outputs "H" level. |  |  |  |  |  |

| DDRA                  | 0    |                         | Port input enabled  |                                    |  |  |  |  |  |

| DDIA                  | 1    |                         | Port output enabled |                                    |  |  |  |  |  |

· Correspondence between registers and pins for port A

|          |      | Correspondence between related register bits and pins |      |      |      |      |      |      |  |

|----------|------|-------------------------------------------------------|------|------|------|------|------|------|--|

| Pin name | PA7  | PA6                                                   | PA5  | PA4  | PA3  | PA2  | PA1  | PA0  |  |

| PDRA     | bit7 | bit6                                                  | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |  |

| DDRA     | DILT | bito                                                  | DIG  | DIL4 | DILO | DILZ | DILI | DILU |  |

## 19.1 Port 0

Port 0 is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95710M/770M Series Hardware Manual".

#### 19.1.1 Port 0 configuration

- Port 0 is made up of the following elements.

- · General-purpose I/O pins/peripheral function I/O pins

- Port 0 data register (PDR0)

- Port 0 direction register (DDR0)

- A/D input disable register (lower) (AIDRL)

#### 19.1.2 Block diagrams of port 0

- P00/INT00/AN00/SEG29/UO2 pin

- This pin has the following peripheral functions:

- External interrupt input pin (INT00)

- 8/12-bit A/D converter analog input pin (AN00)

- LCDC SEG29 output pin (SEG29)

- UART/SIO ch. 2 data output pin (UO2)

- P02/INT02/AN02/SEG27/UCK2 pin

- This pin has the following peripheral functions:

- External interrupt input pin (INT02)

- 8/12-bit A/D converter analog input pin (AN02)

- LCDC SEG27 output pin (SEG27)

- UART/SIO ch. 2 clock I/O pin (UCK2)

- P03/INT03/AN03/SEG26/UO1 pin

- This pin has the following peripheral functions:

- External interrupt input pin (INT03)

- 8/12-bit A/D converter analog input pin (AN03)

- LCDC SEG26 output pin (SEG26)

- UART/SIO ch. 1 data output pin (UO1)

- P05/INT05/AN05/SEG24/UCK1 pin

This pin has the following peripheral functions:

- External interrupt input pin (INT05)

- 8/12-bit A/D converter analog input pin (AN05)

- LCDC SEG24 output pin (SEG24)

- UART/SIO ch. 1 clock I/O pin (UCK1)

- P06/INT06/AN06/SEG23 pin

This pin has the following peripheral functions:

- External interrupt input pin (INT06)

- 8/12-bit A/D converter analog input pin (AN06)

- LCDC SEG23 output pin (SEG23)

- P07/INT07/AN07/SEG22 pin

- This pin has the following peripheral functions:

- External interrupt input pin (INT07)

- 8/12-bit A/D converter analog input pin (AN07)

- LCDC SEG22 output pin (SEG22)

• P15/SEG31/PPG11 pin

This pin has the following peripheral functions:

- LCDC SEG31 output pin (SEG31)

- 8/16-bit PPG ch. 1 output pin (PPG11)

- P16/SEG30/PPG10 pin

- This pin has the following peripheral functions:

- LCDC SEG30 output pin (SEG30)

- 8/16-bit PPG ch. 1 output pin (PPG10)

- Block diagram of P15/SEG31/PPG11 and P16/SEG30/PPG10

### 19.2.3 Port 1 registers

## Port 1 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                               |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|

| PDR1                  | 0    | Pin state is "L" level. | PDR1 value is "0".                          | As output port, outputs "L" level.  |  |  |  |  |

| FURI                  | 1    | Pin state is "H" level. | PDR1 value is "1".                          | As output port, outputs "H" level.* |  |  |  |  |

| DDR1                  | 0    |                         | Port input enabled                          | ł                                   |  |  |  |  |

| DURI                  | 1    |                         | Port output enable                          | d                                   |  |  |  |  |

| PUL1                  | 0    |                         | Pull-up disabled                            |                                     |  |  |  |  |

| FULT                  | 1    |                         | Pull-up enabled                             |                                     |  |  |  |  |

\*: If the pin is an N-ch open drain pin, the pin state becomes Hi-Z.

· Correspondence between registers and pins for port 1

|          | Correspondence between related register bits and pins |       |      |      |      |      |      |      |  |  |

|----------|-------------------------------------------------------|-------|------|------|------|------|------|------|--|--|

| Pin name | P17                                                   | P16   | P15  | P14  | P13  | P12  | P11  | P10  |  |  |

| PDR1     |                                                       | bit6  | bit5 |      |      | bit2 |      |      |  |  |

| DDR1     | bit7                                                  | 510 1 | DILO | bit4 | bit3 | DILZ | bit1 | bit0 |  |  |

| PUL1     |                                                       | -     | -    |      |      | -    |      |      |  |  |

# 22. Electrical Characteristics

## 22.1 Absolute Maximum Ratings

| Parameter                              | Symbol           | Rat                   | ing     | Unit | Remarks                                                                                         |  |  |

|----------------------------------------|------------------|-----------------------|---------|------|-------------------------------------------------------------------------------------------------|--|--|

| Parameter                              | Symbol           | Min                   | Max     | Unit | Neillai N9                                                                                      |  |  |

| Power supply voltage*1                 | Vcc              | V ss - 0.3            | Vss + 6 | V    |                                                                                                 |  |  |

| Input voltage*1                        | Vi               | $V_{\text{SS}} - 0.3$ | Vss + 6 | V    | *2                                                                                              |  |  |

| Output voltage*1                       | Vo               | $V_{\text{SS}} - 0.3$ | Vss + 6 | V    | *2                                                                                              |  |  |

| Maximum clamp current                  | ICLAMP           | -2                    | +2      | mA   | Applicable to specific pins*3                                                                   |  |  |

| Total maximum clamp current            | $\Sigma$  Iclamp | —                     | 20      | mA   | Applicable to specific pins*3                                                                   |  |  |

| "L" level maximum<br>output current    | lol              | —                     | 15      | mA   |                                                                                                 |  |  |

| "L" level average current              | Iolav            | —                     | 4       | mA   | Average output current =<br>operating current × operating ratio (1 pin)                         |  |  |

| "L" level total maximum output current | $\Sigma$ Iol     | _                     | 100     | mA   |                                                                                                 |  |  |

| "L" level total average output current | $\Sigma$ Iolav   | _                     | 50      | mA   | Total average output current =<br>operating current × operating ratio<br>(Total number of pins) |  |  |

| "H" level maximum<br>output current    | Іон              | _                     | -15     | mA   |                                                                                                 |  |  |

| "H" level average current              | Іонау            | —                     | -4      | mA   | Average output current =<br>operating current × operating ratio (1 pin)                         |  |  |

| "H" level total maximum output current | ΣІон             | _                     | -100    | mA   |                                                                                                 |  |  |

| "H" level total average output current | ΣΙοήαν           | _                     | -50     | mA   | Total average output current =<br>operating current × operating ratio<br>(Total number of pins) |  |  |

| Power consumption                      | Pd               | —                     | 320     | mW   |                                                                                                 |  |  |

| Operating temperature                  | TA               | -40                   | +85     | °C   |                                                                                                 |  |  |

| Storage temperature                    | Tstg             | -55                   | +150    | °C   |                                                                                                 |  |  |

\*1: These parameters are based on the condition that Vss is 0.0 V.

\*2: V1 and V0 must not exceed Vcc + 0.3 V. V1 must not exceed the rated voltage. However, if the maximum current to/from an input is limited by means of an external component, the IcLAMP rating is used instead of the V1 rating.

\*3: Specific pins: P00 to P07, P10, P11, P13 to P16, P20 to P22, P40 to P43, P50 to P53, P60 to P67, P90 to P94, PA0 to PA7, PB0 to PB4, PC0 to PC7, PE0 to PE7, PF0, PF1, PG1, PG2 (P40 to P43, P50 to P53, P94, PB2 to PB4 and PC4 to PC7 are only available on the MB95710M Series.)

- Use under recommended operating conditions.

- Use with DC voltage (current).

• The HV (High Voltage) signal is an input signal exceeding the Vcc voltage. Always connect a limiting resistor between the HV (High Voltage) signal and the microcontroller before applying the HV (High Voltage) signal.

| Demonster                                              | Oursela e l | Diaman                                                                             | O a ra ditti a ra | Value   |     |     | 11   | Demorko                                              |  |

|--------------------------------------------------------|-------------|------------------------------------------------------------------------------------|-------------------|---------|-----|-----|------|------------------------------------------------------|--|

| Parameter                                              | Symbol      | Pin name                                                                           | Condition         | Min Typ |     | Max | Unit | Remarks                                              |  |

| "L" level<br>output<br>voltage                         | Vol         | All output pins                                                                    | lo∟ = 4 mA*4      | —       | _   | 0.4 | V    |                                                      |  |

| Input leak<br>current (Hi-Z<br>output leak<br>current) | lu          | All input pins                                                                     | 0.0 V < Vı < Vcc  | -5      | _   | +5  | μA   | When the internal<br>pull-up resistor is<br>disabled |  |

| Internal<br>pull-up<br>resistor                        | Rpull       | P10, P11, P13,<br>P14, P17,<br>P20, P21,<br>P50 to P53 <sup>*2</sup> ,<br>PG1, PG2 | V1 = 0 V          | 75      | 100 | 150 | kΩ   | When the internal<br>pull-up resistor is<br>enabled  |  |

| Input<br>capacitance                                   | Cin         | Other than Vcc<br>and Vss                                                          | f = 1 MHz         |         | 5   | 15  | pF   |                                                      |  |

(Vcc = 3.0 V±10%, Vss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

## 22.4 AC Characteristics

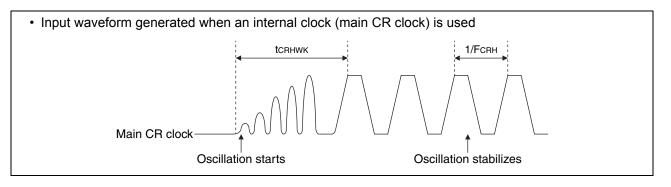

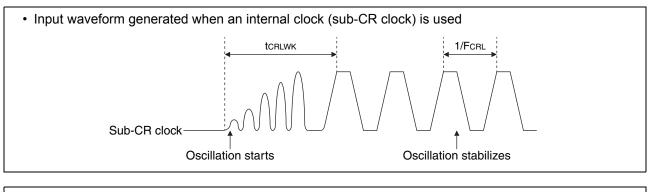

### 22.4.1 Clock Timing

(Vcc = 1.8 V to 5.5 V, Vss = 0.0 V, T<sub>A</sub> = -40 °C to +85 °C)

| Demonster          | 0       | <b>D</b> : |           |       | Value |       | 11   | Demerika                                                                                                                                                          |  |  |

|--------------------|---------|------------|-----------|-------|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter          | Symbol  | Pin name   | Condition | Min   | Тур   | Max   | Unit | Remarks                                                                                                                                                           |  |  |

|                    |         | X0, X1     | _         | 1     | —     | 16.25 | MHz  | When the main oscillation<br>circuit is used                                                                                                                      |  |  |

|                    |         | x0 —       |           | 1     | _     | 32.5  | MHz  | When the main external clock is used                                                                                                                              |  |  |

|                    |         |            |           | 4     | _     | 8.13  | MHz  | Operating conditions <ul> <li>The main clock is used.</li> <li>PLL multiplication rate: 2</li> </ul>                                                              |  |  |

|                    | Fсн     | X0 X1      |           | 4     | _     | 6.5   | MHz  | Operating conditions <ul> <li>The main clock is used.</li> <li>PLL multiplication rate: 2.5</li> </ul>                                                            |  |  |

|                    |         | X0, X1     |           | 4     |       | 5.41  | MHz  | Operating conditions <ul> <li>The main clock is used.</li> <li>PLL multiplication rate: 3</li> </ul>                                                              |  |  |

|                    |         |            |           | 4     |       | 4.06  | MHz  | Operating conditions <ul> <li>The main clock is used.</li> <li>PLL multiplication rate: 4</li> </ul>                                                              |  |  |

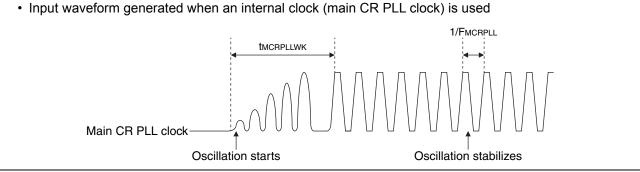

|                    | Fсrн    | _          |           | 3.92  | 4     | 4.08  | MHz  | Operating conditions<br>• The main CR clock is used.<br>• $0 \ ^{\circ}C \le T_A \le +70 \ ^{\circ}C$                                                             |  |  |

| Clock<br>frequency |         |            |           | 3.8   | 4     | 4.2   | MHz  | <ul> <li>Operating conditions</li> <li>The main CR clock is used.</li> <li>- 40 °C ≤ T<sub>A</sub> &lt; 0 °C,<br/>+ 70 °C &lt; T<sub>A</sub> ≤ + 85 °C</li> </ul> |  |  |

|                    | FMCRPLL | . —        |           | 7.84  | 8     | 8.16  | MHz  | Operating conditions<br>• PLL multiplication rate: 2<br>• $0 \ ^{\circ}C \le T_{A} \le +70 \ ^{\circ}C$                                                           |  |  |

|                    |         |            |           | 7.6   | 8     | 8.4   | MHz  | Operating conditions<br>• PLL multiplication rate: 2<br>• $-40 \ ^{\circ}C \le T_A < 0 \ ^{\circ}C,$<br>$+70 \ ^{\circ}C < T_A \le +85 \ ^{\circ}C$               |  |  |

|                    |         |            |           | 9.8   | 10    | 10.2  | MHz  | Operating conditions<br>• PLL multiplication rate: 2.5<br>• $0 \ ^{\circ}C \le T_A \le +70 \ ^{\circ}C$                                                           |  |  |

|                    |         |            |           | 9.5   | 10    | 10.5  | MHz  | Operating conditions<br>• PLL multiplication rate: 2.5<br>• $-40 \ ^{\circ}C \le T_A < 0 \ ^{\circ}C,$<br>$+70 \ ^{\circ}C < T_A \le +85 \ ^{\circ}C$             |  |  |

|                    |         |            |           | 11.76 | 12    | 12.24 | MHz  | Operating conditions<br>• PLL multiplication rate: 3<br>• 0 °C ≤ T <sub>A</sub> ≤ +70 °C                                                                          |  |  |

|                    |         |            |           | 11.4  | 12    | 12.6  | MHz  | Operating conditions<br>• PLL multiplication rate: 3<br>• $-40 \ ^{\circ}C \le T_A < 0 \ ^{\circ}C,$<br>$+70 \ ^{\circ}C < T_A \le +85 \ ^{\circ}C$               |  |  |

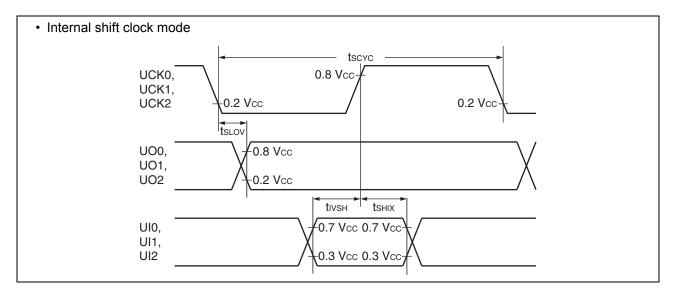

### 22.4.8 UART/SIO, Serial I/O Timing

| Devemeter                                     | Symbol        | Pin name                           | Condition                                   | Value            |      | 11   |

|-----------------------------------------------|---------------|------------------------------------|---------------------------------------------|------------------|------|------|

| Parameter                                     | Symbol        | Pin name                           | Condition                                   | Min              | Max  | Unit |

| Serial clock cycle time                       | tscyc         | UCK0, UCK1, UCK2                   |                                             | <b>4 t</b> мськ* | _    | ns   |

| UCK $\downarrow \rightarrow$ UO time          | tslov         | UCK0, UCK1, UCK2,<br>UO0, UO1, UO2 | Internal clock                              | -190             | +190 | ns   |

| Valid UI $ ightarrow$ UCK $\uparrow$          | tıvsн         | UCK0, UCK1, UCK2,<br>UI0, UI1, UI2 | operation output pin:<br>C∟ = 80 pF + 1 TTL | 2 <b>t</b> MCLK* | _    | ns   |

| UCK $\uparrow \rightarrow$ valid UI hold time | tsнix         | UCK0, UCK1, UCK2,<br>UI0, UI1, UI2 |                                             | 2 <b>t</b> MCLK* | _    | ns   |

| Serial clock "H" pulse width                  | <b>t</b> shsl | UCK0, UCK1, UCK2                   |                                             | 4 <b>t</b> MCLK* | _    | ns   |

| Serial clock "L" pulse width                  | tslsh         | UCK0, UCK1, UCK2                   |                                             | <b>4 t</b> мськ* | _    | ns   |

| UCK $\downarrow \rightarrow$ UO time          | tslov         | UCK0, UCK1, UCK2,<br>UO0, UO1, UO2 | External clock<br>operation output pin:     | —                | 190  | ns   |

| Valid UI $ ightarrow$ UCK $\uparrow$          | tıvsн         | UCK0, UCK1, UCK2,<br>UI0, UI1, UI2 | $C_L = 80 \text{ pF} + 1 \text{ TTL}$       | 2 <b>t</b> MCLK* | _    | ns   |

| UCK $\uparrow \rightarrow$ valid UI hold time | tsнix         | UCK0, UCK1, UCK2,<br>UI0, UI1, UI2 |                                             | 2 <b>t</b> MCLK* | _    | ns   |

\*: See "Source Clock/Machine Clock" for tMCLK.

## 22.6 Flash Memory Program/Erase Characteristics

| Parameter                                                     | Value            |                   |                   | Unit  | Remarks                                                                                       |  |  |

|---------------------------------------------------------------|------------------|-------------------|-------------------|-------|-----------------------------------------------------------------------------------------------|--|--|

| Farameter                                                     | Min              | Тур               | Мах               | Unit  | Reliaiks                                                                                      |  |  |

| Sector erase time<br>(2 Kbyte sector)                         | —                | 0.3* <sup>1</sup> | 1.6*2             | s     | The time of writing "0x00" prior to erasure is excluded.                                      |  |  |

| Sector erase time<br>(24 Kbyte sector and<br>32 Kbyte sector) | _                | 0.6* <sup>1</sup> | 3.1* <sup>2</sup> | s     | The time of writing "0x00" prior to erasure is excluded.                                      |  |  |

| Byte writing time                                             | —                | 17                | 272               | μs    | System-level overhead is excluded.                                                            |  |  |

| Program/erase cycle                                           | 100000           |                   | _                 | cycle |                                                                                               |  |  |

| Power supply voltage at program/erase                         | 1.8              | _                 | 5.5               | V     |                                                                                               |  |  |

|                                                               | 20* <sup>3</sup> | _                 | _                 |       | Average T <sub>A</sub> = +85 °C<br>Number of program/erase cycles: 1000 or below              |  |  |

| Flash memory data retention time                              | 10* <sup>3</sup> | _                 | _                 | year  | Average $T_A = +85 \ ^{\circ}C$<br>Number of program/erase cycles: 1001 to 10000<br>inclusive |  |  |

| $c_{c_{c_{c_{c}}}} = 5.5 \text{ V} + 1.4 = \pm 25 \text{ °C}$ | 5* <sup>3</sup>  |                   | _                 |       | Average T <sub>A</sub> = +85 °C<br>Number of program/erase cycles: 10001 or above             |  |  |

\*1:  $V_{CC} = 5.5 \text{ V}$ ,  $I_A = +25 \text{ °C}$ , 0 cycle

\*2: Vcc = 1.8 V, T<sub>A</sub> = +85 °C, 100000 cycles

\*3: These values were converted from the result of a technology reliability assessment. (These values were converted from the result of a high temperature accelerated test using the Arrhenius equation with the average temperature being +85 °C.)

# **Document History Page**

|          | Document Title: MB95710M Series, MB95770M Series, New 8FX 8-bit Microcontrollers<br>Document Number: 002-09307 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Revision | ECN                                                                                                            | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| **       | -                                                                                                              | YSKA               | 07/31/2013         | Migrated Spansion DS702-00019-1v0-E to Cypress and assigned document number 002-09307.<br>No change to document contents or format.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| *A       | 5511943                                                                                                        | YSKA               | 11/08/2016         | Updated to Cypress template                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| *B       | 5633448                                                                                                        | HTER               | 03/07/2017         | Changed the package codes as the following<br>from "FPT-80P-M37" to "LQH080"<br>from "FPT-64P-M38" to "LQD064"<br>from "FPT-64P-M39" to "LQG064"<br>in chapter:<br>1.Product Line-up (Page 6, 9)<br>2.Packages And Corresponding Products (Page 9)<br>4.Pin Assignment (Page 11 to 12)<br>25.Ordering Information (Page 167)<br>26.Package Dimensions (Page 168 to 170).<br>Changed the Part numbers from "MB95F778JPMC2-G-SNE2" to "MB95F778JPMC2-G-UNE2"<br>in chapter 25.Ordering Information (Page 167). |  |  |  |  |  |

| *C       | 5772061                                                                                                        | YSAT               | 06/15/2017         | Adapted new Cypress logo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| *D       | 5900838                                                                                                        | HUAL               | 09/29/2017         | Modified from "MB95F718JPMC-G-SNE2" to "MB95F718JPMC-G-UNE2" in 25.Ordering Information (Page 167).                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM® Cortex® Microcontrollers | cypress.com/arm        |

|-------------------------------|------------------------|

| Automotive                    | cypress.com/automotive |

| Clocks & Buffers              | cypress.com/clocks     |

| Interface                     | cypress.com/interface  |

| Internet of Things            | cypress.com/iot        |

| Memory                        | cypress.com/memory     |

| Microcontrollers              | cypress.com/mcu        |

| PSoC                          | cypress.com/psoc       |

| Power Management ICs          | cypress.com/pmic       |

| Touch Sensing                 | cypress.com/touch      |

| USB Controllers               | cypress.com/usb        |

| Wireless/RF                   | cypress.com/wireless   |

#### **PSoC®Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners

© Cypress Semiconductor Corporation, 2013-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software provided in binary code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware product. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.