Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Obsolete  F²MC-8FX  8-Bit  16MHz  I²C, SIO, UART/USART  LCD, POR, PWM, WDT |

|----------------------------------------------------------------------------|

| F <sup>2</sup> MC-8FX  8-Bit  16MHz  I <sup>2</sup> C, SIO, UART/USART     |

| 8-Bit  16MHz  I²C, SIO, UART/USART                                         |

| 16MHz<br>I <sup>2</sup> C, SIO, UART/USART                                 |

| I <sup>2</sup> C, SIO, UART/USART                                          |

|                                                                            |

| LCD. POR. PWM. WDT                                                         |

| 202, . 0.9, , 2                                                            |

| 58                                                                         |

| 60KB (60K x 8)                                                             |

| FLASH                                                                      |

| -                                                                          |

| 2K x 8                                                                     |

| 1.8V ~ 5.5V                                                                |

| A/D 8x8/12b                                                                |

| External                                                                   |

| -40°C ~ 85°C (TA)                                                          |

| Surface Mount                                                              |

| 64-LQFP                                                                    |

| C4 LOED (10-10)                                                            |

| 64-LQFP (10x10)                                                            |

|                                                                            |

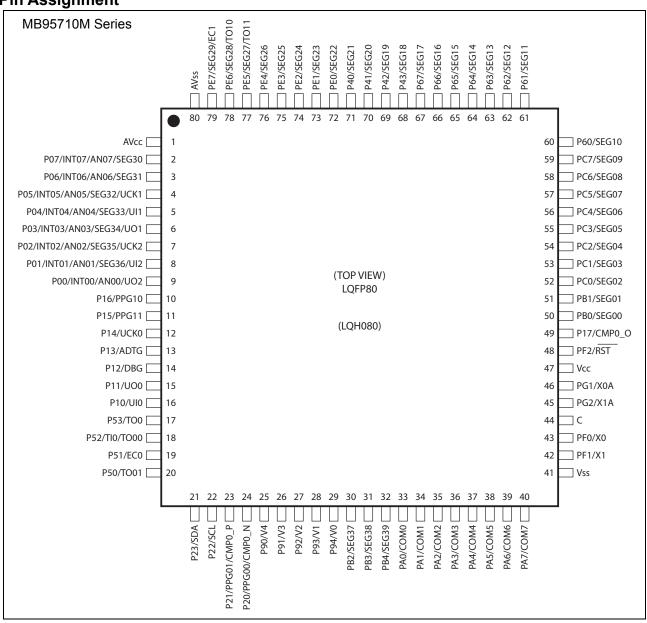

4. Pin Assignment

| D'      | no Bin name I/O circuit Eunction |        | F                                                            | I/O type                           |                        |      |      |

|---------|----------------------------------|--------|--------------------------------------------------------------|------------------------------------|------------------------|------|------|

| Pin no. | Pin name                         | type*1 | Function                                                     | Input                              | Output                 | OD*2 | PU*3 |

|         | P20                              |        | General-purpose I/O port                                     |                                    |                        |      |      |

| 24      | PPG00                            | Т      | 8/16-bit PPG ch. 0 output pin                                | Hysteresis/                        | CMOS                   |      | О    |

| 24      | CMDO N                           |        | Comparator ch. 0 inverting analog input (negative input) pin | analog                             | CIVIOS                 |      |      |

|         | P90                              |        | General-purpose I/O port                                     | Hysteresis/                        | CMOS/                  |      |      |

| 25      | V4                               | R      | LCD drive power supply pin                                   | LCD power supply                   | LCD<br>power<br>supply |      | _    |

|         | P91                              |        | General-purpose I/O port                                     | Hysteresis/                        | CMOS/                  |      |      |

| 26      | V3                               | R      | LCD drive power supply pin                                   | LCD power supply                   | LCD<br>power<br>supply |      |      |

|         | P92                              |        | General-purpose I/O port                                     | Hysteresis/                        | CMOS/                  |      |      |

| 27      | V2                               | R      | LCD drive power supply pin                                   | LCD power supply                   | LCD<br>power<br>supply | _    | _    |

|         | P93                              |        | General-purpose I/O port                                     | Hysteresis/                        | CMOS/                  |      |      |

| 28      | V1                               | R      | LCD drive power supply pin                                   | LCD power supply                   | LCD<br>power<br>supply |      | _    |

|         | P94                              |        | General-purpose I/O port                                     | Hysteresis/<br>LCD power<br>supply | CMOS/                  |      |      |

| 29      | V0                               | R      | LCD drive power supply pin                                   |                                    | LCD<br>power<br>supply |      | _    |

| 30      | PB2                              | M      | General-purpose I/O port                                     | Hysteresis                         | CMOS/                  |      |      |

| 30      | SEG37                            | IVI    | LCDC SEG37 output pin                                        | Trysteresis                        | LCD                    |      | _    |

| 31      | PB3                              | M      | General-purpose I/O port                                     | Hysteresis                         | CMOS/                  |      |      |

| 5       | SEG38                            | IVI    | LCDC SEG38 output pin                                        | Trysteresis                        | LCD                    |      |      |

| 32      | PB4                              | M      | General-purpose I/O port                                     | Hysteresis                         | CMOS/                  |      |      |

| 02      | SEG39                            | 171    | LCDC SEG39 output pin                                        | Tryotorcolo                        | LCD                    |      |      |

| 33      | PA0                              | M      | General-purpose I/O port                                     | Hysteresis                         | CMOS/                  |      |      |

| 33      | COM0                             | IVI    | LCDC COM0 output pin                                         | Trysteresis                        | LCD                    |      |      |

| 34      | PA1                              | M      | General-purpose I/O port                                     | Hysteresis                         | CMOS/                  |      |      |

|         | COM1                             | 171    | LCDC COM1 output pin                                         | Tryotoroolo                        | LCD                    |      |      |

| 35      | PA2                              | M      | General-purpose I/O port                                     | Hysteresis                         | CMOS/                  |      |      |

|         | COM2                             | .,,    | LCDC COM2 output pin                                         | 1.,513,5516                        | LCD                    |      |      |

| 36      | PA3                              | M      | General-purpose I/O port                                     | Hysteresis                         | CMOS/                  | _    | _    |

|         | COM3                             | •••    | LCDC COM3 output pin                                         | 11,510.0010                        | LCD                    |      |      |

| 37      | PA4                              | M      | General-purpose I/O port                                     | Hysteresis                         | CMOS/                  |      | _    |

|         | COM4                             |        | LCDC COM4 output pin                                         | ,                                  | LCD                    |      |      |

| Din no    | Pin name    | I/O circuit | Function                                                         |             | I/O type     |      |          |

|-----------|-------------|-------------|------------------------------------------------------------------|-------------|--------------|------|----------|

| PIII IIO. | Pilitialile | type*1      | Function                                                         | Input       | Output       | OD*2 | PU*3     |

| 75        | PE3         | M           | General-purpose I/O port                                         | Hysteresis  | CMOS/        |      |          |

| 7.5       | SEG25       | IVI         | LCDC SEG25 output pin                                            | Tiysteresis | LCD          |      |          |

| 76        | PE4         | M           | General-purpose I/O port                                         | Hysteresis  | CMOS/        |      |          |

| 70        | SEG26       | IVI         | LCDC SEG26 output pin                                            | TIYSICICSIS | LCD          |      |          |

|           | PE5         |             | General-purpose I/O port                                         |             | 01400/       | _    |          |

| 77        | SEG27       | M           | LCDC SEG27 output pin                                            | Hysteresis  | CMOS/<br>LCD |      | _        |

|           | TO11        |             | 8/16-bit composite timer ch. 1 output pin                        |             |              |      |          |

|           | PE6         |             | General-purpose I/O port                                         | Hysteresis  | 01400/       |      |          |

| 78        | SEG28       | M           | LCDC SEG28 output pin                                            |             | CMOS/<br>LCD | _    | <u> </u> |

|           | TO10        |             | 8/16-bit composite timer ch. 1 output pin                        |             |              |      |          |

|           | PE7         |             | General-purpose I/O port                                         |             |              |      |          |

| 79        | SEG29       | М           | LCDC SEG27 output pin                                            | Hysteresis  | CMOS/        |      |          |

|           | EC1         | •••         | 8/16-bit composite timer ch. 1 clock input pin                   | 11901010010 | LCD          |      |          |

| 80        | AVss        | _           | Power supply pin (GND) for 8/12-bit A/D converter and comparator | _           | _            | _    | —        |

# O: Available

<sup>\*1:</sup> For the I/O circuit types, see "I/O Circuit Type".

<sup>\*2:</sup> N-ch open drain

<sup>\*3:</sup> Pull-up

| Type | Circuit                                                                                                 | Remarks                                                |

|------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| W    | P-ch Digital output Digital output  Analog input  Analog input control Standby control Hysteresis input | CMOS output     Hysteresis input     Analog input      |

| Y    | P-ch Digital output Digital output Standby control Hysteresis input                                     | <ul><li>CMOS output</li><li>Hysteresis input</li></ul> |

(2) Be sure that abnormal current flows do not occur during the power-on sequence.

### Observance of Safety Regulations and Standards

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

### Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

### Precautions Related to Usage of Devices

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

### 8.2 Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under Cypress's recommended conditions. For detailed information about mount conditions, contact your sales representative.

### Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

### Surface Mount Type

Surface mount packaging has longer and thinner leads than lead-insertion packaging, and therefore leads are more easily deformed or bent. The use of packages with higher pin counts and narrower pin pitch results in increased susceptibility to open connections caused by deformed pins, or shorting due to solder bridges.

You must use appropriate mounting techniques. Cypress recommends the solder reflow method, and has established a ranking of mounting conditions for each product. Users are advised to mount packages in accordance with Cypress ranking of recommended conditions.

### Lead-Free Packaging

CAUTION: When ball grid array (BGA) packages with Sn-Ag-Cu balls are mounted using Sn-Pb eutectic soldering, junction strength may be reduced under some conditions of use.

Document Number: 002-09307 Rev. \*D

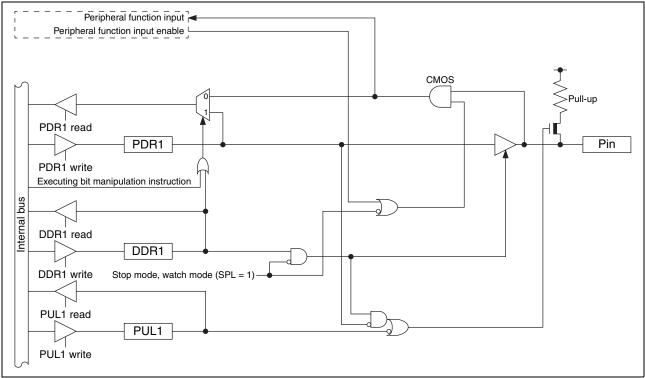

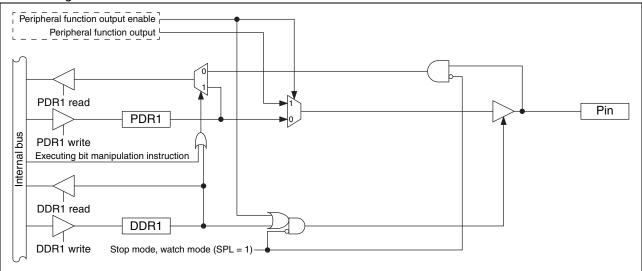

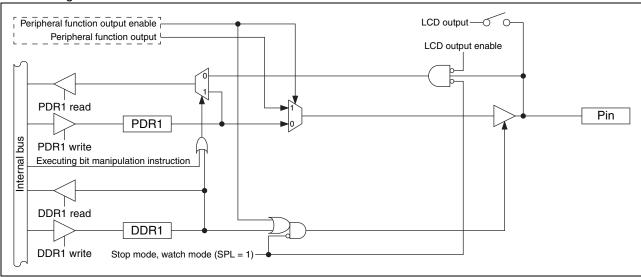

Block diagram of P10/UI0

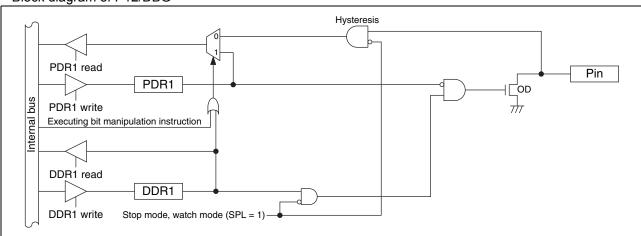

- P12/DBG pin

- This pin has the following peripheral function:

- DBG input pin (DBG)

- Block diagram of P12/DBG

### • P15/PPG11 pin

This pin has the following peripheral function:

- 8/16-bit PPG ch. 1 output pin (PPG11)

- P16/PPG10 pin

This pin has the following peripheral function:

• 8/16-bit PPG ch. 1 output pin (PPG10)

# • Block diagram of P15/PPG11 and P16/PPG10

### 18.2.3 Port 1 registers

· Port 1 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                               |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|

| PDR1                  | 0    | Pin state is "L" level. | PDR1 value is "0".                          | As output port, outputs "L" level.  |  |  |  |  |

| 1                     |      | Pin state is "H" level. | PDR1 value is "1".                          | As output port, outputs "H" level.* |  |  |  |  |

| DDR1                  | 0    |                         | Port input enabled                          | d                                   |  |  |  |  |

| DDK1                  | 1    | Port output enabled     |                                             |                                     |  |  |  |  |

| PUL1                  | 0    |                         | Pull-up disabled                            |                                     |  |  |  |  |

| POLI                  | 1    |                         | Pull-up enabled                             |                                     |  |  |  |  |

<sup>\*:</sup> If the pin is an N-ch open drain pin, the pin state becomes Hi-Z.

· Correspondence between registers and pins for port 1

|          | Correspondence between related register bits and pins |      |      |      |      |      |      |      |

|----------|-------------------------------------------------------|------|------|------|------|------|------|------|

| Pin name | P17                                                   | P16  | P15  | P14  | P13  | P12  | P11  | P10  |

| PDR1     |                                                       | bit6 | bit5 |      |      | bit2 |      |      |

| DDR1     | bit7                                                  | Dito | טונט | bit4 | bit3 | DILZ | bit1 | bit0 |

| PUL1     |                                                       | -    | -    |      |      | -    |      |      |

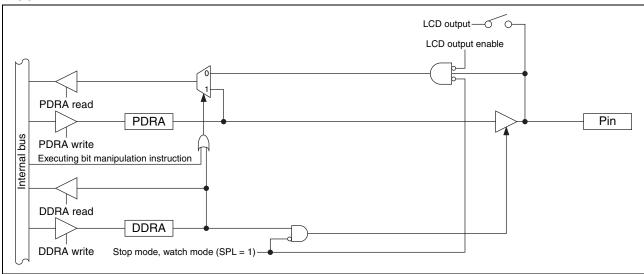

Block diagram of PA0/COM0, PA1/COM1, PA2/COM2, PA3/COM3, PA4/COM4, PA5/COM5, PA6/COM6 and PA7/COM7

# 18.8.3 Port A registers

Port A register functions

| Register abbreviation      | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                              |  |  |  |  |  |

|----------------------------|------|-------------------------|---------------------------------------------|------------------------------------|--|--|--|--|--|

| PDRA                       | 0    | Pin state is "L" level. | PDRA value is "0".                          | As output port, outputs "L" level. |  |  |  |  |  |

| FDRA                       | 1    | Pin state is "H" level. | PDRA value is "1".                          | As output port, outputs "H" level. |  |  |  |  |  |

| DDBA                       | 0    |                         | Port input enabled                          |                                    |  |  |  |  |  |

| DDRA 1 Port output enabled |      |                         |                                             |                                    |  |  |  |  |  |

· Correspondence between registers and pins for port A

|          |      | Correspondence between related register bits and pins |      |      |      |      |      |      |  |

|----------|------|-------------------------------------------------------|------|------|------|------|------|------|--|

| Pin name | PA7  | PA6                                                   | PA5  | PA4  | PA3  | PA2  | PA1  | PA0  |  |

| PDRA     | bit7 | bit6                                                  | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |  |

| DDRA     | DIL! | Dilo                                                  | ນແລ  | DIL4 | טונט | UILZ | DILI | טונט |  |

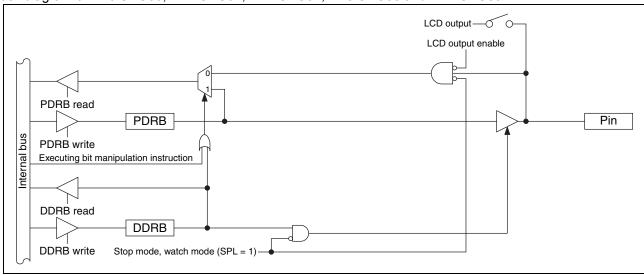

#### 18.9 Port B

Port B is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95710M/770M Series Hardware Manual".

#### 18.9.1 Port B configuration

Port B is made up of the following elements.

- · General-purpose I/O pins/peripheral function I/O pins

- Port B data register (PDRB)

- · Port B direction register (DDRB)

### 18.9.2 Block diagrams of port B

PB0/SEG00 pin

This pin has the following peripheral function:

- LCDC SEG00 output pin (SEG00)

- PB1/SEG01 pin

This pin has the following peripheral function:

- LCDC SEG01 output pin (SEG01)

- PB2/SEG37 pin

This pin has the following peripheral function:

- · LCDC SEG37 output pin (SEG37)

- PB3/SEG38 pin

This pin has the following peripheral function:

- LCDC SEG38 output pin (SEG38)

- · PB4/SEG39 pin

This pin has the following peripheral function:

- LCDC SEG39 output pin (SEG39)

- Block diagram of PB0/SEG00, PB1/SEG01, PB2/SEG37, PB3/SEG38 and PB4/SEG39

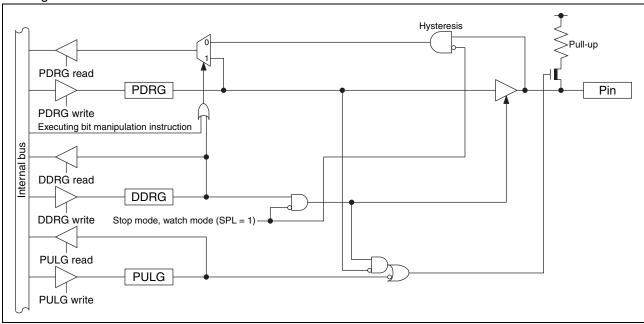

· Block diagram of PG1/X0A and PG2/X1A

# 18.13.3 Port G registers

• Port G register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                              |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|------------------------------------|--|--|--|--|

| PDRG                  | 0    | Pin state is "L" level. | PDRG value is "0".                          | As output port, outputs "L" level. |  |  |  |  |

| 1                     |      | Pin state is "H" level. | PDRG value is "1".                          | As output port, outputs "H" level. |  |  |  |  |

| DDRG                  | 0    |                         | Port input enabled                          |                                    |  |  |  |  |

| DDRG                  | 1    |                         | Port output enable                          | d                                  |  |  |  |  |

| PULG                  | 0    |                         | Pull-up disabled                            |                                    |  |  |  |  |

| FOLG                  | 1    |                         | Pull-up enabled                             |                                    |  |  |  |  |

• Correspondence between registers and pins for port G

|          |   | Correspondence between related register bits and pins |   |   |   |      |      |   |  |

|----------|---|-------------------------------------------------------|---|---|---|------|------|---|--|

| Pin name | - | -                                                     | - | - | - | PG2  | PG1  | - |  |

| PDRG     |   |                                                       |   |   |   |      |      |   |  |

| DDRG     | - | -                                                     | - | - | - | bit2 | bit1 | - |  |

| PULG     |   |                                                       |   |   |   |      |      |   |  |

# 19. I/O Ports (MB95770M Series)

· List of port registers

| Register name                      |       | Read/Write | Initial value |

|------------------------------------|-------|------------|---------------|

| Port 0 data register               | PDR0  | R, RM/W    | 0b00000000    |

| Port 0 direction register          | DDR0  | R/W        | 0b00000000    |

| Port 1 data register               | PDR1  | R, RM/W    | 0b00000000    |

| Port 1 direction register          | DDR1  | R/W        | 0b00000000    |

| Port 2 data register               | PDR2  | R, RM/W    | 0b00000000    |

| Port 2 direction register          | DDR2  | R/W        | 0b00000000    |

| Port 6 data register               | PDR6  | R, RM/W    | 0b00000000    |

| Port 6 direction register          | DDR6  | R/W        | 0b00000000    |

| Port 9 data register               | PDR9  | R, RM/W    | 0b00000000    |

| Port 9 direction register          | DDR9  | R/W        | 0b00000000    |

| Port A data register               | PDRA  | R, RM/W    | 0b00000000    |

| Port A direction register          | DDRA  | R/W        | 0b00000000    |

| Port B data register               | PDRB  | R, RM/W    | 0b0000000     |

| Port B direction register          | DDRB  | R/W        | 0b0000000     |

| Port C data register               | PDRC  | R, RM/W    | 0b0000000     |

| Port C direction register          | DDRC  | R/W        | 0b0000000     |

| Port E data register               | PDRE  | R, RM/W    | 0b0000000     |

| Port E direction register          | DDRE  | R/W        | 0b0000000     |

| Port F data register               | PDRF  | R, RM/W    | 0b0000000     |

| Port F direction register          | DDRF  | R/W        | 0b00000000    |

| Port G data register               | PDRG  | R, RM/W    | 0b00000000    |

| Port G direction register          | DDRG  | R/W        | 0b0000000     |

| Port 1 pull-up register            | PUL1  | R/W        | 0b0000000     |

| Port 2 pull-up register            | PUL2  | R/W        | 0b0000000     |

| Port G pull-up register            | PULG  | R/W        | 0b0000000     |

| A/D input disable register (lower) | AIDRL | R/W        | 0b0000000     |

R/W : Readable/writable (The read value is the same as the write value.)

R, RM/W: Readable/writable (The read value is different from the write value. The write value is read by the read-modify-write (RMW) type of instruction.)

# • P15/SEG31/PPG11 pin

This pin has the following peripheral functions:

- LCDC SEG31 output pin (SEG31)

- 8/16-bit PPG ch. 1 output pin (PPG11)

- P16/SEG30/PPG10 pin

This pin has the following peripheral functions:

- LCDC SEG30 output pin (SEG30)

- 8/16-bit PPG ch. 1 output pin (PPG10)

- Block diagram of P15/SEG31/PPG11 and P16/SEG30/PPG10

# 19.2.3 Port 1 registers

• Port 1 register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                               |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|

| PDR1                  | 0    | Pin state is "L" level. | PDR1 value is "0".                          | As output port, outputs "L" level.  |  |  |  |  |

| 1                     |      | Pin state is "H" level. | PDR1 value is "1".                          | As output port, outputs "H" level.* |  |  |  |  |

| DDR1                  | 0    |                         | Port input enabled                          | d                                   |  |  |  |  |

| DDK1                  | 1    |                         | Port output enabled                         |                                     |  |  |  |  |

| PUL1                  | 0    |                         | Pull-up disabled                            |                                     |  |  |  |  |

| FULI                  | 1    | Pull-up enabled         |                                             |                                     |  |  |  |  |

<sup>\*:</sup> If the pin is an N-ch open drain pin, the pin state becomes Hi-Z.

· Correspondence between registers and pins for port 1

|          | Correspondence between related register bits and pins |      |      |      |      |      |      |      |

|----------|-------------------------------------------------------|------|------|------|------|------|------|------|

| Pin name | P17                                                   | P16  | P15  | P14  | P13  | P12  | P11  | P10  |

| PDR1     |                                                       | bit6 | bit5 |      |      | bit2 |      |      |

| DDR1     | bit7                                                  | Dito | טונט | bit4 | bit3 | DILZ | bit1 | bit0 |

| PUL1     |                                                       | -    | -    |      |      | -    |      |      |

Document Number: 002-09307 Rev. \*D

- Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR1 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open. However, if the interrupt input of P10/UI0/TO0 and P14/UCK0/EC0/TI0 is enabled by the external interrupt control register ch. 0 (EIC00) of the external interrupt circuit and the interrupt pin selection circuit control register (WICR) of the interrupt pin selection circuit, the input is enabled and is not blocked.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

- · Operation of the pull-up register

Setting the bit in the PUL1 register to "1" makes the pull-up resistor be internally connected to the pin. When the pin output is "L" level, the pull-up resistor is disconnected regardless of the value of the PUL1 register.

#### 19.3 Port 2

Port 2 is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95710M/770M Series Hardware Manual".

### 19.3.1 Port 2 configuration

Port 2 is made up of the following elements.

- · General-purpose I/O pins/peripheral function I/O pins

- Port 2 data register (PDR2)

- Port 2 direction register (DDR2)

- Port 2 pull-up register (PUL2)

#### 19.3.2 Block diagrams of port 2

P20/PPG00/CMP0 N pin

This pin has the following peripheral functions:

- 8/16-bit PPG ch. 0 output pin (PPG00)

- Comparator ch. 0 inverting analog input (negative input) pin (CMP0\_N)

- P21/PPG01/CMP0 P pin

This pin has the following peripheral functions:

- 8/16-bit PPG ch. 0 output pin (PPG01)

- Comparator ch. 0 non-inverting analog input (positive input) pin (CMP0 P)

#### 19.4.4 Port 6 operations

- Operation as an output port

- A pin becomes an output port if the bit in the DDR6 register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDR6 register to external pins.

- If data is written to the PDR6 register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDR6 register returns the PDR6 register value.

- To use a pin shared with the LCDC as an output port, set a corresponding function select bit in the LCDC enable register 3 (LCDCE3:SEG[07:06]) or in the LCDC enable register 4 (LCDCE4:SEG[13:08]) to "0" to select the general-purpose I/O port function, and then set the port input control bit in the LCDC enable register 1 (LC-DCE1:PICTL) to "1".

#### · Operation as an input port

- A pin becomes an input port if the bit in the DDR6 register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDR6 register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDR6 register returns the pin value. However, if the read-modify-write (RMW) type of instruction is

used to read the PDR6 register, the PDR6 register value is returned.

- To use a pin shared with the LCDC as an input port, set a corresponding function select bit in the LCDC enable register 3 (LCDCE3:SEG[07:06]) or in the LCDC enable register 4 (LCDCE4:SEG[13:08]) to "0" to select the general-purpose I/O port function, and then set the PICTL bit in the LCDCE1 register to "1".

#### Operation as an LCDC segment output pin

- · Set the bit in the DDR6 register corresponding to an LCDC segment output pin to "0".

- To use a pin shared with a general-purpose I/O port as an LCDC segment output pin, set a corresponding function select bit in the LCDC enable register 3 (LCDCE3:SEG[07:06]) or in the LCDC enable register 4 (LCDCE4:SEG[13:08]) to "1" to select the LCDC segment output function, and then set the PICTL bit in the LCDCE1 register to "1".

#### Operation at reset

If the CPU is reset, all bits in the DDR6 register are initialized to "0" and port input is enabled.

#### Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR6 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

#### 19.6 Port A

Port A is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95710M/770M Series Hardware Manual".

#### 19.6.1 Port A configuration

Port A is made up of the following elements.

- General-purpose I/O pins/peripheral function I/O pins

- Port A data register (PDRA)

- Port A direction register (DDRA)

# 19.6.2 Block diagrams of port A

PA0/COM0 pin

This pin has the following peripheral function:

- LCDC COM0 output pin (COM0)

- PA1/COM1 pin

This pin has the following peripheral function:

- LCDC COM1 output pin (COM1)

- PA2/COM2 pin

This pin has the following peripheral function:

- LCDC COM2 output pin (COM2)

- PA3/COM3 pin

This pin has the following peripheral function:

- LCDC COM3 output pin (COM3)

- PA4/COM4 pin

This pin has the following peripheral function:

- LCDC COM4 output pin (COM4)

- PA5/COM5 pin

This pin has the following peripheral function:

- LCDC COM5 output pin (COM5)

- PA6/COM6 pin

This pin has the following peripheral function:

- LCDC COM6 output pin (COM6)

- PA7/COM7 pin

This pin has the following peripheral function:

• LCDC COM7 output pin (COM7)

# 21. Pin States In Each Mode

| D:         | Normal                                                   | 01                                                       | Stop                                                                           | mode                                                         | Watch                                                                          | mode                                                         | On reset                                                                                       |  |

|------------|----------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| Pin name   | operation                                                | Sleep mode                                               | SPL=0                                                                          | SPL=1                                                        | SPL=0                                                                          | On reset                                                     |                                                                                                |  |

|            | Oscillation input                                        | Oscillation input                                        | Hi-Z                                                                           | Hi-Z                                                         | Hi-Z                                                                           | Hi-Z                                                         | Oscillation input*1                                                                            |  |

| PF0/X0     | I/O port*2                                               | I/O port*2                                               | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*2,*3</li> </ul>    | - Hi-Z<br>- Input<br>blocked*2,*3                            | - Previous state<br>kept<br>- Input<br>blocked*2,*3                            | - Hi-Z<br>- Input<br>blocked*2,*3                            | - Hi-Z<br>- Input enabled*4<br>(However, it<br>does not<br>function.)                          |  |

|            | Oscillation input                                        | Oscillation input                                        | Hi-Z                                                                           | Hi-Z                                                         | Hi-Z                                                                           | Hi-Z                                                         | Oscillation input*1                                                                            |  |

| PF1/X1     | I/O port*2                                               | I/O port*2                                               | - Previous state<br>kept<br>- Input<br>blocked*2,*3                            | - Hi-Z<br>- Input<br>blocked*2,*3                            | - Previous state<br>kept<br>- Input<br>blocked*2,*3                            | - Hi-Z<br>- Input<br>blocked*2,*3                            | - Hi-Z<br>- Input enabled*4<br>(However, it<br>does not<br>function.)                          |  |

|            | Reset input                                              | Reset input                                              | Reset input                                                                    | Reset input                                                  | Reset input                                                                    | Reset input                                                  | Reset input*5                                                                                  |  |

| PF2/RST    | I/O port*2                                               | I/O port*2                                               | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*2,*3</li> </ul>    | - Hi-Z<br>- Input<br>blocked*2,*3                            | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*2,*3</li> </ul>    | - Hi-Z<br>- Input<br>blocked*2, *3                           | <ul> <li>Hi-Z</li> <li>Input enabled*4<br/>(However, it<br/>does not<br/>function.)</li> </ul> |  |

|            | Oscillation input                                        | Oscillation input                                        | Hi-Z                                                                           | Hi-Z                                                         | Hi-Z                                                                           | Hi-Z                                                         | Oscillation input*6                                                                            |  |

| PG1/X0A    | I/O port*2                                               | I/O port*2                                               | - Previous state<br>kept<br>- Input<br>blocked*2,*3                            | - Hi-Z*7<br>- Input<br>blocked*2,*3                          | - Previous state<br>kept<br>- Input<br>blocked*2,*3                            | - Hi-Z*7<br>- Input<br>blocked*2,*3                          | - Hi-Z<br>- Input enabled*4<br>(However, it<br>does not<br>function.)                          |  |

|            | Oscillation input                                        | Oscillation input                                        | Hi-Z                                                                           | Hi-Z                                                         | Hi-Z                                                                           | Hi-Z                                                         | Oscillation input*6                                                                            |  |

| PG2/X1A    | I/O port*2                                               | I/O port*2                                               | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*2,*3</li> </ul>    | - Hi-Z*7<br>- Input<br>blocked*2,*3                          | - Previous state<br>kept<br>- Input<br>blocked*2,*3                            | - Hi-Z* <sup>7</sup><br>- Input<br>blocked* <sup>2, *3</sup> | - Hi-Z<br>- Input enabled*4<br>(However, it<br>does not<br>function.)                          |  |

| D00/INT02/ | I/O port/<br>peripheral<br>function I/O/<br>analog input | I/O port/<br>peripheral<br>function I/O/<br>analog input | - Previous state<br>kept<br>- Input<br>blocked* <sup>3</sup> , * <sup>10</sup> | - Hi-Z<br>- Input<br>blocked* <sup>3</sup> , * <sup>10</sup> | - Previous state<br>kept<br>- Input<br>blocked* <sup>3</sup> , * <sup>10</sup> | - Hi-Z<br>- Input<br>blocked* <sup>3</sup> , * <sup>10</sup> | - Hi-Z<br>- Input blocked* <sup>3</sup>                                                        |  |

| Din nama                                               | Normal Sleep mode Stop mode                              |                                                          |                                                                                |                                                               | Watch                                                                         | On reset                                                      |                                                                                                |

|--------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Pin name                                               | operation                                                | Sieep mode                                               | SPL=0                                                                          | SPL=1                                                         | SPL=0                                                                         | On reset                                                      |                                                                                                |

| SEG32*8/<br>UCK1                                       | I/O port/<br>peripheral<br>function I/O/<br>analog input | I/O port/<br>peripheral<br>function I/O/<br>analog input | - Previous state<br>kept<br>- Input<br>blocked* <sup>3</sup> , * <sup>10</sup> | - Hi-Z<br>- Input<br>blocked* <sup>3</sup> , * <sup>10</sup>  | - Previous state<br>kept<br>- Input<br>blocked*3, *10                         | - Hi-Z<br>- Input<br>blocked* <sup>3</sup> , * <sup>10</sup>  | - Hi-Z<br>- Input blocked* <sup>3</sup>                                                        |

| P10/UI0/                                               | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept<br>- Input blocked*3                                  | - Hi-Z* <sup>7</sup><br>- Input blocked* <sup>3</sup>         | - Previous state<br>kept<br>- Input blocked*3                                 | - Hi-Z* <sup>7</sup><br>- Input blocked* <sup>3</sup>         | - Hi-Z<br>- Input enabled*4<br>(However, it<br>does not<br>function.)                          |

|                                                        | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | <ul> <li>Previous state</li> <li>kept</li> <li>Input blocked*3</li> </ul>      | "H"                                                           | <ul> <li>Previous state</li> <li>kept</li> <li>Input blocked*3</li> </ul>     | "H"                                                           | "H"                                                                                            |

|                                                        | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept<br>- Input blocked*3                                  | - Hi-Z* <sup>7</sup><br>- Input blocked* <sup>3</sup>         | - Previous state<br>kept<br>- Input blocked*3                                 | - Hi-Z* <sup>7</sup><br>- Input blocked* <sup>3</sup>         | - Hi-Z<br>- Input enabled*4<br>(However, it<br>does not<br>function.)                          |

| P15/<br>SEG31*8/<br>PPG11<br>P16/<br>SEG30*8/<br>PPG10 | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept<br>- Input blocked*3                                  | - Hi-Z<br>- Input blocked*3                                   | - Previous state<br>kept<br>- Input blocked*3                                 | - Hi-Z<br>- Input blocked*3                                   | - Hi-Z<br>- Input blocked* <sup>3</sup>                                                        |

| CMP0_O                                                 | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | - Previous state<br>kept*11<br>- Input blocked*3                               | - Hi-Z* <sup>7</sup><br>- Input blocked* <sup>3</sup>         | - Previous state<br>kept*11<br>- Input blocked*3                              | - Hi-Z* <sup>7</sup><br>- Input blocked* <sup>3</sup>         | <ul> <li>Hi-Z</li> <li>Input enabled*4<br/>(However, it<br/>does not<br/>function.)</li> </ul> |

| CMP0_N<br>P21/                                         | I/O port/<br>peripheral<br>function I/O/<br>analog input | I/O port/<br>peripheral<br>function I/O/<br>analog input | - Previous state<br>kept<br>- Input blocked*3,<br>*12                          | - Hi-Z* <sup>7</sup><br>- Input blocked* <sup>3,</sup><br>*12 | <ul> <li>Previous state<br/>kept</li> <li>Input blocked*3,<br/>*12</li> </ul> | - Hi-Z* <sup>7</sup><br>- Input blocked* <sup>3,</sup><br>*12 | - Hi-Z<br>- Input enabled* <sup>4</sup>                                                        |

| P22/SCL                                                | I/O port/<br>peripheral<br>function I/O                  | I/O port/<br>peripheral<br>function I/O                  | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*3, *13</li> </ul>  | - Hi-Z<br>- Input<br>blocked*3,*13                            | <ul> <li>Previous state<br/>kept</li> <li>Input<br/>blocked*3, *13</li> </ul> | - Hi-Z<br>- Input<br>blocked*3, *13                           | - Hi-Z<br>- Input enabled*4                                                                    |

# 22. Electrical Characteristics

# 22.1 Absolute Maximum Ratings

| Donomoton                              | Cumbal               | Rating     |            | Unit | Domostro                                                                                  |  |  |

|----------------------------------------|----------------------|------------|------------|------|-------------------------------------------------------------------------------------------|--|--|

| Parameter                              | Symbol               | Min        | Max        | Unit | Remarks                                                                                   |  |  |

| Power supply voltage*1                 | Vcc                  | Vss - 0.3  | Vss + 6    | V    |                                                                                           |  |  |

| Input voltage*1                        | Vı                   | Vss - 0.3  | Vss + 6    | V    | *2                                                                                        |  |  |

| Output voltage*1                       | Vo                   | Vss - 0.3  | Vss + 6    | V    | *2                                                                                        |  |  |

| Maximum clamp current                  | ICLAMP               | -2         | +2         | mA   | Applicable to specific pins*3                                                             |  |  |

| Total maximum clamp current            | $\Sigma$   $ CLAMP $ | _          | 20         | mA   | Applicable to specific pins*3                                                             |  |  |

| "L" level maximum output current       | lol                  | _          | 15         | mA   |                                                                                           |  |  |

| "L" level average current              | lolav                | _          | 4          | mA   | Average output current = operating current × operating ratio (1 pin)                      |  |  |

| "L" level total maximum output current | $\Sigma$ loL         | _          | 100        | mA   |                                                                                           |  |  |

| "L" level total average output current | $\Sigma$ lolav       | _          | 50         | mA   | Total average output current = operating current × operating ratio (Total number of pins) |  |  |

| "H" level maximum output current       | Іон                  | _          | -15        | mA   |                                                                                           |  |  |

| "H" level average current              | Іонач                | _          | -4         | mA   | Average output current = operating current × operating ratio (1 pin)                      |  |  |

| "H" level total maximum output current | ΣІон                 | _          | -100       | mA   |                                                                                           |  |  |

| "H" level total average output current | $\Sigma$ Iohav       | _          | <b>–50</b> | mA   | Total average output current = operating current × operating ratio (Total number of pins) |  |  |

| Power consumption                      | Pd                   |            | 320        | mW   |                                                                                           |  |  |

| Operating temperature                  | Та                   | -40        | +85        | °C   |                                                                                           |  |  |

| Storage temperature                    | Tstg                 | <b>-55</b> | +150       | °C   |                                                                                           |  |  |

<sup>\*1:</sup> These parameters are based on the condition that Vss is 0.0 V.

- Use under recommended operating conditions.

- Use with DC voltage (current).

- The HV (High Voltage) signal is an input signal exceeding the Vcc voltage. Always connect a limiting resistor between the HV (High Voltage) signal and the microcontroller before applying the HV (High Voltage) signal.

<sup>\*2:</sup> V₁ and V₀ must not exceed Vcc + 0.3 V. V₁ must not exceed the rated voltage. However, if the maximum current to/from an input is limited by means of an external component, the Iclamp rating is used instead of the V₁ rating.

<sup>\*3:</sup> Specific pins: P00 to P07, P10, P11, P13 to P16, P20 to P22, P40 to P43, P50 to P53, P60 to P67, P90 to P94, PA0 to PA7, PB0 to PB4, PC0 to PC7, PE0 to PE7, PF0, PF1, PG1, PG2 (P40 to P43, P50 to P53, P94, PB2 to PB4 and PC4 to PC7 are only available on the MB95710M Series.)

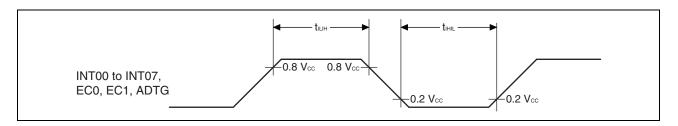

# 22.4.5 Peripheral Input Timing

| Parameter                        | Symbol   | Pin name                  | Va       | Unit |       |

|----------------------------------|----------|---------------------------|----------|------|-------|

| Farameter                        | Syllibol | Fill liaille              | Min      | Max  | Offic |

| Peripheral input "H" pulse width | tılıH    | INT00 to INT07, EC0, EC1, | 2 tmclk* | _    | ns    |

| Peripheral input "L" pulse width | tıнıL    | ADTG                      | 2 tmclk* | _    | ns    |

<sup>\*:</sup> See "Source Clock/Machine Clock" for tmclk.

# 22.4.6 Low-voltage Detection

Normal mode

$(V_{CC} = 1.8 \text{ V to } 5.5 \text{ V}, \text{Vss} = 0.0 \text{ V}, \text{TA} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

|                                                           | •                |       |      |      | .0 0.0 | $\frac{1}{100}$                                                                                 |  |

|-----------------------------------------------------------|------------------|-------|------|------|--------|-------------------------------------------------------------------------------------------------|--|

| Parameter                                                 | Symbol           | Value |      |      | Unit   | Remarks                                                                                         |  |

| i didilietei                                              | Symbol           | Min   | Тур  | Max  | Offic  | Remarks                                                                                         |  |

| Reset release voltage                                     | $V_{PDL+}$       | 1.88  | 2.03 | 2.18 | V      | At power supply rise                                                                            |  |

| Reset detection voltage                                   | V <sub>PDL</sub> | 1.8   | 1.93 | 2.06 | V      | At power supply fall                                                                            |  |

| Interrupt release voltage 0                               | VIDL0+           | 2.13  | 2.3  | 2.47 | V      | At power supply rise                                                                            |  |

| Interrupt detection voltage 0                             | VIDL0-           | 2.05  | 2.2  | 2.35 | V      | At power supply fall                                                                            |  |

| Interrupt release voltage 1                               | VIDL1+           | 2.41  | 2.6  | 2.79 | V      | At power supply rise                                                                            |  |

| Interrupt detection voltage 1                             | VIDL1-           | 2.33  | 2.5  | 2.67 | V      | At power supply fall                                                                            |  |

| Interrupt release voltage 2                               | VIDL2+           | 2.69  | 2.9  | 3.11 | V      | At power supply rise                                                                            |  |

| Interrupt detection voltage 2                             | VIDL2-           | 2.61  | 2.8  | 2.99 | V      | At power supply fall                                                                            |  |

| Interrupt release voltage 3                               | VIDL3+           | 3.06  | 3.3  | 3.54 | V      | At power supply rise                                                                            |  |

| Interrupt detection voltage 3                             | VIDL3-           | 2.98  | 3.2  | 3.42 | V      | At power supply fall                                                                            |  |

| Interrupt release voltage 4                               | VIDL4+           | 3.43  | 3.7  | 3.97 | V      | At power supply rise                                                                            |  |

| Interrupt detection voltage 4                             | VIDL4-           | 3.35  | 3.6  | 3.85 | V      | At power supply fall                                                                            |  |

| Interrupt release voltage 5                               | VIDL5+           | 3.81  | 4.1  | 4.39 | V      | At power supply rise                                                                            |  |

| Interrupt detection voltage 5                             | VIDL5-           | 3.73  | 4    | 4.27 | V      | At power supply fall                                                                            |  |

| Power supply start voltage                                | Voff             | _     | _    | 1.6  | V      |                                                                                                 |  |

| Power supply end voltage                                  | Von              | 4.39  | _    | _    | V      |                                                                                                 |  |

| Power supply voltage change time (at power supply rise)   | <b>t</b> r       | 697.5 | _    | _    | μs     | Slope of power supply that the reset release signal generates within the rating (VPDL+/VIDL+)   |  |

| Power supply voltage change time (at power supply fall)   | tr               | 697.5 | _    | _    | μs     | Slope of power supply that the reset detection signal generates within the rating (VPDL-/VIDL-) |  |

| Reset release delay time                                  | <b>t</b> dp1     | _     | _    | 30   | μs     |                                                                                                 |  |

| Reset detection delay time                                | tdp2             |       | _    | 30   | μs     |                                                                                                 |  |

| Interrupt release delay time                              | <b>t</b> di1     | _     | _    | 30   | μs     |                                                                                                 |  |

| Interrupt detection delay time                            | <b>t</b> di2     | _     | _    | 30   | μs     |                                                                                                 |  |

| Interrupt threshold voltage transition stabilization time | <b>t</b> stb     |       | _    | 30   | μs     |                                                                                                 |  |

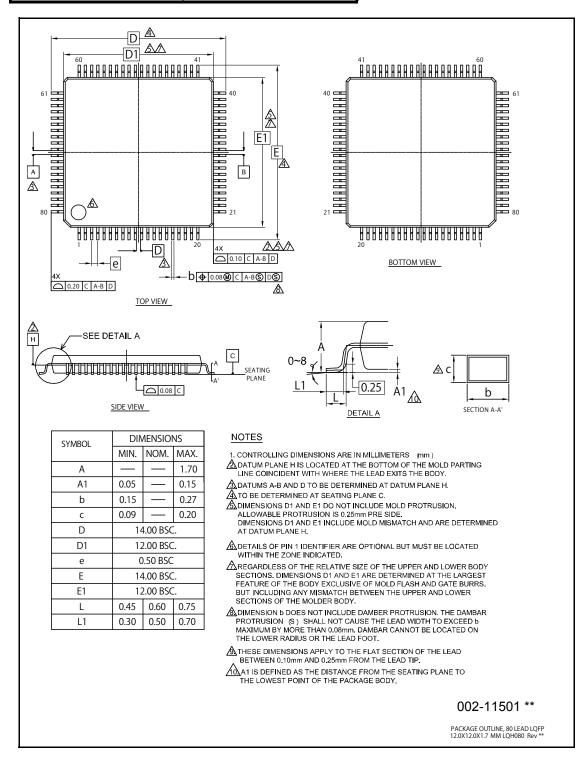

# 26. Package Dimension

| Package Type | Package Code |

|--------------|--------------|

| LQFP 80      | LQH 080      |