Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Deteile                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Details                    |                                                                                 |

| Product Status             | Obsolete                                                                        |

| Core Processor             | F <sup>2</sup> MC-8FX                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                                               |

| Peripherals                | LCD, POR, PWM, WDT                                                              |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 60KB (60K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/12b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f778mpmc2-g-sne2 |

- Low-voltage detection (LVD) circuit (only available on MB95F714J/F716J/F718J/F774J/F776J/F778J)

- □ Built-in low-voltage detection function

- Comparator × 1 channel

- Clock supervisor counter

- □ Built-in clock supervisor counter

- Dual operation Flash memory

- ☐ The program/erase operation and the read operation can be executed in different banks (upper bank/lower bank) simultaneously.

- Flash memory security function

- □ Protects the content of the Flash memory.

Document Number: 002-09307 Rev. \*D Page 2 of 172

# 1. Product Line-up

# 1.1 MB95710M Series

| Part number                    | Series                                                                                                                                                                                                                                                                                                                                                                          |                                                                       |                    |                                                                   |                        |            |  |  |  |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|-------------------------------------------------------------------|------------------------|------------|--|--|--|--|--|

|                                | MB95F714J                                                                                                                                                                                                                                                                                                                                                                       | MB95F716J                                                             | MB95F718J          | MB95F714M                                                         | MB95F716M              | MB95F718M  |  |  |  |  |  |

| Parameter                      |                                                                                                                                                                                                                                                                                                                                                                                 | 2001 7 700                                                            | 2001 7 700         |                                                                   | 2001 1 10              |            |  |  |  |  |  |

| Туре                           | Flash memory product                                                                                                                                                                                                                                                                                                                                                            |                                                                       |                    |                                                                   |                        |            |  |  |  |  |  |

| Clock                          | - identification product                                                                                                                                                                                                                                                                                                                                                        |                                                                       |                    |                                                                   |                        |            |  |  |  |  |  |

|                                | It supervises the                                                                                                                                                                                                                                                                                                                                                               | t supervises the main clock oscillation and the subclock oscillation. |                    |                                                                   |                        |            |  |  |  |  |  |

| Flash memory capacity          | 20 Kbyte                                                                                                                                                                                                                                                                                                                                                                        | 36 Kbyte                                                              | 60 Kbyte           | 20 Kbyte                                                          | 36 Kbyte               | 60 Kbyte   |  |  |  |  |  |

| RAM capacity                   | 512 bytes                                                                                                                                                                                                                                                                                                                                                                       | 1 Kbyte                                                               | 2 Kbyte            | 512 bytes                                                         | 1 Kbyte                | 2 Kbyte    |  |  |  |  |  |

| Power-on reset                 |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                       | Ye                 | es                                                                |                        |            |  |  |  |  |  |

| Low-voltage<br>detection reset |                                                                                                                                                                                                                                                                                                                                                                                 | Yes                                                                   |                    |                                                                   | No                     |            |  |  |  |  |  |

| Reset input                    | Sele                                                                                                                                                                                                                                                                                                                                                                            | cted through soft                                                     | ware               | With                                                              | dedicated reset        | input      |  |  |  |  |  |

| CPU functions                  | Number of basic instructions : 136 Instruction bit length : 8 bits Instruction length : 1 to 3 bytes Data bit length : 1, 8 and 16 bits Minimum instruction execution time : 61.5 ns (machine clock frequency = 16.25 MHz) Interrupt processing time : 0.6 μs (machine clock frequency = 16.25 MHz)                                                                             |                                                                       |                    |                                                                   |                        |            |  |  |  |  |  |

| General-<br>purpose I/O        | <ul><li>I/O port</li><li>CMOS I/O</li><li>N-ch open drai</li></ul>                                                                                                                                                                                                                                                                                                              | : 75<br>: 71<br>n : 4                                                 |                    | <ul><li>I/O port</li><li>CMOS I/O</li><li>N-ch open dra</li></ul> | : 74<br>: 71<br>in : 3 |            |  |  |  |  |  |

| Time-base timer                | Interval time: 0.2                                                                                                                                                                                                                                                                                                                                                              | 56 ms to 8.3 s (e                                                     | xternal clock freq | uency = 4 MHz)                                                    |                        |            |  |  |  |  |  |

|                                | The sub-CR cle                                                                                                                                                                                                                                                                                                                                                                  | on clock at 10 MF<br>ock can be used                                  | as the source clo  | ock of the softwar                                                | e watchdog timer       | :          |  |  |  |  |  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                 | replace 3 bytes                                                       | of data.           |                                                                   |                        |            |  |  |  |  |  |

| 0/12 510                       | 8 channels                                                                                                                                                                                                                                                                                                                                                                      |                                                                       |                    |                                                                   |                        |            |  |  |  |  |  |

|                                |                                                                                                                                                                                                                                                                                                                                                                                 | solution can be se                                                    | elected.           |                                                                   |                        |            |  |  |  |  |  |

|                                | 2 channels                                                                                                                                                                                                                                                                                                                                                                      |                                                                       |                    |                                                                   |                        |            |  |  |  |  |  |

| 8/16-bit<br>composite timer    | <ul> <li>The timer can be configured as an "8-bit timer × 2 channels" or a "16-bit timer × 1 channel".</li> <li>It has the following functions: interval timer function, PWC function, PWM function and input capture function.</li> <li>Count clock: it can be selected from internal clocks (seven types) and external clocks.</li> <li>It can output square wave.</li> </ul> |                                                                       |                    |                                                                   |                        |            |  |  |  |  |  |

|                                | 8 channels                                                                                                                                                                                                                                                                                                                                                                      |                                                                       |                    |                                                                   |                        |            |  |  |  |  |  |

| External<br>interrupt          |                                                                                                                                                                                                                                                                                                                                                                                 | ge detection (The                                                     |                    |                                                                   | -                      | selected.) |  |  |  |  |  |

| On-chip debug                  | <ul><li>1-wire serial co</li><li>It supports seri</li></ul>                                                                                                                                                                                                                                                                                                                     | ontrol<br>al writing (asynch                                          | nronous mode).     |                                                                   |                        |            |  |  |  |  |  |

| <b>─</b> Part number              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |                                                            |                  |           |                                         |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------|------------------|-----------|-----------------------------------------|--|--|--|

|                                   | MB95F774J                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MB95F776J                      | MB95F778J                                                  | MB95F774M        | MB95F776M | MB95F778M                               |  |  |  |

| Parameter                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |                                                            |                  |           |                                         |  |  |  |

| r drameter                        | 3 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                |                                                            |                  |           |                                         |  |  |  |

| UART/SIO                          | <ul> <li>Data transfer with UART/SIO is enabled.</li> <li>It has a full duplex double buffer, variable data length (5/6/7/8 bits), an internal baud rate generator and an error detection function.</li> <li>It uses the NRZ type transfer format.</li> <li>LSB-first data transfer and MSB-first data transfer are available to use.</li> <li>Both clock asynchronous (UART) serial data transfer and clock synchronous (SIO) serial data transfer are enabled.</li> </ul>         |                                |                                                            |                  |           |                                         |  |  |  |

|                                   | 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |                                                            |                  |           |                                         |  |  |  |

| I <sup>2</sup> C bus<br>interface | <ul> <li>It has the follow</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |                                                            |                  |           | irection detection<br>ART conditions.   |  |  |  |

|                                   | 2 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                |                                                            |                  |           |                                         |  |  |  |

| 8/16-bit PPG                      | <ul><li>Each channel of</li><li>The counter of</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                            |                                | in "8-bit timer $\times$ 2 in be selected from             |                  |           | nannel".                                |  |  |  |

|                                   | 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |                                                            |                  |           |                                         |  |  |  |

| 16-bit reload<br>timer            | <ul><li>It can output so</li><li>Count clock: it</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                          | quare wave.<br>can be selected | ter operating mod<br>from internal cloc<br>reload mode and | ks (seven types) |           | cks.                                    |  |  |  |

| Event counter                     | posite timer ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 1.<br>nt counter functio     |                                                            |                  |           | and 8/16-bit com-<br>posite timer ch. 1 |  |  |  |

| LCD controller<br>(LCDC)          | <ul> <li>COM output: 4 or 8 (max) (selectable)</li> <li>SEG output: 28 or 32 (max) (selectable)</li> <li>If the number of COM outputs is 4, the maximum number of SEG outputs is 32, and the maximum number of pixels that can be displayed 128 (4 × 32).</li> <li>If the number of COM outputs is 8, the maximum number of SEG outputs is 28, and the maximum number of pixels that can be displayed 224 (8 × 28).</li> <li>LCD drive power supply (bias) pins: 4 (max)</li> </ul> |                                |                                                            |                  |           |                                         |  |  |  |

|                                   | <ul> <li>Duty LCD mode</li> <li>LCD standby mode</li> <li>Blinking function</li> <li>Internal divider resistor whose resistance value can be selected from 10 kΩ or 100 kΩ through software</li> <li>Interrupt in sync with the LCD module frame frequency</li> <li>Inverted display function</li> </ul>                                                                                                                                                                            |                                |                                                            |                  |           |                                         |  |  |  |

| Watch counter                     | <ul> <li>Count clock: four selectable clock sources (125 ms, 250 ms, 500 ms or 1 s)</li> <li>The counter value can be selected from 0 to 63. (The watch counter can count for one minute when the clock source is one second and the counter value is set to 60.)</li> </ul>                                                                                                                                                                                                        |                                |                                                            |                  |           |                                         |  |  |  |

| Watch prescaler                   | Eight different tin                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ne intervals can b             | oe selected.                                               |                  |           |                                         |  |  |  |

| Comparator                        | 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |                                                            |                  |           |                                         |  |  |  |

| Din no  | D:       | I/O circuit | Function                                                         |             | I/O type |      |      |

|---------|----------|-------------|------------------------------------------------------------------|-------------|----------|------|------|

| Pin no. | Pin name | type*1      | Function                                                         | Input       | Output   | OD*2 | PU*3 |

|         | P00      |             | General-purpose I/O port                                         |             |          |      |      |

| 0       | INT00    | 147         | External interrupt input pin                                     | Hysteresis/ | CMOS/    |      |      |

| 9       | AN00     | W           | 8/12-bit A/D converter analog input pin                          | analog      | LCD      | _    | _    |

|         | UO2      |             | UART/SIO ch. 2 data output pin                                   |             |          |      |      |

| 40      | P16      | V           | General-purpose I/O port                                         | Livetanasia | CMCC     |      |      |

| 10      | PPG10    | Y           | 8/16-bit PPG ch. 1 output pin                                    | Hysteresis  | CMOS     |      |      |

| 44      | P15      | Y           | General-purpose I/O port                                         | Liveteresia | CMOC     |      |      |

| 11      | PPG11    | Y           | 8/16-bit PPG ch. 1 output pin                                    | Hysteresis  | CMOS     | _    |      |

| 40      | P14      | 1.1         | General-purpose I/O port                                         | Livetanasia | CMCC     |      |      |

| 12      | UCK0     | Н           | UART/SIO ch. 0 clock I/O pin                                     | Hysteresis  | CMOS     |      | О    |

| 40      | P13      | 11          | General-purpose I/O port                                         | Liveteresia | CMOC     |      | 0    |

| 13      | ADTG     | Н           | 8/12-bit A/D converter trigger input pin                         | Hysteresis  | CMOS     | _    | О    |

| 14      | P12      | D           | General-purpose I/O port                                         | Llyotoropio | CMOS     | О    |      |

| 14      | DBG      | D           | DBG input pin                                                    | Hysteresis  | CIVIOS   | U    |      |

| 15      | P11      | Н           | General-purpose I/O port                                         | Llyotoropio | CMOS     |      | 0    |

| 15      | UO0      | П           | UART/SIO ch. 0 data output pin                                   | Hysteresis  | CIVIOS   |      | U    |

| 16      | P10      | G           | General-purpose I/O port                                         | CMOS        | CMOS     |      | О    |

| 10      | UI0      | G           | UART/SIO ch. 0 data input pin                                    | CIVIOS      | CIVIOS   |      | U    |

| 17      | P53      | Н           | General-purpose I/O port                                         | Hysteresis  | CMOS     |      | О    |

| 17      | TO0      | 11          | 16-bit reload timer ch. 0 output pin                             | Trysteresis | CIVIOS   |      |      |

|         | P52      |             | General-purpose I/O port                                         |             |          |      |      |

| 18      | TI0      | Н           | 16-bit reload timer ch. 0 input pin                              | Hysteresis  | CMOS     | _    | О    |

|         | TO00     |             | 8/16-bit composite timer ch. 0 output pin                        |             |          |      |      |

|         | P51      |             | General-purpose I/O port                                         |             |          |      |      |

| 19      | EC0      | Н           | 8/16-bit composite timer ch. 0 clock input pin                   | Hysteresis  | CMOS     |      | О    |

| 20      | P50      | Н           | General-purpose I/O port                                         | Hysteresis  | CMOS     |      | О    |

| 20      | TO01     | 11          | 8/16-bit composite timer ch. 0 output pin                        | Trysteresis | OWO      |      | O    |

| 21      | P23      | ı           | General-purpose I/O port                                         | CMOS        | CMOS     | О    |      |

| 21      | SDA      | •           | I <sup>2</sup> C bus interface ch. 0 data I/O pin                | OWICO       | OWO      | O    |      |

| 22      | P22      | ı           | General-purpose I/O port                                         | CMOS        | CMOS     | О    |      |

|         | SCL      | '           | I <sup>2</sup> C bus interface ch. 0 clock I/O pin               | CIVIOO      | 3,4100   |      |      |

|         | P21      |             | General-purpose I/O port                                         |             |          |      |      |

| 23      | PPG01    | Т           | 8/16-bit PPG ch. 0 output pin                                    | Hysteresis/ | CMOS     | _    | О    |

|         | CMP0_P   | •           | Comparator ch. 0 non-inverting analog input (positive input) pin | analog      |          |      | ,    |

| D:      | D:       | I/O circuit                    | Franchica                           |                          | I/O type        |      |      |   |

|---------|----------|--------------------------------|-------------------------------------|--------------------------|-----------------|------|------|---|

| Pin no. | Pin name | type*1                         | Function                            | Input                    | Output          | OD*2 | PU*3 |   |

|         | P90      |                                | General-purpose I/O port            | Hysteresis/              | CMOS/           |      |      |   |

| 21      | 21       |                                | R                                   |                          | LCD power       | LCD  | _    | _ |

|         | V4       |                                | LCD drive power supply pin          | supply                   | power supply    |      |      |   |

|         | P91      |                                | General-purpose I/O port            |                          | CMOS/           |      |      |   |

| 22      |          | R                              | Constant part posts in a post       | Hysteresis/<br>LCD power | LCD             |      |      |   |

| 22      | V3       | IX                             | LCD drive power supply pin          | supply                   | power           |      |      |   |

|         | P92      |                                | General-purpose I/O port            |                          | supply<br>CMOS/ |      |      |   |

|         | F92      | _                              | General-purpose 1/O port            | Hysteresis/              | LCD             |      |      |   |

| 23      | V2       | R                              | LCD drive power supply pin          | LCD power supply         | power           |      |      |   |

|         |          |                                |                                     | Зарріу                   | supply          |      |      |   |

|         | P93      |                                | General-purpose I/O port            | Hysteresis/              | CMOS/<br>LCD    |      |      |   |

| 24      | V1       | R                              | LCD drive power supply pin          | LCD power                | power           |      |      |   |

|         |          |                                | Los anto ponor supply pin           | supply                   | supply          |      |      |   |

| 25      | PA0      | M                              | General-purpose I/O port            | Hysteresis               | CMOS/           |      |      |   |

| 25      | COM0     | IVI                            | LCDC COM0 output pin                | Trysteresis              | LCD             |      |      |   |

| 26      | PA1      | M                              | General-purpose I/O port            | - Hysteresis             | CMOS/           |      |      |   |

| 20      | COM1     | IVI                            | LCDC COM1 output pin                | Trystorosis              | LCD             |      |      |   |

| 27      | PA2      | M                              | General-purpose I/O port            | - Hysteresis             | CMOS/           |      |      |   |

|         | COM2     | 141                            | LCDC COM2 output pin                | Tryotorcolo              | LCD             |      |      |   |

| 28      | PA3      | M                              | General-purpose I/O port            | Hysteresis               | CMOS/           | _    |      |   |

|         | COM3     |                                | LCDC COM3 output pin                | 11,000.00.0              | LCD             |      |      |   |

| 29      | PA4      | M                              | General-purpose I/O port            | Hysteresis               | CMOS/           | _    |      |   |

|         | COM4     |                                | LCDC COM4 output pin                | 1.7010.00.0              | LCD             |      |      |   |

| 30      | PA5      | M                              | General-purpose I/O port            | Hysteresis               | CMOS/           | _    |      |   |

|         | COM5     |                                | LCDC COM5 output pin                | ,                        | LCD             |      |      |   |

| 31      | PA6      | M                              | General-purpose I/O port            | Hysteresis               | CMOS/           | _    | _    |   |

|         | COM6     |                                | LCDC COM6 output pin                | ,                        | LCD             |      |      |   |

| 32      | PA7      | М                              | General-purpose I/O port            | Hysteresis               | CMOS/           | _    | _    |   |

|         | COM7     |                                | LCDC COM7 output pin                |                          | LCD             |      |      |   |

| 33      | Vss      |                                | Power supply pin (GND)              | _                        |                 | _    |      |   |

| 34      | PF1      | В                              | General-purpose I/O port            | Hysteresis               | CMOS            | _    |      |   |

|         | X1       |                                | Main clock I/O oscillation pin      | ,                        |                 |      |      |   |

| 35      | PF0      | В                              | General-purpose I/O port            | Hysteresis               | CMOS            | _    | _    |   |

|         | X0       |                                | Main clock input oscillation pin    |                          |                 |      |      |   |

| 36      | С        |                                | Decoupling capacitor connection pin | _                        | _               |      | _    |   |

| 37      | PG2      | PG2 C General-purpose I/O port |                                     | Hysteresis               | CMOS            | _    | О    |   |

| -       | X1A C    |                                | Subclock I/O oscillation pin        |                          |                 |      |      |   |

| Type | Circuit                                                                                                 | Remarks                                                |

|------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| W    | P-ch Digital output Digital output  Analog input  Analog input control Standby control Hysteresis input | CMOS output     Hysteresis input     Analog input      |

| Y    | P-ch Digital output Digital output Standby control Hysteresis input                                     | <ul><li>CMOS output</li><li>Hysteresis input</li></ul> |

### Storage of Semiconductor Devices

Because plastic chip packages are formed from plastic resins, exposure to natural environmental conditions will cause absorption of moisture. During mounting, the application of heat to a package that has absorbed moisture can cause surfaces to peel, reducing moisture resistance and causing packages to crack. To prevent, do the following:

- (1) Avoid exposure to rapid temperature changes, which cause moisture to condense inside the product. Store products in locations where temperature changes are slight.

- (2) Use dry boxes for product storage. Products should be stored below 70% relative humidity, and at temperatures between 5°C and 30°C.

- When you open Dry Package that recommends humidity 40% to 70% relative humidity.

- (3) When necessary, Cypress packages semiconductor devices in highly moisture-resistant aluminum laminate bags, with a silica gel desiccant. Devices should be sealed in their aluminum laminate bags for storage.

- (4) Avoid storing packages where they are exposed to corrosive gases or high levels of dust.

#### Baking

Packages that have absorbed moisture may be de-moisturized by baking (heat drying). Follow the Cypress recommended conditions for baking.

Condition: 125°C/24 h

### Static Electricity

Because semiconductor devices are particularly susceptible to damage by static electricity, you must take the following precautions:

- (1) Maintain relative humidity in the working environment between 40% and 70%. Use of an apparatus for ion generation may be needed to remove electricity.

- (2) Electrically ground all conveyors, solder vessels, soldering irons and peripheral equipment.

- (3) Eliminate static body electricity by the use of rings or bracelets connected to ground through high resistance (on the level of 1 M $\Omega$ ).

- Wearing of conductive clothing and shoes, use of conductive floor mats and other measures to minimize shock loads is recommended.

- (4) Ground all fixtures and instruments, or protect with anti-static measures.

- (5) Avoid the use of styrofoam or other highly static-prone materials for storage of completed board assemblies.

### 8.3 Precautions for Use Environment

Reliability of semiconductor devices depends on ambient temperature and other conditions as described above.

For reliable performance, do the following:

(1) Humidity

Prolonged use in high humidity can lead to leakage in devices as well as printed circuit boards. If high humidity levels are anticipated, consider anti-humidity processing.

(2) Discharge of Static Electricity

When high-voltage charges exist close to semiconductor devices, discharges can cause abnormal operation. In such cases, use anti-static measures or processing to prevent discharges.

(3) Corrosive Gases, Dust, or Oil

Exposure to corrosive gases or contact with dust or oil may lead to chemical reactions that will adversely affect the device. If you use devices in such conditions, consider ways to prevent such exposure or to protect the devices.

| Address                | Register abbreviation | Register name                                              | R/W | Initial value |

|------------------------|-----------------------|------------------------------------------------------------|-----|---------------|

| 0x007E                 | ILR5                  | Interrupt level setting register 5                         | R/W | 0b11111111    |

| 0x007F                 | _                     | (Disabled)                                                 | _   | _             |

| 0x0F80                 | WRARH0                | Wild register address setting register (upper) ch. 0       | R/W | 0b00000000    |

| 0x0F81                 | WRARL0                | Wild register address setting register (lower) ch. 0       | R/W | 0b00000000    |

| 0x0F82                 | WRDR0                 | Wild register data setting register ch. 0                  | R/W | 0b00000000    |

| 0x0F83                 | WRARH1                | Wild register address setting register (upper) ch. 1       | R/W | 0b00000000    |

| 0x0F84                 | WRARL1                | Wild register address setting register (lower) ch. 1       | R/W | 0b00000000    |

| 0x0F85                 | WRDR1                 | Wild register data setting register ch. 1                  | R/W | 0b00000000    |

| 0x0F86                 | WRARH2                | Wild register address setting register (upper) ch. 2       | R/W | 0b00000000    |

| 0x0F87                 | WRARL2                | Wild register address setting register (lower) ch. 2       | R/W | 0b00000000    |

| 0x0F88                 | WRDR2                 | Wild register data setting register ch. 2                  | R/W | 0b00000000    |

| 0x0F89<br>to<br>0x0F91 | _                     | (Disabled)                                                 |     | _             |

| 0x0F92                 | T01CR0                | 8/16-bit composite timer 01 status control register 0      | R/W | 0b00000000    |

| 0x0F93                 | T00CR0                | 8/16-bit composite timer 00 status control register 0      | R/W | 0b00000000    |

| 0x0F94                 | T01DR                 | 8/16-bit composite timer 01 data register                  | R/W | 0b00000000    |

| 0x0F95                 | T00DR                 | 8/16-bit composite timer 00 data register                  | R/W | 0b00000000    |

| 0x0F96                 | TMCR0                 | 8/16-bit composite timer 00/01 timer mode control register | R/W | 0b00000000    |

| 0x0F97                 | T11CR0                | 8/16-bit composite timer 11 status control register 0      | R/W | 0b00000000    |

| 0x0F98                 | T10CR0                | 8/16-bit composite timer 10 status control register 0      | R/W | 0b00000000    |

| 0x0F99                 | T11DR                 | 8/16-bit composite timer 11 data register                  | R/W | 0b00000000    |

| 0x0F9A                 | T10DR                 | 8/16-bit composite timer 10 data register                  | R/W | 0b00000000    |

| 0x0F9B                 | TMCR1                 | 8/16-bit composite timer 10/11 timer mode control register | R/W | 0b00000000    |

| 0x0F9C                 | PPS01                 | 8/16-bit PPG01 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0F9D                 | PPS00                 | 8/16-bit PPG00 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0F9E                 | PDS01                 | 8/16-bit PPG01 duty setting buffer register                | R/W | 0b11111111    |

| 0x0F9F                 | PDS00                 | 8/16-bit PPG00 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA0                 | PPS11                 | 8/16-bit PPG11 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0FA1                 | PPS10                 | 8/16-bit PPG10 cycle setting buffer register               | R/W | 0b11111111    |

| 0x0FA2                 | PDS11                 | 8/16-bit PPG11 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA3                 | PDS10                 | 8/16-bit PPG10 duty setting buffer register                | R/W | 0b11111111    |

| 0x0FA4                 | PPGS                  | 8/16-bit PPG start register                                | R/W | 0b00000000    |

| 0x0FA5                 | REVC                  | 8/16-bit PPG output inversion register                     | R/W | 0b00000000    |

| 0.0546                 | TMRH0                 | 16-bit reload timer timer register (upper) ch. 0           | DAA | 050000000     |

| 0x0FA6                 | TMRLRH0               | 16-bit reload timer reload register (upper) ch. 0          | R/W | 0b00000000    |

- · Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDR1 register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open. However, if the interrupt input of P10/UI0/TO0 and P14/UCK0/EC0/TI0 is enabled by the external interrupt control register ch. 0 (EIC00) of the external interrupt circuit and the interrupt pin selection circuit control register (WICR) of the interrupt pin selection circuit, the input is enabled and is not blocked.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

- · Operation of the pull-up register

Setting the bit in the PUL1 register to "1" makes the pull-up resistor be internally connected to the pin. When the pin output is "L" level, the pull-up resistor is disconnected regardless of the value of the PUL1 register.

#### 19.3 Port 2

Port 2 is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95710M/770M Series Hardware Manual".

### 19.3.1 Port 2 configuration

Port 2 is made up of the following elements.

- · General-purpose I/O pins/peripheral function I/O pins

- Port 2 data register (PDR2)

- Port 2 direction register (DDR2)

- Port 2 pull-up register (PUL2)

#### 19.3.2 Block diagrams of port 2

P20/PPG00/CMP0 N pin

This pin has the following peripheral functions:

- 8/16-bit PPG ch. 0 output pin (PPG00)

- Comparator ch. 0 inverting analog input (negative input) pin (CMP0\_N)

- P21/PPG01/CMP0 P pin

This pin has the following peripheral functions:

- 8/16-bit PPG ch. 0 output pin (PPG01)

- Comparator ch. 0 non-inverting analog input (positive input) pin (CMP0 P)

#### 19.8.4 Port C operations

- · Operation as an output port

- · A pin becomes an output port if the bit in the DDRC register corresponding to that pin is set to "1".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- When a pin is used as an output port, it outputs the value of the PDRC register to external pins.

- If data is written to the PDRC register, the value is stored in the output latch and is output to the pin set as an output port as it is.

- Reading the PDRC register returns the PDRC register value.

- To use a pin shared with the LCDC as an output port, set a corresponding function select bit in the LCDC enable register 3 (LCDCE3:SEG[05:02]) to "0" to select the general-purpose I/O port function, and then set the port input control bit in the LCDC enable register 1 (LCDCE1:PICTL) to "1".

### · Operation as an input port

- A pin becomes an input port if the bit in the DDRC register corresponding to that pin is set to "0".

- For a pin shared with other peripheral functions, disable the output of such peripheral functions.

- If data is written to the PDRC register, the value is stored in the output latch but is not output to the pin set as an input port.

- Reading the PDRC register returns the pin value. However, if the read-modify-write (RMW) type of instruction is

used to read the PDRC register, the PDRC register value is returned.

- To use a pin shared with the LCDC as an input port, set a corresponding function select bit in the LCDC enable register 3 (LCDCE3:SEG[05:02]) to "0" to select the general-purpose I/O port function, and then set the PICTL bit in the LCDCE1 register to "1".

### Operation as an LCDC segment output pin

- Set the bit in the DDRC register corresponding to an LCDC segment output pin to "0".

- To use a pin shared with a general-purpose I/O port as an LCDC segment output pin, set a corresponding function select bit in the LCDC enable register 3 (LCDCE3:SEG[05:02]) to "1" to select the LCDC segment output function, and then set the PICTL bit in the LCDCE1 register to "1".

### · Operation at reset

If the CPU is reset, all bits in the DDRC register are initialized to "0" and port input is enabled.

#### Operation in stop mode and watch mode

- If the pin state setting bit in the standby control register (STBC:SPL) is set to "1" and the device transits to stop mode or watch mode, the pin is compulsorily made to enter the high impedance state regardless of the DDRC register value. The input of that pin is locked to "L" level and blocked in order to prevent leaks due to input open.

- If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

• If the pin state setting bit is "0", the state of the port I/O or that of the peripheral function I/O remains unchanged and the output level is maintained.

#### 19.10 Port F

Port F is a general-purpose I/O port. This section focuses on its functions as a general-purpose I/O port. For details of peripheral functions, refer to their respective chapters in "New 8FX MB95710M/770M Series Hardware Manual".

#### 19.10.1 Port F configuration

Port F is made up of the following elements.

- General-purpose I/O pins/peripheral function I/O pins

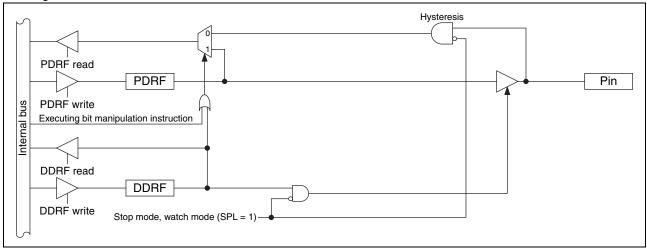

- Port F data register (PDRF)

- Port F direction register (DDRF)

#### 19.10.2 Block diagrams of port F

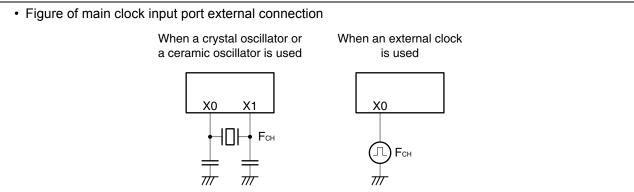

PF0/X0 pin

This pin has the following peripheral function:

- Main clock input oscillation pin (X0)

- PF1/X1 pin

This pin has the following peripheral function:

- Main clock I/O oscillation pin (X1)

- Block diagram of PF0/X0 and PF1/X1

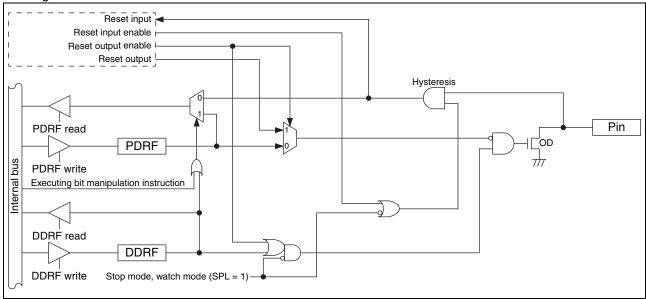

- PF2/RST pin

- This pin has the following peripheral function:

- Reset pin (RST)

- Block diagram of PF2/RST

### 19.10.3 Port F registers

Port F register functions

| Register abbreviation | Data | Read                    | Read by read-modify-write (RMW) instruction | Write                               |  |  |  |  |

|-----------------------|------|-------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|

| PDRF                  | 0    | Pin state is "L" level. | PDRF value is "0".                          | As output port, outputs "L" level.  |  |  |  |  |

| FURF                  | 1    | Pin state is "H" level. | PDRF value is "1".                          | As output port, outputs "H" level.* |  |  |  |  |

| DDRF                  | 0    |                         | Port input enabled                          |                                     |  |  |  |  |

| DDKF                  | 1    |                         | Port output enabled                         |                                     |  |  |  |  |

<sup>\*:</sup> If the pin is an N-ch open drain pin, the pin state becomes Hi-Z.

· Correspondence between registers and pins for port F

|          |   | Correspondence between related register bits and pins |   |   |   |      |      |      |  |  |  |

|----------|---|-------------------------------------------------------|---|---|---|------|------|------|--|--|--|

| Pin name | - | -                                                     | - | - | - | PF2* | PF1  | PF0  |  |  |  |

| PDRF     |   |                                                       |   |   |   | bit2 | bit1 | bit0 |  |  |  |

| DDRF     | 1 | -                                                     | - | - | 1 | DILZ | DILI | DILU |  |  |  |

<sup>\*:</sup> PF2/RST is the dedicated reset pin on MB95F774M/F776M/F778M.

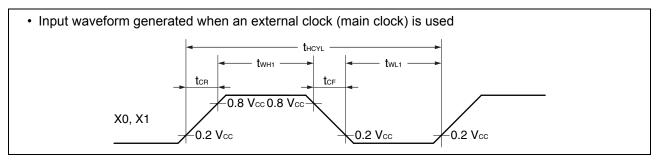

# 22.4 AC Characteristics

22.4.1 Clock Timing

$(Vcc = 1.8 \text{ V to } 5.5 \text{ V}, \text{Vss} = 0.0 \text{ V}, \text{TA} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

| Parameter          | Symbol   | Din namo      | Condition |     | Value |       | Unit  | Remarks                                                                                                                                                           |                                                                                    |                                                                                                                     |                                                                                                 |

|--------------------|----------|---------------|-----------|-----|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Faranietei         | Syllibol | r III IIaiiie | Condition | Min | Тур   | Max   | Ollit |                                                                                                                                                                   |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          | X0, X1        | _         | 1   | _     | 16.25 | MHz   | When the main oscillation circuit is used                                                                                                                         |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          | X0            | _         | 1   | _     | 32.5  | MHz   | When the main external clock is used                                                                                                                              |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          |               |           | 4   | _     | 8.13  | MHz   | Operating conditions  The main clock is used.  PLL multiplication rate: 2                                                                                         |                                                                                    |                                                                                                                     |                                                                                                 |

|                    | Fсн      | V0 V1         |           | 4   | _     | 6.5   | MHz   | Operating conditions  The main clock is used.  PLL multiplication rate: 2.5                                                                                       |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          | X0, X1        | _         | 4   | _     | 5.41  | MHz   | Operating conditions  The main clock is used.  PLL multiplication rate: 3                                                                                         |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          |               |           | 4   | _     | 4.06  | MHz   | Operating conditions The main clock is used. PLL multiplication rate: 4                                                                                           |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          |               |           |     |       | 3.92  | 4     | 4.08                                                                                                                                                              | MHz                                                                                | <ul> <li>Operating conditions</li> <li>The main CR clock is used.</li> <li>0 °C ≤ T<sub>A</sub> ≤ +70 °C</li> </ul> |                                                                                                 |

| Clock<br>frequency | Fcrh     | _             | _         | 3.8 | 4     | 4.2   | MHz   | <ul> <li>Operating conditions</li> <li>The main CR clock is used.</li> <li>- 40 °C ≤ T<sub>A</sub> &lt; 0 °C,<br/>+ 70 °C &lt; T<sub>A</sub> ≤ + 85 °C</li> </ul> |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          | FMCRPLL —     |           |     | 7.84  | 8     | 8.16  | MHz                                                                                                                                                               | Operating conditions • PLL multiplication rate: 2 • 0 °C ≤ T <sub>A</sub> ≤ +70 °C |                                                                                                                     |                                                                                                 |

|                    |          |               |           | 7.6 | 8     | 8.4   | MHz   | Operating conditions • PLL multiplication rate: 2 • − 40 °C ≤ TA < 0 °C, + 70 °C < TA ≤ + 85 °C                                                                   |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          |               |           |     |       |       | 9.8   | 10                                                                                                                                                                | 10.2                                                                               | MHz                                                                                                                 | Operating conditions • PLL multiplication rate: 2.5 • 0 °C ≤ T <sub>A</sub> ≤ +70 °C            |

| F                  | FMCRPLL  |               | _         | 9.5 | 10    | 10.5  | MHz   | Operating conditions • PLL multiplication rate: 2.5 • − 40 °C ≤ T <sub>A</sub> < 0 °C, + 70 °C < T <sub>A</sub> ≤ + 85 °C                                         |                                                                                    |                                                                                                                     |                                                                                                 |

|                    |          |               |           |     | 11.76 | 12    | 12.24 | MHz                                                                                                                                                               | Operating conditions • PLL multiplication rate: 3 • 0 °C ≤ T <sub>A</sub> ≤ +70 °C |                                                                                                                     |                                                                                                 |

|                    |          |               |           |     |       |       | 11.4  | 12                                                                                                                                                                | 12.6                                                                               | MHz                                                                                                                 | Operating conditions • PLL multiplication rate: 3 • − 40 °C ≤ TA < 0 °C, + 70 °C < TA ≤ + 85 °C |

# 22.4.9 Comparator Timing

$(AVcc = 1.8 \text{ V to } 5.5 \text{ V}, AVss = 0.0 \text{ V}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

| Parameter                   | Pin name          |      | Value |      | Unit  | Remarks                               |

|-----------------------------|-------------------|------|-------|------|-------|---------------------------------------|

| Parameter                   | Fill Hallie       | Min  | Тур   | Max  | Ullit | Remarks                               |

| Voltage range               | CMP0_P,<br>CMP0_N | 0    | _     | AVcc | V     |                                       |

| Offset voltage              | CMP0_P,<br>CMP0_N | -20  | _     | +20  | mV    |                                       |

| Delay time                  | CMP0 O            | _    | 600   | 1200 | ns    | Overdrive 5 mV                        |

| Delay tille                 | CIVIFU_O          | _    | 120   | 420  | ns    | Overdrive 50 mV                       |

| Power down delay            | CMP0_O            | _    | _     | 1200 | ns    | Power down recovery PD: 1 → 0         |

| Power down delay            | CIVIPU_O          | 0    | _     | 150  | ns    | Power down<br>PD: 0 → 1               |

| Power up stabilization time | CMP0_O            |      | _     | 1200 | ns    | Output stabilization time at power up |

| Bandgap reference voltage   | _                 | 1.15 | 1.21  | 1.27 | V     |                                       |

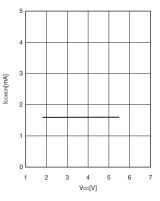

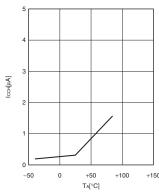

ICCMCR - VCC  $T_A = +25$  °C,  $F_{MP} = 4$  MHz (no division) Main CR clock mode

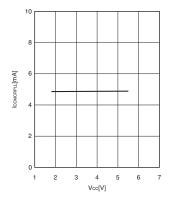

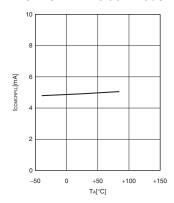

$\mathsf{ICCMCRPLL} - \mathsf{VCC}$

Main CR PLL clock mode

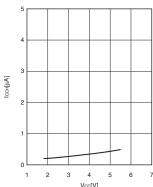

Іссн – Та Vcc = 3.3 V, Fmpl = (stop)Substop mode with the external clock stopping

ICCMCR - TA Vcc = 3.3 V, Fmp = 4 MHz (no division)Main CR clock mode

ICCMCRPLL - TA

$T_A = +25$  °C,  $F_{MP} = 16$  MHz (PLL multiplication rate: 4)  $V_{CC} = 3.3$  V,  $F_{MP} = 16$  MHz (PLL multiplication rate: 4) Main CR PLL clock mode

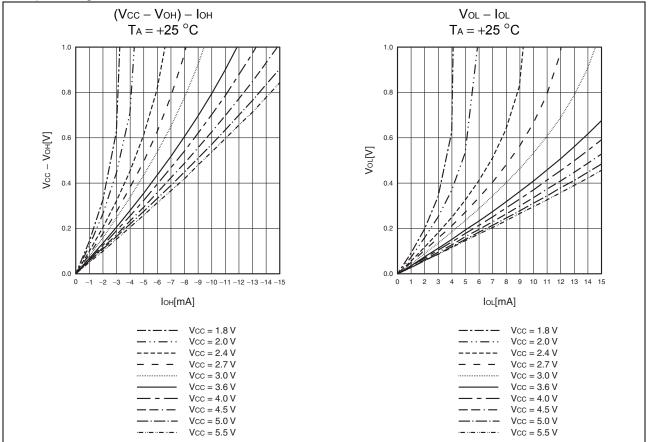

### · Output voltage characteristics

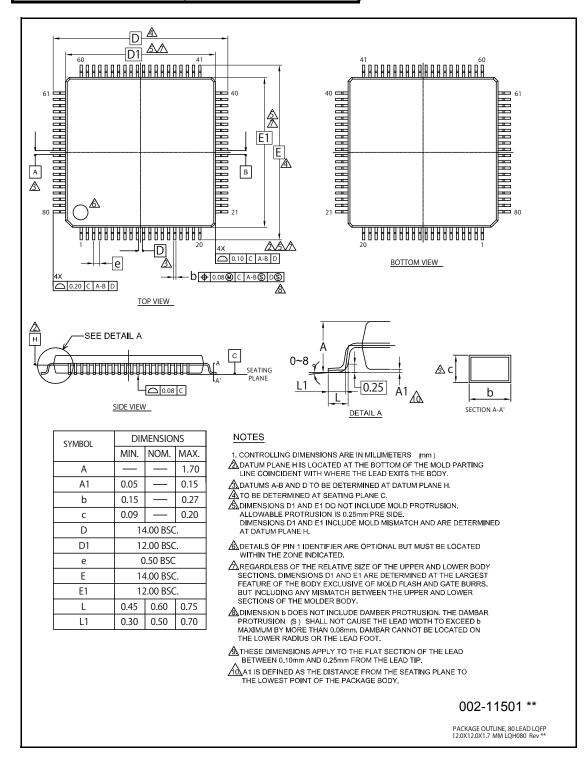

# 26. Package Dimension

| Package Type | Package Code |

|--------------|--------------|

| LQFP 80      | LQH 080      |