Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

| Product Status          | Active                                                         |

|-------------------------|----------------------------------------------------------------|

| Туре                    | Fixed Point                                                    |

| Interface               | I <sup>2</sup> C, SPI                                          |

| Clock Rate              | 150MHz                                                         |

| Non-Volatile Memory     | -                                                              |

| On-Chip RAM             | 128kB                                                          |

| Voltage - I/O           | 3.30V                                                          |

| Voltage - Core          | 1.80V                                                          |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                |

| Mounting Type           | Surface Mount                                                  |

| Package / Case          | 100-LQFP Exposed Pad                                           |

| Supplier Device Package | 100-LQFP-EP (14x14)                                            |

| Purchase URL            | https://www.e-xfl.com/product-detail/cirrus-logic/cs47048c-cqz |

|                         |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

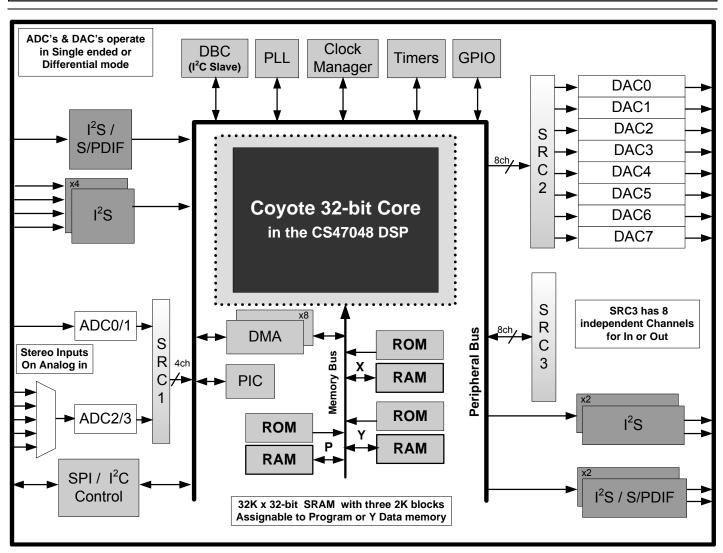

CS47048 Block Diagram

# **1** Documentation Strategy

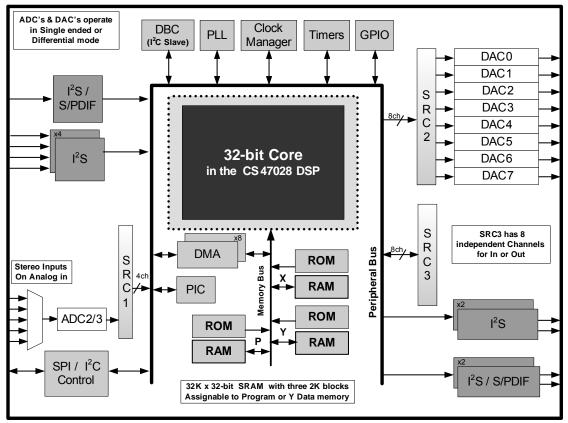

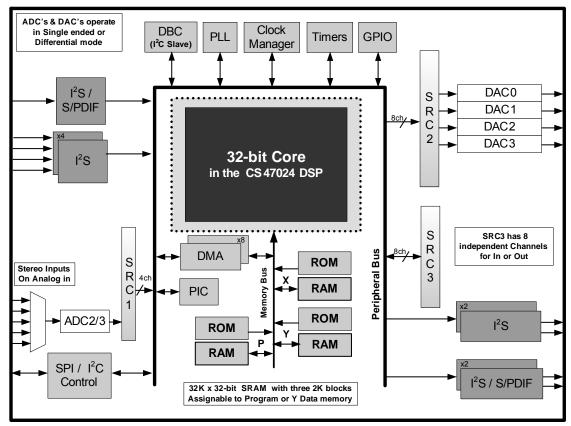

The CS470xx Data Sheet describes the CS47048, CS47028, and CS47024 audio processors. This document should be used in conjunction with the following documents when evaluating or designing a system around the CS470xx processors.

| Table 1-1. | CS470xx Related | Documentation |

|------------|-----------------|---------------|

|------------|-----------------|---------------|

| Document Name                        | Description                                                                                                                                                                                      |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS470xx Data Sheet                   | This document                                                                                                                                                                                    |

| CS470xx Hardware User's Manual Guide | Includes detailed system design information such as typical connection diagrams, boot-proce-<br>dures, and pin descriptions                                                                      |

|                                      | Includes a list of firmware modules available on the CS470xx family platform and detailed firm-<br>ware design information including signal processing flow diagrams and control API information |

| DSP Composer User's Manual           | Includes detailed configuration and usage information for the GUI development tool                                                                                                               |

| CDB470xx User's Manual               | Includes detailed instructions on the use of the CDB470xx development board                                                                                                                      |

The scope of the CS470xx Data Sheet is primarily the hardware specifications of the CS470xx family of devices. This includes hardware functionality, characteristic data, pinout, and packaging information.

The intended audience for the CS470xx Data Sheet is the system PCB designer, MCU programmer, and the quality control engineer.

# 2 Overview

The CS470xx DSP is designed to provide high-performance post-processing and mixing of analog and digital audio. Dual clock domains are supported when the DAI and SPDIF RX inputs are used together. Integrated sample rate converters (SRCs) allow audio streams with different sample rates to be mixed. The low-power standby preserves battery life for applications that are always on, but not necessarily processing audio, such as automotive audio systems.

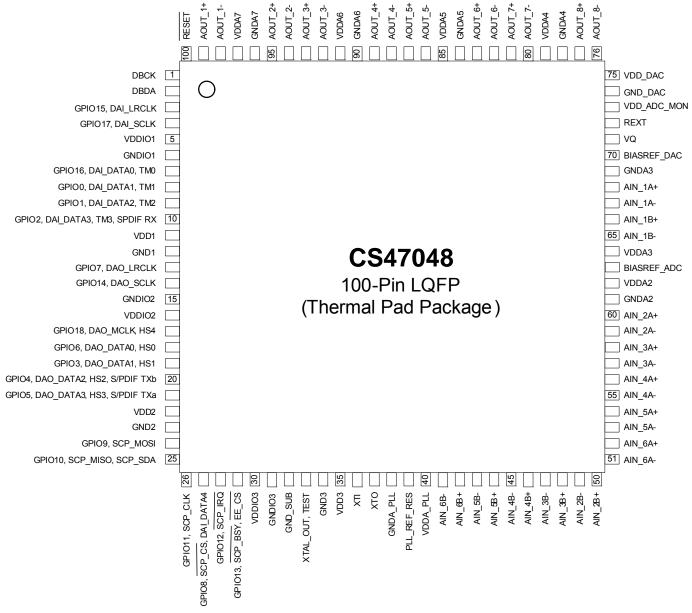

The CS470xx uses voltage-out DACs and is capable of supporting dual input clock domains through the use of the internal SRCs. The CS470xx is available in a 100-pin LQFP package. Refer to Table 3-1 and Table 3-2 for the input, output, and firmware configurations for the CS470xx DSP.

# 2.1 Licensing

Licenses are required for any third-party audio processing algorithms provided for the CS470xx. Contact your local Cirrus Logic Sales representative for more information.

# 3 Code Overlays

The suite of software available for the CS470xx family consists of an operating system (OS) and a library of overlays. The software components for the CS470xx family include:

- 1. OS/Kernel—Encompasses all non-audio processing tasks, including loading data from external serial memory, processing host messages, calling audio-processing subroutines, error concealment, etc.

- Decoder—Any module that performs a compressed audio decode on IEC61937-packed data delivered via S/PDIF Rx or I<sup>2</sup>S input, such as Dolby Digital (AC3).

- 3. *Matrix-processor*—Any Module that performs a matrix decode on PCM data to produce more output channels than input channels (2Æn channels). Examples are Dolby<sup>®</sup> Pro Logic<sup>®</sup> IIx and SRS Circle Surround II<sup>®</sup>. Generally speaking, these modules increase the number of valid channels in the audio I/O buffer.

- 4. *Virtualizer-processor*—Any module that encodes PCM data into fewer output channels than input channels (nÆ2 channels) with the effect of providing "phantom" speakers to represent the physical audio channels that were eliminated. Examples are Dolby Headphone<sup>®</sup> 2 and Dolby<sup>®</sup> Virtual Speaker<sup>®</sup> 2. Generally speaking, these modules reduce the number of valid channels in the audio I/O buffer.

- Post-processors—Any module that processes audio I/O buffer PCM data. Examples are bass management, audio manager, tone control, EQ, delay, customer-specific effects, and any post-processing algorithms available for the CS470xx DSP.

The bulk of standard overlays are stored in ROM within the CS470xx, but a small image is required to configure the overlays and boot the DSP. This small image can either be stored in an external serial flash/EEPROM, or downloaded via a host controller through the SPI/I<sup>2</sup>C serial port.

The overlay structure reduces the time required to reconfigure the DSP when a processing change is requested. Each overlay can be reloaded independently without disturbing the other overlays. For example, when a different post-processor is selected, the OS, does not need to be reloaded—only the new post-processor.

Table 3-1 lists the different configuration options available. Refer to the CS470xx Firmware User's Manual for the latest listing of application codes and Cirrus Framework<sup>™</sup> modules available. See Table 3-2, which provides a summary of the available channels for each type of input and output communication mode for members of the CS470xx family of DSPs.

| Table 3-1. | CS470xx Device Selection Guide |  |

|------------|--------------------------------|--|

|------------|--------------------------------|--|

| Features                                    | CS47048-CQZ<br>CS47048-DQZ                                                                                                                                                                                                            | CS47028-CQZ<br>CS47028-DQZ                                                                                    | CS47024-CQZ<br>CS47024-DQZ                                                                                                                                                              |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Primary Applications                        | <ul> <li>4-In/8-Out Car Audio</li> <li>High-end Digital TV</li> <li>Dual Source/Dual Zone</li> </ul>                                                                                                                                  | <ul> <li>2-In/8-Out Car Audio</li> <li>Sound Bar</li> <li>DVD Receiver</li> </ul>                             | <ul> <li>2-In/4-Out Car Audio</li> <li>Digital TV</li> <li>Portable Audio Docking Station</li> <li>Portable DVD</li> <li>DVD Mini / Receiver</li> <li>Multimedia PC Speakers</li> </ul> |

| Package                                     | 100-pin LQFP with Exposed Pad                                                                                                                                                                                                         |                                                                                                               |                                                                                                                                                                                         |

| DSP Core                                    | Cirrus Logic 32-bit Core                                                                                                                                                                                                              |                                                                                                               |                                                                                                                                                                                         |

| SRAM                                        | 32K x 32-bit SRAM with three 2K bloc                                                                                                                                                                                                  | ks x 32-bit SRAM, assignable to eithe                                                                         | r Y data or program memory                                                                                                                                                              |

| Integrated DAC and ADC                      | <ul> <li>2 Channels of ADC input: with integrated 5:1 analog mux</li> <li>2 additional channels of ADC input: without mux</li> <li>8 channels of DAC output</li> </ul>                                                                | <ul> <li>2 channels of ADC input: with integrated 5:1 analog mux</li> <li>8 channels of DAC output</li> </ul> | <ul> <li>2 channels of ADC input: with inte-<br/>grated 5:1 analog mux</li> <li>4 channels of DAC output</li> </ul>                                                                     |

| Configurable Serial Audio<br>Inputs/Outputs | <ul> <li>Integrated 192 kHz S/PDIF Rx, 2 Ir</li> <li>I2S support for 32-bit Samples @ 1</li> <li>TDM Input modes (Up to 8 channe</li> <li>TDM Output modes (Up to 8 channe</li> </ul>                                                 | 192 kHz<br>Is)                                                                                                |                                                                                                                                                                                         |

| Supports Different Fs<br>Sample Rates       | <ul> <li>Integrated hardware SRC blocks for</li> <li>Additional 8-channel hardware SRG</li> <li>Dual-domain Fs on inputs (I2S and</li> <li>Output can be master or slave</li> </ul>                                                   | C block                                                                                                       |                                                                                                                                                                                         |

| Other Features                              | <ul> <li>Integrated Clock Manager/PLL with</li> <li>Host Control and Boot via SPI/I<sup>2</sup>C S</li> <li>DSP Tool Set w/ Private Keys Prote</li> <li>Configurable GPIOs and External I</li> <li>Hardware Watchdog Timer</li> </ul> | ect Customer IP                                                                                               | ., external crystal, external oscillator                                                                                                                                                |

#### Table 3-2. CS470xx Channel Count

| Product | PCM/TDM In <sup>1</sup>                                                                                               | TDM Out <sup>1</sup>  | PCM<br>Out | ADC with 5:1<br>Input Mux | ADC with-<br>out Mux | DAC<br>Out | S/PDIF In<br>(Stereo<br>Pairs) | S/PDIF<br>Out (Ste-<br>reo Pairs) |

|---------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|------------|---------------------------|----------------------|------------|--------------------------------|-----------------------------------|

| CS47048 | <ul> <li>Up to 5 I2S lines, 2 channels per<br/>line or</li> <li>1 TDM line, up to 8 channels per<br/>line.</li> </ul> | Up to 8 chan-<br>nels | 8          | 2                         | 2                    | 8          | 1                              | 2                                 |

| CS47028 | <ul> <li>Up to 5 I2S lines, 2 channels per<br/>line or</li> <li>1 TDM line, up to 8 channels per<br/>line.</li> </ul> | Up to 8 chan-<br>nels | 8          | 2                         | 0                    | 8          | 1                              | 2                                 |

| CS47024 | <ul> <li>Up to 5 I2S lines, 2 channels per<br/>line or</li> <li>1 TDM line, up to 8 channels per<br/>line.</li> </ul> | Up to 8 chan-<br>nels | 8          | 2                         | 0                    | 4          | 1                              | 2                                 |

1. Contact your Cirrus Logic representative to determine the TDM modes that are supported. The CS470xx can support up to 8 channels per line, but the DSP software provided for the IC can restrict this capability.

Figure 4-3. CS47024 Top-level Block Diagram

#### 4.3.8 Serial Control Port (I<sup>2</sup>C or SPI)

The on-chip serial control port is capable of operating as master or slave in either SPI or I2C modes. Master/Slave operation is chosen by mode select pins when the CS470xx comes out of reset. The serial clock pin can support frequencies as high as 25 MHz in SPI mode (SPI clock speed must always be  $\leq$  (DSP Core Frequency/2)). The CS470xx serial control port also includes a pin for flow control of the communications interface (SCP\_BSY) and a pin to indicate when the DSP has a message for the host (SCP\_IRQ).

#### 4.3.9 GPIO

Many of the CS470xx peripheral pins are multiplexed with GPIO. Each GPIO can be configured as an output, an input, or an input with interrupt. Each input-pin interrupt can be configured as rising edge, falling edge, active-low, or active-high.

#### 4.3.10 PLL-based Clock Generator

The low-jitter PLL generates integer or fractional multiples of a reference frequency, which is used to clock the DSP core and peripherals. Through a second PLL divider chain, a dependent clock domain can be output on the DAO port for driving audio converters. The CS470xx defaults to running from the external reference frequency and is switched to use the PLL output after overlays have been loaded and configured, either through master boot from an external flash or through host control. A built-in crystal oscillator circuit with a buffered output is provided. The buffered output frequency ratio is selectable between 1:1 (default) or 2:1.

#### 4.3.11 Hardware Watchdog Timer

The CS470xx has an integrated watchdog timer that acts as a "health" monitor for the DSP. The watchdog timer must be reset by the DSP before the counter expires, or the entire chip is reset. This peripheral ensures that the CS470xx resets itself in the event of a temporary system failure. In stand-alone mode (where there is no host MCU), the DSP reboots from external flash. In slave mode (where the host MCU is present), a GPIO is used to signal the host that the watchdog has expired and the DSP should be rebooted and re-configured.

#### 4.4 DSP I/O Description

#### 4.4.1 Multiplexed Pins

Many of the CS470xx pins are multifunctional. For details on pin functionality, see Section 10.5, "Pin Assignments", in the CS470xx Hardware User's Manual.

#### 4.4.2 Termination Requirements

Open-drain pins on the CS470xx must be pulled high for proper operation. See the CS470xx Hardware User's Manual to identify which pins are open-drain and what value of pull-up resistor is required for proper operation.

Mode select pins on CS470xx are used to select the boot mode on the rising edge from reset. A detailed explanation of termination requirements for each communication mode select pin can be found in the CS470xx Hardware User's Manual.

#### 4.4.3 Pads

The CS470xx Digital I/Os operate from the 3.3 V supply and are 5 V tolerant.

#### 4.5 Application Code Security

The external program code can be encrypted by the programmer to protect any intellectual property it contains. A secret, customer-specific key is used to encrypt the program code that is to be stored external to the device. Contact your local Cirrus representative for details.

## **5** Characteristics and Specifications

**Note:** All data sheet minimum and maximum timing parameters are guaranteed over the rated voltage and temperature. All data sheet typical parameters are measured under the following conditions: T = 25°C, VDD = 1.8 V, VDDIO = VDDA = 3.3 V, GND = GNDIO = GNDA = 0 V.

## 5.1 Absolute Maximum Ratings

(GND = GNDIO = GNDA = 0V; all voltages with respect to 0V)

| Parameter                                                                       | Symbol               | Min                      | Max                      | Unit           |

|---------------------------------------------------------------------------------|----------------------|--------------------------|--------------------------|----------------|

| DC power supplies:<br>Core supply<br>Analog supply<br>I/O supply<br>IVDDA–VDDIO | VDD<br>VDDA<br>VDDIO | -0.3<br>-0.3<br>-0.3<br> | 2.0<br>3.6<br>3.6<br>0.3 | > > ><br>> > > |

| Input pin current, any pin except supplies                                      | l <sub>in</sub>      | —                        | ±10                      | mA             |

| Input voltage on PLL_REF_RES                                                    | V <sub>filt</sub>    | -0.3                     | 3.6                      | V              |

| Input voltage on digital I/O pins                                               | V <sub>inio</sub>    | -0.3                     | 5.0                      | V              |

| Analog Input Voltage                                                            | V <sub>in</sub>      | AGND-0.7                 | VA+0.7                   | V              |

| Storage temperature                                                             | T <sub>stg</sub>     | -65                      | 150                      | °C             |

**WARNING:** Operation at or beyond these limits can result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

#### 5.2 Recommended Operating Conditions

(GND = GNDIO = GNDA = 0V; all voltages with respect to 0V)

| Parameter                                                                                                         | Symbol               | Min                  | Тур | Max                  | Unit             |

|-------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----|----------------------|------------------|

| DC power supplies:<br>Core supply<br>Analog supply<br>I/O supply<br>IVDDA – VDDIO                                 | VDD<br>VDDA<br>VDDIO | 1.71<br>3.13<br>3.13 | 3.3 | 1.89<br>3.46<br>3.46 | ><br>><br>><br>> |

| Ambient operating temperature<br>Commercial—CQZ (147 MHz)<br>Automotive—DQZ (131 MHz)<br>Automotive—DQZ (113 MHz) | T <sub>A</sub>       | 0<br>-40<br>-40      |     | +70<br>+85<br>+105   | °C               |

**Note:** It is recommended that the 3.3 V IO supply come up ahead of or simultaneously with the 1.8 V core supply.

# 5.3 Digital DC Characteristics

(Measurements performed under static conditions.)

| Parameter                                                                        | Symbol              | Min       | Тур | Max       | Unit |

|----------------------------------------------------------------------------------|---------------------|-----------|-----|-----------|------|

| High-level input voltage                                                         | V <sub>IH</sub>     | 2.0       | _   | —         | V    |

| Low-level input voltage, except XTI                                              | V <sub>IL</sub>     | —         | —   | 0.8       | V    |

| Low-level input voltage, XTI                                                     | V <sub>ILKXTI</sub> | —         |     | 0.6       | V    |

| Input Hysteresis                                                                 | V <sub>hys</sub>    | —         | 0.4 | —         | V    |

| High-level output voltage ( $I_0 = -2mA$ ), except XTO                           | V <sub>OH</sub>     | VDDIO*0.9 | _   | —         | V    |

| Low-level output voltage (I <sub>O</sub> = 2mA), except XTO                      | V <sub>OL</sub>     | —         | _   | VDDIO*0.1 | V    |

| Input leakage XTI                                                                | I <sub>LXTI</sub>   | —         | _   | 5         | μA   |

| Input leakage current (all digital pins with internal pull-up resistors enabled) | I <sub>LEAK</sub>   | —         |     | 70        | μA   |

#### 5.4 Power Supply Characteristics

Note: Measurements performed under operating conditions

| Parameter                                                     | Min | Тур  | Мах | Unit |

|---------------------------------------------------------------|-----|------|-----|------|

| Operational Power Supply Current:                             |     |      |     |      |

| VDD: Core and I/O operating <sup>1</sup>                      |     | 325  |     | mΑ   |

| VDDA: PLL operating current                                   |     | 16   |     | mΑ   |

| VDDA: DAC operating current (all 8 channels enabled)          | —   | 56   |     | mΑ   |

| VDDA: ADC operating current (all 4 channels enabled)          | —   | 34   |     | mΑ   |

| VDDIO: With most ports operating                              | —   | 27   | —   | mA   |

| Total Operational Power Dissipation:                          |     | 1025 |     | mW   |

| Standby Power Supply Current:                                 |     |      |     |      |

| VDD: Core and I/O not clocked                                 |     | 410  |     | μA   |

| VDDA: PLLs halted                                             |     | 26   |     | μA   |

| VDDA: DAC disabled                                            | —   | 40   |     | μA   |

| VDDA: ADC disabled                                            | _   | 24   |     | μA   |

| VDDIO: All connected I/O pins 3-stated by other ICs in system | —   | 215  | —   | μA   |

| Total Standby Power Dissipation:                              |     | 1745 |     | μW   |

1. Dependent on application firmware and DSP clock speed.

#### 5.5 Thermal Data (100-pin LQFP with Exposed Pad)

| Parameter                                                                                                        | Symbol        | Min | Тур         | Max | Unit    |

|------------------------------------------------------------------------------------------------------------------|---------------|-----|-------------|-----|---------|

| Thermal Resistance (Junction to Ambient)<br>Two-layer Board <sup>1</sup><br>Four-layer Board <sup>2</sup>        | $\theta_{ja}$ |     | 34<br>18    | _   | °C/Watt |

| Thermal Resistance (Junction to Top of Package)<br>Two-layer Board <sup>1</sup><br>Four-layer Board <sup>2</sup> | $\psi_{jt}$   |     | 0.54<br>.28 |     | °C/Watt |

1. To calculate the die temperature for a given power dissipation:

$T_i$  = Ambient temperature + [ (Power Dissipation in Watts) \*  $\theta_{ia}$  ]

2. To calculate the case temperature for a given power dissipation:

$T_c = T_j - [$  (Power Dissipation in Watts) \*  $\psi_{jt} ]$

**Note:** Two-layer board is specified as a 76 mm X 114 mm, 1.6 mm thick FR-4 material with 1-oz. copper covering 20% of the top and bottom layers.

Four-layer board is specified as a 76 mm X 114 mm, 1.6 mm thick FR-4 material with 1-oz. copper covering 20% of the top and bottom layers and 0.5-oz. copper covering 90% of the internal power plane and ground plane layers.

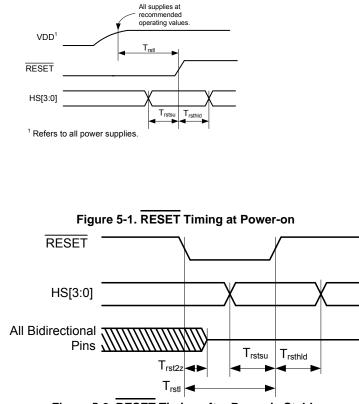

#### 5.6 Digital Switching Characteristics-RESET

| Parameter                                     | Symbol              | Min | Max | Unit |

|-----------------------------------------------|---------------------|-----|-----|------|

| RESET minimum pulse width low <sup>1</sup>    | T <sub>rstl</sub>   | 1   | _   | μs   |

| All bidirectional pins high-Z after RESET low | T <sub>rst2z</sub>  | —   | 200 | ns   |

| Configuration pins setup before RESET high    | T <sub>rstsu</sub>  | 50  | _   | ns   |

| Configuration pins hold after RESET high      | T <sub>rsthld</sub> | 20  | _   | ns   |

1. The rising edge of RESET must not occur before the power supplies are stable at the recommended operating values as described in Section 5.2. In addition, for the configuration pins to be read correctly, the RESET T<sub>rstl</sub> requirement must be met.

Figure 5-2. RESET Timing after Power is Stable

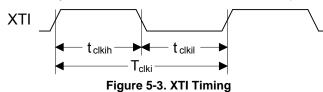

# 5.7 Digital Switching Characteristics-XTI

| Parameter                                                          | Symbol             | Min    | Max    | Unit |

|--------------------------------------------------------------------|--------------------|--------|--------|------|

| External Crystal operating frequency <sup>1</sup>                  | F <sub>xtal</sub>  | 12.288 | 24.576 | MHz  |

| XTI period                                                         | T <sub>clki</sub>  | 41     | 81     | ns   |

| XTI high time                                                      | T <sub>clkih</sub> | 13.3   | —      | ns   |

| XTI low time                                                       | T <sub>clkil</sub> | 13.3   | —      | ns   |

| External Crystal Load Capacitance (parallel resonant) <sup>2</sup> | CL                 | 10     | 18     | pF   |

| External Crystal Equivalent Series Resistance                      | ESR                |        | 50     | Ω    |

1. Part characterized with the following crystal frequency values: 12.288 and 24.576 MHz.

2. C<sub>L</sub> refers to the total load capacitance as specified by the crystal manufacturer. Crystals that require a C<sub>L</sub> outside this range should be avoided. The crystal oscillator circuit design should follow the crystal manufacturer's recommendation for load capacitor selection.

### 5.8 Digital Switching Characteristics–Internal Clock

| Parameter                                                                                                                                        | Symbol            | Min (2-<br>layer Boards)                                                                                                                                            | Min (4-<br>layer Boards)                      | Max (2-<br>layer Boards)                                                                                                               | Max (4-<br>layer Boards) | Unit                                                                                                  |  |                                               |                                               |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|--|-----------------------------------------------|-----------------------------------------------|-----|

| Internal DSP_CLK frequency <sup>1</sup><br>CS47048-CQZ<br>CS47048-DQZ<br>CS47028-CQZ<br>CS47028-DQZ<br>CS47028-DQZ<br>CS47024-CQZ<br>CS47024-DQZ | F <sub>dclk</sub> | (See Footnote 2)<br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub> |                                               | F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub>                                  |                          | F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub><br>F <sub>xtal</sub> |  | 147<br>131<br>147<br>131<br>147<br>147<br>131 | 147<br>147<br>147<br>147<br>147<br>147<br>147 | MHz |

| Internal DSP_CLK period <sup>1</sup><br>CS47048-CQZ<br>CS47048-DQZ<br>CS47028-CQZ<br>CS47028-DQZ<br>CS47028-DQZ<br>CS47024-CQZ<br>CS47024-DQZ    | DCLKP             | 6.8<br>7.6<br>6.8<br>7.6<br>6.8<br>7.6<br>7.6                                                                                                                       | 6.8<br>6.8<br>6.8<br>6.8<br>6.8<br>6.8<br>6.8 | 1/F <sub>xtal</sub><br>1/F <sub>xtal</sub><br>1/F <sub>xtal</sub><br>1/F <sub>xtal</sub><br>1/F <sub>xtal</sub><br>1/F <sub>xtal</sub> |                          | ns                                                                                                    |  |                                               |                                               |     |

1. After initial power-on reset, F<sub>dclk</sub> = F<sub>xtal</sub>. After initial kick-start commands, the PLL is locked to max F<sub>dclk</sub> and remains locked until the next power-on reset.

2. See Section 5.7. for all references to  $F_{xtal}$ .

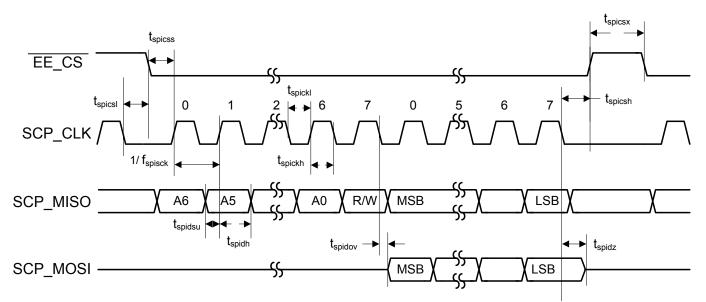

# 5.9 Digital Switching Characteristics-Serial Control Port-SPI Slave Mode

| Parameter                               | Symbol                | Min | Typical    | Max | Unit |

|-----------------------------------------|-----------------------|-----|------------|-----|------|

| SCP_CLK frequency <sup>1</sup>          | f <sub>spisck</sub>   | _   | _          | 25  | MHz  |

| SCP_CS falling to SCP_CLK rising        | t <sub>spicss</sub>   | 24  |            | —   | ns   |

| SCP_CLK low time                        | t <sub>spickl</sub>   | 20  | _          | —   | ns   |

| SCP_CLK high time                       | t <sub>spickh</sub>   | 20  | _          | —   | ns   |

| Setup time SCP_MOSI input               | t <sub>spidsu</sub>   | 5   |            | —   | ns   |

| Hold time SCP_MOSI input                | t <sub>spidh</sub>    | 5   | _          | —   | ns   |

| SCP_CLK low to SCP_MISO output valid    | t <sub>spidov</sub>   | —   | —          | 11  | ns   |

| SCP_CLK falling to SCP_IRQ rising       | t <sub>spiirqh</sub>  | —   | _          | 27  | ns   |

| SCP_CS rising to SCP_IRQ falling        | t <sub>spiirql</sub>  | 0   | _          | —   | ns   |

| SCP_CLK low to SCP_CS rising            | t <sub>spicsh</sub>   | 24  | _          | —   | ns   |

| SCP_CS rising to SCP_MISO output high-Z | t <sub>spicsdz</sub>  | _   | 20         | _   | ns   |

| SCP_CLK rising to SCP_BSY falling       | t <sub>spicbsyl</sub> | —   | 3*DCLKP+20 | _   | ns   |

1. f<sub>spisck</sub> indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port can be limited by the firmware application. Flow control using the SCP\_BSY pin should be implemented to prevent overflow of the input data buffer. At boot the maximum speed is F<sub>xtal</sub>/3.

Figure 5-5. Serial Control Port–SPI Master Mode Timing

#### 5.11 Digital Switching Characteristics–Serial Control Port I<sup>2</sup>C Slave Mode

| Parameter                                                               | Symbol                | Min  | Typical    | Max        | Units |

|-------------------------------------------------------------------------|-----------------------|------|------------|------------|-------|

| SCP_CLK frequency <sup>1</sup>                                          | f <sub>iicck</sub>    | —    | —          | 400        | kHz   |

| SCP_CLK rise time                                                       | t <sub>iicr</sub>     | —    | —          | 150        | ns    |

| SCP_CLK fall time                                                       | t <sub>iicf</sub>     | _    | —          | 150        | ns    |

| SCP_CLK low time                                                        | t <sub>iicckl</sub>   | 1.25 | —          | —          | μs    |

| SCP_CLK high time                                                       | t <sub>iicckh</sub>   | 1.25 | —          | —          | μs    |

| SCP_CLK rising to SCP_SDA rising or falling for START or STOP condition | tiicckcmd             | 1.25 | —          | —          | μs    |

| START condition to SCP_CLK falling                                      | t <sub>iicstscl</sub> | 1.25 | —          | —          | μs    |

| SCP_CLK falling to STOP condition                                       | t <sub>iicstp</sub>   | 2.5  | —          | —          | μs    |

| Bus free time between STOP and START conditions                         | t <sub>iicbft</sub>   | 3    | —          | —          | μs    |

| Setup time SCP_SDA input valid to SCP_CLK rising                        | t <sub>iicsu</sub>    | 110  | —          | —          | ns    |

| Hold time SCP_SDA input after SCP_CLK falling                           | t <sub>iich</sub>     | 100  | —          | —          | ns    |

| SCP_CLK low to SCP_SDA out valid                                        | t <sub>iicdov</sub>   | _    | —          | 18         | ns    |

| SCP_CLK falling to SCP_IRQ rising                                       | t <sub>iicirqh</sub>  | _    | —          | 3*DCLKP+40 | ns    |

| NAK condition to SCP_IRQ low                                            | t <sub>iicirql</sub>  | —    | 3*DCLKP+20 | —          | ns    |

| SCP_CLK rising to SCB_BSY low                                           | t <sub>iicbsyl</sub>  | —    | 3*DCLKP+20 | —          | ns    |

1. f<sub>licck</sub> indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port can be limited by the firmware application. Flow control using the SCP\_BSY pin should be implemented to prevent overflow of the input data buffer.

I<sup>2</sup>C Slave Address = 0x82

#### 5.13 Digital Switching Characteristics–Digital Audio Slave Input Port

| Parameter            | Symbol               | Min | Max                | Unit      |

|----------------------|----------------------|-----|--------------------|-----------|

| DAI_SCLK period      | T <sub>daiclkp</sub> | 20  | _                  | ns        |

| DAI_SCLK duty cycle  | _                    | 45  | 55                 | %         |

| Setup time DAI_DATAn | t <sub>daidsu</sub>  | 8   | _                  | ns        |

| Hold time DAI_DATAn  | t <sub>daidh</sub>   | 5   | _                  | ns        |

| DAI_SCLK             |                      |     |                    | $\square$ |

| DAI_DATAn            |                      |     | — t <sub>dai</sub> | dh<br>    |

Figure 5-8. Digital Audio Input (DAI) Port Timing Diagram

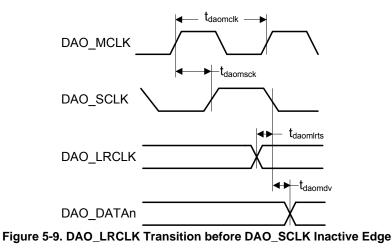

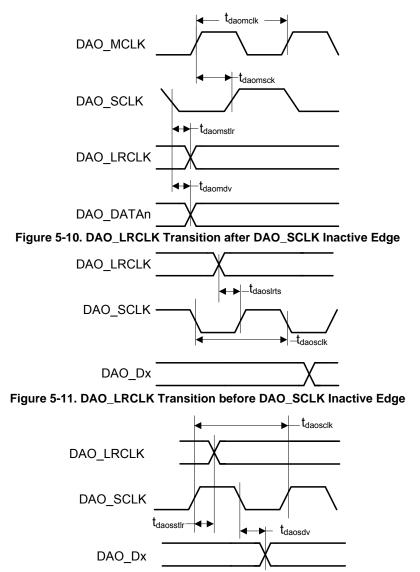

## 5.14 Digital Switching Characteristics–Digital Audio Output Port

| Parameter                                                        | Symbol                | Min | Max | Unit |

|------------------------------------------------------------------|-----------------------|-----|-----|------|

| DAO_MCLK period                                                  | T <sub>daomclk</sub>  | 20  |     | ns   |

| DAO_MCLK duty cycle                                              | —                     | 45  | 55  | %    |

| DAO_SCLK period for Master or Slave mode <sup>1</sup>            | T <sub>daosclk</sub>  | 20  | _   | ns   |

| DAO_SCLK duty cycle for Master or Slave mode1                    | —                     | 40  | 60  | %    |

| Master Mode (Output A1 Mode) <sup>1,2</sup>                      |                       |     |     |      |

| DAO_SCLK delay from DAO_MCLK rising edge, DAO MCLK as an input   | t <sub>daomsck</sub>  | _   | 19  | ns   |

| DAO_LRCLK to DAO_SCLK inactive edge <sup>3</sup> . See Fig. 5-9. | t <sub>daomIrts</sub> | _   | 8   | ns   |

| DAO_SCLK inactive edge <sup>3</sup> to DAO_LRCLK. See Fig. 5-10. | t <sub>daomstir</sub> | _   | 8   | ns   |

| DAO_DATA[3:0] delay from DAO_SCLK inactive edge3                 | t <sub>daomdy</sub>   | _   | 8   | ns   |

| Slave Mode (Output A0 Mode) <sup>4</sup>                         |                       |     |     |      |

| DAO_SCLK active edge to DAO_LRCLK transition. See Fig. 5-11.     | t <sub>daosstir</sub> | 10  | _   | ns   |

| DAO_LRCLK transition to DAO_SCLK active edge. See Fig. 5-12.     | t <sub>daoslrts</sub> | 10  | _   | ns   |

| DAO_Dx delay from DAO_SCLK inactive edge                         | t <sub>daosdv</sub>   | —   | 11  | ns   |

1. Master mode timing specifications are characterized, not production tested.

2. Master mode is defined as the CS47048 driving both DAO\_SCLK, DAO\_LRCLK. When MCLK is an input, it is divided to produce DAO\_SCLK, DAO\_ LRCLK.

3. The DAO\_LRCLK transition can occur on either side of the edge of DAO\_SCLK. The active edge of DAO\_SCLK is the point at which the data is valid.

4. Slave mode is defined as DAO\_SCLK, DAO\_LRCLK driven by an external source.

Figure 5-12. DAO\_LRCLK Transition after DAO\_SCLK Inactive Edge

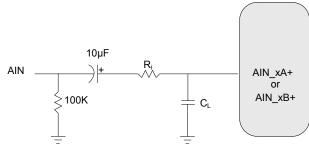

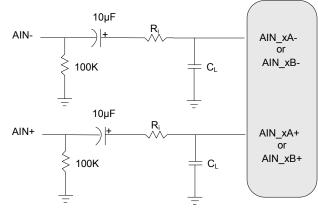

#### 5.16.2 Analog Input Characteristics (Automotive)

Test Conditions (unless otherwise specified): TA =  $-40-85^{\circ}$ C; VDD =  $1.8V\pm5\%$ , VDDA (VA) =  $3.3V\pm5\%$ ; kHz sine wave driven through the passive input filter (R<sub>i</sub> =  $10 \text{ k}\Omega$ ) in Fig. 5-13 or Fig. 5-14; DSP running test application; Measurement Bandwidth is 10 Hz-20 kHz.

|                                                                                                         | Differential  |                          |             | Si            | ngle-end                 | ed          |                      |

|---------------------------------------------------------------------------------------------------------|---------------|--------------------------|-------------|---------------|--------------------------|-------------|----------------------|

| Parameter                                                                                               | Min           | Тур                      | Max         | Min           | Тур                      | Max         | Unit                 |

| Fs = 96 kHz                                                                                             |               |                          |             |               |                          |             |                      |

| Dynamic Range <sup>1,6,7</sup><br>A-weighted<br>Unweighted<br>40 kHz bandwidth unweighted               | 97<br>94<br>— | 105<br>102<br>99         |             | 94<br>91<br>— | 102<br>99<br>96          |             | dB<br>dB<br>dB       |

| Total Harmonic Distortion + Noise <sup>6,7</sup><br>–1 dB<br>–20 dB<br>–60 dB<br>40 kHz bandwidth –1 dB |               | -98<br>-82<br>-42<br>-90 | -90<br><br> |               | -95<br>-79<br>-39<br>-90 | -87<br><br> | dB<br>dB<br>dB<br>dB |

| AIN_1A/B Interchannel Isolation <sup>10</sup>                                                           | _             | 95                       | _           | _             | 95                       | _           | dB                   |

| AID_[2.6]A/B MUX Interchannel Isolation                                                                 |               | 95                       | _           | —             | 95                       | _           | dB                   |

| DC Accuracy                                                                                             |               |                          |             |               |                          |             |                      |

| Interchannel Gain Mismatch                                                                              |               | 0.1                      | —           |               | 0.1                      | _           | dB                   |

| Gain Drift                                                                                              |               | ±120                     | _           | —             | ±120                     | _           | ppm/°C               |

| Analog Input                                                                                            |               |                          |             |               |                          |             |                      |

| Full-scale Input Voltage <sup>2,3</sup>                                                                 | 3.3           | 3.7•VA                   | 3.9         | 1.65          | 1.85•VA                  | 1.95        | V <sub>PP</sub>      |

| Differential Input Impedance <sup>4</sup>                                                               |               | 400                      | —           |               | —                        | —           | Ω                    |

| Single-ended Input Impedance <sup>5</sup>                                                               | —             |                          |             |               | 200                      |             | Ω                    |

| Common Mode Rejection Ratio (CMRR) <sup>8</sup>                                                         | —             | 60                       | —           | —             | —                        | —           | dB                   |

| Parasitic Load Capacitance (C <sub>L</sub> ) <sup>9</sup>                                               | _             | _                        | 20          | _             | _                        | 20          | pF                   |

1. dB units referred to the typical full-scale voltage.

2. These full-scale values were measured with R<sub>i</sub>=10k for both the single-ended and differential mode input circuits.

3. The full-scale voltage can be changed by scaling R<sub>i</sub>. Differential Full-Scale (Vpp) = 3.7\*VDDA\*(Ri+200)/(10k+200)

Single-Ended Full-Scale (Vpp) = 1.85\*VDDA\*(Ri+200)/(10k+200)

4. Measured between AIN\_xx+ and AN\_xx-.

5. Measured between AIN\_xx+ and AGND.

6. Decreasing full-scale voltage by reducing  $\mathsf{R}_i$  causes the noise floor to increase.

- 7. Common mode input current should be kept to less than ±160uA to avoid performance degradation:  $|(I_{ip}+I_{in})/2| < 160uA$ . This corresponds to ±1.6V for R<sub>i</sub>=10 k $\Omega$  in the differential case.

- 8. This number was measured using perfectly matched external resistors ( $R_i$ ). Mismatch in the external resistors typically reduces CMRR by 20 log ( $|\Delta R_i|/R_i + 0.001$ ).

9. CL represents the parasitic load capacitance between Ri on the input circuit and the input pin of the CS47048 package.

10. This measurement is not applicable to the CS47028 and CS47024 devices.

Figure 5-13. ADC Single-ended Input Test Circuit

Figure 5-14. ADC Differential Input Test Circuit

#### 5.16.3 ADC Digital Filter Characteristics

| Parameter <sup>1,2</sup>                        | Min    | Тур                 | Max    | Unit     |

|-------------------------------------------------|--------|---------------------|--------|----------|

| Fs = 96 kHz                                     |        |                     |        |          |

| Passband (Frequency Response) to –0.1 dB corner | 0      | —                   | 0.4896 | Fs       |

| Passband Ripple                                 | —      | _                   | 0.08   | dB       |

| Stopband                                        | 0.5688 | _                   | —      | Fs       |

| Stopband Attenuation                            | 70     | _                   | —      | dB       |

| Total Group Delay                               | —      | 12/Fs               | —      | S        |

| High-pass Filter Characteristics                |        |                     |        |          |

| Frequency Response:<br>–3.0 dB<br>–0.13 dB      | _      | 1<br>20             | _      | Hz<br>Hz |

| Phase Deviation @ 20 Hz                         | —      | 10                  |        | Deg      |

| Passband Ripple                                 | —      | _                   | 0      | dB       |

| Filter Settling Time                            | —      | 10 <sup>5</sup> /Fs | 0      | S        |

1. Filter response is guaranteed by design.

2. Response is clock-dependent and scales with Fs.

#### **5.17 DAC Characteristics**

#### 5.17.1 Analog Output Characteristics (Commercial)

Test Conditions (unless otherwise specified): TA =  $0-+70^{\circ}$ C; VDD =  $1.8V\pm5\%$ , VDDA(VA) =  $3.3V\pm5\%$ ; 1 kHz sine wave driven through a filter shown in Fig. 5-15 or Fig. 5-16; DSP running test application; Measurement Bandwidth is 20 Hz–20 kHz.

|                                                               | D         | Differential   |         |          | Single-ended      |         |                |

|---------------------------------------------------------------|-----------|----------------|---------|----------|-------------------|---------|----------------|

| Parameter                                                     | Min       | Тур            | Max     | Min      | Тур               | Max     | Unit           |

| Fs = 96 kHz                                                   |           |                |         |          |                   |         |                |

| Dynamic Range<br>A-weighted<br>Unweighted                     | 102<br>99 | 108<br>105     | _       | 99<br>96 | 105<br>102        | _       | dB<br>dB       |

| Total Harmonic Distortion + Noise<br>0 dB<br>-20 dB<br>-60 dB |           | 98<br>88<br>48 | -90<br> |          | -95<br>-85<br>-45 | -87<br> | dB<br>dB<br>dB |

| Interchannel Isolation (1 kHz)                                | —         | 95             | —       | —        | 95                | —       | dB             |

# 8 Device Pinout Diagrams

# 8.1 CS47048, 100-pin LQFP Pinout Diagram

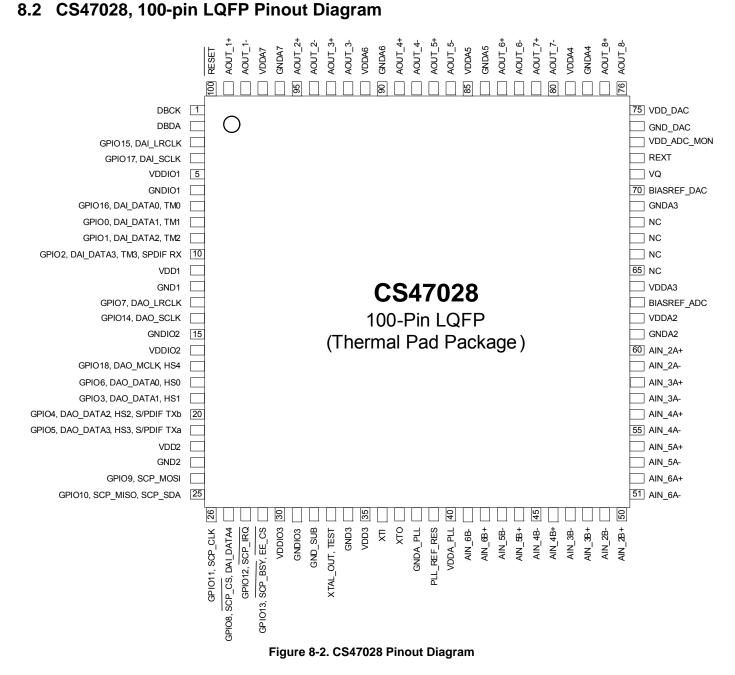

# 0.2 004/020, 100-p

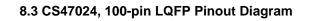

8.3 CS47024, 100-pin LQFP Pinout Diagram

Figure 8-3. CS47024 Pinout Diagram

# **10 Parameter Definitions**

# 10.1 Dynamic Range

The ratio of the RMS value of the signal to the RMS sum of all other spectral components over the specified bandwidth. Dynamic Range is a signal-to-noise ratio measurement over the specified bandwidth made with a -60 dBFS signal. 60 dB is added to resulting measurement to refer the measurement to full-scale. This technique ensures that the distortion components are below the noise level and do not affect the measurement. This measurement technique has been accepted by the Audio Engineering Society, AES17-1991, and the Electronic Industries Association of Japan, EIAJ CP-307. Expressed in decibels.

# 10.2 Total Harmonic Distortion + Noise

The ratio of the RMS value of the signal to the RMS sum of all other spectral components over the specified bandwidth (typically 10 Hz–20 kHz), including distortion components. Expressed in decibels. Measured at –1 and –20 dBFS as suggested in AES17-1991 Annex A.

## **10.3 Frequency Response**

A measure of the amplitude response variation from 10 Hz–20 kHz relative to the amplitude response at 1 kHz. Units in decibels.

## **10.4 Interchannel Isolation**

A measure of crosstalk between the left and right channels. Measured for each channel at the converter's output with no signal to the input under test and a full-scale signal applied to the other channel. Units in decibels.

# **10.5 Interchannel Gain Mismatch**

The gain difference between left and right channels. Units in decibels.

# 10.6 Gain Error

The deviation from the nominal full-scale analog output for a full-scale digital input.

# 10.7 Gain Drift

The change in gain value with temperature. Units in ppm/°C.

# **11 Revision History**

| Revision | Date           | Changes                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PP1      | August, 2009   | Updated Characterization data in Section 5.4, Section 5.7, Section 5.9, Section 5.11, Section 5.12, Section 5.16.1, Section 5.16.2, Section 5.16.3, Section 5.17.1, and Section 5.17.2. Modified Footnote 3 in both Section 5.16.1 and Section 5.16.2. Added Footnote 5 to Section 5.14. Updated Section 2.1. Modified Section 4.3.6 and Section 4.3.8. Modified references to TDM in various sections of the data sheet. |

| PP2      | January, 2010  | Updated TDM Feature description on page 1. Modified note at the bottom of the feature list on page 1. Updated table in Section 5.8, specifying performance data for 2- and 4-layer boards. Updated Table 3-1 and Table 3-2 Updated block diagrams in Fig. 4-1, Fig. 4-2, and Fig. 4-3.                                                                                                                                    |

| PP3      | June, 2010     | Table 3-1: Straddled all three columns in the "Supports Different Fs Sample Rates" row to indicate thatCS47024 devices have the same features as the CS47048 and CS47028.Added "The CS47024 has the 8-channel SRC block" to Section 4.3.7.                                                                                                                                                                                |

|          |                | Added text in the following places to indicate that the CS47024 implements the S/PDIF Rx functionality:                                                                                                                                                                                                                                                                                                                   |

|          |                | Removed dagger from the S/PDIF Rx bullet on p. 1.                                                                                                                                                                                                                                                                                                                                                                         |

|          |                | Updated bullet in "Configurable Serial Audio Inputs/Outputs" row in Table 2 Integrated 192 kHz S/PDIF<br>Rx, 2 Integrated 192 kHz S/PDIF Tx.                                                                                                                                                                                                                                                                              |

|          |                | <ul> <li>Changed entry in "S/PDIF In (Stereo Pairs)" column in Table 3-2.</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

|          |                | Updated I2S block in Table 3-2.                                                                                                                                                                                                                                                                                                                                                                                           |

|          |                | Removed text "On the CS47048 and CS47028" from Section 4.3.4.                                                                                                                                                                                                                                                                                                                                                             |

|          |                | <ul> <li>Removed "(Not available on CS47024)" from the heading to Section 5.15.</li> </ul>                                                                                                                                                                                                                                                                                                                                |

|          |                | <ul> <li>Described additional support for TDM 8-channel output mode on CS47024.</li> </ul>                                                                                                                                                                                                                                                                                                                                |

|          |                | <ul> <li>Removed dagger from the TDM I/O bullet on p. 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |

|          |                | <ul> <li>Straddled "Configurable Serial Audio Inputs/Outputs" row in Table 3-1.</li> </ul>                                                                                                                                                                                                                                                                                                                                |

|          |                | Changed cell in "TDM Out" column in Table 3-2.                                                                                                                                                                                                                                                                                                                                                                            |

|          |                | Removed text "On the CS47048 and CS47028" from Section 4.3.5.                                                                                                                                                                                                                                                                                                                                                             |

| PP4      | February, 2011 | Added "Decoder" information to Section 3. Changed the name of the core to "Cirrus Logic 32-bit core".                                                                                                                                                                                                                                                                                                                     |

| PP5      | February, 2011 | Added "SPDIF RX" to Fig. 5-17.                                                                                                                                                                                                                                                                                                                                                                                            |

| PP6      | June, 2011     | In Section 4.3.1 and Section 4.3.7, removed mention of 192 kHz sampling frequency. Updated temperature operating conditions in Section 5.2. Updated pin 33 to XTAL_OUT, TEST in Fig. 8-1, Fig. 8-2, and Fig. 8-3.                                                                                                                                                                                                         |

| PP7      | April, 2012    | Corrected peak reflow temperature in Table 7-1.                                                                                                                                                                                                                                                                                                                                                                           |

| PP8      | June, 2012     | Added number of bits to Integrated DAC and ADC Functionality on the cover page.                                                                                                                                                                                                                                                                                                                                           |

| PP9      | July, 2012     | Updated frequencies in Section 5.2. Added extended automotive grade information to Section 6 and Section 7.                                                                                                                                                                                                                                                                                                               |