Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | SPI, UART/USART, USI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 54                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega165-16mi |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

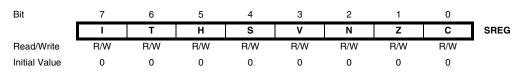

# **Status Register**

The Status Register contains information about the result of the most recently executed arithmetic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the Instruction Set Reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code.

The Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt. This must be handled by software.

The AVR Status Register - SREG - is defined as:

# • Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the Global Interrupt Enable Register is cleared, none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts. The Ibit can also be set and cleared by the application with the SEI and CLI instructions, as described in the instruction set reference.

### • Bit 6 – T: Bit Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or destination for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.

# • Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry Is useful in BCD arithmetic. See the "Instruction Set Description" for detailed information.

#### Bit 4 – S: Sign Bit, S = N ⊕ V

The S-bit is always an exclusive or between the Negative Flag N and the Two's Complement Overflow Flag V. See the "Instruction Set Description" for detailed information.

# • Bit 3 – V: Two's Complement Overflow Flag

The Two's Complement Overflow Flag V supports two's complement arithmetics. See the "Instruction Set Description" for detailed information.

# • Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

#### Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

# ATmega165/V

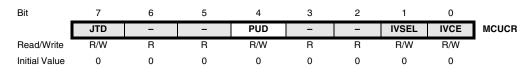

#### MCU Control Register – MCUCR

#### • Bit 4 – PUD: Pull-up Disable

When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ( $\{DDxn, PORTxn\} = 0b01$ ). See "Configuring the Pin" on page 56 for more details about this feature.

# Alternate Functions of Port B The Port B pins with alternate functions are shown in Table 27.

Table 27. Port B Pins Alternate Functions

| Port Pin | Alternate Functions                                                                          |

|----------|----------------------------------------------------------------------------------------------|

| PB7      | OC2A/PCINT15 (Output Compare and PWM Output A for Timer/Counter2 or Pin Change Interrupt15). |

| PB6      | OC1B/PCINT14 (Output Compare and PWM Output B for Timer/Counter1 or Pin Change Interrupt14). |

| PB5      | OC1A/PCINT13 (Output Compare and PWM Output A for Timer/Counter1 or Pin Change Interrupt13). |

| PB4      | OC0A/PCINT12 (Output Compare and PWM Output A for Timer/Counter0 or Pin Change Interrupt12). |

| PB3      | MISO/PCINT11 (SPI Bus Master Input/Slave Output or Pin Change Interrupt11).                  |

| PB2      | MOSI/PCINT10 (SPI Bus Master Output/Slave Input or Pin Change Interrupt10).                  |

| PB1      | SCK/PCINT9 (SPI Bus Serial Clock or Pin Change Interrupt9).                                  |

| PB0      | SS/PCINT8 (SPI Slave Select input or Pin Change Interrupt8).                                 |

The alternate pin configuration is as follows:

# • OC2A/PCINT15, Bit 7

OC2, Output Compare Match A output: The PB7 pin can serve as an external output for the Timer/Counter2 Output Compare A. The pin has to be configured as an output (DDB7 set (one)) to serve this function. The OC2A pin is also the output pin for the PWM mode timer function.

PCINT15, Pin Change Interrupt source 15: The PB7 pin can serve as an external interrupt source.

# • OC1B/PCINT14, Bit 6

OC1B, Output Compare Match B output: The PB6 pin can serve as an external output for the Timer/Counter1 Output Compare B. The pin has to be configured as an output (DDB6 set (one)) to serve this function. The OC1B pin is also the output pin for the PWM mode timer function.

PCINT14, Pin Change Interrupt Source 14: The PB6 pin can serve as an external interrupt source.

# 16-bit Timer/Counter Register Description

Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     | _      |

|---------------|--------|--------|--------|--------|---|---|-------|-------|--------|

|               | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | WGM11 | WGM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R | R | R/W   | R/W   | •      |

| Initial Value | 0      | 0      | 0      | 0      | 0 | 0 | 0     | 0     |        |

#### • Bit 7:6 - COM1A1:0: Compare Output Mode for Unit A

#### • Bit 5:4 - COM1B1:0: Compare Output Mode for Unit B

The COM1A1:0 and COM1B1:0 control the Output Compare pins (OC1A and OC1B respectively) behavior. If one or both of the COM1A1:0 bits are written to one, the OC1A output overrides the normal port functionality of the I/O pin it is connected to. If one or both of the COM1B1:0 bit are written to one, the OC1B output overrides the normal port functionality of the I/O pin it is connected to. However, note that the *Data Direction Register* (DDR) bit corresponding to the OC1A or OC1B pin must be set in order to enable the output driver.

When the OC1A or OC1B is connected to the pin, the function of the COM1x1:0 bits is dependent of the WGM13:0 bits setting. Table 48 shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to a Normal or a CTC mode (non-PWM).

| Table 48. | Compare Output Mode, non-PWM |

|-----------|------------------------------|

|-----------|------------------------------|

| COM1A1/COM1B1 | COM1A0/COM1B0 | Description                                                 |

|---------------|---------------|-------------------------------------------------------------|

| 0             | 0             | Normal port operation, OC1A/OC1B disconnected.              |

| 0             | 1             | Toggle OC1A/OC1B on Compare Match.                          |

| 1             | 0             | Clear OC1A/OC1B on Compare Match (Set output to low level). |

| 1             | 1             | Set OC1A/OC1B on Compare Match (Set output to high level).  |

Table 49 shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to the fast PWM mode.

Table 49. Compare Output Mode, Fast PWM<sup>(1)</sup>

| COM1A1/COM1B1 | COM1A0/COM1B0 | Description                                                                                                                                                                       |

|---------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0             | Normal port operation, OC1A/OC1B disconnected.                                                                                                                                    |

| 0             | 1             | WGM13:0 = 14 or 15: Toggle OC1A on Compare<br>Match, OC1B disconnected (normal port<br>operation). For all other WGM1 settings, normal<br>port operation, OC1A/OC1B disconnected. |

| 1             | 0             | Clear OC1A/OC1B on Compare Match, set<br>OC1A/OC1B at BOTTOM (non-inverting mode)                                                                                                 |

| 1             | 1             | Set OC1A/OC1B on Compare Match, clear<br>OC1A/OC1B at BOTTOM (inverting mode)                                                                                                     |

|                                       | The OCR2A Register is double buffered when using any of the Pulse Width Modulation (PWM) modes. For the Normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR2A Compare Register to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.                     |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | The OCR2A Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR2A Buffer Register, and if double buffering is disabled the CPU will access the OCR2A directly.                                                                                                                                                                                                                                                 |

| Force Output Compare                  | In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC2A) bit. Forcing compare match will not set the OCF2A Flag or reload/clear the timer, but the OC2A pin will be updated as if a real compare match had occurred (the COM2A1:0 bits settings define whether the OC2A pin is set, cleared or toggled).                                                                                          |

| Compare Match Blocking by TCNT2 Write | All CPU write operations to the TCNT2 Register will block any compare match that occurs in the next timer clock cycle, even when the timer is stopped. This feature allows OCR2A to be initialized to the same value as TCNT2 without triggering an interrupt when the Timer/Counter clock is enabled.                                                                                                                                                                               |

| Using the Output Compare<br>Unit      | Since writing TCNT2 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT2 when using the Output Compare unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT2 equals the OCR2A value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT2 value equal to BOT-TOM when the counter is downcounting. |

|                                       | The setup of the OC2A should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC2A value is to use the Force Output Compare (FOC2A) strobe bit in Normal mode. The OC2A Register keeps its value even when changing between Waveform Generation modes.                                                                                                                                                             |

|                                       | Be aware that the COM2A1:0 bits are not double buffered together with the compare value. Changing the COM2A1:0 bits will take effect immediately.                                                                                                                                                                                                                                                                                                                                    |

When the SPI is enabled, the data direction of the MOSI, MISO, SCK, and  $\overline{SS}$  pins is overridden according to Table 59. For more details on automatic port overrides, refer to "Alternate Port Functions" on page 60.

Table 59. SPI Pin Overrides<sup>(1)</sup>

| Pin  | Direction, Master SPI | Direction, Slave SPI |

|------|-----------------------|----------------------|

| MOSI | User Defined          | Input                |

| MISO | Input                 | User Defined         |

| SCK  | User Defined          | Input                |

| SS   | User Defined          | Input                |

Note: 1. See "Alternate Functions of Port B" on page 62 for a detailed description of how to define the direction of the user defined SPI pins.

The following code examples show how to initialize the SPI as a Master and how to perform a simple transmission. DDR\_SPI in the examples must be replaced by the actual Data Direction Register controlling the SPI pins. DD\_MOSI, DD\_MISO and DD\_SCK must be replaced by the actual data direction bits for these pins. E.g. if MOSI is placed on pin PB5, replace DD\_MOSI with DDB5 and DDR\_SPI with DDRB.

#### • Bit 4 – MSTR: Master/Slave Select

This bit selects Master SPI mode when written to one, and Slave SPI mode when written logic zero. If  $\overline{SS}$  is configured as an input and is driven low while MSTR is set, MSTR will be cleared, and SPIF in SPSR will become set. The user will then have to set MSTR to re-enable SPI Master mode.

#### • Bit 3 – CPOL: Clock Polarity

When this bit is written to one, SCK is high when idle. When CPOL is written to zero, SCK is low when idle. Refer to Figure 67 and Figure 68 for an example. The CPOL functionality is summarized below:

#### Table 60. CPOL Functionality

| CPOL | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Rising       | Falling       |

| 1    | Falling      | Rising        |

### • Bit 2 – CPHA: Clock Phase

The settings of the Clock Phase bit (CPHA) determine if data is sampled on the leading (first) or trailing (last) edge of SCK. Refer to Figure 67 and Figure 68 for an example. The CPOL functionality is summarized below:

#### Table 61. CPHA Functionality

| СРНА | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Sample       | Setup         |

| 1    | Setup        | Sample        |

#### • Bits 1, 0 – SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a Master. SPR1 and SPR0 have no effect on the Slave. The relationship between SCK and the Oscillator Clock frequency  $f_{osc}$  is shown in the following table:

| SPI2X | SPR1 | SPR0 | SCK Frequency         |

|-------|------|------|-----------------------|

| 0     | 0    | 0    | f <sub>osc</sub> /4   |

| 0     | 0    | 1    | f <sub>osc</sub> /16  |

| 0     | 1    | 0    | f <sub>osc</sub> /64  |

| 0     | 1    | 1    | f <sub>osc</sub> /128 |

| 1     | 0    | 0    | f <sub>osc</sub> /2   |

| 1     | 0    | 1    | f <sub>osc</sub> /8   |

| 1     | 1    | 0    | f <sub>osc</sub> /32  |

| 1     | 1    | 1    | f <sub>osc</sub> /64  |

Table 62. Relationship Between SCK and the Oscillator Frequency

| Start Condition Detector | The start condition detector is shown in Figure 81. The SDA line is delayed (in the range  |

|--------------------------|--------------------------------------------------------------------------------------------|

|                          | of 50 to 300 ns) to ensure valid sampling of the SCL line. The start condition detector is |

|                          | only enabled in Two-wire mode.                                                             |

The start condition detector is working asynchronously and can therefore wake up the processor from the Power-down sleep mode. However, the protocol used might have restrictions on the SCL hold time. Therefore, when using this feature in this case the Oscillator start-up time set by the CKSEL Fuses (see "Clock Systems and their Distribution" on page 23) must also be taken into the consideration. Refer to the USISIF bit description on page 182 for further details.

**Clock speed considerations.** Maximum frequency for SCL and SCK is  $f_{CK}$  /4. This is also the maximum data transmit and receieve rate in both two- and three-wire mode. In two-wire slave mode the Two-wire Clock Control Unit will hold the SCL low until the slave is ready to receive more data. This may reduce the actual data rate in two-wire mode.

Alternative USI Usage When the USI unit is not used for serial communication, it can be set up to do alternative tasks due to its flexible design.

Half-duplex AsynchronousBy utilizing the Shift Register in Three-wire mode, it is possible to implement a more<br/>compact and higher performance UART than by software only.

4-bit CounterThe 4-bit counter can be used as a stand-alone counter with overflow interrupt. Note<br/>that if the counter is clocked externally, both clock edges will generate an increment.

**12-bit Timer/Counter** Combining the USI 4-bit counter and Timer/Counter0 allows them to be used as a 12-bit counter.

Edge Triggered ExternalBy setting the counter to maximum value (F) it can function as an additional externalInterruptinterrupt. The Overflow Flag and Interrupt Enable bit are then used for the external interrupt. This feature is selected by the USICS1 bit.

**Software Interrupt** The counter overflow interrupt can be used as a software interrupt triggered by a clock strobe.

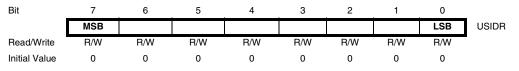

# USI Register Descriptions

USI Data Register - USIDR

The USI uses no buffering of the Serial Register, i.e., when accessing the Data Register (USIDR) the Serial Register is accessed directly. If a serial clock occurs at the same cycle the register is written, the register will contain the value written and no shift is performed. A (left) shift operation is performed depending of the USICS1..0 bits setting. The shift operation can be controlled by an external clock edge, by a Timer/Counter0 Compare Match, or directly by software using the USICLK strobe bit. Note that even when no wire mode is selected (USIWM1..0 = 0) both the external data input (DI/SDA) and the external clock input (USCK/SCL) can still be used by the Shift Register.

The output pin in use, DO or SDA depending on the wire mode, is connected via the output latch to the most significant bit (bit 7) of the Data Register. The output latch is open

| USIWM1 | USIWM0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | Outputs, clock hold, and start detector disabled. Port pins operates as normal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0      | 1      | Three-wire mode. Uses DO, DI, and USCK pins.<br>The <i>Data Output</i> (DO) pin overrides the corresponding bit in the PORT<br>Register in this mode. However, the corresponding DDR bit still<br>controls the data direction. When the port pin is set as input the pins<br>pull-up is controlled by the PORT bit.<br>The <i>Data Input</i> (DI) and <i>Serial Clock</i> (USCK) pins do not affect the<br>normal port operation. When operating as master, clock pulses are<br>software generated by toggling the PORT Register, while the data<br>direction is set to output. The USITC bit in the USICR Register can be<br>used for this purpose.                                                                                                                                                                                                                                                                                                                                                                              |

| 1      | 0      | Two-wire mode. Uses SDA (DI) and SCL (USCK) pins <sup>(1)</sup> .<br>The <i>Serial Data</i> (SDA) and the <i>Serial Clock</i> (SCL) pins are bi-<br>directional and uses open-collector output drives. The output drivers<br>are enabled by setting the corresponding bit for SDA and SCL in the<br>DDR Register.<br>When the output driver is enabled for the SDA pin, the output driver wil<br>force the line SDA low if the output of the Shift Register or the<br>corresponding bit in the PORT Register is zero. Otherwise the SDA<br>line will not be driven (i.e., it is released). When the SCL pin output<br>driver is enabled the SCL line will be forced low if the corresponding bi<br>in the PORT Register is zero, or by the start detector. Otherwise the<br>SCL line will not be driven.<br>The SCL line is held low when a start detector detects a start conditior<br>and the output is enabled. Clearing the Start Condition Flag (USISIF)<br>releases the line. The SDA and SCL pin inputs is not affected by |

| 1      | 1      | <ul> <li>enabling this mode. Pull-ups on the SDA and SCL port pin are disabled in Two-wire mode.</li> <li>Two-wire mode. Uses SDA and SCL pins.</li> <li>Same operation as for the Two-wire mode described above, except that the SCL line is also held low when a counter overflow occurs, and is held low until the Counter Overflow Flag (USIOIF) is cleared.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

**Table 76.** Relations between USIWM1..0 and the USI Operation

Note: 1. The DI and USCK pins are renamed to *Serial Data* (SDA) and *Serial Clock* (SCL) respectively to avoid confusion between the modes of operation.

#### •Bit 3..2 – USICS1..0: Clock Source Select

These bits set the clock source for the Shift Register and counter. The data output latch ensures that the output is changed at the opposite edge of the sampling of the data input (DI/SDA) when using external clock source (USCK/SCL). When software strobe or Timer/Counter0 Compare Match clock option is selected, the output latch is transparent and therefore the output is changed immediately. Clearing the USICS1..0 bits enables software strobe option. When using this option, writing a one to the USICLK bit clocks both the Shift Register and the counter. For external clock source (USICS1 = 1), the USICLK bit is no longer used as a strobe, but selects between external clocking and software clocking by the USITC strobe bit.

Table 77 shows the relationship between the USICS1..0 and USICLK setting and clock source used for the Shift Register and the 4-bit counter.

| USICS1 | USICSO | USICLK | Shift Register Clock<br>Source    | 4-bit Counter Clock<br>Source     |

|--------|--------|--------|-----------------------------------|-----------------------------------|

| 0      | 0      | 0      | No Clock                          | No Clock                          |

| 0      | 0      | 1      | Software clock strobe<br>(USICLK) | Software clock strobe<br>(USICLK) |

| 0      | 1      | х      | Timer/Counter0 Compare<br>Match   | Timer/Counter0 Compare<br>Match   |

| 1      | 0      | 0      | External, positive edge           | External, both edges              |

| 1      | 1      | 0      | External, negative edge           | External, both edges              |

| 1      | 0      | 1      | External, positive edge           | Software clock strobe<br>(USITC)  |

| 1      | 1      | 1      | External, negative edge           | Software clock strobe<br>(USITC)  |

Table 77.

Relations between the USICS1..0 and USICLK Setting

#### • Bit 1 – USICLK: Clock Strobe

Writing a one to this bit location strobes the Shift Register to shift one step and the counter to increment by one, provided that the USICS1..0 bits are set to zero and by doing so the software clock strobe option is selected. The output will change immediately when the clock strobe is executed, i.e., in the same instruction cycle. The value shifted into the Shift Register is sampled the previous instruction cycle. The bit will be read as zero.

When an external clock source is selected (USICS1 = 1), the USICLK function is changed from a clock strobe to a Clock Select Register. Setting the USICLK bit in this case will select the USITC strobe bit as clock source for the 4-bit counter (see Table 77).

#### Bit 0 – USITC: Toggle Clock Port Pin

Writing a one to this bit location toggles the USCK/SCL value either from 0 to 1, or from 1 to 0. The toggling is independent of the setting in the Data Direction Register, but if the PORT value is to be shown on the pin the DDRE4 must be set as output (to one). This feature allows easy clock generation when implementing master devices. The bit will be read as zero.

When an external clock source is selected (USICS1 = 1) and the USICLK bit is set to one, writing to the USITC strobe bit will directly clock the 4-bit counter. This allows an early detection of when the transfer is done when operating as a master device.

to Data Registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, neither register is updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL Registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the Data Registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

**Starting a Conversion** A single conversion is started by writing a logical one to the ADC Start Conversion bit, ADSC. This bit stays high as long as the conversion is in progress and will be cleared by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

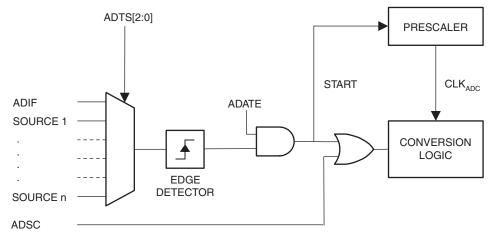

Alternatively, a conversion can be triggered automatically by various sources. Auto Triggering is enabled by setting the ADC Auto Trigger Enable bit, ADATE in ADCSRA. The trigger source is selected by setting the ADC Trigger Select bits, ADTS in ADCSRB (See description of the ADTS bits for a list of the trigger sources). When a positive edge occurs on the selected trigger signal, the ADC prescaler is reset and a conversion is started. This provides a method of starting conversions at fixed intervals. If the trigger signal still is set when the conversion completes, a new conversion will not be started. If another positive edge occurs on the trigger signal during conversion, the edge will be ignored. Note that an Interrupt Flag will be set even if the specific interrupt is disabled or the Global Interrupt Enable bit in SREG is cleared. A conversion can thus be triggered without causing an interrupt. However, the Interrupt Flag must be cleared in order to trigger a new conversion at the next interrupt event.

Using the ADC Interrupt Flag as a trigger source makes the ADC start a new conversion as soon as the ongoing conversion has finished. The ADC then operates in Free Running mode, constantly sampling and updating the ADC Data Register. The first conversion must be started by writing a logical one to the ADSC bit in ADCSRA. In this mode the ADC will perform successive conversions independently of whether the ADC Interrupt Flag, ADIF is cleared or not.

If Auto Triggering is enabled, single conversions can be started by writing ADSC in ADCSRA to one. ADSC can also be used to determine if a conversion is in progress.

Bypass RegisterThe Bypass Register consists of a single Shift Register stage. When the Bypass Register is selected as path between TDI and TDO, the register is reset to 0 when leaving the<br/>Capture-DR controller state. The Bypass Register can be used to shorten the scan<br/>chain on a system when the other devices are to be tested.

**Device Identification Register**

**Register** Figure 99 shows the structure of the Device Identification Register.

Figure 99. The Format of the Device Identification Register

|           | MSB  |     |    |             |    |        |            | LSB   |   |

|-----------|------|-----|----|-------------|----|--------|------------|-------|---|

| Bit       | 31   | 28  | 27 |             | 12 | 11     | 1          | 0     |   |

| Device ID | Vers | ion |    | Part Number |    | Manufa | acturer ID | 1     |   |

|           | 4 bi | ts  |    | 16 bits     |    | 11     | 1 bits     | 1-bit | _ |

Version

Version is a 4-bit number identifying the revision of the component. The JTAG version number follows the revision of the device. Revision A is 0x0, revision B is 0x1 and so on.

Part NumberThe part number is a 16-bit code identifying the component. The JTAG Part Number for<br/>ATmega165 is listed in Table 104 on page 249. Note that the JTAG Part Number is the<br/>same as ATmega169.

Manufacturer IDThe Manufacturer ID is a 11-bit code identifying the manufacturer. The JTAG manufac-<br/>turer ID for ATMEL is listed in Table 105 on page 249.

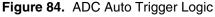

**Reset Register** The Reset Register is a test Data Register used to reset the part. Since the AVR tristates Port Pins when reset, the Reset Register can also replace the function of the unimplemented optional JTAG instruction HIGHZ.

A high value in the Reset Register corresponds to pulling the external Reset low. The part is reset as long as there is a high value present in the Reset Register. Depending on the fuse settings for the clock options, the part will remain reset for a reset time-out period (refer to "Clock Sources" on page 24) after releasing the Reset Register. The output from this Data Register is not latched, so the reset will take place immediately, as shown in Figure 100.

Figure 100. Reset Register

ClockDR · AVR\_RESET

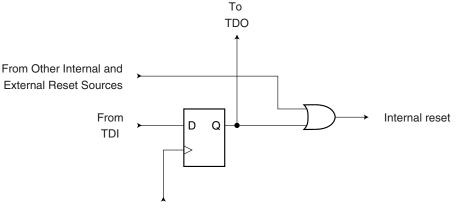

MCU Status Register –

The MCU Status Register provides information on which reset source caused an MCU

MCUSR

reset.

## • Bit 4 – JTRF: JTAG Reset Flag

This bit is set if a reset is being caused by a logic one in the JTAG Reset Register selected by the JTAG instruction AVR\_RESET. This bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

**Boundary-scan Chain** The Boundary-scan chain has the capability of driving and observing the logic levels on the digital I/O pins, as well as the boundary between digital and analog logic for analog circuitry having off-chip connection.

Scanning the Digital Port Pins Figure 101 shows the Boundary-scan Cell for a bi-directional port pin with pull-up function. The cell consists of a standard Boundary-scan cell for the Pull-up Enable – PUExn – function, and a bi-directional pin cell that combines the three signals Output Control – OCxn, Output Data – ODxn, and Input Data – IDxn, into only a two-stage Shift Register. The port and pin indexes are not used in the following description

The Boundary-scan logic is not included in the figures in the datasheet. Figure 102 shows a simple digital port pin as described in the section "External Interrupts" on page 51. The Boundary-scan details from Figure 101 replaces the dashed box in Figure 102.

When no alternate port function is present, the Input Data – ID – corresponds to the PINxn Register value (but ID has no synchronizer), Output Data corresponds to the PORT Register, Output Control corresponds to the Data Direction – DD Register, and the Pull-up Enable – PUExn – corresponds to logic expression  $\overline{PUD} \cdot \overline{DDxn} \cdot PORTxn$ .

Digital alternate port functions are connected outside the dotted box in Figure 102 to make the scan chain read the actual pin value. For Analog function, there is a direct connection from the external pin to the analog circuit, and a scan chain is inserted on the interface between the digital logic and the analog circuitry.

# ATmega165/V

```

ret

; re-enable the RWW section

ldi spmcrval, (1<<RWWSRE) | (1<<SPMEN)</pre>

call Do_spm

rjmp Return

Do_spm:

; check for previous SPM complete

Wait_spm:

in temp1, SPMCSR

sbrc temp1, SPMEN

rjmp Wait_spm

; input: spmcrval determines SPM action

; disable interrupts if enabled, store status

in

temp2, SREG

cli

; check that no EEPROM write access is present

Wait_ee:

sbic EECR, EEWE

rjmp Wait_ee

; SPM timed sequence

out SPMCSR, spmcrval

spm

; restore SREG (to enable interrupts if originally enabled)

out SREG, temp2

ret

```

#### ATmega165 Boot Loader Parameters

In Table 96 through Table 98, the parameters used in the description of the Self-Programming are given.

| Table 96. | Boot Size | Configuration <sup>(1)</sup> |

|-----------|-----------|------------------------------|

|-----------|-----------|------------------------------|

| BOOTSZ1 | BOOTSZ0 | Boot Size     | Pages | Application<br>Flash<br>Section | Boot Loader<br>Flash<br>Section | End Application<br>Section | Boot Reset<br>Address<br>(Start Boot<br>Loader Section) |

|---------|---------|---------------|-------|---------------------------------|---------------------------------|----------------------------|---------------------------------------------------------|

| 1       | 1       | 128<br>words  | 2     | 0x0000 -<br>0x1F7F              | 0x1F80 -<br>0x1FFF              | 0x1F7F                     | 0x1F80                                                  |

| 1       | 0       | 256<br>words  | 4     | 0x0000 -<br>0x1EFF              | 0x1F00 -<br>0x1FFF              | 0x1EFF                     | 0x1F00                                                  |

| 0       | 1       | 512<br>words  | 8     | 0x0000 -<br>0x1DFF              | 0x1E00 -<br>0x1FFF              | 0x1DFF                     | 0x1E00                                                  |

| 0       | 0       | 1024<br>words | 16    | 0x0000 -<br>0x1BFF              | 0x1C00-<br>0x1FFF               | 0x1BFF                     | 0x1C00                                                  |

Note: 1. The different BOOTSZ Fuse configurations are shown in Figure 109

#### Table 97. Read-While-Write Limit<sup>(1)</sup>

| Section                            | Pages | Address         |

|------------------------------------|-------|-----------------|

| Read-While-Write section (RWW)     | 112   | 0x0000 - 0x1BFF |

| No Read-While-Write section (NRWW) | 16    | 0x1C00 - 0x1FFF |

Note: 1. For details about these two section, see "NRWW – No Read-While-Write Section" on page 233 and "RWW – Read-While-Write Section" on page 233.

| Memor | r <mark>y Lock</mark> Bi | ts | Protection Type                                                                                                                                                                                                                                                                                           |

|-------|--------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 1                        | 1  | No restrictions for SPM or LPM accessing the Boot Loader section.                                                                                                                                                                                                                                         |

| 2     | 1                        | 0  | SPM is not allowed to write to the Boot Loader section.                                                                                                                                                                                                                                                   |

| 3     | 0                        | 0  | SPM is not allowed to write to the Boot Loader section,<br>and LPM executing from the Application section is not<br>allowed to read from the Boot Loader section. If Interrupt<br>Vectors are placed in the Application section, interrupts<br>are disabled while executing from the Boot Loader section. |

| 4     | 0                        | 1  | LPM executing from the Application section is not allowed<br>to read from the Boot Loader section. If Interrupt Vectors<br>are placed in the Application section, interrupts are<br>disabled while executing from the Boot Loader section.                                                                |

# Table 100. Lock Bit Protection Modes<sup>(1)(2)</sup> (Continued)

Notes: 1. Program the Fuse bits and Boot Lock bits before programming the LB1 and LB2. 2. "1" means unprogrammed, "0" means programmed

**Fuse Bits**

The ATmega165 has three Fuse bytes. Table 101 - Table 103 describe briefly the functionality of all the fuses and how they are mapped into the Fuse bytes. Note that the fuses are read as logical zero, "0", if they are programmed.

| Table 101.         Extended Fuse Byte |

|---------------------------------------|

|---------------------------------------|

| Fuse Low Byte            | Bit No | Description                      | Default Value    |

|--------------------------|--------|----------------------------------|------------------|

| -                        | 7      | _                                | 1                |

| -                        | 6      | _                                | 1                |

| -                        | 5      | _                                | 1                |

| -                        | 4      | _                                | 1                |

| BODLEVEL2 <sup>(1)</sup> | 3      | Brown-out Detector trigger level | 1 (unprogrammed) |

| BODLEVEL1 <sup>(1)</sup> | 2      | Brown-out Detector trigger level | 1 (unprogrammed) |

| BODLEVEL0 <sup>(1)</sup> | 1      | Brown-out Detector trigger level | 1 (unprogrammed) |

| RESERVED <sup>(2)</sup>  | 0      |                                  | 1 (unprogrammed) |

Notes: 1. See Table 17 on page 40 for BODLEVEL Fuse decoding.

2. This bit should never be programmed.

| The AVR specific public JTAG instruction for setting the AVR device in the Reset mode<br>or taking the device out from the Reset mode. The TAP controller is not reset by this<br>instruction. The one bit Reset Register is selected as Data Register. Note that the reset<br>will be active as long as there is a logic "one" in the Reset Chain. The output from this<br>chain is not latched. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>The active states are:</li><li>Shift-DR: The Reset Register is shifted by the TCK input.</li></ul>                                                                                                                                                                                                                                                                                        |

| <ul> <li>The AVR specific public JTAG instruction for enabling programming via the JTAG port.</li> <li>The 16-bit Programming Enable Register is selected as Data Register. The active states are the following:</li> <li>Shift-DR: The programming enable signature is shifted into the Data Register.</li> </ul>                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                   |

• Update-DR: The programming enable signature is compared to the correct value, and Programming mode is entered if the signature is valid.

| PROG_COMMANDS (0x5) | <ul> <li>The AVR specific public JTAG instruction for entering programming commands via the JTAG port. The 15-bit Programming Command Register is selected as Data Register. The active states are the following:</li> <li>Capture-DR: The result of the previous command is loaded into the Data Register.</li> <li>Shift-DR: The Data Register is shifted by the TCK input, shifting out the result of the previous command and shifting in the new command.</li> <li>Update-DR: The programming command is applied to the Flash inputs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | <ul> <li>Run-Test/Idle: One clock cycle is generated, executing the applied command (not<br/>always required, see Table 115 below).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PROG_PAGELOAD (0x6) | <ul> <li>The AVR specific public JTAG instruction to directly load the Flash data page via the JTAG port. An 8-bit Flash Data Byte Register is selected as the Data Register. This is physically the 8 LSBs of the Programming Command Register. The active states are the following:</li> <li>Shift-DR: The Flash Data Byte Register is shifted by the TCK input.</li> <li>Update-DR: The content of the Flash Data Byte Register is copied into a temporary register. A write sequence is initiated that within 11 TCK cycles loads the content of the temporary register into the Flash page buffer. The AVR automatically alternates between writing the low and the high byte for each new Update-DR state, starting with the low byte for the first Update-DR encountered after entering the PROG_PAGELOAD command. The Program Counter is pre-incremented before writing the low byte, except for the first written byte. This ensures that the first data is written to the address set up by PROG_COMMANDS, and loading the last location in the page buffer does not make the program counter increment into the next page.</li> </ul> |

| PROG_PAGEREAD (0x7) | <ul> <li>The AVR specific public JTAG instruction to directly capture the Flash content via the JTAG port. An 8-bit Flash Data Byte Register is selected as the Data Register. This is physically the 8 LSBs of the Programming Command Register. The active states are the following:</li> <li>Capture-DR: The content of the selected Flash byte is captured into the Flash Data Byte Register. The AVR automatically alternates between reading the low and the high byte for each new Capture-DR state, starting with the low byte for the first Capture-DR encountered after entering the PROG_PAGEREAD command. The Program Counter is post-incremented after reading each high byte, including the first read byte. This ensures that the first data is captured from the first address set up by PROG_COMMANDS, and reading the last location in the page makes the program counter increment into the next page.</li> <li>Shift-DR: The Flash Data Byte Register is shifted by the TCK input.</li> </ul>                                                                                                                                |

| Data Registers      | <ul> <li>The Data Registers are selected by the JTAG instruction registers described in section "Programming Specific JTAG Instructions" on page 266. The Data Registers relevant for programming operations are:</li> <li>Reset Register</li> <li>Programming Enable Register</li> <li>Programming Command Register</li> <li>Flash Data Byte Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

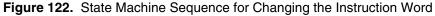

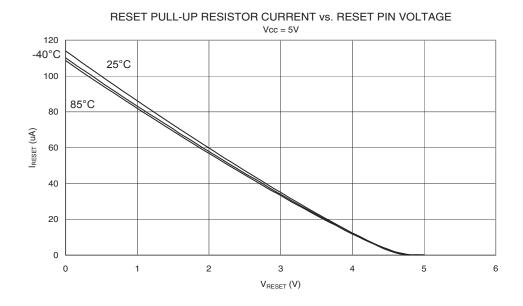

Figure 155. I/O Pin Pull-up Resistor Current vs. Input Voltage (V<sub>CC</sub> = 1.8V)

ATmega165/V

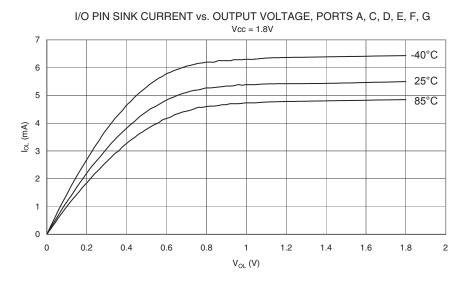

Figure 167. I/O Pin Sink Current vs. Output Voltage, Ports A, C, D, E, F, G (V<sub>CC</sub> = 1.8V)

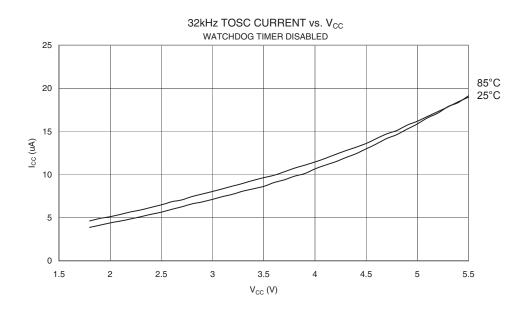

Figure 190. 32 kHZ TOSC Current vs. V<sub>CC</sub> (Watchdog Timer Disabled)

The differential current consumption between Power-save with WD disabled and 32 kHz TOSC represents the current drawn by Timer/Counter2.

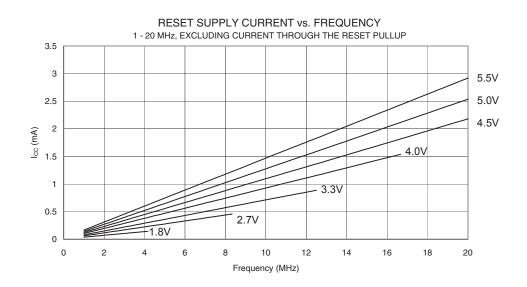

Figure 195. Reset Supply Current vs.  $V_{CC}$  (1 - 20 MHz, Excluding Current Through The Reset Pull-up)

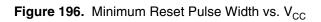

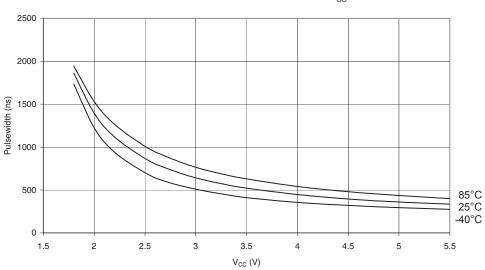

MINIMUM RESET PULSE WIDTH vs.  $\mathrm{V}_{\mathrm{CC}}$