Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 29                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1621pm020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers **Product Specification**

| IIART                                                                                                                                                                                                                                                                                                                                        | 103                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| UART         Overview         Architecture         Operation         Data Format         Transmitting Data using the Polled Method         Transmitting Data using the Interrupt-Driven Method         Receiving Data using the Polled Method         Receiving Data using the Interrupt-Driven Method         Clear To Send (CTS) Operation | 103<br>104<br>104<br>105<br>106<br>107<br>108<br>109 |

| MULTIPROCESSOR (9-bit) Mode                                                                                                                                                                                                                                                                                                                  |                                                      |

| External Driver Enable                                                                                                                                                                                                                                                                                                                       |                                                      |

| UART Baud Rate Generator                                                                                                                                                                                                                                                                                                                     |                                                      |

| UART Control Register Definitions                                                                                                                                                                                                                                                                                                            |                                                      |

| UART Transmit Data Register                                                                                                                                                                                                                                                                                                                  |                                                      |

| UART Receive Data Register                                                                                                                                                                                                                                                                                                                   |                                                      |

| UART Status 0 Register                                                                                                                                                                                                                                                                                                                       | 115                                                  |

| UART Status 1 Register                                                                                                                                                                                                                                                                                                                       | 116                                                  |

| UART Control 0 and Control 1 Registers                                                                                                                                                                                                                                                                                                       |                                                      |

| UART Address Compare Register                                                                                                                                                                                                                                                                                                                |                                                      |

| UART Baud Rate High and Low Byte Registers                                                                                                                                                                                                                                                                                                   | 120                                                  |

| Infrared Encoder/Decoder                                                                                                                                                                                                                                                                                                                     | 125                                                  |

| Overview                                                                                                                                                                                                                                                                                                                                     | 125                                                  |

| Architecture                                                                                                                                                                                                                                                                                                                                 | 125                                                  |

| Operation                                                                                                                                                                                                                                                                                                                                    | 126                                                  |

| Transmitting IrDA Data                                                                                                                                                                                                                                                                                                                       |                                                      |

| Receiving IrDA Data                                                                                                                                                                                                                                                                                                                          |                                                      |

| Infrared Encoder/Decoder Control Register Definitions                                                                                                                                                                                                                                                                                        | 128                                                  |

| Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                  | 129                                                  |

| Overview                                                                                                                                                                                                                                                                                                                                     | 129                                                  |

| Architecture                                                                                                                                                                                                                                                                                                                                 | 129                                                  |

| Operation                                                                                                                                                                                                                                                                                                                                    |                                                      |

| SPI Signals                                                                                                                                                                                                                                                                                                                                  |                                                      |

| SPI Clock Phase and Polarity Control                                                                                                                                                                                                                                                                                                         |                                                      |

| Multi-Master Operation                                                                                                                                                                                                                                                                                                                       |                                                      |

| Slave Operation                                                                                                                                                                                                                                                                                                                              | 134                                                  |

#### **Operating Mode Reset Source Reset Type** NORMAL or HALT Power-On Reset/Voltage system reset modes Brownout Watchdog Timer time-out system reset when configured for Reset RESET pin assertion system reset On-Chip Debugger initiated Reset system reset except the On-Chip Debugger is (OCDCTL[0] set to 1) unaffected by the reset Power-On Reset/Voltage STOP mode system reset Brownout **RESET** pin assertion system reset DBG pin driven Low system reset

### Table 9. Reset Sources and Resulting Reset Type

### **Power-On Reset**

Each device in the 64K Series contains an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 66 cycles of the Watchdog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The devices are held in the Reset state until both the POR Counter and XTAL counter have timed out. After the 64K Series devices exit the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watchdog Timer Control (WDTCTL) register is set to 1.

Figure 8 displays Power-On Reset operation. For the POR threshold voltage ( $V_{POR}$ ), see Electrical Characteristics on page 215.

C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

### Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 36) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port input pin. The Interrupt Port Select register selects between Port A and Port D for the individual interrupts.

### Table 36. Interrupt Edge Select Register (IRQES)

| BITS  | 7    | 6                                       | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|------|-----------------------------------------|---|----|----|---|---|---|--|--|

| FIELD | IES7 | IES7 IES6 IES5 IES4 IES3 IES2 IES1 IES0 |   |    |    |   |   |   |  |  |

| RESET |      | 0                                       |   |    |    |   |   |   |  |  |

| R/W   |      | R/W                                     |   |    |    |   |   |   |  |  |

| ADDR  |      |                                         |   | FC | DH |   |   |   |  |  |

IES*x*—Interrupt Edge Select *x*

The minimum pulse width should be greater than 1 system clock to guarantee capture of the edge triggered interrupt. Shorter pulses may be captured but not guaranteed. 0 = An interrupt request is generated on the falling edge of the PAx/PDx input.

1 = An interrupt request is generated on the rising edge of the PAx/PDx input.

where *x* indicates the specific GPIO Port pin number (0 through 7).

### Interrupt Port Select Register

The Port Select (IRQPS) register (Table 37) determines the port pin that generates the PAx/PDx interrupts. This register allows either Port A or Port D pins to be used as interrupts. The Interrupt Edge Select register controls the active interrupt edge.

| BITS  | 7     | 6     | 5     | 4     | 3     | 2     | 1     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| FIELD | PAD7S | PAD6S | PAD5S | PAD4S | PAD3S | PAD2S | PAD1S |

| RESET |       |       |       | (     | )     |       |       |

### Table 37. Interrupt Port Select Register (IRQPS)

0

PAD0S

configuration bits. In general, the address compare feature reduces the load on the CPU, since it does not need to access the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes.

- Interrupt on matched address bytes and correctly framed data bytes.

- Interrupt only on correctly framed data bytes.

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all MULTIPROCESSOR modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. At this point, each new incoming byte interrupts the CPU. The software is then responsible for determining the end of the frame. It checks for end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, then set MPMD[0] to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme is enabled by setting MPMD[1:0] to 10b and writing the UART's address into the UART Address Compare Register. This mode introduces more hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. The first data byte in the frame contains the NEWFRM=1 in the UART Status 1 Register. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continue sand the NEWFRM bit is set for the first byte of the new frame. If there is no match, then the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame is still accompanied by a NEWFRM assertion.

### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 17. The Driver Enable signal asserts

# zilog

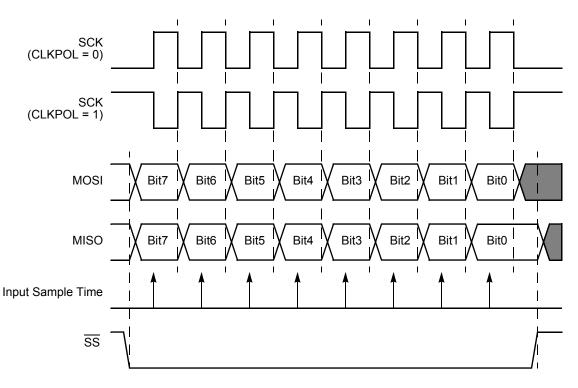

### **Transfer Format PHASE Equals Zero**

Figure 25 displays the timing diagram for an SPI transfer in which PHASE is cleared to 0. The two SCK waveforms show polarity with CLKPOL reset to 0 and with CLKPOL set to one. The diagram may be interpreted as either a Master or Slave timing diagram because the SCK Master-In/Slave-Out (MISO) and Master-Out/Slave-In (MOSI) pins are directly connected between the Master and the Slave.

### Figure 25. SPI Timing When PHASE is 0

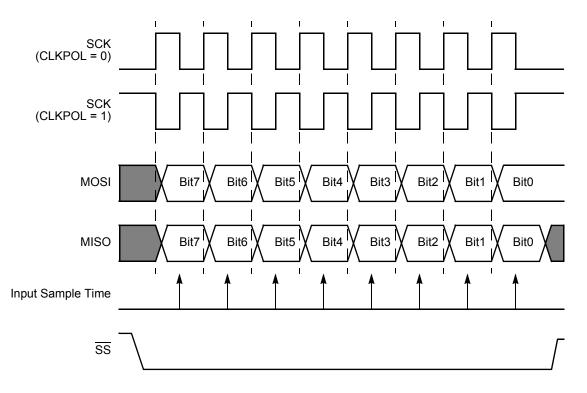

### Transfer Format PHASE Equals One

Figure 26 on page 134 displays the timing diagram for an SPI transfer in which PHASE is one. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

Figure 26. SPI Timing When PHASE is 1

### **Multi-Master Operation**

In a multi-master SPI system, all SCK pins are tied together, all MOSI pins are tied together and all MISO pins are tied together. All SPI pins must then be configured in OPEN-DRAIN mode to prevent bus contention. At any one time, only one SPI device is configured as the Master and all other SPI devices on the bus are configured as Slaves. The Master enables a single Slave by asserting the  $\overline{SS}$  pin on that Slave only. Then, the single Master drives data out its SCK and MOSI pins to the SCK and MOSI pins on the Slaves (including those which are not enabled). The enabled Slave drives data out its MISO pin to the MISO Master pin.

For a Master device operating in a multi-master system, if the  $\overline{SS}$  pin is configured as an input and is driven Low by another Master, the COL bit is set to 1 in the SPI Status Register. The COL bit indicates the occurrence of a multi-master collision (mode fault error condition).

### Slave Operation

The SPI block is configured for SLAVE mode operation by setting the SPIEN bit to 1 and the MMEN bit to 0 in the SPICTL register and setting the SSIO bit to 0 in the SPIMODE

Table 64. SPI Control Register (SPICTL)

| BITS  | 7    | 6                                   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|------|-------------------------------------|---|----|----|---|---|---|--|--|

| FIELD | IRQE | IRQE STR BIRQ PHASE CLKPOL WOR MMEN |   |    |    |   |   |   |  |  |

| RESET |      | 0                                   |   |    |    |   |   |   |  |  |

| R/W   |      | R/W                                 |   |    |    |   |   |   |  |  |

| ADDR  |      |                                     |   | F6 | 1H |   |   |   |  |  |

IRQE—Interrupt Request Enable

0 = SPI interrupts are disabled. No interrupt requests are sent to the Interrupt Controller.

1 = SPI interrupts are enabled. Interrupt requests are sent to the Interrupt Controller.

STR—Start an SPI Interrupt Request

0 = No effect.

1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART. Writing a 1 to the IRQ bit in the SPI Status register clears this bit to 0.

BIRQ-BRG Timer Interrupt Request

If the SPI is enabled, this bit has no effect. If the SPI is disabled:

0 = The Baud Rate Generator timer function is disabled.

1 = The Baud Rate Generator timer function and time-out interrupt are enabled.

PHASE—Phase Select

Sets the phase relationship of the data to the clock. For more information on operation of the PHASE bit, see SPI Clock Phase and Polarity Control on page 132.

CLKPOL—Clock Polarity

0 = SCK idles Low (0).

1 = SCK idle High (1).

WOR-Wire-OR (OPEN-DRAIN) Mode Enabled

0 = SPI signal pins not configured for open-drain.

$1 = \text{All four SPI signal pins (SCK, \overline{SS}, MISO, MOSI)}$  configured for open-drain function. This setting is typically used for multi-master and/or multi-slave configurations.

MMEN-SPI Master Mode Enable

0 = SPI configured in Slave mode.

1 = SPI configured in Master mode.

SPIEN—SPI Enable

0 = SPI disabled.

1 = SPI enabled.

### 42

### SPI Baud Rate High and Low Byte Registers

The SPI Baud Rate High and Low Byte registers (Table 68 and Table 69) combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator.

When configured as a general purpose timer, the SPI BRG interrupt interval is calculated using the following equation:

SPI BRG Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

### Table 68. SPI Baud Rate High Byte Register (SPIBRH)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|

| FIELD |   | BRH |   |    |    |   |   |   |  |  |

| RESET |   | 1   |   |    |    |   |   |   |  |  |

| R/W   |   | R/W |   |    |    |   |   |   |  |  |

| ADDR  |   |     |   | F6 | 6H |   |   |   |  |  |

BRH = SPI Baud Rate High Byte

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

### Table 69. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|

| FIELD |   | BRL |   |    |    |   |   |   |  |  |

| RESET |   | 1   |   |    |    |   |   |   |  |  |

| R/W   |   | R/W |   |    |    |   |   |   |  |  |

| ADDR  |   |     |   | F6 | 7H |   |   |   |  |  |

BRL = SPI Baud Rate Low Byte

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

**Caution:** Software must be cautious in making decisions based on this bit within a transaction because software cannot tell when the bit is updated by hardware. In the case of write transactions, the  $I^2C$  pauses at the beginning of the Acknowledge cycle if the next transmit data or address byte has not been written (TDRE = 1) and STOP and START = 0. In this case the ACK bit is not updated until the transmit interrupt is serviced and the Acknowledge cycle for the previous byte completes. For examples of how the ACK bit can be used, see Address Only Transaction with a 7-bit Address on page 148 and Address Only Transaction with a 10-bit Address on page 150.

### 10B—10-Bit Address

This bit indicates whether a 10- or 7-bit address is being transmitted. After the START bit is set, if the five most-significant bits of the address are 11110B, this bit is set. When set, it is reset once the first byte of the address has been sent.

### RD—Read

This bit indicates the direction of transfer of the data. It is active high during a read. The status of this bit is determined by the least-significant bit of the  $I^2C$  Shift register after the START bit is set.

TAS—Transmit Address State

This bit is active high while the address is being shifted out of the I<sup>2</sup>C Shift register.

### DSS—Data Shift State

This bit is active high while data is being shifted to or from the I<sup>2</sup>C Shift register.

### NCKI—NACK Interrupt

This bit is set high when a Not Acknowledge condition is received or sent and neither the START nor the STOP bit is active. When set, this bit generates an interrupt that can only be cleared by setting the START or STOP bit, allowing you to specify whether to perform a STOP or a repeated START.

### I<sup>2</sup>C Control Register

The I<sup>2</sup>C Control register (Table 72) enables the I<sup>2</sup>C operation.

| BITS  | 7   | 6                             | 5    | 4    | 3   | 2   | 1     | 0      |  |  |

|-------|-----|-------------------------------|------|------|-----|-----|-------|--------|--|--|

| FIELD | IEN | START                         | STOP | BIRQ | ТХІ | NAK | FLUSH | FILTEN |  |  |

| RESET |     | 0                             |      |      |     |     |       |        |  |  |

| R/W   | R/W | R/W R/W1 R/W1 R/W R/W1 W1 R/W |      |      |     |     |       |        |  |  |

| ADDR  |     |                               |      | F5   | 2H  |     |       |        |  |  |

### Table 72. I<sup>2</sup>C Control Register (I2CCTL)

### **Direct Memory Access Controller**

### **Overview**

The 64K Series Direct Memory Access (DMA) Controller provides three independent Direct Memory Access channels. Two of the channels (DMA0 and DMA1) transfer data between the on-chip peripherals and the Register File. The third channel (DMA\_ADC) controls the ADC operation and transfers SINGLE-SHOT mode ADC output data to the Register File.

### Operation

### **DMA0 and DMA1 Operation**

DMA0 and DMA1, referred to collectively as DMAx, transfer data either from the on-chip peripheral control registers to the Register File, or from the Register File to the on-chip peripheral control registers. The sequence of operations in a DMAx data transfer is:

- 1. DMAx trigger source requests a DMA data transfer.

- 2. DMAx requests control of the system bus (address and data) from the eZ8 CPU.

- 3. After the eZ8 CPU acknowledges the bus request, DMAx transfers either a single byte or a two-byte word (depending upon configuration) and then returns system bus control back to the eZ8 CPU.

- 4. If Current Address equals End Address:

- DMAx reloads the original Start Address

- If configured to generate an interrupt, DMAx sends an interrupt request to the Interrupt Controller

- If configured for single-pass operation, DMAx resets the DEN bit in the DMAx Control register to 0 and the DMA is disabled.

If Current Address does not equal End Address, the Current Address increments by 1 (single-byte transfer) or 2 (two-byte word transfer).

0101 = ADC Analog Inputs 0-5 updated. 0110 = ADC Analog Inputs 0-6 updated. 0111 = ADC Analog Inputs 0-7 updated. 1000 = ADC Analog Inputs 0-8 updated. 1001 = ADC Analog Inputs 0-9 updated. 1010 = ADC Analog Inputs 0-10 updated. 1011 = ADC Analog Inputs 0-11 updated. 1100-1111 = Reserved.

### DMA Status Register

The DMA Status register (Table 85 on page 173) indicates the DMA channel that generated the interrupt and the ADC Analog Input that is currently undergoing conversion. Reads from this register reset the Interrupt Request Indicator bits (IRQA, IRQ1, and IRQ0) to 0. Therefore, software interrupt service routines that read this register must process all three interrupt sources from the DMA.

| BITS  | 7 | 6   | 5      | 4  | 3        | 2    | 1    | 0    |  |

|-------|---|-----|--------|----|----------|------|------|------|--|

| FIELD |   | CAD | C[3:0] |    | Reserved | IRQA | IRQ1 | IRQ0 |  |

| RESET |   | 0   |        |    |          |      |      |      |  |

| R/W   |   | R   |        |    |          |      |      |      |  |

| ADDR  |   |     |        | FB | FH       |      |      |      |  |

### Table 85. DMA\_ADC Status Register (DMAA\_STAT)

CADC[3:0]—Current ADC Analog Input

This field identifies the Analog Input that the ADC is currently converting.

Reserved

This bit is reserved and must be 0.

IRQA—DMA\_ADC Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

$0 = DMA\_ADC$  is not the source of the interrupt from the DMA Controller.

1 = DMA\_ADC completed transfer of data from the last ADC Analog Input and generated an interrupt.

IRQ1—DMA1 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

0 = DMA1 is not the source of the interrupt from the DMA Controller.

1 = DMA1 completed transfer of data to/from the End Address and generated an interrupt.

IRQ0—DMA0 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

## **Analog-to-Digital Converter**

### **Overview**

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- 12 analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Internal voltage reference generator

- Direct Memory Access (DMA) controller can automatically initiate data conversion and transfer of the data from 1 to 12 of the analog inputs

### Architecture

Figure 34 displays the three major functional blocks (converter, analog multiplexer, and voltage reference generator) of the ADC. The ADC converts an analog input signal to its digital representation. The 12-input analog multiplexer selects one of the 12 analog input sources. The ADC requires an input reference voltage for the conversion. The voltage reference for the conversion may be input through the external VREF pin or generated internally by the voltage reference generator.

0100 = ANA4 0101 = ANA5 0110 = ANA6 0111 = ANA7 1000 = ANA8 1001 = ANA9 1010 = ANA10 1011 = ANA1111XX = Reserved.

### ADC Data High Byte Register

The ADC Data High Byte register (Table 87) contains the upper eight bits of the 10-bit ADC output. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

| Table 87. | ADC Data | High I | Byte | Register | (ADCD | _H) |

|-----------|----------|--------|------|----------|-------|-----|

|-----------|----------|--------|------|----------|-------|-----|

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|

| FIELD |   | ADCD_H |   |    |    |   |   |   |  |  |

| RESET |   | X      |   |    |    |   |   |   |  |  |

| R/W   |   | R      |   |    |    |   |   |   |  |  |

| ADDR  |   |        |   | F7 | 2H |   |   |   |  |  |

### ADCD\_H—ADC Data High Byte

This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the last conversion output is held in this register. These bits are undefined after a Reset.

### ADC Data Low Bits Register

The ADC Data Low Bits register (Table 88) contains the lower two bits of the conversion value. The data in the ADC Data Low Bits register is latched each time the ADC Data High Byte register is read. Reading this register always returns the lower two bits of the conversion last read into the ADC High Byte register. Access to the ADC Data Low Bits register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

### Operation

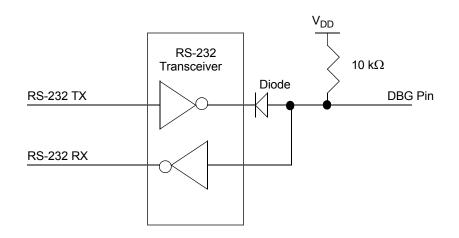

### **OCD** Interface

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bi-directional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the 64K Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are depicted in Figure 37 and Figure 38 on page 201.

**Caution:** For operation of the On-Chip Debugger, all power pins  $(V_{DD} \text{ and } AV_{DD})$  must be supplied with power, and all ground pins  $(V_{SS} \text{ and } AV_{SS})$  must be properly grounded.

The DBG pin is open-drain and must always be connected to  $V_{DD}$  through an external pull-up resistor to ensure proper operation.

Figure 37. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

210

eZ8 CPU loops on the BRK instruction. 0 = BRK instruction sets DBGMODE to 1. 1 = eZ8 CPU loops on BRK instruction.

Reserved

These bits are reserved and must be 0.

RST—Reset

Setting this bit to 1 resets the 64K Series devices. The devices go through a normal Power-On Reset sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 when the reset finishes.

0 = No effect

1 =Reset the 64K Series device

### **OCD Status Register**

The OCD Status register (Table 103) reports status information about the current state of the debugger and the system.

| BITS  | 7    | 6    | 5    | 4        | 3 | 2 | 1 | 0 |

|-------|------|------|------|----------|---|---|---|---|

| FIELD | IDLE | HALT | RPEN | Reserved |   |   |   |   |

| RESET | 0    |      |      |          |   |   |   |   |

| R/W   | R    |      |      |          |   |   |   |   |

### IDLE—CPU idling

This bit is set if the part is in DEBUG mode (DBGMODE is 1), or if a BRK instruction occurred since the last time OCDCTL was written. This can be used to determine if the CPU is running or if it is idling.

0 = The eZ8 CPU is running.

1 = The eZ8 CPU is either stopped or looping on a BRK instruction.

HALT—HALT Mode

0 = The device is not in HALT mode.

1 = The device is in HALT mode.

RPEN—Read Protect Option Bit Enabled

0 = The Read Protect Option Bit is disabled (1).

1 = The Read Protect Option Bit is enabled (0), disabling many OCD commands.

### Reserved

These bits are always 0.

zilog 222

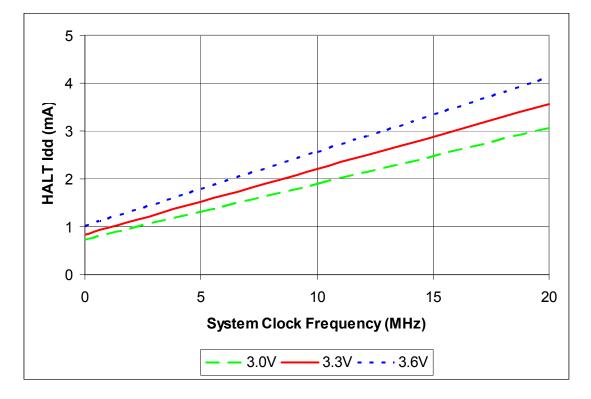

Figure 45 displays the typical current consumption in HALT mode while operating at 25 °C versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 45. Typical HALT Mode Idd Versus System Clock Frequency

|                  |                                                                                               | T <sub>A</sub> = –40 °C to 125 °C |                      |         |       |                                                                  |

|------------------|-----------------------------------------------------------------------------------------------|-----------------------------------|----------------------|---------|-------|------------------------------------------------------------------|

| Symbol           | Parameter                                                                                     | Minimum                           | Typical <sup>1</sup> | Maximum | Units | Conditions                                                       |

| V <sub>DD</sub>  | Operating Voltage<br>Range                                                                    | 2.70 <sup>1</sup>                 | _                    | -       | V     |                                                                  |

| R <sub>EXT</sub> | External Resistance from XIN to VDD                                                           | 40                                | 45                   | 200     | kΩ    | V <sub>DD</sub> = V <sub>VBO</sub>                               |

| C <sub>EXT</sub> | External Capacitance<br>from XIN to VSS                                                       | 0                                 | 20                   | 1000    | pF    |                                                                  |

| F <sub>OSC</sub> | External RC Oscillation<br>Frequency                                                          | _                                 | _                    | 4       | MHz   |                                                                  |

| 2.7 V, but       | sing the external RC oscillato<br>before the power supply dro<br>he supply voltage exceeds 2. | ps to the volt                    |                      |         |       | e power supply drops below<br>illator will resume oscillation as |

### Table 108. External RC Oscillator Electrical Characteristics and Timing

### Table 109. Reset and Stop Mode Recovery Pin Timing

|                    |                                                     | T <sub>A</sub> = –40 °C to 125 °C |         |         |                  |                                                                 |  |

|--------------------|-----------------------------------------------------|-----------------------------------|---------|---------|------------------|-----------------------------------------------------------------|--|

| Symbol             | Parameter                                           | Minimum                           | Typical | Maximum | Units            | Conditions                                                      |  |

| T <sub>RESET</sub> | RESET pin assertion to initiate a system reset.     | 4                                 | _       | -       | T <sub>CLK</sub> | Not in STOP Mode.<br>T <sub>CLK</sub> = System Clock<br>period. |  |

| T <sub>SMR</sub>   | Stop Mode Recovery<br>pin Pulse Rejection<br>Period | 10                                | 20      | 40      | ns               | RESET, DBG, and GPIO<br>pins configured as SMR<br>sources.      |  |

zilog

Table 125 through Table 132 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| CP       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| CPX      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

### Table 125. Arithmetic Instructions

### Table 126. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction      |

|----------|-------------|------------------|

| BCLR     | bit, dst    | Bit Clear        |

| BIT      | p, bit, dst | Bit Set or Clear |

| BSET     | bit, dst    | Bit Set          |

246

### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

# Packaging

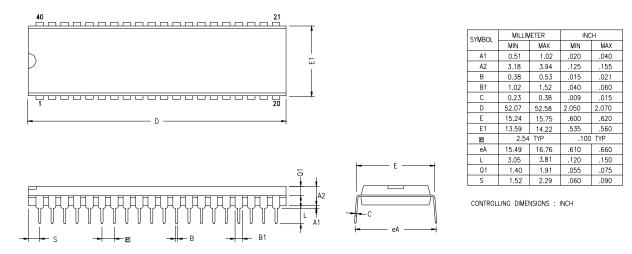

Figure 62 displays the 40-pin Plastic Dual-inline Package (PDIP) available for the Z8X1601, Z8X2401, Z8X3201, Z8X4801, and Z8X6401 devices.

Figure 62. 40-Lead Plastic Dual-Inline Package (PDIP)

### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

285

error detection 135 interrupts 135 mode fault error 135 mode register 140 multi-master operation 134 operation 130 overrun error 135 signals 131 single master, multiple slave system 130 single master, single slave system 129 status register 139 timing, PHASE = 0.133timing, PHASE=1 134 SPI controller signals 14 SPI mode (SPIMODE) 140 SPIBRH register 142 SPIBRL register 142 SPICTL register 138 SPIDATA register 137 SPIMODE register 140 SPISTAT register 139 SRA 249 src 244 SRL 250 SRP 247 stack pointer 244 status register, I2C 157 **STOP 248** STOP mode 55, 248 STOP mode recovery sources 52 using a GPIO port pin transition 53 using watchdog timer time-out 52 **SUB 246** subtract 246 subtract - extended addressing 246 subtract with carry 246 subtract with carry - extended addressing 246 **SUBX 246 SWAP 250** swap nibbles 250 symbols, additional 244 system and core resets 48

### Т

TCM 247 **TCMX 247 Technical Support 287** test complement under mask 247 test complement under mask - extended addressing 247 test under mask 247 test under mask - extended addressing 247 timer signals 15 timers 5, 81 architecture 81 block diagram 82 capture mode 86, 95 capture/compare mode 89, 95 compare mode 87, 95 continuous mode 83, 94 counter mode 84 counter modes 94 gated mode 88, 95 one-shot mode 82, 94 operating mode 82 PWM mode 85, 94 reading the timer count values 90 reload high and low byte registers 91 timer control register definitions 90 timer output signal operation 90 timers 0-3 control 0 registers 93 control 1 registers 94 high and low byte registers 90, 92 TM 247 TMX 247 transmit IrDA data 126 transmit interrupt 145 transmitting UART data-interrupt-driven method 106 transmitting UART data-polled method 105 **TRAP 249**

### U

UART 4