Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1622ar020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

| Option Bits195Overview195Operation195Option Bit Configuration By Reset195Option Bit Address Space195Flash Memory Address 0000H196Flash Memory Address 0001H197On-Chip Debugger199Overview199Architecture199Operation200OCD Interface200OCD Interface200DEBUG Mode201OCD Data Format202OCD Auto-Baud Detector/Generator202OCD Serial Errors203Breakpoints203On-Chip Debugger Commands204On-Chip Debugger Control Register Definitions209OCD Status Register210On-Chip Oscillator211Operating Modes211Cystal Oscillator Operation211Oscillator Operation211Oscillator Operation211Oscillator Operation211Oscillator Operation211Or-Chip Scillator215Absolute Maximum Ratings215DC Characteristics226AC Characteristics226AC Characteristics226AC Characteristics226AC Characteristics231Con-Chip Peripheral AC and DC Electrical Characteristics236Actionarce I/O Port Input Data Sample Timing332 | Flash Status Register                                                                                                                                                                                                                                                                                                                 | 191<br>192                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Operation195Option Bit Configuration By Reset195Option Bit Address Space195Flash Memory Address 0000H196Flash Memory Address 0001H197On-Chip Debugger199Overview199Architecture199Operation200OCD Interface200DEBUG Mode201OCD Data Format202OCD Auto-Baud Detector/Generator203Or-Chip Debugger Commands203On-Chip Debugger Control Register Definitions209OCD Control Register209OCD Status Register211On-Chip Oscillator211Orsystal Scallator Operation211Orsystal Scallator Operation211Orsystal Scallator Operation211Orsystal Scallator Operation211Orschilator Operation211Orschlator Operation211Orschlator Operation211Orschlator Operation211Orschlator Operation211Orschlator Operation211Orschlator Operation211Orschlator Operation215DC Characteristics215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                     | Option Bits                                                                                                                                                                                                                                                                                                                           | 195                                                                              |

| Overview199Architecture199Operation200OCD Interface200DEBUG Mode201OCD Data Format202OCD Auto-Baud Detector/Generator202OCD Serial Errors203Breakpoints203On-Chip Debugger Commands204On-Chip Debugger Control Register Definitions209OCD Status Register210On-Chip Oscillator211Overview211Operating Modes211Crystal Oscillator Operation211Oscillator Operation with an External RC Network213Electrical Characteristics215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                | Operation                                                                                                                                                                                                                                                                                                                             | 195<br>195<br>195<br>196                                                         |

| Architecture199Operation200OCD Interface200DEBUG Mode201OCD Data Format202OCD Auto-Baud Detector/Generator202OCD Serial Errors203Breakpoints203On-Chip Debugger Commands204On-Chip Debugger Control Register Definitions209OCD Status Register210On-Chip Oscillator211Overview211Overview211Cystal Oscillator Operation211Oscillator Operation with an External RC Network213Electrical Characteristics215Absolute Maximum Ratings215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                        | On-Chip Debugger                                                                                                                                                                                                                                                                                                                      | 199                                                                              |

| Overview211Operating Modes211Crystal Oscillator Operation211Oscillator Operation with an External RC Network213Electrical Characteristics215Absolute Maximum Ratings215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Architecture       7         Operation       7         OCD Interface       7         DEBUG Mode       7         OCD Data Format       7         OCD Auto-Baud Detector/Generator       7         OCD Serial Errors       7         Breakpoints       7         On-Chip Debugger Commands       7         OCD Control Register       7 | 199<br>200<br>201<br>202<br>202<br>203<br>203<br>203<br>203<br>204<br>209<br>209 |

| Operating Modes211Crystal Oscillator Operation211Oscillator Operation with an External RC Network213Electrical Characteristics215Absolute Maximum Ratings215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | On-Chip Oscillator                                                                                                                                                                                                                                                                                                                    | 211                                                                              |

| Absolute Maximum Ratings215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Operating Modes    2      Crystal Oscillator Operation    2                                                                                                                                                                                                                                                                           | 211<br>211                                                                       |

| DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DC Characteristics    2      On-Chip Peripheral AC and DC Electrical Characteristics    2                                                                                                                                                                                                                                             | 217<br>226<br>231                                                                |

## Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

## Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

Data Register

PS019919-1207

| _        |    | $\frown$ | $\frown$ |  |

|----------|----|----------|----------|--|

|          |    | ()       |          |  |

| <b>~</b> | Ψ. | $\smile$ | 9        |  |

|          |    |          |          |  |

| Device  | Packages       | Port A | Port B | Port C | Port D               | Port E | Port F | Port G | Port H |

|---------|----------------|--------|--------|--------|----------------------|--------|--------|--------|--------|

| Z8X4823 | 80-pin         | [7:0]  | [7:0]  | [7:0]  | [7:0]                | [7:0]  | [7:0]  | [7:0]  | [3:0]  |

| Z8X6421 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | <u>[6:3,</u><br>1:0] | -      | -      | -      | -      |

| Z8X6421 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]                | -      | -      | -      | -      |

| Z8X6422 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]                | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8X6423 | 80-pin         | [7:0]  | [7:0]  | [7:0]  | [7:0]                | [7:0]  | [7:0]  | [7:0]  | [3:0]  |

Table 11. Port Availability by Device and Package Type (Continued)

## Architecture

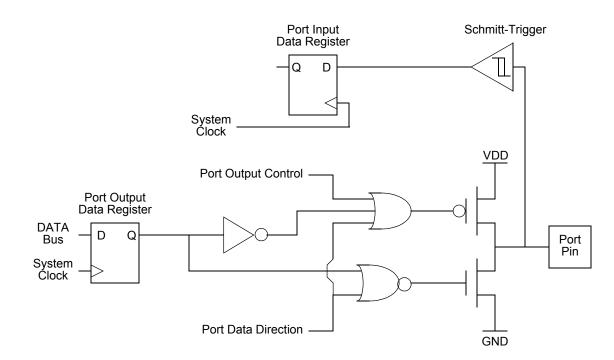

Figure 10 displays a simplified block diagram of a GPIO port pin. In Figure 10, the ability to accommodate alternate functions and variable port current drive strength are not illustrated.

Figure 10. GPIO Port Pin Block Diagram

| Port   | Pin     | Mnemonic   | Alternate Function Description               |

|--------|---------|------------|----------------------------------------------|

| Port C | PC0     | T1IN       | Timer 1 Input                                |

|        | PC1     | T10UT      | Timer 1 Output                               |

|        | PC2     | SS         | SPI Slave Select                             |

|        | PC3     | SCK        | SPI Serial Clock                             |

|        | PC4     | MOSI       | SPI Master Out/Slave In                      |

|        | PC5     | MISO       | SPI Master In/Slave Out                      |

|        | PC6     | T2IN       | Timer 2 In                                   |

|        | PC7     | T2OUT      | Timer 2 Out                                  |

| Port D | PD0     | T3IN       | Timer 3 In (unavailable in 44-pin packages)  |

|        | PD1     | T3OUT      | Timer 3 Out (unavailable in 44-pin packages) |

|        | PD2     | N/A        | No alternate function                        |

|        | PD3     | DE1        | UART 1 Driver Enable                         |

|        | PD4     | RXD1/IRRX1 | UART 1/IrDA 1 Receive Data                   |

|        | PD5     | TXD1/IRTX1 | UART 1/IrDA 1 Transmit Data                  |

|        | PD6     | CTS1       | UART 1 Clear to Send                         |

|        | PD7     | RCOUT      | Watchdog Timer RC Oscillator Output          |

| Port E | PE[7:0] | N/A        | No alternate functions                       |

| Port F | PF[7:0] | N/A        | No alternate functions                       |

| Port G | PG[7:0] | N/A        | No alternate functions                       |

| Port H | PH0     | ANA8       | ADC Analog Input 8                           |

|        | PH1     | ANA9       | ADC Analog Input 9                           |

|        | PH2     | ANA10      | ADC Analog Input 10                          |

|        | PH3     | ANA11      | ADC Analog Input 11                          |

|        |         |            |                                              |

Table 12. Port Alternate Function Mapping (Continued)

## **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins may be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupts generate an interrupt when any edge occurs (both rising and falling). For more information on interrupts using the GPIO pins, see Interrupt Controller on page 67.

## **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 13 lists these Port registers. Use the Port A–H Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| PxADDR                     | Port A–H Address Register<br>(Selects sub-registers)            |

| PxCTL                      | Port A–H Control Register<br>(Provides access to sub-registers) |

| PxIN                       | Port A–H Input Data Register                                    |

| PxOUT                      | Port A–H Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

|                            |                                                                 |

| PxDD                       | Data Direction                                                  |

| PxDD<br>PxAF               | Data Direction           Alternate Function                     |

| - <u></u>                  |                                                                 |

| PxAF                       | Alternate Function                                              |

#### Table 13. GPIO Port Registers and Sub-Registers

#### Port A–H Address Registers

The Port A–H Address registers select the GPIO Port functionality accessible through the Port A–H Control registers. The Port A–H Address and Control registers combine to provide access to all GPIO Port control (Table 14).

| BITS  | 7 | 6                                              | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------------------------------------------|---|---|---|---|---|---|

| FIELD |   | PADDR[7:0]                                     |   |   |   |   |   |   |

| RESET |   | 00H                                            |   |   |   |   |   |   |

| R/W   |   | R/W                                            |   |   |   |   |   |   |

| ADDR  |   | FD0H, FD4H, FD8H, FDCH, FE0H, FE4H, FE8H, FECH |   |   |   |   |   |   |

PADxS—PAx/PDx Selection 0 = PAx is used for the interrupt for PAx/PDx interrupt request. 1 = PDx is used for the interrupt for PAx/PDx interrupt request. where x indicates the specific GPIO Port pin number (0 through 7).

## Interrupt Control Register

The Interrupt Control (IRQCTL) register (Table 38) contains the master enable bit for all interrupts.

#### Table 38. Interrupt Control Register (IRQCTL)

| BITS  | 7    | 6 | 5        | 4 | 3 | 2 | 1 | 0 |

|-------|------|---|----------|---|---|---|---|---|

| FIELD | IRQE |   | Reserved |   |   |   |   |   |

| RESET |      | 0 |          |   |   |   |   |   |

| R/W   | R/W  |   | R        |   |   |   |   |   |

| ADDR  | FCFH |   |          |   |   |   |   |   |

IRQE—Interrupt Request Enable

This bit is set to 1 by execution of an EI or IRET instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, or Reset.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—Must be 0.

# zilog <sub>11</sub>

#### **Receiver Interrupts**

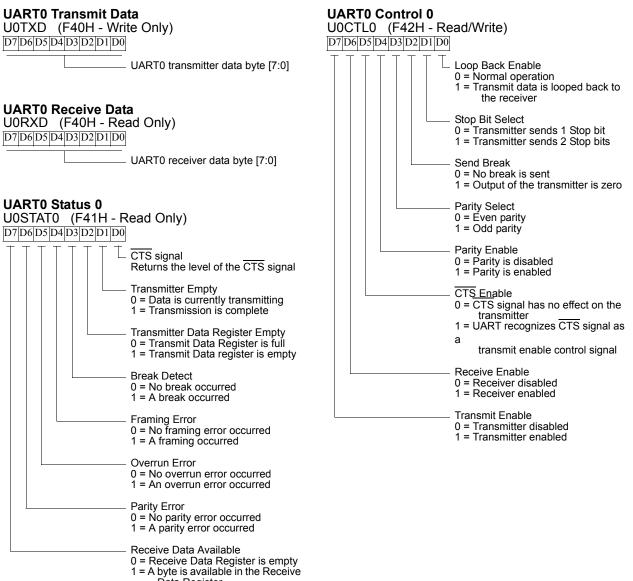

The receiver generates an interrupt when any of the following occurs:

• A data byte has been received and is available in the UART Receive Data register. This interrupt can be disabled independent of the other receiver interrupt sources. The received data interrupt occurs once the receive character has been received and placed in the Receive Data register. Software must respond to this received data available condition before the next character is completely received to avoid an overrun error.

**Note:** In MULTIPROCESSOR mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and should be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data register must be read again to clear the error bits is the UART Status 0 register. Updates to the Receive Data register occur only when the next data word is received.

#### **UART Data and Error Handling Procedure**

Figure 18 on page 113 displays the recommended procedure for use in UART receiver interrupt service routines.

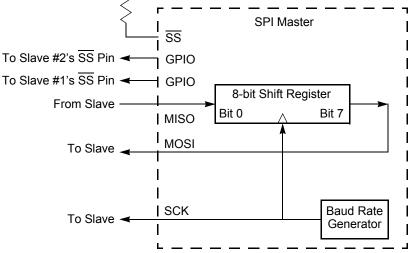

Figure 23. SPI Configured as a Master in a Single Master, Multiple Slave System

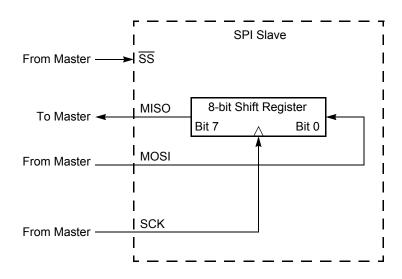

Figure 24. SPI Configured as a Slave

## Operation

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (serial clock, transmit, receive and Slave select). The SPI block consists of a transmit/receive shift register, a Baud Rate (clock) Generator and a control unit.

Table 64. SPI Control Register (SPICTL)

| BITS  | 7    | 6    | 5    | 4     | 3      | 2   | 1    | 0     |

|-------|------|------|------|-------|--------|-----|------|-------|

| FIELD | IRQE | STR  | BIRQ | PHASE | CLKPOL | WOR | MMEN | SPIEN |

| RESET |      | 0    |      |       |        |     |      |       |

| R/W   |      | R/W  |      |       |        |     |      |       |

| ADDR  |      | F61H |      |       |        |     |      |       |

IRQE—Interrupt Request Enable

0 = SPI interrupts are disabled. No interrupt requests are sent to the Interrupt Controller.

1 = SPI interrupts are enabled. Interrupt requests are sent to the Interrupt Controller.

STR—Start an SPI Interrupt Request

0 = No effect.

1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART. Writing a 1 to the IRQ bit in the SPI Status register clears this bit to 0.

BIRQ-BRG Timer Interrupt Request

If the SPI is enabled, this bit has no effect. If the SPI is disabled:

0 = The Baud Rate Generator timer function is disabled.

1 = The Baud Rate Generator timer function and time-out interrupt are enabled.

PHASE—Phase Select

Sets the phase relationship of the data to the clock. For more information on operation of the PHASE bit, see SPI Clock Phase and Polarity Control on page 132.

CLKPOL—Clock Polarity

0 = SCK idles Low (0).

1 = SCK idle High (1).

WOR-Wire-OR (OPEN-DRAIN) Mode Enabled

0 = SPI signal pins not configured for open-drain.

$1 = \text{All four SPI signal pins (SCK, \overline{SS}, MISO, MOSI)}$  configured for open-drain function. This setting is typically used for multi-master and/or multi-slave configurations.

MMEN—SPI Master Mode Enable

0 = SPI configured in Slave mode.

1 = SPI configured in Master mode.

SPIEN—SPI Enable

0 = SPI disabled.

1 = SPI enabled.

## SPI Status Register

The SPI Status register (Table 65) indicates the current state of the SPI. All bits revert to their reset state if the SPIEN bit in the SPICTL register = 0.

## Table 65. SPI Status Register (SPISTAT)

| BITS                                                       | 7    | 6   | 5   | 4   | 3   | 2      | 1    | 0    |

|------------------------------------------------------------|------|-----|-----|-----|-----|--------|------|------|

| FIELD                                                      | IRQ  | OVR | COL | ABT | Res | served | TXST | SLAS |

| RESET                                                      | 0 1  |     |     |     |     |        |      | 1    |

| R/W                                                        |      | R/  | W*  |     |     |        | R    |      |

| ADDR                                                       | F62H |     |     |     |     |        |      |      |

| Note: R/W* = Read access. Write a 1 to clear the bit to 0. |      |     |     |     |     |        |      |      |

IRQ—Interrupt Request

If SPIEN = 1, this bit is set if the STR bit in the SPICTL register is set, or upon completion of an SPI master or slave transaction. This bit does not set if SPIEN = 0 and the SPI Baud Rate Generator is used as a timer to generate the SPI interrupt.

- 0 = No SPI interrupt request pending.

- 1 =SPI interrupt request is pending.

OVR—Overrun

- 0 = An overrun error has not occurred.

- 1 = An overrun error has been detected.

COL—Collision

0 = A multi-master collision (mode fault) has not occurred.

1 = A multi-master collision (mode fault) has been detected.

## ABT-Slave mode transaction abort

This bit is set if the SPI is configured in slave mode, a transaction is occurring and  $\overline{SS}$  deasserts before all bits of a character have been transferred as defined by the NUMBITS field of the SPIMODE register. The IRQ bit also sets, indicating the transaction has completed.

0 = A slave mode transaction abort has not occurred.

1 = A slave mode transaction abort has been detected.

Reserved—Must be 0.

TXST—Transmit Status

0 = No data transmission currently in progress.

1 = Data transmission currently in progress.

SLAS—Slave Select If SPI enabled as a Slave,

IEN— $I^2C$  Enable 1 = The  $I^2C$  transmitter and receiver are enabled. 0 = The  $I^2C$  transmitter and receiver are disabled.

## START-Send Start Condition

This bit sends the Start condition. Once asserted, it is cleared by the I<sup>2</sup>C Controller after it sends the START condition or if the IEN bit is deasserted. If this bit is 1, it cannot be cleared to 0 by writing to the register. After this bit is set, the Start condition is sent if there is data in the I<sup>2</sup>C Data or I<sup>2</sup>C Shift register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until the Data register is written. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a START condition after the byte shifts and the acknowledge phase completes. If the STOP bit is also set, it also waits until the STOP condition is sent before the sending the START condition.

#### STOP—Send Stop Condition

This bit causes the I<sup>2</sup>C Controller to issue a Stop condition after the byte in the I<sup>2</sup>C Shift register has completed transmission or after a byte has been received in a receive operation. Once set, this bit is reset by the I<sup>2</sup>C Controller after a Stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by writing to the register.

#### BIRQ—Baud Rate Generator Interrupt Request

This bit allows the I<sup>2</sup>C Controller to be used as an additional timer when the I<sup>2</sup>C Controller is disabled. This bit is ignored when the I<sup>2</sup>C Controller is enabled. 1 = An interrupt occurs every time the baud rate generator counts down to one. 0 = No baud rate generator interrupt occurs.

#### TXI—Enable TDRE interrupts

This bit enables the transmit interrupt when the  $I^2C$  Data register is empty (TDRE = 1).

1 = Transmit interrupt (and DMA transmit request) is enabled.

0 = Transmit interrupt (and DMA transmit request) is disabled.

#### NAK-Send NAK

This bit sends a Not Acknowledge condition after the next byte of data has been read from the  $I^2C$  slave. Once asserted, it is deasserted after a Not Acknowledge is sent or the IEN bit is deasserted. If this bit is 1, it cannot be cleared to 0 by writing to the register.

#### FLUSH-Flush Data

Setting this bit to 1 clears the I<sup>2</sup>C Data register and sets the TDRE bit to 1. This bit allows flushing of the I<sup>2</sup>C Data register when a Not Acknowledge interrupt is received after the data has been sent to the I<sup>2</sup>C Data register. Reading this bit always returns 0.

## FILTEN—I<sup>2</sup>C Signal Filter Enable

This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.

- 1 =low-pass filters are enabled.

- 0 =low-pass filters are disabled.

| TXRXSTATE | State Description                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0_000     | Idle State                                                                                                                              |

| 0_0001    | START State                                                                                                                             |

| 0_0010    | Send/Receive data bit 7                                                                                                                 |

| 0_0011    | Send/Receive data bit 6                                                                                                                 |

| 0_0100    | Send/Receive data bit 5                                                                                                                 |

| 0_0101    | Send/Receive data bit 4                                                                                                                 |

| 0_0110    | Send/Receive data bit 3                                                                                                                 |

| 0_0111    | Send/Receive data bit 2                                                                                                                 |

| 0_1000    | Send/Receive data bit 1                                                                                                                 |

| 0_1001    | Send/Receive data bit 0                                                                                                                 |

| 0_1010    | Data Acknowledge State                                                                                                                  |

| 0_1011    | Second half of data Acknowledge State used only for not acknowledge                                                                     |

| 0_1100    | First part of STOP state                                                                                                                |

| 0_1101    | Second part of STOP state                                                                                                               |

| 0_1110    | 10-bit addressing: Acknowledge State for 2nd address byte<br>7-bit addressing: Address Acknowledge State                                |

| 0_1111    | 10-bit address: Bit 0 (Least significant bit) of 2nd address byte<br>7-bit address: Bit 0 (Least significant bit) (R/W) of address byte |

| 1_0000    | 10-bit addressing: Bit 7 (Most significant bit) of 1st address byte                                                                     |

| 1_0001    | 10-bit addressing: Bit 6 of 1st address byte                                                                                            |

| 1_0010    | 10-bit addressing: Bit 5 of 1st address byte                                                                                            |

| 1_0011    | 10-bit addressing: Bit 4 of 1st address byte                                                                                            |

| 1_0100    | 10-bit addressing: Bit 3 of 1st address byte                                                                                            |

| 1_0101    | 10-bit addressing: Bit 2 of 1st address byte                                                                                            |

| 1_0110    | 10-bit addressing: Bit 1 of 1st address byte                                                                                            |

| 1_0111    | 10-bit addressing: Bit 0 (R/W) of 1st address byte                                                                                      |

| 1_1000    | 10-bit addressing: Acknowledge state for 1st address byte                                                                               |

| 1_1001    | 10-bit addressing: Bit 7 of 2nd address byte<br>7-bit addressing: Bit 7 of address byte                                                 |

| 1_1010    | 10-bit addressing: Bit 6 of 2nd address byte<br>7-bit addressing: Bit 6 of address byte                                                 |

| 1_1011    | 10-bit addressing: Bit 5 of 2nd address byte<br>7-bit addressing: Bit 5 of address byte                                                 |

| 1_1100    | 10-bit addressing: Bit 4 of 2nd address byte<br>7-bit addressing: Bit 4 of address byte                                                 |

0101 = ADC Analog Inputs 0-5 updated. 0110 = ADC Analog Inputs 0-6 updated. 0111 = ADC Analog Inputs 0-7 updated. 1000 = ADC Analog Inputs 0-8 updated. 1001 = ADC Analog Inputs 0-9 updated. 1010 = ADC Analog Inputs 0-10 updated. 1011 = ADC Analog Inputs 0-11 updated. 1100-1111 = Reserved.

## DMA Status Register

The DMA Status register (Table 85 on page 173) indicates the DMA channel that generated the interrupt and the ADC Analog Input that is currently undergoing conversion. Reads from this register reset the Interrupt Request Indicator bits (IRQA, IRQ1, and IRQ0) to 0. Therefore, software interrupt service routines that read this register must process all three interrupt sources from the DMA.

| BITS  | 7 | 6   | 5      | 4  | 3        | 2    | 1    | 0    |

|-------|---|-----|--------|----|----------|------|------|------|

| FIELD |   | CAD | C[3:0] |    | Reserved | IRQA | IRQ1 | IRQ0 |

| RESET | 0 |     |        |    |          |      |      |      |

| R/W   |   |     |        | F  | २        |      |      |      |

| ADDR  |   |     |        | FB | FH       |      |      |      |

#### Table 85. DMA\_ADC Status Register (DMAA\_STAT)

CADC[3:0]—Current ADC Analog Input

This field identifies the Analog Input that the ADC is currently converting.

Reserved

This bit is reserved and must be 0.

IRQA—DMA\_ADC Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

$0 = DMA\_ADC$  is not the source of the interrupt from the DMA Controller.

1 = DMA\_ADC completed transfer of data from the last ADC Analog Input and generated an interrupt.

IRQ1—DMA1 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

0 = DMA1 is not the source of the interrupt from the DMA Controller.

1 = DMA1 completed transfer of data to/from the End Address and generated an interrupt.

IRQ0—DMA0 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

## zilog

#### 186

## **Timing Using the Flash Frequency Registers**

Before performing a program or erase operation on the Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasure of the Flash with system clock frequencies ranging from 20 kHz through 20 MHz (the valid range is limited to the device operating frequencies).

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit Flash Frequency value must contain the system clock frequency in kHz. This value is calculated using the following equation:.

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 20 kHz, above 20 MHz, or outside of the device operating frequency range. The Flash Frequency High and Low Byte registers must be loaded with the correct value to insure proper Flash programming and erase operations.

## Flash Read Protection

The user code contained within the Flash memory can be protected from external access. Programming the Flash Read Protect Option Bit prevents reading of user code by the On-Chip Debugger or by using the Flash Controller Bypass mode. For more information, see Option Bits on page 195 and On-Chip Debugger on page 199.

## Flash Write/Erase Protection

The 64K Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by the Flash Controller unlock mechanism, the Flash Sector Protect register, and the Flash Write Protect option bit.

#### Flash Controller Unlock Mechanism

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, the Flash controller must be unlocked. After unlocking the Flash Controller, the Flash can be programmed or erased. Any value written by user code to the Flash Control register or Page Select Register out of sequence will lock the Flash Controller.

Follow the steps below to unlock the Flash Controller from user code:

- 1. Write 00H to the Flash Control register to reset the Flash Controller.

- 2. Write the page to be programmed or erased to the Page Select register.

the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved

These Option Bits are reserved for future use and must always be 1. This setting is the default for unprogrammed (erased) Flash.

FWP—Flash Write Protect (Flash version only)

| FWP | Description                                                                                                                     |

|-----|---------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming, Page Erase, and Mass Erase through User Code is disabled.<br>Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, and Page Erase are enabled for all of Flash Program Memory.                                                        |

## Flash Memory Address 0001H

#### Table 99. Options Bits at Flash Memory Address 0001H

| BITS        | 7                         | 6              | 5            | 4           | 3     | 2 | 1 | 0 |

|-------------|---------------------------|----------------|--------------|-------------|-------|---|---|---|

| FIELD       |                           |                |              | Rese        | erved |   |   |   |

| RESET       | U                         |                |              |             |       |   |   |   |

| R/W         | R/W                       |                |              |             |       |   |   |   |

| ADDR        | ADDR Program Memory 0001H |                |              |             |       |   |   |   |

| Note: U = U | Jnchanged b               | y Reset. R = I | Read-Only. R | /W = Read/W | rite. |   |   |   |

Reserved

These Option Bits are reserved for future use and must always be 1. This setting is the default for unprogrammed (erased) Flash.

| 24 | 5 |

|----|---|

|    | • |

| Binary | Hex | Assembly<br>Mnemonic | Definition                     | Flag Test Operation   |

|--------|-----|----------------------|--------------------------------|-----------------------|

| 0011   | 3   | ULE                  | Unsigned Less Than or Equal    | (C OR Z) = 1          |

| 0100   | 4   | OV                   | Overflow                       | V = 1                 |

| 0101   | 5   | MI                   | Minus                          | S = 1                 |

| 0110   | 6   | Z                    | Zero                           | Z = 1                 |

| 0110   | 6   | EQ                   | Equal                          | Z = 1                 |

| 0111   | 7   | С                    | Carry                          | C = 1                 |

| 0111   | 7   | ULT                  | Unsigned Less Than             | C = 1                 |

| 1000   | 8   | T (or blank)         | Always True                    | -                     |

| 1001   | 9   | GE                   | Greater Than or Equal          | (S XOR V) = 0         |

| 1010   | А   | GT                   | Greater Than                   | (Z OR (S XOR V)) = 0  |

| 1011   | В   | UGT                  | Unsigned Greater Than          | (C = 0 AND Z = 0) = 1 |

| 1100   | С   | NOV                  | No Overflow                    | V = 0                 |

| 1101   | D   | PL                   | Plus                           | S = 0                 |

| 1110   | Е   | NZ                   | Non-Zero                       | Z = 0                 |

| 1110   | Е   | NE                   | Not Equal                      | Z = 0                 |

| 1111   | F   | NC                   | No Carry                       | C = 0                 |

| 1111   | F   | UGE                  | Unsigned Greater Than or Equal | C = 0                 |

## Table 124. Condition Codes (Continued)

## eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

zilog

Table 125 through Table 132 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| СР       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| CPX      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### Table 125. Arithmetic Instructions

#### Table 126. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction      |

|----------|-------------|------------------|

| BCLR     | bit, dst    | Bit Clear        |

| BIT      | p, bit, dst | Bit Set or Clear |

| BSET     | bit, dst    | Bit Set          |

246

| Assembly      |                                                    |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | - Fetch | Instr. |

|---------------|----------------------------------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic      | Symbolic Operation                                 | dst | src         | (Hex)       | С | Ζ | S   | V   | D | Н | Cycles  |        |

| RRC dst       |                                                    | R   |             | C0          | * | * | *   | *   | - | - | 2       | 2      |

|               | ► <u>D7 D6 D5 D4 D3 D2 D1 D0</u> ► <u>C</u><br>dst | IR  |             | C1          | • |   |     |     |   |   | 2       | 3      |

| SBC dst, src  | $dst \gets dst - src - C$                          | r   | r           | 32          | * | * | *   | *   | 1 | * | 2       | 3      |

|               | -                                                  | r   | lr          | 33          | • |   |     |     |   |   | 2       | 4      |

|               | -                                                  | R   | R           | 34          | • |   |     |     |   |   | 3       | 3      |

|               | -                                                  | R   | IR          | 35          | • |   |     |     |   |   | 3       | 4      |

|               | -                                                  | R   | IM          | 36          | • |   |     |     |   |   | 3       | 3      |

|               | -                                                  | IR  | IM          | 37          | • |   |     |     |   |   | 3       | 4      |

| SBCX dst, src | $dst \leftarrow dst - src - C$                     | ER  | ER          | 38          | * | * | *   | *   | 1 | * | 4       | 3      |

|               | -                                                  | ER  | IM          | 39          | • |   |     |     |   |   | 4       | 3      |

| SCF           | C ← 1                                              |     |             | DF          | 1 | - | -   | -   | - | - | 1       | 2      |

| SRA dst       |                                                    | R   |             | D0          | * | * | *   | 0   | - | - | 2       | 2      |

|               | D7_D6_D5_D4_D3_D2_D1_D0 → Cdst                     | IR  |             | D1          |   |   |     |     |   |   | 2       | 3      |

| SRL dst       | ) → D7 D6 D5 D4 D3 D2 D1 D0 → C                    | R   |             | 1F C0       | * | * | 0   | *   | - | - | 3       | 2      |

|               | dst                                                | IR  |             | 1F C1       | • |   |     |     |   |   | 3       | 3      |

| SRP src       | $RP \leftarrow src$                                |     | IM          | 01          | - | - | -   | -   | - | - | 2       | 2      |

| STOP          | STOP Mode                                          |     |             | 6F          | - | - | -   | -   | - | - | 1       | 2      |

| SUB dst, src  | $dst \leftarrow dst - src$                         | r   | r           | 22          | * | * | *   | *   | 1 | * | 2       | 3      |

|               | -                                                  | r   | lr          | 23          | • |   |     |     |   |   | 2       | 4      |

|               | -                                                  | R   | R           | 24          | • |   |     |     |   |   | 3       | 3      |

|               | -                                                  | R   | IR          | 25          | • |   |     |     |   |   | 3       | 4      |

|               | -                                                  | R   | IM          | 26          |   |   |     |     |   |   | 3       | 3      |

|               | -                                                  | IR  | IM          | 27          |   |   |     |     |   |   | 3       | 4      |

| SUBX dst, src | $dst \leftarrow dst - src$                         | ER  | ER          | 28          | * | * | *   | *   | 1 | * | 4       | 3      |

|               | -                                                  | ER  | IM          | 29          | • |   |     |     |   |   | 4       | 3      |

## Table 133. eZ8 CPU Instruction Summary (Continued)

## Table 134. Opcode Map Abbreviations

| Abbreviation | Description                           | Abbreviation                                   | Description            |

|--------------|---------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |

| сс           | Condition code                        | р                                              | Polarity (0 or 1)      |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                   | R                                              | 8-bit register         |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register             | RA                                             | Relative               |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |