#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 68-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1622vs020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Master Interrupt Enable 69                                   |

|--------------------------------------------------------------|

| Interrupt Vectors and Priority 70                            |

| Interrupt Assertion                                          |

| Software Interrupt Assertion                                 |

| Interrupt Control Register Definitions                       |

| Interrupt Request 0 Register 71                              |

| Interrupt Request 1 Register 72                              |

| Interrupt Request 2 Register 73                              |

| IRQ0 Enable High and Low Bit Registers                       |

| IRQ1 Enable High and Low Bit Registers                       |

| IRQ2 Enable High and Low Bit Registers                       |

| Interrupt Edge Select Register                               |

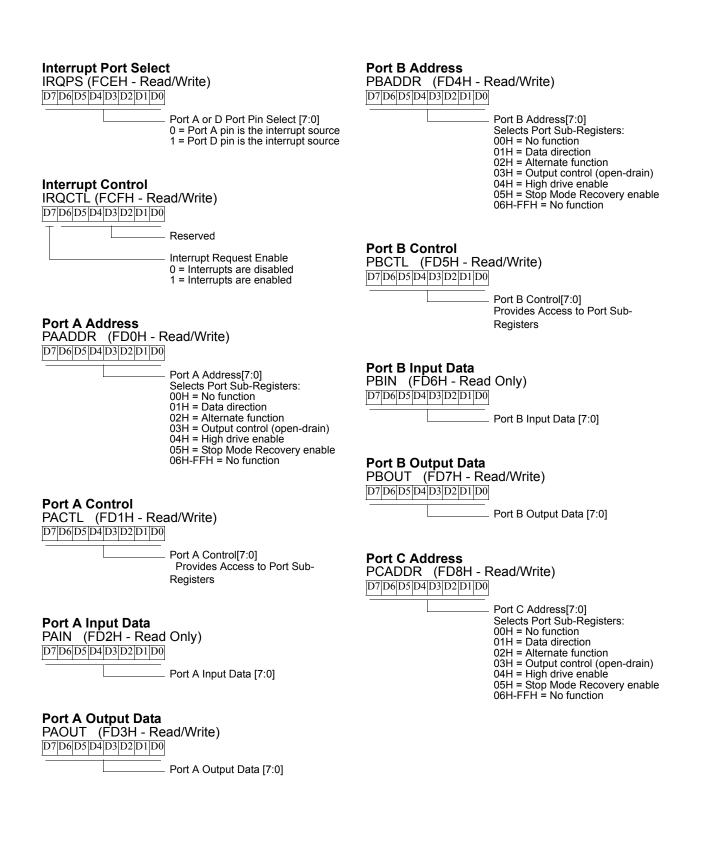

| Interrupt Port Select Register                               |

| Interrupt Control Register                                   |

| Timers                                                       |

| Overview                                                     |

| Architecture                                                 |

| Operation                                                    |

| Timer Operating Modes                                        |

| Reading the Timer Count Values                               |

| Timer Output Signal Operation                                |

| Timer Control Register Definitions                           |

| Timer 0-3 High and Low Byte Registers                        |

| Timer Reload High and Low Byte Registers                     |

| Timer 0-3 PWM High and Low Byte Registers                    |

| Timer 0-3 Control 0 Registers                                |

| Timer 0-3 Control 1 Registers                                |

| <b>v</b>                                                     |

| Watchdog Timer                                               |

| Overview                                                     |

| Operation                                                    |

| Watchdog Timer Refresh 98                                    |

| Watchdog Timer Time-Out Response    98                       |

| Watchdog Timer Reload Unlock Sequence                        |

| Watchdog Timer Control Register Definitions                  |

| Watchdog Timer Control Register 100                          |

| Watchdog Timer Reload Upper, High and Low Byte Registers 101 |

#### xiii

#### Braces

The curly braces, { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• Example: The 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most-significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

#### Parentheses

The parentheses, (), indicate an indirect register address lookup.

• Example: (R1) is the memory location referenced by the address contained in the Working Register R1.

#### **Parentheses/Bracket Combinations**

The parentheses, (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• Example: Assume PC[15:0] contains the value 1234h. (PC[15:0]) then refers to the contents of the memory location at address 1234h.

#### Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words reset or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* may not be included; however, it is implied.

#### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register [n:n].

• Example: ADDR[15:0] refers to bits 15 through bit 0 of the Address.

#### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least* significant byte and most significant byte, respectively. The lowercase forms, *lsb* and *msb*, mean *least* significant bit and most significant bit, respectively.

#### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings and conditions in general text.

- Example 1: The receiver forces the SCL line to Low.

- Example 2: The Master can generate a Stop condition to abort the transfer.

# **Signal Descriptions**

Table 3 describes the Z8 Encore! XP signals. To determine the signals available for the specific package styles, see Pin Configurations on page 8.

# Table 3. Signal Descriptions

| Signal<br>Mnemonic          | I/O        | Description                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purp                | ose I/O Po | rts A-H                                                                                                                                                                                                                                                                                                                                                 |

| PA[7:0]                     | I/O        | Port A[7:0]. These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                                                                                               |

| PB[7:0]                     | I/O        | Port B[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                                                               |

| PC[7:0]                     | I/O        | Port C[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs                                                                                                                                                                                                                   |

| PD[7:0]                     | I/O        | Port D[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs                                                                                                                                                                                                                   |

| PE[7:0]                     | I/O        | Port E[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                                                  |

| PF[7:0]                     | I/O        | Port F[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                                                  |

| PG[7:0]                     | I/O        | Port G[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                                                  |

| PH[3:0]                     | I/O        | Port H[3:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                                                               |

| I <sup>2</sup> C Controller |            |                                                                                                                                                                                                                                                                                                                                                         |

| SCL                         | 0          | Serial Clock. This is the output clock for the I <sup>2</sup> C. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SCL function, this pin is open-drain.                                                                                                      |

| SDA                         | I/O        | Serial Data. This open-drain pin transfers data between the I <sup>2</sup> C and a slave. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SDA function, this pin is open-drain.                                                                             |

| SPI Controller              | r          |                                                                                                                                                                                                                                                                                                                                                         |

| SS                          | I/O        | Slave Select. This signal can be an output or an input. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI master, this pin may be configured as the Slave Select output. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI slave, this pin is the input slave select. It is multiplexed with a general-purpose I/O pin. |

| Program Memory Address (Hex)              | Function                 |

|-------------------------------------------|--------------------------|

| 0000-0001                                 | Option Bits              |

| 0002-0003                                 | Reset Vector             |

| 0004-0005                                 | WDT Interrupt Vector     |

| 0006-0007                                 | Illegal Instruction Trap |

| 0008-0037                                 | Interrupt Vectors*       |

| 0038-BFFF                                 | Program Memory           |

| Z8F642x Products                          |                          |

| 0000-0001                                 | Option Bits              |

| 0002-0003                                 | Reset Vector             |

| 0004-0005                                 | WDT Interrupt Vector     |

| 0006-0007                                 | Illegal Instruction Trap |

| 0008-0037                                 | Interrupt Vectors*       |

| 0038-FFFF                                 | Program Memory           |

| *See Table 23 on page 68 for a list of th | ne interrupt vectors.    |

### Table 5. Z8 Encore! XP 64K Series Flash Microcontrollers Program Memory Maps (Continued)

## **Data Memory**

The Z8 Encore! XP 64K Series Flash Microcontrollers does not use the eZ8 CPU's 64 KB Data Memory address space.

## **Information Area**

Table 6 on page 22 describes the Z8 Encore! XP 64K Series Flash Microcontrollers Information Area. This 512 byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into the Program Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, execution of LDC and LDCI instruction from these Program Memory addresses return the Information Area data rather than the Program Memory data. Reads of these addresses through the On-Chip Debugger also returns the Information Area data. Execution of code from these addresses continues to correctly use the Program Memory. Access to the Information Area is read-only.

# Port A–H Data Direction Sub-Registers

The Port A–H Data Direction sub-register is accessed through the Port A–H Control register by writing 01H to the Port A–H Address register (Table 16).

## Table 16. Port A–H Data Direction Sub-Registers

| BITS  | 7      | 6             | 5           | 4             | 3             | 2            | 1            | 0      |  |

|-------|--------|---------------|-------------|---------------|---------------|--------------|--------------|--------|--|

| FIELD | DD7    | DD6           | DD5         | DD4           | DD3           | DD2          | DD1          | DD0    |  |

| RESET |        | 1             |             |               |               |              |              |        |  |

| R/W   |        | R/W           |             |               |               |              |              |        |  |

| ADDR  | lf 01F | I in Port A–I | H Address R | egister, acce | essible throu | igh Port A–⊦ | I Control Re | gister |  |

DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

- 0 = Output. Data in the Port A–H Output Data register is driven onto the port pin.

- 1 = Input. The port pin is sampled and the value written into the Port A–H Input Data Register. The output driver is tri-stated.

## Port A–H Alternate Function Sub-Registers

The Port A–H Alternate Function sub-register (Table 17) is accessed through the Port A–H Control register by writing 02H to the Port A–H Address register. The Port A–H Alternate Function sub-registers select the alternate functions for the selected pins. To determine the alternate function associated with each port pin, see GPIO Alternate Functions on page 59.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline may result in unpredictable operation.

## Table 17. Port A–H Alternate Function Sub-Registers

| BITS  | 7      | 6             | 5           | 4             | 3             | 2            | 1            | 0      |  |  |

|-------|--------|---------------|-------------|---------------|---------------|--------------|--------------|--------|--|--|

| FIELD | AF7    | AF6           | AF5         | AF4           | AF3           | AF2          | AF1          | AF0    |  |  |

| RESET |        | 0             |             |               |               |              |              |        |  |  |

| R/W   |        | R/W           |             |               |               |              |              |        |  |  |

| ADDR  | lf 02⊦ | l in Port A–ł | H Address R | egister, acce | essible throu | igh Port A–⊦ | I Control Re | gister |  |  |

**Caution:** The following style of coding to generate software interrupts by setting bits in the Interrupt Request registers is NOT recommended. All incoming interrupts that are received between execution of the first LDX command and the last LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

To avoid missing interrupts, the following style of coding to set bits in the Interrupt Request registers is recommended:

Good coding style that avoids lost interrupt requests:

ORX IRQO, MASK

## **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## Interrupt Request 0 Register

The Interrupt Request 0 (IRO0) register (Table 24) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8<sup>™</sup> CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending

|       |     |     | - J ( |       |       |      |      |      |  |  |

|-------|-----|-----|-------|-------|-------|------|------|------|--|--|

| BITS  | 7   | 6   | 5     | 4     | 3     | 2    | 1    | 0    |  |  |

| FIELD | T2I | T1I | TOI   | U0RXI | U0TXI | I2CI | SPII | ADCI |  |  |

| RESET |     | 0   |       |       |       |      |      |      |  |  |

| R/W   |     | R/W |       |       |       |      |      |      |  |  |

| ADDR  |     |     |       | FC    | 0H    |      |      |      |  |  |

Table 24. Interrupt Request 0 Register (IRQ0)

T2I—Timer 2 Interrupt Request

0 = No interrupt request is pending for Timer 2.

1 = An interrupt request from Timer 2 is awaiting service.

# zilog ,

#### Table 33. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 1          | 1          | Level 3  | High        |

**Note:** where *x* indicates the register bits from 0 through 7.

### Table 34. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |  |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|--|--|

| FIELD | T3ENH | U1RENH | U1TENH | DMAENH | C3ENH | C2ENH | C1ENH | C0ENH |  |  |

| RESET |       | 0      |        |        |       |       |       |       |  |  |

| R/W   |       | R/W    |        |        |       |       |       |       |  |  |

| ADDR  |       |        |        | FC     | 7H    |       |       |       |  |  |

T3ENH—Timer 3 Interrupt Request Enable High Bit U1RENH—UART 1 Receive Interrupt Request Enable High Bit U1TENH—UART 1 Transmit Interrupt Request Enable High Bit DMAENH—DMA Interrupt Request Enable High Bit C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 35. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|--|

| FIELD | T3ENL | U1RENL | U1TENL | DMAENL | C3ENL | C2ENL | C1ENL | C0ENL |  |

| RESET | 0     |        |        |        |       |       |       |       |  |

| R/W   |       | R/W    |        |        |       |       |       |       |  |

| ADDR  |       |        |        | FC     | 8H    |       |       |       |  |

T3ENL—Timer 3 Interrupt Request Enable Low Bit U1RENL—UART 1 Receive Interrupt Request Enable Low Bit U1TENL—UART 1 Transmit Interrupt Request Enable Low Bit DMAENL—DMA Interrupt Request Enable Low Bit C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H), affecting only the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control 1 register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation must be used to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO Port pin Timer Input alternate function. The TPOL bit in the Timer Control 1 Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** *The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency.*

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control 1 register to:

- Disable the timer

- Configure the timer for COUNTER mode

- 6. Write to the Timer Control 1 register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In m/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Output Signal Operation**

Timer Output is a GPIO Port pin alternate function. Generally, the Timer Output is toggled every time the counter is reloaded.

### **Timer Control Register Definitions**

Timers 0-2 are available in all packages. Timer 3 is only available in the 64-, 68-, and 80-pin packages.

### Timer 0-3 High and Low Byte Registers

The Timer 0-3 High and Low Byte (TxH and TxL) registers (see Table 39 and Table 40 on page 91) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TMRL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TMRL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

Timer 3 is unavailable in the 40- and 44-pin packages.

| WDT Reload Value | WDT Reload Value |          | e Time-Out Delay<br>WDT oscillator frequency) |

|------------------|------------------|----------|-----------------------------------------------|

| (Hex)            | (Decimal)        | Typical  | Description                                   |

| 000004           | 4                | 400 μs   | Minimum time-out delay                        |

| FFFFF            | 16,777,215       | 1677.5 s | Maximum time-out delay                        |

#### Table 47. Watchdog Timer Approximate Time-Out Delays

## Watchdog Timer Refresh

When first enabled, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer then counts down to 000000H unless a WDT instruction is executed by the eZ8<sup>TM</sup> CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When the 64K Series devices are operating in DEBUG Mode (through the On-Chip Debugger), the Watchdog Timer is continuously refreshed to prevent spurious Watchdog Timer time-outs.

## Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a Reset. The WDT\_RES Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Option Bit, see Option Bits on page 195.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the 64K Series devices are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 47.

# zilog

## 108

## **Receiving Data using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the desired priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) mode functions, if desired.

- Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- Set the MULTIPROCESSOR Mode Bits, MPMD[1:0], to select the desired address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! devices without a DMA block).

- 7. Write the device address to the Address Compare Register (automatic multiprocessor modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception.

- Enable parity, if desired and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine performs the following:

- 1. Check the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. If the interrupt was caused by data available, read the data from the UART Receive Data register. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

# zilog

- 120

- 1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

## **UART Address Compare Register**

The UART Address Compare register (Table 58) stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

## Table 58. UART Address Compare Register (UxADDR)

| BITS  | 7         | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |

|-------|-----------|-----|---|---------|---------|---|---|---|--|

| FIELD | COMP_ADDR |     |   |         |         |   |   |   |  |

| RESET | 0         |     |   |         |         |   |   |   |  |

| R/W   |           | R/W |   |         |         |   |   |   |  |

| ADDR  |           |     |   | F45H ar | nd F4DH |   |   |   |  |

COMP\_ADDR—Compare Address

This 8-bit value is compared to the incoming address bytes.

## UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (see Table 59 and Table 60 on page 121) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the desired 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the UART BRG interrupt interval is calculated using the following equation:

UART BRG Interrupt Interval(s) = System Clock Period (s) × BRG[15:0]

- 0 = DMA0 is not the source of the interrupt from the DMA Controller.

- 1 = DMA0 completed transfer of data to/from the End Address and generated an interrupt.

0100 = ANA4 0101 = ANA5 0110 = ANA6 0111 = ANA7 1000 = ANA8 1001 = ANA9 1010 = ANA10 1011 = ANA1111XX = Reserved.

## ADC Data High Byte Register

The ADC Data High Byte register (Table 87) contains the upper eight bits of the 10-bit ADC output. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

| Table 87. | ADC Data | High | Byte | Register | (ADCD | _H) |

|-----------|----------|------|------|----------|-------|-----|

|-----------|----------|------|------|----------|-------|-----|

| BITS  | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---|---|---|---|---|---|---|

| FIELD | ADCD_H |   |   |   |   |   |   |   |

| RESET | X      |   |   |   |   |   |   |   |

| R/W   | R      |   |   |   |   |   |   |   |

| ADDR  | F72H   |   |   |   |   |   |   |   |

### ADCD\_H—ADC Data High Byte

This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the last conversion output is held in this register. These bits are undefined after a Reset.

## ADC Data Low Bits Register

The ADC Data Low Bits register (Table 88) contains the lower two bits of the conversion value. The data in the ADC Data Low Bits register is latched each time the ADC Data High Byte register is read. Reading this register always returns the lower two bits of the conversion last read into the ADC High Byte register. Access to the ADC Data Low Bits register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

# **On-Chip Debugger Control Register Definitions**

# **OCD Control Register**

The OCD Control register (Table 102) controls the state of the On-Chip Debugger. This register enters or exits DEBUG mode and enables the BRK instruction. It can also reset the Z8F642x family, Z8R642x family device.

A 'reset and stop' function can be achieved by writing 81H to this register. A 'reset and go' function can be achieved by writing 41H to this register. If the device is in DEBUG mode, a 'run' function can be implemented by writing 40H to this register.

Table 102. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4       | 3 | 2 | 1        | 0   |

|-------|---------|-------|--------|---------|---|---|----------|-----|

| FIELD | DBGMODE | BRKEN | DBGACK | BRKLOOP |   |   | Reserved | RST |

| RESET | 0       |       |        |         |   |   |          |     |

| R/W   |         | R/W   |        |         | R |   |          | R/W |

#### DBGMODE—DEBUG Mode

Setting this bit to 1 causes the device to enter DEBUG mode. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to start running again. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device, it cannot be written to 0.

0 = The 64K Series device is operating in NORMAL mode.

1 = The 64K Series device is in DEBUG mode.

#### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves like a NOP. If this bit is set to 1 and a BRK instruction is decoded, the OCD takes action dependent upon the BRKLOOP bit.

- 0 = BRK instruction is disabled.

- 1 = BRK instruction is enabled.

#### DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, then the OCD sends an Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled.

1 = Debug Acknowledge is enabled.

#### BRKLOOP—Breakpoint Loop

This bit determines what action the OCD takes when a BRK instruction is decoded if breakpoints are enabled (BRKEN is 1). If this bit is 0, then the DBGMODE bit is automatically set to 1 and the OCD entered DEBUG mode. If BRKLOOP is set to 1, then the

V<sub>DD</sub> = 3.3 V

V<sub>DD</sub> = 3.3 V

mΑ

5

4

V<sub>DD</sub> = 3.6 V, Fsysclk = 10 MHz

|                                                                        |                                                                           | T <sub>A</sub> = -40 ° | T <sub>A</sub> = –40 °C to 125 °C |          |       |                                                                        |

|------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------|-----------------------------------|----------|-------|------------------------------------------------------------------------|

| Symbol                                                                 | Parameter                                                                 | Minimum                | Typical                           | Maximum  | Units | Conditions                                                             |

| C <sub>PAD</sub>                                                       | GPIO Port Pad<br>Capacitance                                              | -                      | 8.0 <sup>2</sup>                  | _        | pF    |                                                                        |

| C <sub>XIN</sub>                                                       | XIN Pad Capacitance                                                       | _                      | 8.0 <sup>2</sup>                  | _        | pF    |                                                                        |

| C <sub>XOUT</sub>                                                      | XOUT Pad Capacitance                                                      | _                      | 9.5 <sup>2</sup>                  | _        | pF    |                                                                        |

| I <sub>PU</sub>                                                        | Weak Pull-up Current                                                      | 30                     | 100                               | 350      | mA    | V <sub>DD</sub> = 3.0 - 3.6 V                                          |

| Current<br>(See Figure 43 on<br>page 220 and Figu<br>on page 221) GPI0 | (See Figure 43 on                                                         | -                      | 11                                | 16<br>12 | mA    | V <sub>DD</sub> = 3.6 V, Fsysclk = 2<br>MHz<br>V <sub>DD</sub> = 3.3 V |

|                                                                        | page 220 and Figure 44<br>on page 221) GPIO pins<br>configured as outputs | _                      | 9                                 | 11<br>9  | mA    | V <sub>DD</sub> = 3.6 V, Fsysclk =<br>MHz<br>V <sub>DD</sub> = 3.3 V   |

| I <sub>DDH</sub>                                                       | HALT Mode Supply<br>Current                                               |                        | 4                                 | 7<br>5   | mA    | V <sub>DD</sub> = 3.6 V, Fsysclk = 2<br>MHz                            |

3

\_

## Table 106

(See Figure 45 on page 222 and Figure 46

on page 223) GPIO pins

configured as outputs

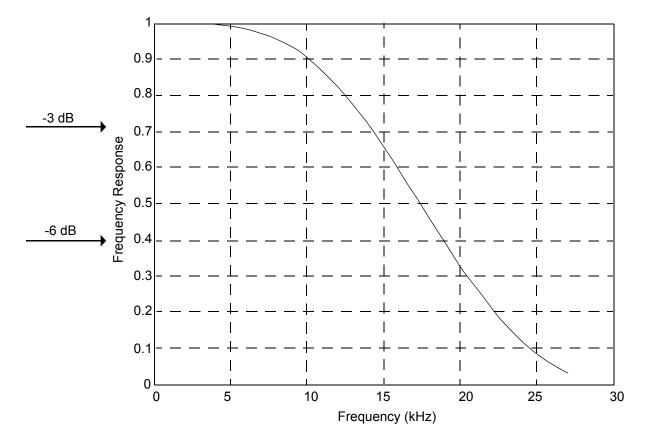

## ADC Magnitude Transfer Function (Linear Scale)

Figure 49. Analog-to-Digital Converter Frequency Response

# 235

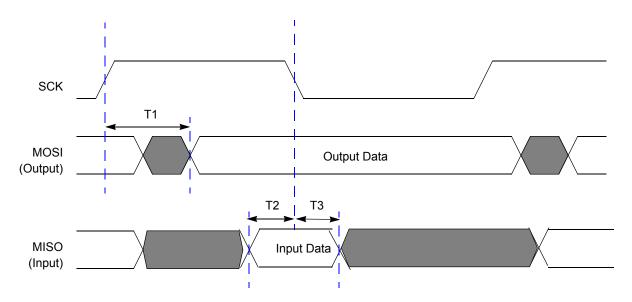

## **SPI Master Mode Timing**

Figure 53 and Table 117 provide timing information for SPI Master mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

|                |                                             | Delay (ns) |     |  |

|----------------|---------------------------------------------|------------|-----|--|

| Parameter      | Abbreviation                                | Min        | Max |  |

| SPI Master     |                                             |            |     |  |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5         | +5  |  |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20         |     |  |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0          |     |  |

# Table 130. Logical Instructions (Continued)

| Mnemonic | Operands | Instruction                                       |

|----------|----------|---------------------------------------------------|

| XOR      | dst, src | Logical Exclusive OR                              |

| XORX     | dst, src | Logical Exclusive OR using Extended<br>Addressing |

Table 131. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |