Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 29                                                        |

| Program Memory Size        | 24KB (24K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2421pm020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Option Bits195Overview195Operation195Option Bit Configuration By Reset195Option Bit Address Space195Flash Memory Address 0000H196Flash Memory Address 0001H197On-Chip Debugger199Overview199Architecture199Operation200OCD Interface200OCD Interface200DEBUG Mode201OCD Data Format202OCD Auto-Baud Detector/Generator202OCD Serial Errors203Breakpoints203On-Chip Debugger Commands204On-Chip Debugger Control Register Definitions209OCD Status Register210On-Chip Oscillator211Operating Modes211Cystal Oscillator Operation211Oscillator Operation211Oscillator Operation211Oscillator Operation211Oscillator Operation211Or-Chip Scillator215Absolute Maximum Ratings215DC Characteristics226AC Characteristics226AC Characteristics226AC Characteristics231Con-Chip Peripheral AC and DC Electrical Characteristics236Actionarder Volument Data Sample Timing332                                                                     | Flash Status Register                                                                                                                                                                                                                                                        | 191<br>192                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Operation195Option Bit Configuration By Reset195Option Bit Address Space195Flash Memory Address 0000H196Flash Memory Address 0001H197On-Chip Debugger199Overview199Architecture199Operation200OCD Interface200DEBUG Mode201OCD Data Format202OCD Auto-Baud Detector/Generator203Or-Chip Debugger Commands203On-Chip Debugger Control Register Definitions209OCD Control Register209OCD Status Register211On-Chip Oscillator211Orsystal Scallator Operation211Orsystal Scallator Operation211Orsystal Scallator Operation211Orsystal Scallator Operation211Orschild Active Scallator Operation211Orschild Debration Scallator Operation211Orschild Register211Orschild Register211Orschild Register211Orschild Register211Orschild Register211Orschild Register211Operation Mith an External RC Network213Electrical Characteristics215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231 | Option Bits                                                                                                                                                                                                                                                                  | 195                                                                              |

| Overview199Architecture199Operation200OCD Interface200DEBUG Mode201OCD Data Format202OCD Auto-Baud Detector/Generator202OCD Serial Errors203Breakpoints203On-Chip Debugger Commands204On-Chip Debugger Control Register Definitions209OCD Status Register210On-Chip Oscillator211Overview211Operating Modes211Crystal Oscillator Operation211Oscillator Operation with an External RC Network213Electrical Characteristics215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                          | Operation                                                                                                                                                                                                                                                                    | 195<br>195<br>195<br>196                                                         |

| Architecture199Operation200OCD Interface200DEBUG Mode201OCD Data Format202OCD Auto-Baud Detector/Generator202OCD Serial Errors203Breakpoints203On-Chip Debugger Commands204On-Chip Debugger Control Register Definitions209OCD Status Register210On-Chip Oscillator211Overview211Overview211Cystal Oscillator Operation211Oscillator Operation with an External RC Network213Electrical Characteristics215Absolute Maximum Ratings215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                  | On-Chip Debugger                                                                                                                                                                                                                                                             | 199                                                                              |

| Overview211Operating Modes211Crystal Oscillator Operation211Oscillator Operation with an External RC Network213Electrical Characteristics215Absolute Maximum Ratings215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Architecture    7      Operation    7      OCD Interface    7      DEBUG Mode    7      OCD Data Format    7      OCD Auto-Baud Detector/Generator    7      OCD Serial Errors    7      Breakpoints    7      On-Chip Debugger Commands    7      OCD Control Register    7 | 199<br>200<br>201<br>202<br>202<br>203<br>203<br>203<br>203<br>204<br>209<br>209 |

| Operating Modes211Crystal Oscillator Operation211Oscillator Operation with an External RC Network213Electrical Characteristics215Absolute Maximum Ratings215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | On-Chip Oscillator                                                                                                                                                                                                                                                           | 211                                                                              |

| Absolute Maximum Ratings215DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operating Modes 2   Crystal Oscillator Operation 2                                                                                                                                                                                                                           | 211<br>211                                                                       |

| DC Characteristics217On-Chip Peripheral AC and DC Electrical Characteristics226AC Characteristics231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                              |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DC Characteristics 2   On-Chip Peripheral AC and DC Electrical Characteristics 2                                                                                                                                                                                             | 217<br>226<br>231                                                                |

### xiii

### Braces

The curly braces, { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• Example: The 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most-significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

### Parentheses

The parentheses, (), indicate an indirect register address lookup.

• Example: (R1) is the memory location referenced by the address contained in the Working Register R1.

### **Parentheses/Bracket Combinations**

The parentheses, (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• Example: Assume PC[15:0] contains the value 1234h. (PC[15:0]) then refers to the contents of the memory location at address 1234h.

### Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words reset or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* may not be included; however, it is implied.

### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register [n:n].

• Example: ADDR[15:0] refers to bits 15 through bit 0 of the Address.

### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least* significant byte and most significant byte, respectively. The lowercase forms, *lsb* and *msb*, mean *least* significant bit and most significant bit, respectively.

### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings and conditions in general text.

- Example 1: The receiver forces the SCL line to Low.

- Example 2: The Master can generate a Stop condition to abort the transfer.

Reserved

# zilog

# Stop Mode Recovery Using a GPIO Port Pin Transition HALT

Each of the GPIO Port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery. The GPIO Stop Mode Recovery signals are filtered to reject pulses less than 10 ns (typical) in duration. In the Watchdog Timer Control register, the STOP bit is set to 1.

**Caution:** In STOP mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. Thus, short pulses on the Port pin can initiate Stop Mode Recovery without being written to the Port Input Data register or without initiating an interrupt (if enabled for that pin).

| WDT Reload Value | WDT Reload Value |          | e Time-Out Delay<br>WDT oscillator frequency) |

|------------------|------------------|----------|-----------------------------------------------|

| (Hex)            | (Decimal)        | Typical  | Description                                   |

| 000004           | 4                | 400 μs   | Minimum time-out delay                        |

| FFFFF            | 16,777,215       | 1677.5 s | Maximum time-out delay                        |

### Table 47. Watchdog Timer Approximate Time-Out Delays

### Watchdog Timer Refresh

When first enabled, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer then counts down to 000000H unless a WDT instruction is executed by the eZ8<sup>TM</sup> CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When the 64K Series devices are operating in DEBUG Mode (through the On-Chip Debugger), the Watchdog Timer is continuously refreshed to prevent spurious Watchdog Timer time-outs.

### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a Reset. The WDT\_RES Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Option Bit, see Option Bits on page 195.

### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the 64K Series devices are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 47.

98

# zilog <sub>11</sub>

### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte has been received and is available in the UART Receive Data register. This interrupt can be disabled independent of the other receiver interrupt sources. The received data interrupt occurs once the receive character has been received and placed in the Receive Data register. Software must respond to this received data available condition before the next character is completely received to avoid an overrun error.

**Note:** In MULTIPROCESSOR mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and should be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data register must be read again to clear the error bits is the UART Status 0 register. Updates to the Receive Data register occur only when the next data word is received.

### **UART Data and Error Handling Procedure**

Figure 18 on page 113 displays the recommended procedure for use in UART receiver interrupt service routines.

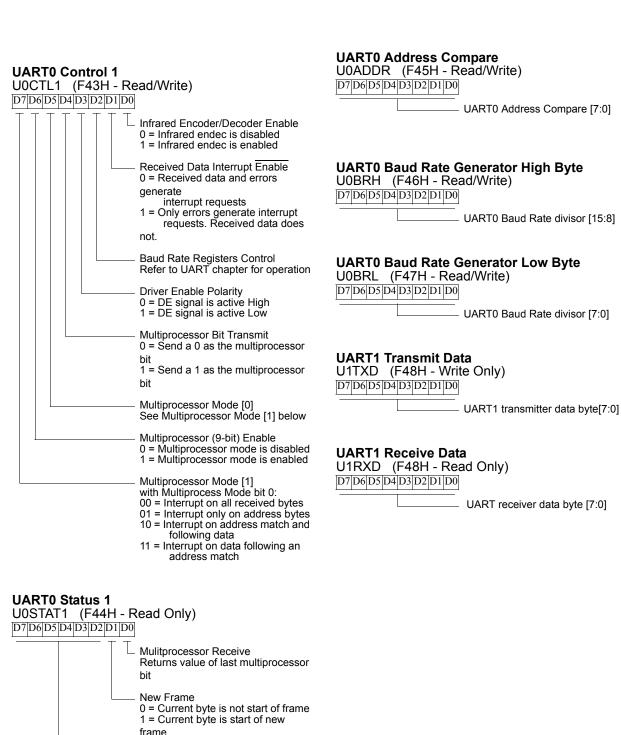

# Table 59. UART Baud Rate High Byte Register (UxBRH)

| BITS  | 7 | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |

|-------|---|-----|---|---------|---------|---|---|---|--|--|--|

| FIELD |   | BRH |   |         |         |   |   |   |  |  |  |

| RESET |   | 1   |   |         |         |   |   |   |  |  |  |

| R/W   |   | R/W |   |         |         |   |   |   |  |  |  |

| ADDR  |   |     |   | F46H ar | nd F4EH |   |   |   |  |  |  |

# Table 60. UART Baud Rate Low Byte Register (UxBRL)

| BITS  | 7 | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|-------|---|-----|---|---------|---------|---|---|---|--|--|

| FIELD |   | BRL |   |         |         |   |   |   |  |  |

| RESET |   | 1   |   |         |         |   |   |   |  |  |

| R/W   |   | R/W |   |         |         |   |   |   |  |  |

| ADDR  |   |     |   | F47H ar | nd F4FH |   |   |   |  |  |

For a given UART data rate, the integer baud rate divisor value is calculated using the following equation:

UART Baud Rate Divisor Value (BRG) =  $Round\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the desired baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 61 provides information on data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

| 9.60 | 23  | 9.73 | 1.32  | <br>9.60 | 12  | 9.60 | 0.00 |

|------|-----|------|-------|----------|-----|------|------|

| 4.80 | 47  | 4.76 | -0.83 | <br>4.80 | 24  | 4.80 | 0.00 |

| 2.40 | 93  | 2.41 | 0.23  | <br>2.40 | 48  | 2.40 | 0.00 |

| 1.20 | 186 | 1.20 | 0.23  | <br>1.20 | 96  | 1.20 | 0.00 |

| 0.60 | 373 | 0.60 | -0.04 | <br>0.60 | 192 | 0.60 | 0.00 |

| 0.30 | 746 | 0.30 | -0.04 | <br>0.30 | 384 | 0.30 | 0.00 |

# Table 61. UART Baud Rates (Continued)

124

# zilog

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

### **SPI Signals**

The four basic SPI signals are:

- Master-In/Slave-Out

- Master-Out/Slave-In

- Serial Clock

- Slave Select

Each signal is described in both Master and Slave modes.

### Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

### Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

### **Serial Clock**

The Serial Clock (SCK) synchronizes data movement both in and out of the device through its MOSI and MISO pins. In MASTER mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted. When configured as a slave, the SPI block requires a minimum SCK period of greater than or equal to 8 times the system (XIN) clock period.

SSIO—Slave Select I/O  $0 = \overline{SS}$  pin configured as an input.  $1 = \overline{SS}$  pin configured as an output (Master mode only). SSV—Slave Select Value If SSIO = 1 and SPI configured as a Master:  $0 = \overline{SS}$  pin driven Low (0).  $1 = \overline{SS}$  pin driven High (1).

# This bit has no effect if SSIO = 0 or SPI configured as a Slave.

## **SPI Diagnostic State Register**

The SPI Diagnostic State register (Table 67) provides observability of internal state. This is a read only register used for SPI diagnostics.

### Table 67. SPI Diagnostic State Register (SPIDST)

| BITS  | 7     | 6     | 5 4 3 2 1 0 |          |    |  |  |  |  |  |

|-------|-------|-------|-------------|----------|----|--|--|--|--|--|

| FIELD | SCKEN | TCKEN |             | SPISTATE |    |  |  |  |  |  |

| RESET |       | 0     |             |          |    |  |  |  |  |  |

| R/W   |       | R     |             |          |    |  |  |  |  |  |

| ADDR  |       |       |             | F6       | 4H |  |  |  |  |  |

SCKEN—Shift Clock Enable

- 0 = The internal Shift Clock Enable signal is deasserted

- 1 = The internal Shift Clock Enable signal is asserted (shift register is updates on next system clock)

TCKEN—Transmit Clock Enable

- 0 = The internal Transmit Clock Enable signal is deasserted.

- 1 = The internal Transmit Clock Enable signal is asserted. When this is asserted the serial data out is updated on the next system clock (MOSI or MISO).

SPISTATE—SPI State Machine

Defines the current state of the internal SPI State Machine.

# Table 74. I<sup>2</sup>C Baud Rate Low Byte Register (I2CBRL)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|--|

| FIELD |   | BRL |   |    |    |   |   |   |  |  |  |

| RESET |   | FFH |   |    |    |   |   |   |  |  |  |

| R/W   |   | R/W |   |    |    |   |   |   |  |  |  |

| ADDR  |   |     |   | F5 | 4H |   |   |   |  |  |  |

BRL =  $I^2C$  Baud Rate Low Byte

Least significant byte, BRG[7:0], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRL register returns the current value of the  $I^2C$  Baud Rate Counter[7:0].

# I<sup>2</sup>C Diagnostic State Register

The I<sup>2</sup>C Diagnostic State register (Table 75) provides observability of internal state. This is a read only register used for I<sup>2</sup>C diagnostics and manufacturing test.

| BITS  | 7     | 6     | 5      | 4         | 4 3 2 1 0 |  |  |  |  |  |

|-------|-------|-------|--------|-----------|-----------|--|--|--|--|--|

| FIELD | SCLIN | SDAIN | STPCNT | TXRXSTATE |           |  |  |  |  |  |

| RESET | >     | K     | 0      |           |           |  |  |  |  |  |

| R/W   |       | R     |        |           |           |  |  |  |  |  |

| ADDR  |       |       |        | F5        | 5H        |  |  |  |  |  |

Table 75. I<sup>2</sup>C Diagnostic State Register (I2CDST)

SCLIN—Value of Serial Clock input signal

SDAIN—Value of the Serial Data input signal

STPCNT—Value of the internal Stop Count control signal

TXRXSTATE—Value of the internal I<sup>2</sup>C state machine

169

DMAx\_IO[7:0]}. When the DMA is configured for two-byte word transfers, the DMAx I/O Address register must contain an even numbered address.

Table 78. DMAx I/O Address Register (DMAxIO)

| BITS  | 7 | 6      | 5 | 4     | 3    | 2 | 1 | 0 |  |  |

|-------|---|--------|---|-------|------|---|---|---|--|--|

| FIELD |   | DMA_IO |   |       |      |   |   |   |  |  |

| RESET |   | X      |   |       |      |   |   |   |  |  |

| R/W   |   | R/W    |   |       |      |   |   |   |  |  |

| ADDR  |   |        |   | FB1H, | FB9H |   |   |   |  |  |

DMA\_IO—DMA on-chip peripheral control register address This byte sets the low byte of the on-chip peripheral control register address on Register File Page FH (addresses F00H to FFFH).

# DMAx Address High Nibble Register

The DMAx Address High register (Table 79) specifies the upper four bits of address for the Start/Current and End Addresses of DMAx.

| BITS  | 7                     | 6   | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |

|-------|-----------------------|-----|---|-------|------|---|---|---|--|--|--|

| FIELD | DMA_END_H DMA_START_H |     |   |       |      |   |   |   |  |  |  |

| RESET |                       | x   |   |       |      |   |   |   |  |  |  |

| R/W   |                       | R/W |   |       |      |   |   |   |  |  |  |

| ADDR  |                       |     |   | FB2H, | FBAH |   |   |   |  |  |  |

DMA\_END\_H—DMAx End Address High Nibble

These bits, used with the DMAx End Address Low register, form a 12-bit End Address. The full 12-bit address is given by {DMA\_END\_H[3:0], DMA\_END[7:0]}.

DMA\_START\_H—DMAx Start/Current Address High Nibble These bits, used with the DMAx Start/Current Address Low register, form a 12-bit Start/Current Address. The full 12-bit address is given by {DMA\_START\_H[3:0], DMA\_START[7:0]}.

- 0 = DMA0 is not the source of the interrupt from the DMA Controller.

- 1 = DMA0 completed transfer of data to/from the End Address and generated an interrupt.

# **ADC Control Register Definitions**

# **ADC Control Register**

The ADC Control register selects the analog input channel and initiates the analog-to-digital conversion.

Table 86. ADC Control Register (ADCCTL)

| BITS  | 7    | 6        | 5    | 4    | 3          | 2 | 1 | 0 |

|-------|------|----------|------|------|------------|---|---|---|

| FIELD | CEN  | Reserved | VREF | CONT | ANAIN[3:0] |   |   |   |

| RESET | (    | )        | 1    |      | 0          |   |   |   |

| R/W   | R/W  |          |      |      |            |   |   |   |

| ADDR  | F70H |          |      |      |            |   |   |   |

### CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion has been completed.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

### Reserved—Must be 0.

VREF

0 = Internal voltage reference generator enabled. The VREF pin should be left unconnected (or capacitively coupled to analog ground) if the internal voltage reference is selected as the ADC reference voltage.

1 = Internal voltage reference generator disabled. An external voltage reference must be provided through the VREF pin.

### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.

1 = Continuous conversion. ADC data updated every 256 system clock cycles.

# ANAIN—Analog Input Select

These bits select the analog input for conversion. Not all Port pins in this list are available in all packages for the Z8F642x family Z8R642x family of products. For information on the Port pins available with each package style, see Signal and Pin Descriptions on page 7. Do not enable unavailable analog inputs.

0000 = ANA0 0001 = ANA1 0010 = ANA2 0011 = ANA3

Reserved These bits are reserved and must be 0.

FSTAT—Flash Controller Status

$00_{0000} =$ Flash Controller locked

00\_0001 = First unlock command received

$00_{010} =$  Second unlock command received

00\_0011 = Flash Controller unlocked

00\_0100 = Flash Sector Protect register selected

00\_1xxx = Program operation in progress

01\_0xxx = Page erase operation in progress

10\_0xxx = Mass erase operation in progress

# Page Select Register

The Page Select (FPS) register (Table 94) selects one of the 128 available Flash memory pages to be erased or programmed. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory locations with the 7 most significant bits of the address given by the PAGE field are erased to FFH.

The Page Select register shares its Register File address with the Flash Sector Protect Register. The Page Select register cannot be accessed when the Flash Sector Protect register is enabled.

| BITS  | 7       | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|------|---|---|---|---|---|---|

| FIELD | INFO_EN | PAGE |   |   |   |   |   |   |

| RESET | 0       |      |   |   |   |   |   |   |

| R/W   | R/W     |      |   |   |   |   |   |   |

| ADDR  | FF9H    |      |   |   |   |   |   |   |

Table 94. Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area is not selected.

1 = Information Area is selected. The Information area is mapped into the Flash Memory address space at addresses FE00H through FFFFH.

PAGE—Page Select

This 7-bit field selects the Flash memory page for Programming and Page Erase operations. Flash Memory Address[15:9] = PAGE[6:0].

# **Oscillator Operation with an External RC Network**

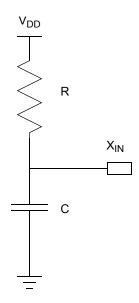

The External RC oscillator mode is applicable to timing insensitive applications. Figure 41 displays a recommended configuration for connection with an external resistorcapacitor (RC) network.

### Figure 41. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of 45 k $\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the following equation:

Oscillator Frequency (kHz) =  $\frac{1 \times 10^6}{(0.4 \times R \times C) + (4 \times C)}$

Figure 42 displays the typical (3.3 V and 25 °C) oscillator frequency as a function of the capacitor (*C* in pF) employed in the RC network assuming a 45 k $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator XIN pin and the printed circuit board should be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20 pF are recommended.

### 7

# **DC Characteristics**

Table 106 lists the DC characteristics of the 64K Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

# Table 106. DC Characteristics

|                  |                                             | T <sub>A</sub> = –40 °C to 125 °C |                     |                      |       |                                                                                          |  |

|------------------|---------------------------------------------|-----------------------------------|---------------------|----------------------|-------|------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                   | Minimum                           | num Typical Maximum |                      | Units | Conditions                                                                               |  |

| V <sub>DD</sub>  | Supply Voltage                              | 3.0                               | _                   | 3.6                  | V     |                                                                                          |  |

| V <sub>IL1</sub> | Low Level Input Voltage                     | -0.3                              | -                   | 0.3*V <sub>DD</sub>  | V     | For all input pins except RESET, DBG, XIN                                                |  |

| V <sub>IL2</sub> | Low Level Input Voltage                     | -0.3                              | -                   | 0.2*V <sub>DD</sub>  | V     | For $\overline{\text{RESET}}$ , DBG, and XIN.                                            |  |

| V <sub>IH1</sub> | High Level Input Voltage                    | 0.7*V <sub>DD</sub>               | -                   | 5.5                  | V     | Port A, C, D, E, F, and G pins.                                                          |  |

| V <sub>IH2</sub> | High Level Input Voltage                    | 0.7*V <sub>DD</sub>               | -                   | V <sub>DD</sub> +0.3 | V     | Port B and H pins.                                                                       |  |

| V <sub>IH3</sub> | High Level Input Voltage                    | 0.8*V <sub>DD</sub>               | -                   | V <sub>DD</sub> +0.3 | V     | RESET, DBG, and XIN pins                                                                 |  |

| V <sub>OL1</sub> | Low Level Output<br>Voltage Standard Drive  | -                                 | -                   | 0.4                  | V     | I <sub>OL</sub> = 2 mA; VDD = 3.0 V<br>High Output Drive disabled.                       |  |

| V <sub>OH1</sub> | High Level Output<br>Voltage Standard Drive | 2.4                               | -                   | -                    | V     | I <sub>OH</sub> = -2 mA; VDD = 3.0 V<br>High Output Drive disabled.                      |  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage High Drive      | -                                 | -                   | 0.6                  | V     | $I_{OL}$ = 20 mA; VDD = 3.3 V<br>High Output Drive enabled<br>$T_A$ = -40 °C to +70 °C   |  |

| V <sub>OH2</sub> | High Level Output<br>Voltage<br>High Drive  | 2.4                               | _                   | _                    | V     | $I_{OH}$ = -20 mA; VDD = 3.3 V<br>High Output Drive enabled;<br>$T_A$ = -40 °C to +70 °C |  |

| V <sub>OL3</sub> | Low Level Output<br>Voltage<br>High Drive   | -                                 | _                   | 0.6                  | V     | $I_{OL}$ = 15 mA; VDD = 3.3 V<br>High Output Drive enabled;<br>$T_A$ = +70 °C to +105 °C |  |

| V <sub>OH3</sub> | High Level Output<br>Voltage<br>High Drive  | 2.4                               | _                   | _                    | V     | $I_{OH}$ = 15 mA; VDD = 3.3 V<br>High Output Drive enabled;<br>$T_A$ = +70 °C to +105 °C |  |

| V <sub>RAM</sub> | RAM Data Retention                          | 0.7                               | -                   | -                    | V     |                                                                                          |  |

| I <sub>IL</sub>  | Input Leakage Current                       | -5                                | -                   | +5                   | μA    | V <sub>DD</sub> = 3.6 V;<br>V <sub>IN</sub> = VDD or VSS <sup>1</sup>                    |  |

| I <sub>TL</sub>  | Tri-State Leakage<br>Current                | -5                                | -                   | +5                   | μA    | V <sub>DD</sub> = 3.6 V                                                                  |  |

zilog 224

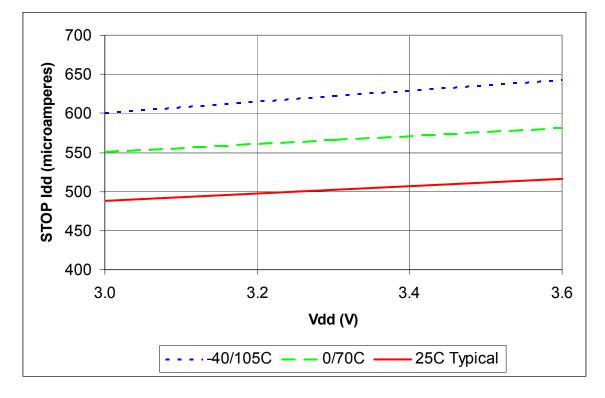

Figure 47 displays the maximum current consumption in STOP mode with the VBO and Watchdog Timer enabled versus the power supply voltage. All GPIO pins are configured as outputs and driven High.

# Figure 47. Maximum STOP Mode Idd with VBO enabled versus Power Supply Voltage

# General-Purpose I/O Port Input Data Sample Timing

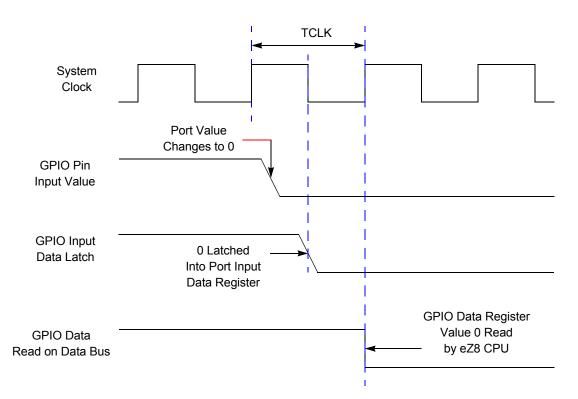

Figure 50 displays timing of the GPIO Port input sampling. Table 114 lists the GPIO port input timing.

# Figure 50. Port Input Sample Timing

# Table 114. GPIO Port Input Timing

|                     |                                                                                                          | Delay (ns) |     |  |

|---------------------|----------------------------------------------------------------------------------------------------------|------------|-----|--|

| Parameter           | Abbreviation                                                                                             | Min        | Max |  |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Fall Setup Time (Not pictured)                                              | 5          | -   |  |

| T <sub>H_PORT</sub> | XIN Fall to Port Input Transition Hold Time (Not pictured)                                               | 6          | -   |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to Insure Stop Mode<br>Recovery<br>(for GPIO Port Pins enabled as SMR sources) | 1 μs       |     |  |

zilog

# UART Timing

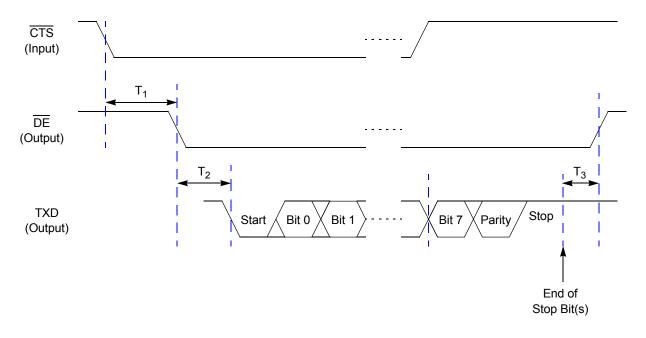

Figure 56 and Table 120 provide timing information for UART pins for the case where the Clear To Send input pin ( $\overline{\text{CTS}}$ ) is used for flow control. In this example, it is assumed that the Driver Enable polarity has been configured to be Active Low and is represented here by  $\overline{\text{DE}}$ . The  $\overline{\text{CTS}}$  to  $\overline{\text{DE}}$  assertion delay (T1) assumes the UART Transmit Data register has been loaded with data prior to  $\overline{\text{CTS}}$  assertion.

# Figure 56. UART Timing with CTS

# Table 120. UART Timing with CTS

|                |                                                                | Delay (ns)     |                                  |  |

|----------------|----------------------------------------------------------------|----------------|----------------------------------|--|

| Paramet        | er Abbreviation                                                | Minimum        | Maximum                          |  |

| T <sub>1</sub> | CTS Fall to DE Assertion Delay                                 | 2 * XIN period | 2 * XIN period<br>+ 1 Bit period |  |

| T <sub>2</sub> | DE Assertion to TXD Falling Edge (Start)<br>Delay              | 1 Bit period   | 1 Bit period +<br>1 * XIN period |  |

| T <sub>3</sub> | End of Stop Bit(s) to $\overline{\text{DE}}$ Deassertion Delay | 1 * XIN period | 2 * XIN period                   |  |