Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 31                                                            |

| Program Memory Size        | 24KB (24K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 2K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 44-LCC (J-Lead)                                               |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2421vn020ec00tr |

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers **Product Specification**

| ı | L | U | y | i |

|---|---|---|---|---|

|   |   |   |   |   |

| DMA_ADC Operation                            | 166 |

|----------------------------------------------|-----|

| Configuring DMA_ADC for Data Transfer        | 167 |

| DMA Control Register Definitions             | 167 |

| DMAx Control Register                        | 167 |

| DMAx I/O Address Register                    | 168 |

| DMAx Address High Nibble Register            | 169 |

| DMAx Start/Current Address Low Byte Register | 170 |

| DMAx End Address Low Byte Register           |     |

| DMA_ADC Address Register                     | 171 |

| DMA_ADC Control Register                     | 172 |

| DMA Status Register                          | 173 |

| Analog-to-Digital Converter                  | 176 |

|                                              |     |

| Overview                                     |     |

| Architecture                                 |     |

| Operation                                    |     |

| Automatic Power-Down                         |     |

| Single-Shot Conversion                       |     |

| Continuous Conversion                        |     |

| DMA Control of the ADC                       |     |

| ADC Control Register Definitions             |     |

| ADC Control Register                         |     |

| ADC Data High Byte Register                  |     |

| ADC Data Low Bits Register                   | 180 |

| Flash Memory                                 | 183 |

| Overview                                     | 183 |

| Information Area                             |     |

| Operation                                    |     |

| Timing Using the Flash Frequency Registers   |     |

| Flash Read Protection                        |     |

| Flash Write/Erase Protection                 |     |

| Byte Programming                             | 187 |

| Page Erase                                   | 188 |

| Mass Erase                                   | 189 |

| Flash Controller Bypass                      | 189 |

| Flash Controller Behavior in Debug Mode      | 189 |

| Flash Control Register Definitions           | 190 |

| Flash Control Register                       | 190 |

|                                              |     |

PS019919-1207 **Table of Contents**

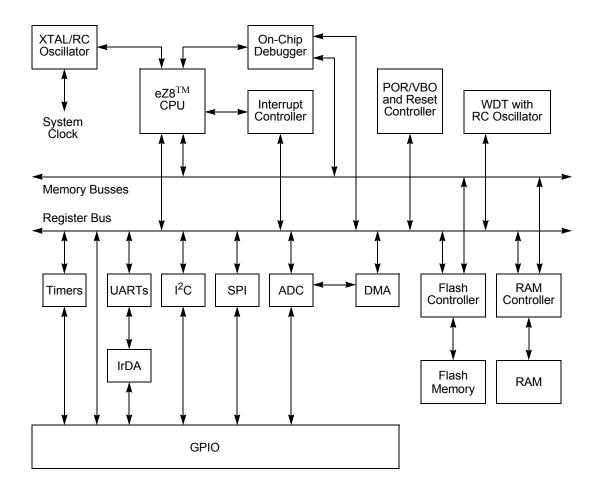

# **Block Diagram**

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP 64K Series Flash Microcontrollers.

Figure 1. Z8 Encore! XP 64K Series Flash Microcontrollers Block Diagram

# **CPU and Peripheral Overview**

# eZ8<sup>™</sup> CPU Features

The latest 8-bit eZ8 CPU meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8<sup>®</sup> instruction set.

PS019919-1207 Introduction

**Interrupt Request 2 IRQ0 Enable Low Bit** IRQ2 (FC6H - Read/Write) IRQ0ENL (FC2H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 Port C Pin Interrupt Request ADC IRQ Enable Hit Bit 0 = IRQ from corresponding pin [3:0] is not pending SPI IRQ Enable Low Bit 1 = IRQ from corresponding pin [3:0] is awaiting service I2C IRQ Enable Low Bit **DMA Interrupt Request UART 0 Transmitter IRQ Enable UART 1 Transmitter Interrupt** UART 0 Receiver IRQ Enable Low **UART 1 Receiver Interrupt Request** Timer 0 IRQ Enable Low Bit Timer 3 Interrupt Request Timer 1 IRQ Enable Low Bit For all of the above peripherals: Timer 2 IRQ Enable Low Bit 0 = Peripheral IRQ is not pending 1 = Peripheral IRQ is awaiting service **Interrupt Request 1** IRQ1 (FC3H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 IRQ2 Enable High Bit IRQ2ENH (FC7H - Read/Write) Port A or D Pin Interrupt Request D7 D6 D5 D4 D3 D2 D1 D0 0 = IRQ from corresponding pin [7:0] is not pending 1 = IRQ from corresponding pin [7:0] Port C Pin IRQ Enable High Bit is awaiting service DMA IRQ Enable High Bit **UART 1 Transmitter IRQ Enable** IRQ1 Enable High Bit UART 1 Receiver IRQ Enable High IRQ1ENH (FC4H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Timer 3 IRQ Enable High Bit Port A or D Pin IRQ Enable High Bit **IRQ2 Enable Low Bit** IRQ2ENL (FC8H - Read/Write) **IRQ1 Enable Low Bit** D7 D6 D5 D4 D3 D2 D1 D0 IRQ1ENL (FC5H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Port C Pin IRQ Enable Low Bit Port A or D Pin IRQ Enable Low Bit DMA IRQ Enable Low Bit **UART 1 Transmitter IRQ Enable** UART 1 Receiver IRQ Enable Low Timer 3 IRQ Enable Low Bit

> Interrupt Edge Select IRQES (FCDH - Read/Write)

D7 D6 D5 D4 D3 D2 D1 D0

Port A or D Interrupt Edge Select

0 = Falling edge 1 = Rising edge

zilog

| gisters:<br>tion<br>(open-drain)<br>ble<br>covery enable<br>on |

|----------------------------------------------------------------|

|                                                                |

| ort Sub-                                                       |

|                                                                |

|                                                                |

| o]<br>7:0]                                                     |

|                                                                |

| gisters:<br>tion<br>(open-drain)<br>ble<br>covery enable<br>on |

|                                                                |

|                                                                |

|                                                                |

**Flags** FLAGS (FFC - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 F1 - User Flag 1 F2 - User Flag 2 H - Half Carry D - Decimal Adjust V - Overflow Flag S - Sign Flag Z - Zero Flag C - Carry Flag Register Pointer

RP (FFDH - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Working Register Page Address Working Register Group Address Stack Pointer High Byte SPH (FFEH - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Stack Pointer [15:8] Stack Pointer Low Byte SPL (FFFH - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0

Stack Pointer [7:0]

110 = Divide by 64

111 = Divide by 128

TMODE—TIMER mode

000 = ONE-SHOT mode

001 = CONTINUOUS mode

010 = COUNTER mode

$011 = PWM \mod e$

100 = CAPTURE mode

101 = COMPARE mode

$110 = GATED \mod e$

111 = CAPTURE/COMPARE mode

PS019919-1207 Timers

**Caution:** *The 24-bit WDT Reload Value must not be set to a value less than* 000004H.

## Table 49. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS      | 7                                                                                           | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|---------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|

| FIELD     |                                                                                             | WDTU |   |   |   |   |   |   |

| RESET     | 1                                                                                           |      |   |   |   |   |   |   |

| R/W       | R/W*                                                                                        |      |   |   |   |   |   |   |

| ADDR      | ADDR FF1H                                                                                   |      |   |   |   |   |   |   |

| Note: R/W | Note: R/W* - Read returns the current WDT count value. Write sets the desired Reload Value. |      |   |   |   |   |   |   |

WDTU—WDT Reload Upper Byte Most significant byte, Bits[23:16], of the 24-bit WDT reload value.

## Table 50. Watchdog Timer Reload High Byte Register (WDTH)

| BITS      | 7                                                                                           | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|---------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|

| FIELD     |                                                                                             | WDTH |   |   |   |   |   |   |

| RESET     |                                                                                             | 1    |   |   |   |   |   |   |

| R/W       | R/W*                                                                                        |      |   |   |   |   |   |   |

| ADDR      | FF2H                                                                                        |      |   |   |   |   |   |   |

| Note: R/W | Note: R/W* - Read returns the current WDT count value. Write sets the desired Reload Value. |      |   |   |   |   |   |   |

WDTH—WDT Reload High Byte Middle byte, Bits[15:8], of the 24-bit WDT reload value.

## Table 51. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS                                                                                        | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------------------------------------------------------------------------------------------|------|------|---|---|---|---|---|---|--|

| FIELD                                                                                       |      | WDTL |   |   |   |   |   |   |  |

| RESET                                                                                       |      | 1    |   |   |   |   |   |   |  |

| R/W                                                                                         | R/W* |      |   |   |   |   |   |   |  |

| ADDR                                                                                        | FF3H |      |   |   |   |   |   |   |  |

| Note: R/W* - Read returns the current WDT count value. Write sets the desired Reload Value. |      |      |   |   |   |   |   |   |  |

WDTL-WDT Reload Low

Least significant byte, Bits[7:0], of the 24-bit WDT reload value.

PS019919-1207 Watchdog Timer

118

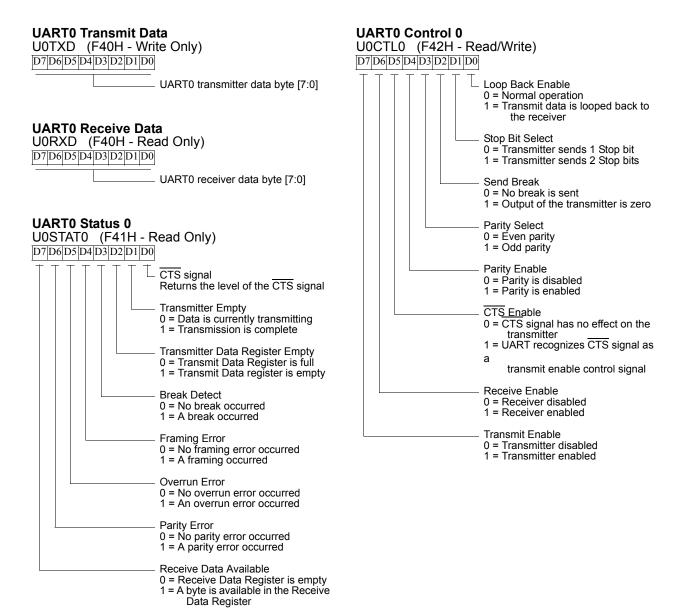

REN—Receive Enable

This bit enables or disables the receiver.

0 =Receiver disabled.

1 = Receiver enabled.

#### CTSE—CTS Enable

$0 = \text{The } \overline{\text{CTS}}$  signal has no effect on the transmitter.

$1 = \text{The UART recognizes the } \overline{\text{CTS}}$  signal as an enable control from the transmitter.

#### PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit. It is over-ridden by the MPEN bit.

0 = Parity is disabled.

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.

#### PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data.

1 = Odd parity is transmitted and expected on all received data.

#### SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.

0 = No break is sent.

1 =The output of the transmitter is zero.

#### STOP—Stop Bit Select

0 = The transmitter sends one stop bit.

1 = The transmitter sends two stop bits.

#### LBEN—Loop Back Enable

0 = Normal operation.

1 = All transmitted data is looped back to the receiver.

## Table 57. UART Control 1 Register (UxCTL1)

| BITS  | 7       | 6             | 5       | 4    | 3     | 2      | 1      | 0    |

|-------|---------|---------------|---------|------|-------|--------|--------|------|

| FIELD | MPMD[1] | MPEN          | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |

| RESET | 0       |               |         |      |       |        |        |      |

| R/W   | R/W     |               |         |      |       |        |        |      |

| ADDR  |         | F43H and F4BH |         |      |       |        |        |      |

MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address).

PS019919-1207 UART

## Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver via the TXD pin. Likewise, data received from the infrared transceiver is passed to the Infrared Endec via the RXD pin, decoded by the Infrared Endec, and then passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 Kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

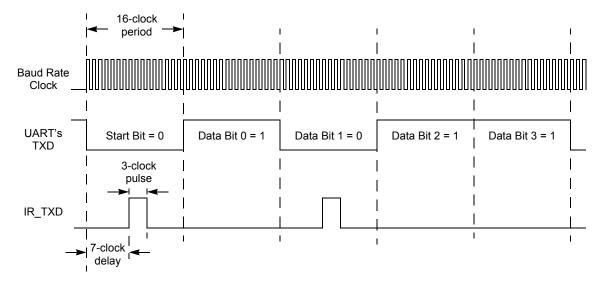

## **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clock wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 20 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the 64K Series products while the IR TXD signal is output through the TXD pin.

Figure 20. Infrared Data Transmission

PS019919-1207 Infrared Encoder/Decoder

# **Serial Peripheral Interface**

## **Overview**

The Serial Peripheral Interface is a synchronous interface allowing several SPI-type devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- Full-duplex, synchronous, character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-half the system clock frequency

- Error detection

- Dedicated Baud Rate Generator

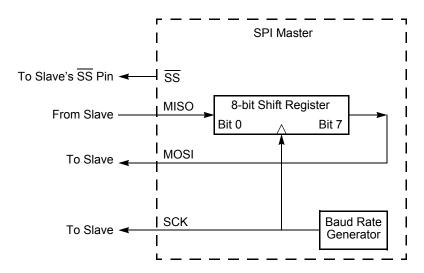

## **Architecture**

The SPI may be configured as either a Master (in single or multi-master systems) or a Slave as displayed in Figure 22 through Figure 24.

Figure 22. SPI Configured as a Master in a Single Master, Single Slave System

## IEN—I<sup>2</sup>C Enable

$1 = \text{The } I^2C$  transmitter and receiver are enabled.

$0 = \text{The I}^2\text{C}$  transmitter and receiver are disabled.

#### START—Send Start Condition

This bit sends the Start condition. Once asserted, it is cleared by the I<sup>2</sup>C Controller after it sends the START condition or if the IEN bit is deasserted. If this bit is 1, it cannot be cleared to 0 by writing to the register. After this bit is set, the Start condition is sent if there is data in the I<sup>2</sup>C Data or I<sup>2</sup>C Shift register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until the Data register is written. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a START condition after the byte shifts and the acknowledge phase completes. If the STOP bit is also set, it also waits until the STOP condition is sent before the sending the START condition.

#### STOP—Send Stop Condition

This bit causes the I<sup>2</sup>C Controller to issue a Stop condition after the byte in the I<sup>2</sup>C Shift register has completed transmission or after a byte has been received in a receive operation. Once set, this bit is reset by the I<sup>2</sup>C Controller after a Stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by writing to the register.

#### BIRQ—Baud Rate Generator Interrupt Request

This bit allows the I<sup>2</sup>C Controller to be used as an additional timer when the I<sup>2</sup>C Controller is disabled. This bit is ignored when the I<sup>2</sup>C Controller is enabled.

1 = An interrupt occurs every time the baud rate generator counts down to one.

0 = No band rate generator interrupt occurs.

#### TXI—Enable TDRE interrupts

This bit enables the transmit interrupt when the  $I^2C$  Data register is empty (TDRE = 1).

- 1 = Transmit interrupt (and DMA transmit request) is enabled.

- 0 = Transmit interrupt (and DMA transmit request) is disabled.

#### NAK—Send NAK

This bit sends a Not Acknowledge condition after the next byte of data has been read from the I<sup>2</sup>C slave. Once asserted, it is deasserted after a Not Acknowledge is sent or the IEN bit is deasserted. If this bit is 1, it cannot be cleared to 0 by writing to the register.

#### FLUSH—Flush Data

Setting this bit to 1 clears the I<sup>2</sup>C Data register and sets the TDRE bit to 1. This bit allows flushing of the I<sup>2</sup>C Data register when a Not Acknowledge interrupt is received after the data has been sent to the I<sup>2</sup>C Data register. Reading this bit always returns 0.

## FILTEN—I<sup>2</sup>C Signal Filter Enable

This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.

- 1 = low-pass filters are enabled.

- 0 = low-pass filters are disabled.

PS019919-1207 I2C Controller

# Table 88. ADC Data Low Bits Register (ADCD\_L)

| BITS  | 7   | 6      | 5 | 4        | 3 | 2 | 1 | 0 |

|-------|-----|--------|---|----------|---|---|---|---|

| FIELD | ADC | ADCD_L |   | Reserved |   |   |   |   |

| RESET |     | X      |   |          |   |   |   |   |

| R/W   |     | R      |   |          |   |   |   |   |

| ADDR  |     | F73H   |   |          |   |   |   |   |

ADCD\_L—ADC Data Low Bits

These are the least significant two bits of the 10-bit ADC output. These bits are undefined after a Reset.

#### Reserved

These bits are reserved and are always undefined.

185

### **Information Area**

Table 91 describes the 64K Series Information Area. This 512-byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into Flash Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, LDC instructions return data from the Information Area. CPU instruction fetches always comes from Flash Memory regardless of the Information Area access bit. Access to the Information Area is readonly.

Table 91. Z8 Encore! XP 64K Series Flash Microcontrollers Information Area Map

| Flash Memory Address (Hex) | Function                                                                                    |

|----------------------------|---------------------------------------------------------------------------------------------|

| FE00H-FE3FH                | Reserved                                                                                    |

| FE40H-FE53H                | Part Number<br>20-character ASCII alphanumeric code<br>Left justified and filled with zeros |

| FE54H-FFFFH                | Reserved                                                                                    |

# **Operation**

The Flash Controller provides the proper signals and timing for Byte Programming, Page Erase, and Mass Erase of the Flash memory. The Flash Controller contains a protection mechanism, via the Flash Control register (FCTL), to prevent accidental programming or erasure. The following subsections provide details on the various operations (Lock, Unlock, Sector Protect, Byte Programming, Page Erase, and Mass Erase).

PS019919-1207 Flash Memory

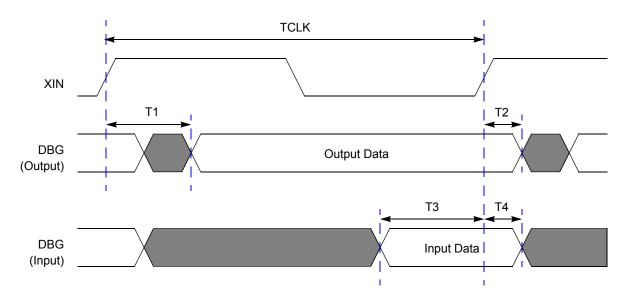

# **On-Chip Debugger Timing**

Figure 52 and Table 116 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 µs maximum rise and fall time.

Figure 52. On-Chip Debugger Timing

Table 116. On-Chip Debugger Timing

|                |                                  | Delay (ns) |                |  |  |

|----------------|----------------------------------|------------|----------------|--|--|

| Parameter      | Abbreviation                     | Minimum    | Maximum        |  |  |

| DBG            |                                  |            |                |  |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | _          | 30             |  |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | _              |  |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 10         | _              |  |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _              |  |  |

|                | DBG frequency                    |            | System Clock/4 |  |  |

PS019919-1207 Electrical Characteristics

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

zilog

240

PS019919-1207 Electrical Characteristics

Table 125 through Table 132 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

**Table 125. Arithmetic Instructions**

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| СР       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| CPX      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

**Table 126. Bit Manipulation Instructions**

| Mnemonic | Operands    | Instruction      |

|----------|-------------|------------------|

| BCLR     | bit, dst    | Bit Clear        |

| BIT      | p, bit, dst | Bit Set or Clear |

| BSET     | bit, dst    | Bit Set          |

PS019919-1207 eZ8<sup>™</sup> CPU Instruction Set

Table 133. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                                  | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   |   | - Fetch | Instr. |

|---------------|----------------------------------|-----------------|-----|-------------|-------|---|---|---|---|---|---------|--------|

| Mnemonic      | Symbolic Operation               | dst             | src | (Hex)       | С     | Z | S | ٧ | D | Н |         | Cycles |

| RRC dst       | D7D6D5D4D3D2D1D0 → C — dst       | R               |     | C0          | *     | * | * | * | - | - | 2       | 2      |

|               |                                  | IR              |     | C1          | -     |   |   |   |   |   | 2       | 3      |

| SBC dst, src  | $dst \leftarrow dst - src - C$   | r               | r   | 32          | *     | * | * | * | 1 | * | 2       | 3      |

|               | _                                | r               | lr  | 33          | •     |   |   |   |   |   | 2       | 4      |

|               | <del>-</del>                     | R               | R   | 34          | •     |   |   |   |   |   | 3       | 3      |

|               | <del>-</del>                     | R               | IR  | 35          | •     |   |   |   |   |   | 3       | 4      |

|               | <del>-</del>                     | R               | IM  | 36          | •     |   |   |   |   |   | 3       | 3      |

|               | <del>-</del>                     | IR              | IM  | 37          | •     |   |   |   |   |   | 3       | 4      |

| SBCX dst, src | : dst ← dst – src - C            | ER              | ER  | 38          | *     | * | * | * | 1 | * | 4       | 3      |

|               | _                                | ER              | IM  | 39          | •     |   |   |   |   |   | 4       | 3      |

| SCF           | C ← 1                            |                 |     | DF          | 1     | - | - | - | - | - | 1       | 2      |

| SRA dst       |                                  | R               |     | D0          | *     | * | * | 0 | - | - | 2       | 2      |

|               | D7 D6 D5 D4 D3 D2 D1 D0  → C dst | IR              |     | D1          |       |   |   |   |   |   | 2       | 3      |

| SRL dst       | ) → D7 D6 D5 D4 D3 D2 D1 D0 → C  | R               |     | 1F C0       | *     | * | 0 | * | - | - | 3       | 2      |

|               | dst                              | IR              |     | 1F C1       | •     |   |   |   |   |   | 3       | 3      |

| SRP src       | RP ← src                         |                 | IM  | 01          | -     | - | - | - | - | - | 2       | 2      |

| STOP          | STOP Mode                        |                 |     | 6F          | -     | - | - | - | - | - | 1       | 2      |

| SUB dst, src  | dst ← dst – src                  | r               | r   | 22          | *     | * | * | * | 1 | * | 2       | 3      |

|               | _                                | r               | lr  | 23          | •     |   |   |   |   |   | 2       | 4      |

|               | _                                | R               | R   | 24          | •     |   |   |   |   |   | 3       | 3      |

|               | _                                | R               | IR  | 25          | •     |   |   |   |   |   | 3       | 4      |

|               | <del>-</del>                     | R               | IM  | 26          | •     |   |   |   |   |   | 3       | 3      |

|               | <del>-</del>                     | IR              | IM  | 27          | •     |   |   |   |   |   | 3       | 4      |

| SUBX dst, src | : dst ← dst – src                | ER              | ER  | 28          | *     | * | * | * | 1 | * | 4       | 3      |

|               | <del>-</del>                     | ER              | IM  | 29          |       |   |   |   |   |   | 4       | 3      |

PS019919-1207 eZ8<sup>™</sup> CPU Instruction Set

# Index

# **Symbols**

# 244

% 244

@ 244

## **Numerics**

10-bit ADC 4

40-lead plastic dual-inline package 265

44-lead low-profile quad flat package 266

44-lead plastic lead chip carrier package 267

64-lead low-profile quad flat package 267

68-lead plastic lead chip carrier package 268

80-lead quad flat package 269

# Α

absolute maximum ratings 215

AC characteristics 231

ADC 246

architecture 175

automatic power-down 176

block diagram 176

continuous conversion 177

control register 179

control register definitions 179

data high byte register 180

data low bits register 180

DMA control 178

electrical characteristics and timing 229

operation 176

single-shot conversion 177

ADCCTL register 179

ADCDH register 180

ADCDL register 180

ADCX 246

**ADD 246**

add - extended addressing 246

add with carry 246

add with carry - extended addressing 246

additional symbols 244

address space 19

**ADDX 246**

analog signals 15

analog-to-digital converter (ADC) 175

AND 248

ANDX 248

arithmetic instructions 246

assembly language programming 241

assembly language syntax 242

## В

B 244

b 243

baud rate generator, UART 113

**BCLR 246**

binary number suffix 244

BIT 246

bit 243

clear 246

manipulation instructions 246

set 246

set or clear 246

swap 247

test and jump 249

test and jump if non-zero 249

test and jump if zero 249

bit jump and test if non-zero 249

bit swap 249

block diagram 3

block transfer instructions 247

**BRK 249**

**BSET 246**

BSWAP 247, 249

BTJ 249

BTJNZ 249

**BTJZ 249**

#### C

CALL procedure 249 capture mode 95

capture/compare mode 95

PS019919-1207 Index

| Operational Description 103<br>OR 248               | push using extended addressing 248<br>PUSHX 248 |  |  |  |  |  |  |  |

|-----------------------------------------------------|-------------------------------------------------|--|--|--|--|--|--|--|

|                                                     |                                                 |  |  |  |  |  |  |  |

| ordering information 270                            | PWM mode 94                                     |  |  |  |  |  |  |  |

| ORX 248                                             | PxADDR register 61                              |  |  |  |  |  |  |  |

| oscillator signals 15                               | PxCTL register 62                               |  |  |  |  |  |  |  |

| P                                                   | Q                                               |  |  |  |  |  |  |  |

| p 243                                               | QFP 269                                         |  |  |  |  |  |  |  |

| packaging                                           |                                                 |  |  |  |  |  |  |  |

| LQFP                                                |                                                 |  |  |  |  |  |  |  |

| 44 lead 266                                         | R                                               |  |  |  |  |  |  |  |

| 64 lead 267                                         | R 243                                           |  |  |  |  |  |  |  |

| PDIP 265                                            | r 243                                           |  |  |  |  |  |  |  |

| PLCC                                                | RA                                              |  |  |  |  |  |  |  |

| 44 lead 267                                         | register address 243                            |  |  |  |  |  |  |  |

| 68 lead 268                                         | RCF 247                                         |  |  |  |  |  |  |  |

| QFP 269                                             | receive                                         |  |  |  |  |  |  |  |

| part number description 275                         | 10-bit data format (I2C) 154                    |  |  |  |  |  |  |  |

| part selection guide 2                              | 7-bit data transfer format (I2C) 153            |  |  |  |  |  |  |  |

| PC 244                                              | IrDA data 127                                   |  |  |  |  |  |  |  |

| PDIP 265                                            | receive interrupt 145                           |  |  |  |  |  |  |  |

| peripheral AC and DC electrical characteristics 226 | receiving UART data-interrupt-driven method 108 |  |  |  |  |  |  |  |

| PHASE=0 timing (SPI) 133                            | receiving UART data-polled method 107           |  |  |  |  |  |  |  |

| PHASE=1 timing (SPI) 134                            | register 140, 169, 243                          |  |  |  |  |  |  |  |

| pin characteristics 16                              | ADC control (ADCCTL) 179                        |  |  |  |  |  |  |  |

| PLCC                                                | ADC data high byte (ADCDH) 180                  |  |  |  |  |  |  |  |

| 44 lead 267                                         | ADC data low bits (ADCDL) 180                   |  |  |  |  |  |  |  |

| 68-lead 268                                         | baud low and high byte (I2C) 160, 161, 163      |  |  |  |  |  |  |  |

| polarity 243                                        | baud rate high and low byte (SPI) 142           |  |  |  |  |  |  |  |

| POP 248                                             | control (SPI) 137                               |  |  |  |  |  |  |  |

| pop using extended addressing 248                   | control, I2C 158                                |  |  |  |  |  |  |  |

| POPX 248                                            | data, SPI 137                                   |  |  |  |  |  |  |  |

| port availability, device 57                        | DMA status (DMAA_STAT) 173                      |  |  |  |  |  |  |  |

| port input timing (GPIO) 232                        | DMA_ADC address 171                             |  |  |  |  |  |  |  |

| port output timing, GPIO 233                        | DMA_ADC control DMAACTL) 172                    |  |  |  |  |  |  |  |

| power supply signals 16                             | DMAx address high nibble (DMAxH) 169            |  |  |  |  |  |  |  |

| power-down, automatic (ADC) 176                     | DMAx control (DMAxCTL) 167                      |  |  |  |  |  |  |  |

| power-on and voltage brown-out 226                  | DMAx end/address low byte (DMAxEND) 170         |  |  |  |  |  |  |  |

| power-on reset (POR) 49                             | DMAx start/current address low byte register    |  |  |  |  |  |  |  |

| program control instructions 249                    | (DMAxSTART) 170                                 |  |  |  |  |  |  |  |

| program counter 244                                 | flash control (FCTL) 190                        |  |  |  |  |  |  |  |

| program memory 20                                   | flash high and low byte (FFREQH and FRE-        |  |  |  |  |  |  |  |

| PUSH 248                                            | EQL) 192                                        |  |  |  |  |  |  |  |

PS019919-1207 Index