# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| 5 |

|---|

|   |

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 46                                                            |

| Program Memory Size        | 24KB (24K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 2K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 68-LCC (J-Lead)                                               |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2422vs020ec00tr |

|                            |                                                               |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| General-Purpose I/O Port Output Timing     | 233 |

|--------------------------------------------|-----|

| On-Chip Debugger Timing                    | 234 |

| SPI Master Mode Timing 2                   | 235 |

| SPI Slave Mode Timing 2                    | 236 |

| I2C Timing                                 | 237 |

| UART Timing                                | 238 |

| eZ8 <sup>™</sup> CPU Instruction Set       | 241 |

| Assembly Language Programming Introduction | 241 |

| Assembly Language Syntax 2                 | 242 |

| eZ8 CPU Instruction Notation 2             | 242 |

| Condition Codes                            | 244 |

| eZ8 CPU Instruction Classes                | 245 |

| eZ8 CPU Instruction Summary 2              |     |

| Flags Register                             | 259 |

| Opcode Maps                                | 261 |

| Packaging                                  | 265 |

| Ordering Information                       | 270 |

| Part Number Suffix Designations            | 275 |

| Index                                      | 277 |

| Customer Support                           | 287 |

## Part Selection Guide

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore! XP product line.

## Table 1. Z8 Encore! XP 64K Series Flash Microcontrollers Part Selection Guide

| Part<br>Number    | Flash<br>(KB)                 | RAM<br>(KB) | I/O | 16-bit<br>Timers<br>with PWM | ADC<br>Inputs | UARTs<br>with IrDA | l <sup>2</sup> C | SPI |   | 64/68-pin<br>packages | 80-pin<br>package |

|-------------------|-------------------------------|-------------|-----|------------------------------|---------------|--------------------|------------------|-----|---|-----------------------|-------------------|

| Z8F1621           | 16                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F1622           | 16                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F2421           | 24                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F2422           | 24                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F3221           | 32                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F3222           | 32                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F4821           | 48                            | 4           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F4822           | 48                            | 4           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F4823           | 48                            | 4           | 60  | 4                            | 12            | 2                  | 1                | 1   |   |                       | Х                 |

| Z8F6421           | 64                            | 4           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F6422           | 64                            | 4           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F6423           | 64                            | 4           | 60  | 4                            | 12            | 2                  | 1                | 1   |   |                       | Х                 |

| Die Form<br>Sales | Contact<br>Zilog <sup>®</sup> |             |     |                              |               |                    |                  |     |   |                       |                   |

| Program Memory Address (Hex)              | Function                 |

|-------------------------------------------|--------------------------|

| 0000-0001                                 | Option Bits              |

| 0002-0003                                 | Reset Vector             |

| 0004-0005                                 | WDT Interrupt Vector     |

| 0006-0007                                 | Illegal Instruction Trap |

| 0008-0037                                 | Interrupt Vectors*       |

| 0038-BFFF                                 | Program Memory           |

| Z8F642x Products                          |                          |

| 0000-0001                                 | Option Bits              |

| 0002-0003                                 | Reset Vector             |

| 0004-0005                                 | WDT Interrupt Vector     |

| 0006-0007                                 | Illegal Instruction Trap |

| 0008-0037                                 | Interrupt Vectors*       |

| 0038-FFFF                                 | Program Memory           |

| *See Table 23 on page 68 for a list of th | ne interrupt vectors.    |

## Table 5. Z8 Encore! XP 64K Series Flash Microcontrollers Program Memory Maps (Continued)

## **Data Memory**

The Z8 Encore! XP 64K Series Flash Microcontrollers does not use the eZ8 CPU's 64 KB Data Memory address space.

## **Information Area**

Table 6 on page 22 describes the Z8 Encore! XP 64K Series Flash Microcontrollers Information Area. This 512 byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into the Program Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, execution of LDC and LDCI instruction from these Program Memory addresses return the Information Area data rather than the Program Memory data. Reads of these addresses through the On-Chip Debugger also returns the Information Area data. Execution of code from these addresses continues to correctly use the Program Memory. Access to the Information Area is read-only.

**Caution:** The following style of coding to generate software interrupts by setting bits in the Interrupt Request registers is NOT recommended. All incoming interrupts that are received between execution of the first LDX command and the last LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

To avoid missing interrupts, the following style of coding to set bits in the Interrupt Request registers is recommended:

Good coding style that avoids lost interrupt requests:

ORX IRQO, MASK

## Interrupt Control Register Definitions

For all interrupts other than the Watchdog Timer interrupt, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## Interrupt Request 0 Register

The Interrupt Request 0 (IRO0) register (Table 24) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8<sup>™</sup> CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending

|       |     |     | - J ( |       |       |      |      |      |

|-------|-----|-----|-------|-------|-------|------|------|------|

| BITS  | 7   | 6   | 5     | 4     | 3     | 2    | 1    | 0    |

| FIELD | T2I | T1I | TOI   | U0RXI | U0TXI | I2CI | SPII | ADCI |

| RESET |     |     |       | (     | )     |      |      |      |

| R/W   |     |     |       | R/    | W     |      |      |      |

| ADDR  |     |     |       | FC    | 0H    |      |      |      |

Table 24. Interrupt Request 0 Register (IRQ0)

T2I—Timer 2 Interrupt Request

0 = No interrupt request is pending for Timer 2.

1 = An interrupt request from Timer 2 is awaiting service.

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |  |  |  |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| FIELD | PAD7ENH | PAD6ENH | PAD5ENH | PAD4ENH | PAD3ENH | PAD2ENH | PAD1ENH | PAD0ENH |  |  |  |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |  |  |  |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |  |  |  |

| ADDR  |         | FC4H    |         |         |         |         |         |         |  |  |  |

## Table 31. IRQ1 Enable High Bit Register (IRQ1ENH)

PADxENH—Port A or Port D Bit[x] Interrupt Request Enable High Bit. For selection of either Port A or Port D as the interrupt source, see Interrupt Port Select Register on page 78.

Table 32. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| FIELD | PAD7ENL | PAD6ENL | PAD5ENL | PAD4ENL | PAD3ENL | PAD2ENL | PAD1ENL | PAD0ENL |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ADDR  |         |         |         | FC      | 5H      |         |         |         |

PADxENL—Port A or Port D Bit[x] Interrupt Request Enable Low Bit For selection of either Port A or Port D as the interrupt source, see Interrupt Port Select Register on page 78.

## **IRQ2 Enable High and Low Bit Registers**

The IRQ2 Enable High and Low Bit registers (see Table 34 and Table 35 on page 77) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register. Table 33 describes the priority control for IRQ2.

| Table 33 | IRQ2 | Enable | and | Priority | <sup>,</sup> Encoding |

|----------|------|--------|-----|----------|-----------------------|

|----------|------|--------|-----|----------|-----------------------|

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control 1 Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

## **Timer 0-3 Control 0 Registers**

The Timer 0-3 Control 0 (TxCTL0) registers (see Table 45 and Table 46) allow cascading of the Timers.

Table 45. Timer 0-3 Control 0 Register (TxCTL0)

| BITS  | 7                     | 6   | 5 | 4          | 3          | 2 | 1     | 0 |  |  |  |

|-------|-----------------------|-----|---|------------|------------|---|-------|---|--|--|--|

| FIELD | Reserved CSC Reserved |     |   |            |            |   | erved |   |  |  |  |

| RESET |                       |     |   | (          | )          |   |       |   |  |  |  |

| R/W   |                       | R/W |   |            |            |   |       |   |  |  |  |

| ADDR  |                       |     | F | 06H, F0EH, | F16H, F1EI | Н |       |   |  |  |  |

CSC—Cascade Timers

0 = Timer Input signal comes from the pin.

1 = For Timer 0, Input signal is connected to Timer 3 output.

For Timer 1, Input signal is connected to Timer 0 output.

For Timer 2, Input signal is connected to Timer 1 output.

For Timer 3, Input signal is connected to Timer 2 output.

## UART

## **Overview**

The Universal Asynchronous Receiver/Transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two Stop bits

- Separate transmit and receive interrupts

- Framing, parity, overrun and break detection

- Separate transmit and receive enables

- 16-bit Baud Rate Generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes

- Baud Rate Generator timer mode

- Driver Enable output for external bus transceivers

## Architecture

The UART consists of three primary functional blocks: Transmitter, Receiver, and Baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 13 on page 104 displays the UART architecture.

18.432 MHz System Clock

## 122

#### Table 61. UART Baud Rates

## 20.0 MHz System Clock

| 20.0 Militz Oy3 | Certi Olock  |             |       | 10:402 Milliz Oystelli Olock |                |             |        |  |  |

|-----------------|--------------|-------------|-------|------------------------------|----------------|-------------|--------|--|--|

| Desired Rate    | BRG Divisor  | Actual Rate | Error | Desired<br>Rate              | BRG<br>Divisor | Actual Rate | Error  |  |  |

| (kHz)           | (Decimal)    | (kHz)       | (%)   | (kHz)                        | (Decimal)      | (kHz)       | (%)    |  |  |

| 1250.0          | 1            | 1250.0      | 0.00  | 1250.0                       | 1              | 1152.0      | -7.84% |  |  |

| 625.0           | 2            | 625.0       | 0.00  | 625.0                        | 2              | 576.0       | -7.84% |  |  |

| 250.0           | 5            | 250.0       | 0.00  | 250.0                        | 5              | 230.4       | -7.84% |  |  |

| 115.2           | 11           | 113.6       | -1.36 | 115.2                        | 10             | 115.2       | 0.00   |  |  |

| 57.6            | 22           | 56.8        | -1.36 | 57.6                         | 20             | 57.6        | 0.00   |  |  |

| 38.4            | 33           | 37.9        | -1.36 | 38.4                         | 30             | 38.4        | 0.00   |  |  |

| 19.2            | 65           | 19.2        | 0.16  | 19.2                         | 60             | 19.2        | 0.00   |  |  |

| 9.60            | 130          | 9.62        | 0.16  | 9.60                         | 120            | 9.60        | 0.00   |  |  |

| 4.80            | 260          | 4.81        | 0.16  | 4.80                         | 240            | 4.80        | 0.00   |  |  |

| 2.40            | 521          | 2.40        | -0.03 | 2.40                         | 480            | 2.40        | 0.00   |  |  |

| 1.20            | 1042         | 1.20        | -0.03 | 1.20                         | 960            | 1.20        | 0.00   |  |  |

| 0.60            | 2083         | 0.60        | 0.02  | 0.60                         | 1920           | 0.60        | 0.00   |  |  |

| 0.30            | 4167         | 0.30        | -0.01 | 0.30                         | 3840           | 0.30        | 0.00   |  |  |

|                 | intern Clask |             |       | 44.0500 MU                   | - 0            | -l-         |        |  |  |

#### 16.667 MHz System Clock

|     | 0.30        | -0.01  | 0.30            | 3840           |    |

|-----|-------------|--------|-----------------|----------------|----|

| k   |             |        | 11.0592 MHz     | System Clo     | ck |

| sor | Actual Rate | Error  | Desired<br>Rate | BRG<br>Divisor | Ac |

| l)  | (kHz)       | (%)    | (kHz)           | (Decimal)      |    |

|     | 1041.69     | -16.67 | 1250.0          | N/A            |    |

|     | 520.8       | -16.67 | 625.0           | 1              |    |

|     | 260.4       | 4.17   | 250.0           | 3              |    |

|     | 115.7       | 0.47   | 115.2           | 6              |    |

4.80

2.40

|      | Desired | BRG       |             |       |

|------|---------|-----------|-------------|-------|

| ror  | Rate    | Divisor   | Actual Rate | Error |

| %)   | (kHz)   | (Decimal) | (kHz)       | (%)   |

| 6.67 | 1250.0  | N/A       | N/A         | N/A   |

| 6.67 | 625.0   | 1         | 691.2       | 10.59 |

| .17  | 250.0   | 3         | 230.4       | -7.84 |

| .47  | 115.2   | 6         | 115.2       | 0.00  |

| .47  | 57.6    | 12        | 57.6        | 0.00  |

| .47  | 38.4    | 18        | 38.4        | 0.00  |

| .47  | 19.2    | 36        | 19.2        | 0.00  |

| .45  | 9.60    | 72        | 9.60        | 0.00  |

144

288

4.80

2.40

| <b>Desired Rate</b> | BRG Divisor | Actual Rate | Error  |

|---------------------|-------------|-------------|--------|

| (kHz)               | (Decimal)   | (kHz)       | (%)    |

| 1250.0              | 1           | 1041.69     | -16.67 |

| 625.0               | 2           | 520.8       | -16.67 |

| 250.0               | 4           | 260.4       | 4.17   |

| 115.2               | 9           | 115.7       | 0.47   |

| 57.6                | 18          | 57.87       | 0.47   |

| 38.4                | 27          | 38.6        | 0.47   |

| 19.2                | 54          | 19.3        | 0.47   |

| 9.60                | 109         | 9.56        | -0.45  |

| 4.80                | 217         | 4.80        | -0.83  |

434

2.40

0.01

2.40

0.00

0.00

# zilog

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

## **SPI Signals**

The four basic SPI signals are:

- Master-In/Slave-Out

- Master-Out/Slave-In

- Serial Clock

- Slave Select

Each signal is described in both Master and Slave modes.

#### Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### **Serial Clock**

The Serial Clock (SCK) synchronizes data movement both in and out of the device through its MOSI and MISO pins. In MASTER mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted. When configured as a slave, the SPI block requires a minimum SCK period of greater than or equal to 8 times the system (XIN) clock period.

Transmit interrupts occur when the TDRE bit of the  $I^2C$  Status register sets and the TXI bit in the  $I^2C$  Control register is set. Transmit interrupts occur under the following conditions when the transmit data register is empty:

- The I<sup>2</sup>C Controller is enabled.

- The first bit of the byte of an address is shifting out and the RD bit of the I<sup>2</sup>C Status register is deasserted.

- The first bit of a 10-bit address shifts out.

- The first bit of write data shifts out.

**Note:** Writing to the  $l^2C$  Data register always clears the TRDE bit to 0. When TDRE is asserted, the  $l^2C$  Controller pauses at the beginning of the Acknowledge cycle of the byte currently shifting out until the Data register is written with the next value to send or the STOP or START bits are set indicating the current byte is the last one to send.

The fourth interrupt source is the baud rate generator. If the I<sup>2</sup>C Controller is disabled (IEN bit in the I2CCTL register = 0) and the BIRQ bit in the I2CCTL register = 1, an interrupt is generated when the baud rate generator counts down to 1. This allows the I<sup>2</sup>C baud rate generator to be used by software as a general purpose timer when IEN = 0.

## Software Control of I<sup>2</sup>C Transactions

Software can control  $I^2C$  transactions by using the  $I^2C$  Controller interrupt, by polling the  $I^2C$  Status register or by DMA. Note that not all products include a DMA Controller.

To use interrupts, the  $I^2C$  interrupt must be enabled in the Interrupt Controller. The TXI bit in the  $I^2C$  Control register must be set to enable transmit interrupts.

To control transactions by polling, the interrupt bits (TDRE, RDRF and NCKI) in the I<sup>2</sup>C Status register should be polled. The TDRE bit asserts regardless of the state of the TXI bit.

Either or both transmit and receive data movement can be controlled by the DMA Controller. The DMA Controller channel(s) must be initialized to select the I<sup>2</sup>C transmit and receive requests. Transmit DMA requests require that the TXI bit in the I<sup>2</sup>C Control register be set.

**Caution:** A transmit (write) DMA operation hangs if the slave responds with a Not Acknowledge before the last byte has been sent. After receiving the Not Acknowledge, the I<sup>2</sup>C Controller sets the NCKI bit in the Status register and pauses until either the STOP or START bits in the Control register are set.

## Table 74. I<sup>2</sup>C Baud Rate Low Byte Register (I2CBRL)

| BITS  | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|---|---|---|----|----|---|---|---|

| FIELD |   |   |   | BF | RL |   |   |   |

| RESET |   |   |   | FF | FΗ |   |   |   |

| R/W   |   |   |   | R/ | W  |   |   |   |

| ADDR  |   |   |   | F5 | 4H |   |   |   |

BRL =  $I^2C$  Baud Rate Low Byte

Least significant byte, BRG[7:0], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRL register returns the current value of the  $I^2C$  Baud Rate Counter[7:0].

## I<sup>2</sup>C Diagnostic State Register

The I<sup>2</sup>C Diagnostic State register (Table 75) provides observability of internal state. This is a read only register used for I<sup>2</sup>C diagnostics and manufacturing test.

| BITS  | 7     | 6     | 5      | 4  | 3  | 2         | 1 | 0 |  |

|-------|-------|-------|--------|----|----|-----------|---|---|--|

| FIELD | SCLIN | SDAIN | STPCNT |    | -  | TXRXSTATE | E |   |  |

| RESET | >     | K     |        |    | 0  |           |   |   |  |

| R/W   |       |       |        | F  | २  |           |   |   |  |

| ADDR  |       |       |        | F5 | 5H |           |   |   |  |

Table 75. I<sup>2</sup>C Diagnostic State Register (I2CDST)

SCLIN—Value of Serial Clock input signal

SDAIN—Value of the Serial Data input signal

STPCNT—Value of the internal Stop Count control signal

TXRXSTATE—Value of the internal I<sup>2</sup>C state machine

162

| TXRXSTATE | State Description                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0_000     | Idle State                                                                                                                              |

| 0_0001    | START State                                                                                                                             |

| 0_0010    | Send/Receive data bit 7                                                                                                                 |

| 0_0011    | Send/Receive data bit 6                                                                                                                 |

| 0_0100    | Send/Receive data bit 5                                                                                                                 |

| 0_0101    | Send/Receive data bit 4                                                                                                                 |

| 0_0110    | Send/Receive data bit 3                                                                                                                 |

| 0_0111    | Send/Receive data bit 2                                                                                                                 |

| 0_1000    | Send/Receive data bit 1                                                                                                                 |

| 0_1001    | Send/Receive data bit 0                                                                                                                 |

| 0_1010    | Data Acknowledge State                                                                                                                  |

| 0_1011    | Second half of data Acknowledge State used only for not acknowledge                                                                     |

| 0_1100    | First part of STOP state                                                                                                                |

| 0_1101    | Second part of STOP state                                                                                                               |

| 0_1110    | 10-bit addressing: Acknowledge State for 2nd address byte<br>7-bit addressing: Address Acknowledge State                                |

| 0_1111    | 10-bit address: Bit 0 (Least significant bit) of 2nd address byte<br>7-bit address: Bit 0 (Least significant bit) (R/W) of address byte |

| 1_0000    | 10-bit addressing: Bit 7 (Most significant bit) of 1st address byte                                                                     |

| 1_0001    | 10-bit addressing: Bit 6 of 1st address byte                                                                                            |

| 1_0010    | 10-bit addressing: Bit 5 of 1st address byte                                                                                            |

| 1_0011    | 10-bit addressing: Bit 4 of 1st address byte                                                                                            |

| 1_0100    | 10-bit addressing: Bit 3 of 1st address byte                                                                                            |

| 1_0101    | 10-bit addressing: Bit 2 of 1st address byte                                                                                            |

| 1_0110    | 10-bit addressing: Bit 1 of 1st address byte                                                                                            |

| 1_0111    | 10-bit addressing: Bit 0 (R/W) of 1st address byte                                                                                      |

| 1_1000    | 10-bit addressing: Acknowledge state for 1st address byte                                                                               |

| 1_1001    | 10-bit addressing: Bit 7 of 2nd address byte<br>7-bit addressing: Bit 7 of address byte                                                 |

| 1_1010    | 10-bit addressing: Bit 6 of 2nd address byte<br>7-bit addressing: Bit 6 of address byte                                                 |

| 1_1011    | 10-bit addressing: Bit 5 of 2nd address byte<br>7-bit addressing: Bit 5 of address byte                                                 |

| 1_1100    | 10-bit addressing: Bit 4 of 2nd address byte<br>7-bit addressing: Bit 4 of address byte                                                 |

If the current ADC Analog Input is not the highest numbered input to be converted, DMA ADC initiates data conversion in the next higher numbered ADC Analog Input.

## Configuring DMA\_ADC for Data Transfer

Follow the steps below to configure and enable DMA\_ADC:

- 1. Write the DMA\_ADC Address register with the 7 most-significant bits of the Register File address for data transfers.

- 2. Write to the DMA\_ADC Control register to complete the following:

- Enable the DMA ADC interrupt request, if desired

- Select the number of ADC Analog Inputs to convert

- Enable the DMA\_ADC channel

**Caution:** When using the DMA\_ADC to perform conversions on multiple ADC inputs, the Analog-to-Digital Converter must be configured for SINGLE-SHOT mode. If the ADC\_IN field in the DMA\_ADC Control Register is greater than 000b, the ADC must be in SINGLE-SHOT mode.

CONTINUOUS mode operation of the ADC can only be used in conjunction with DMA\_ADC if the ADC\_IN field in the DMA\_ADC Control Register is reset to 000b to enable conversion on ADC Analog Input 0 only.

## **DMA Control Register Definitions**

## DMAx Control Register

The DMAx Control register (see Table 77 on page 167) enables and selects the mode of operation for DMAx.

| Table 77. | . DMAx Control | Register | (DMAxCTL) |

|-----------|----------------|----------|-----------|

|-----------|----------------|----------|-----------|

| BITS  | 7   | 6   | 5    | 4     | 3    | 2 | 1   | 0 |

|-------|-----|-----|------|-------|------|---|-----|---|

| FIELD | DEN | DLE | DDIR | IRQEN | WSEL |   | RSS |   |

| RESET |     |     |      | (     | )    |   |     |   |

| R/W   |     |     |      | R/    | W    |   |     |   |

| ADDR  |     |     |      | FB0H, | FB8H |   |     |   |

DEN—DMAx Enable

0 = DMAx is disabled and data transfer requests are disregarded.

## 190

## **Flash Control Register Definitions**

## **Flash Control Register**

The Flash Control register (Table 92) unlocks the Flash Controller for programming and erase operations, or to select the Flash Sector Protect register.

The Write-only Flash Control Register shares its Register File address with the Read-only Flash Status Register.

Table 92. Flash Control Register (FCTL)

| BITS  | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|---|---|---|----|----|---|---|---|

| FIELD |   |   |   | FC | MD |   |   |   |

| RESET |   |   |   | (  | )  |   |   |   |

| R/W   |   |   |   | V  | V  |   |   |   |

| ADDR  |   |   |   | FF | 8H |   |   |   |

FCMD—Flash Command

73H = First unlock command.

8CH = Second unlock command.

95H = Page erase command.

63H = Mass erase command

5EH = Flash Sector Protect register select.

\* All other commands, or any command out of sequence, lock the Flash Controller.

## Flash Status Register

The Flash Status register (Table 93) indicates the current state of the Flash Controller. This register can be read at any time. The Read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

| BITS  | 7    | 6     | 5 | 4      | 3  | 2   | 1 | 0 |  |

|-------|------|-------|---|--------|----|-----|---|---|--|

| FIELD | Rese | erved |   |        | FS | TAT |   |   |  |

| RESET |      |       |   | 0      |    |     |   |   |  |

| R/W   |      |       |   | 0<br>R |    |     |   |   |  |

| ADDR  |      |       |   | FF     | 8H |     |   |   |  |

Table 93. Flash Status Register (FSTAT)

208

```

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• **Read Program Memory CRC (0EH)**—The Read Program Memory CRC command computes and returns the CRC (cyclic redundancy check) of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Read Protect Option Bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Read Protect Option Bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• Execute Instruction (12H)—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG mode or the Read Protect Option Bit is enabled, the OCD ignores this command

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 105 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, unused inputs must be tied to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +125    | С     |       |

| Storage temperature                                 | -65     | +150    | С     |       |

| Voltage on any pin with respect to $V_{SS}$         | -0.3    | +5.5    | V     | 1     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 80-Pin QFP Maximum Ratings at –40 °C to 70 °C       |         |         |       |       |

| Total power dissipation                             |         | 550     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 150     | mA    |       |

| 80-Pin QFP Maximum Ratings at 70 °C to 125 °C       |         |         |       |       |

| Total power dissipation                             |         | 200     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 56      | mA    |       |

| 68-Pin PLCC Maximum Ratings at –40 °C to 70 °C      |         |         |       |       |

| Total power dissipation                             |         | 1000    | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 275     | mA    |       |

| 68-Pin PLCC Maximum Ratings at 70 °C to 125 °C      |         |         |       |       |

| Total power dissipation                             |         | 500     | mW    |       |

|                                                     |         |         |       |       |

## Table 105. Absolute Maximum Ratings

zilog 223

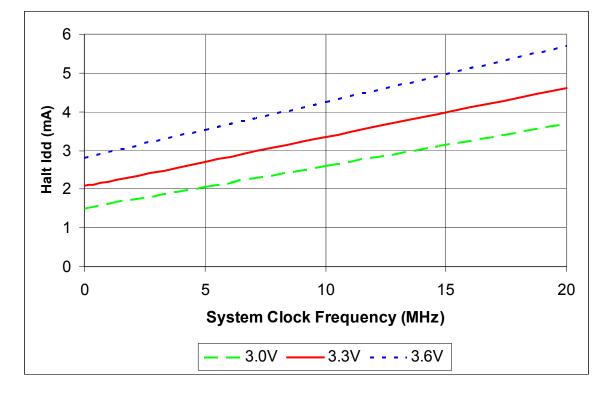

Figure 45 displays the maximum HALT mode current consumption across the full operating temperature range of the device and versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 46. Maximum HALT Mode Icc Versus System Clock Frequency

## **Opcode Maps**

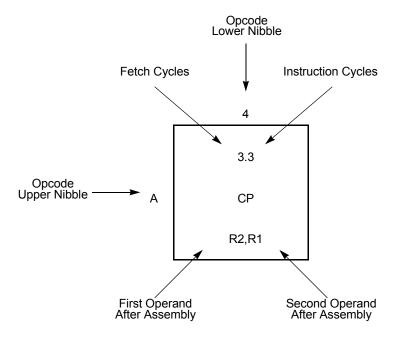

A description of the opcode map data and the abbreviations are provided in Figure 59 and Table 134 on page 262. Figure 60 on page 263 and Figure 61 on page 264 provide information on each of the  $eZ8^{TM}$  CPU instructions.

Figure 59. Opcode Map Cell Description

zilog

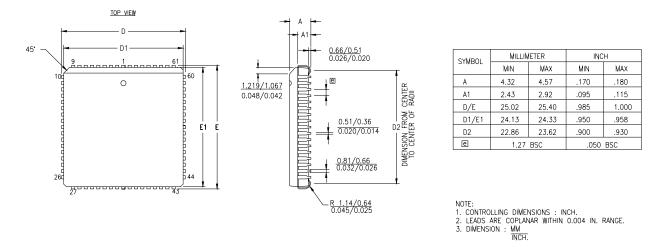

Figure 66. 68-Lead Plastic Lead Chip Carrier Package (PLCC)

Figure 66 displays the 68-pin Plastic Lead Chip Carrier (PLCC) package available for the Z8X1622, Z8X2422, Z8X3222, Z8X4822, and Z8X6422 devices.

268

282

## Μ

master interrupt enable 69 master-in, slave-out and-in 131 memory program 20 **MISO 131** mode capture 95 capture/compare 95 continuous 94 counter 94 gated 95 one-shot 94 **PWM 94** modes 95 **MULT 246** multiply 246 multiprocessor mode, UART 109

## Ν

NOP (no operation) 247 not acknowledge interrupt 145 notation b 243 cc 243 DA 243 ER 243 IM 243 IR 243 Ir 243 **IRR 243** Irr 243 p 243 R 243 r 243 RA 243 **RR 243** rr 243 vector 243 X 243 notational shorthand 243

## 0

OCD architecture 199 auto-baud detector/generator 202 baud rate limits 202 block diagram 199 breakpoints 203 commands 204 control register 209 data format 202 DBG pin to RS-232 Interface 200 debug mode 201 debugger break 249 interface 200 serial errors 203 status register 210 timing 234 OCD commands execute instruction (12H) 208 read data memory (0DH) 207 read OCD control register (05H) 206 read OCD revision (00H) 205 read OCD status register (02H) 205 read program counter (07H) 206 read program memory (0BH) 207 read program memory CRC (0EH) 208 read register (09H) 206 step instruction (10H) 208 stuff instruction (11H) 208 write data memory (0CH) 207 write OCD control register (04H) 206 write program counter (06H) 206 write program memory (0AH) 207 write register (08H) 206 on-chip debugger 5 on-chip debugger (OCD) 199 on-chip debugger signals 16 on-chip oscillator 211 one-shot mode 94 opcode map abbreviations 262 cell description 261 first 263 second after 1FH 264