Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 29                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f3221pm020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IIART                                                                                                                                                                                                                                                                                  | 103                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| UART   Overview   Architecture   Operation   Data Format   Transmitting Data using the Polled Method   Transmitting Data using the Interrupt-Driven Method   Receiving Data using the Polled Method   Receiving Data using the Interrupt-Driven Method   Clear To Send (CTS) Operation | 103<br>104<br>104<br>105<br>106<br>107<br>108<br>109 |

| MULTIPROCESSOR (9-bit) Mode                                                                                                                                                                                                                                                            |                                                      |

| External Driver Enable                                                                                                                                                                                                                                                                 |                                                      |

| UART Baud Rate Generator                                                                                                                                                                                                                                                               |                                                      |

| UART Control Register Definitions                                                                                                                                                                                                                                                      |                                                      |

| UART Transmit Data Register                                                                                                                                                                                                                                                            |                                                      |

| UART Receive Data Register                                                                                                                                                                                                                                                             |                                                      |

| UART Status 0 Register                                                                                                                                                                                                                                                                 | 115                                                  |

| UART Status 1 Register                                                                                                                                                                                                                                                                 | 116                                                  |

| UART Control 0 and Control 1 Registers                                                                                                                                                                                                                                                 |                                                      |

| UART Address Compare Register                                                                                                                                                                                                                                                          |                                                      |

| UART Baud Rate High and Low Byte Registers                                                                                                                                                                                                                                             | 120                                                  |

| Infrared Encoder/Decoder                                                                                                                                                                                                                                                               | 125                                                  |

| Overview                                                                                                                                                                                                                                                                               | 125                                                  |

| Architecture                                                                                                                                                                                                                                                                           | 125                                                  |

| Operation                                                                                                                                                                                                                                                                              | 126                                                  |

| Transmitting IrDA Data                                                                                                                                                                                                                                                                 |                                                      |

| Receiving IrDA Data                                                                                                                                                                                                                                                                    |                                                      |

| Infrared Encoder/Decoder Control Register Definitions                                                                                                                                                                                                                                  | 128                                                  |

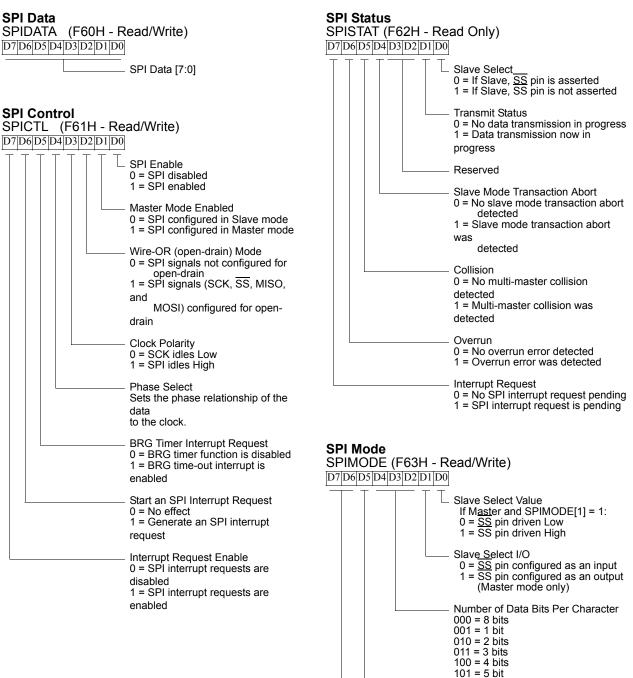

| Serial Peripheral Interface                                                                                                                                                                                                                                                            | 129                                                  |

| Overview                                                                                                                                                                                                                                                                               | 129                                                  |

| Architecture                                                                                                                                                                                                                                                                           | 129                                                  |

| Operation                                                                                                                                                                                                                                                                              |                                                      |

| SPI Signals                                                                                                                                                                                                                                                                            |                                                      |

| SPI Clock Phase and Polarity Control                                                                                                                                                                                                                                                   |                                                      |

| Multi-Master Operation                                                                                                                                                                                                                                                                 |                                                      |

| Slave Operation                                                                                                                                                                                                                                                                        | 134                                                  |

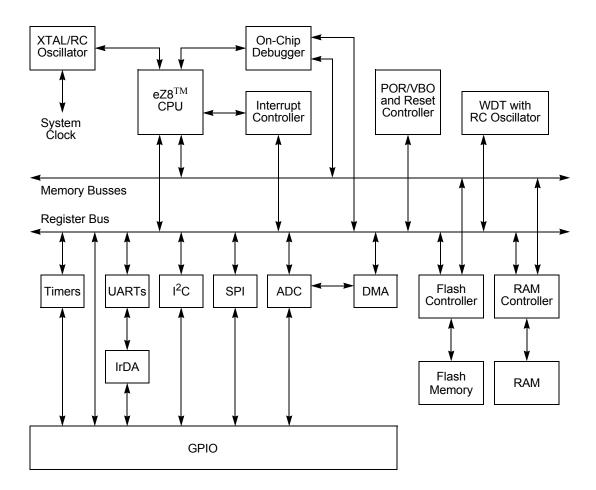

#### **Block Diagram**

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP 64K Series Flash Microcontrollers.

### **CPU and Peripheral Overview**

## eZ8<sup>™</sup> CPU Features

The latest 8-bit eZ8 CPU meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{\mathbb{R}}$  instruction set.

### **Pin Configurations**

Figure 2 through Figure 7 on page 13 display the pin configurations for all of the packages available in the Z8 Encore! XP 64K Series Flash Microcontrollers. For description of the signals, see Table 3 on page 14. Timer 3 is not available in the 40-pin and 44-pin packages.

| Г              |       |                |

|----------------|-------|----------------|

| PD4/RXD1 —     | 1 40  | — PD5 / TXD1   |

| PD3 / DE1 —    |       | — PC4 / MOSI   |

| PC5 / MISO —   |       | — PA4 / RXD0   |

| PA3 / CTS0 —   |       | — PA5 / TXD0   |

| PA2/DE0        | 5     | — PA6 / SCL    |

| PA1 /T0OUT -   | 35    | — PA7 / SDA    |

| PA0 / T0IN —   |       | — PD6 / CTS1   |

| PC2 / SS       |       | — PC3 / SCK    |

| RESET -        |       | — VSS          |

| VDD —          | 10    | — VDD          |

| VSS —          | 30    | — PC6 / T2IN * |

| PD1 —          |       | — DBG          |

| PD0 —          |       | — PC1 / T1OUT  |

| XOUT —         |       | — PC0 / T1IN   |

| XIN —          | 15    | — AVSS         |

| AVDD —         | 25    | — VREF         |

| PB0 / ANA0 —   |       | — PB2 / ANA2   |

| PB1 / ANA1 —   |       | — PB3 / ANA3   |

| PB4 / ANA4 —   |       | — PB7 / ANA7   |

| PB5 / ANA5 — 2 | 20 21 | — PB6 / ANA6   |

| L              |       |                |

Note: Timer 3 is not supported.

\* T2OUT is not supported.

#### Figure 2. Z8 Encore! XP 64K Series Flash Microcontrollers in 40-Pin Dual Inline Package (PDIP)

| Address (Hex)   | · · ·                              | Mnemonic  | Reset (Hex) | Page No |

|-----------------|------------------------------------|-----------|-------------|---------|

| -61             | SPI Control                        | SPICTL    | 00          | 137     |

| F62             | SPI Status                         | SPISTAT   | 01          | 139     |

| F63             | SPI Mode                           | SPIMODE   | 00          | 140     |

| F64             | SPI Diagnostic State               | SPIDST    | 00          | 141     |

| F65             | Reserved                           | _         | XX          |         |

| F66             | SPI Baud Rate High Byte            | SPIBRH    | FF          | 142     |

| F67             | SPI Baud Rate Low Byte             | SPIBRL    | FF          | 142     |

| F68-F6F         | Reserved                           | _         | XX          |         |

| Analog-to-Digit | tal Converter                      |           |             |         |

| F70             | ADC Control                        | ADCCTL    | 20          | 179     |

| F71             | Reserved                           | _         | XX          |         |

| F72             | ADC Data High Byte                 | ADCD_H    | XX          | 180     |

| F73             | ADC Data Low Bits                  | ADCD_L    | XX          | 180     |

| F74-FAF         | Reserved                           | _         | XX          |         |

| DMA 0           |                                    |           |             |         |

| FB0             | DMA0 Control                       | DMA0CTL   | 00          | 167     |

| FB1             | DMA0 I/O Address                   | DMA0IO    | XX          | 169     |

| FB2             | DMA0 End/Start Address High Nibble | DMA0H     | XX          | 169     |

| FB3             | DMA0 Start Address Low Byte        | DMA0START | XX          | 170     |

| FB4             | DMA0 End Address Low Byte          | DMA0END   | XX          | 170     |

| DMA 1           |                                    |           |             |         |

| FB8             | DMA1 Control                       | DMA1CTL   | 00          | 167     |

| FB9             | DMA1 I/O Address                   | DMA1IO    | XX          | 169     |

| FBA             | DMA1 End/Start Address High Nibble | DMA1H     | XX          | 169     |

| FBB             | DMA1 Start Address Low Byte        | DMA1START | XX          | 170     |

| FBC             | DMA1 End Address Low Byte          | DMA1END   | XX          | 170     |

| DMA ADC         |                                    |           |             |         |

| FBD             | DMA ADC Address                    | DMAA_ADDR | XX          | 171     |

| FBE             | DMA ADC Control                    | DMAACTL   | 00          | 172     |

| FBF             | DMA ADC Status                     | DMAASTAT  | 00          | 173     |

| Interrupt Contr |                                    | _         |             | -       |

| FC0             | Interrupt Request 0                | IRQ0      | 00          | 71      |

| FC1             | IRQ0 Enable High Bit               | IRQ0ENH   | 00          | 74      |

| FC2             | IRQ0 Enable Low Bit                | IRQ0ENL   | 00          | 74      |

| FC3             | Interrupt Request 1                | IRQ1      | 00          | 72      |

| FC4             | IRQ1 Enable High Bit               | IRQ1ENH   | 00          | 75      |

| FC5             | IRQ1 Enable Low Bit                | IRQ1ENL   | 00          | 75      |

| FC6             | Interrupt Request 2                | IRQ2      | 00          | 73      |

| FC7             | IRQ2 Enable High Bit               | IRQ2ENH   | 00          | 76      |

| FC8             | IRQ2 Enable Low Bit                | IRQ2ENL   | 00          | 76      |

| FC9-FCC         | Reserved                           |           | XX          |         |

Table 7. Z8 Encore! XP 64K Series Flash Microcontrollers Register File Address Map (Continued)

AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A–H Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A–H Output Control Sub-Registers

The Port A–H Output Control sub-register (Table 18) is accessed through the Port A–H Control register by writing 03H to the Port A–H Address register. Setting the bits in the Port A–H Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

#### Table 18. Port A-H Output Control Sub-Registers

| BITS  | 7                                                                                 | 6    | 5    | 4                   | 3 | 2    | 1    | 0    |  |  |

|-------|-----------------------------------------------------------------------------------|------|------|---------------------|---|------|------|------|--|--|

| FIELD | POC7                                                                              | POC6 | POC5 | POC5 POC4 POC3 POC2 |   | POC2 | POC1 | POC0 |  |  |

| RESET | 0                                                                                 |      |      |                     |   |      |      |      |  |  |

| R/W   | R/W                                                                               |      |      |                     |   |      |      |      |  |  |

| ADDR  | If 03H in Port A–H Address Register, accessible through Port A–H Control Register |      |      |                     |   |      |      |      |  |  |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and disables the drains if set to 1.

0 = The drains are enabled for any output mode.

1 = The drain of the associated pin is disabled (open-drain mode).

#### Port A-H High Drive Enable Sub-Registers

The Port A–H High Drive Enable sub-register (Table 19) is accessed through the Port A–H Control register by writing 04H to the Port A–H Address register. Setting the bits in the Port A–H High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–H High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

# Watchdog Timer

#### Overview

The Watchdog Timer (WDT) helps protect against corrupt or unreliable software, power faults, and other system-level problems which may place the Z8 Encore! XP into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator.

- A selectable time-out response.

- WDT Time-out response: Reset or interrupt.

- 24-bit programmable time-out value.

#### Operation

The Watchdog Timer (WDT) is a retriggerable one-shot timer that resets or interrupts the 64K Series devices when the WDT reaches its terminal count. The Watchdog Timer uses its own dedicated on-chip RC oscillator as its clock source. The Watchdog Timer has only two modes of operation—ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. An enable can be performed by executing the WDT instruction or by setting the WDT\_AO Option Bit. The WDT\_AO bit enables the Watchdog Timer to operate all the time, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the  $eZ8^{TM}$  CPU register space to set the reload value. The nominal WDT time-out period is given by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed once it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 47 provides information on approximate time-out delays for the minimum and maximum WDT reload values.

- 120

- 1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

#### **UART Address Compare Register**

The UART Address Compare register (Table 58) stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

#### Table 58. UART Address Compare Register (UxADDR)

| BITS  | 7 | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |

|-------|---|-----|---|---------|---------|---|---|---|--|

| FIELD |   |     |   | COMP    | _ADDR   |   |   |   |  |

| RESET |   | 0   |   |         |         |   |   |   |  |

| R/W   |   | R/W |   |         |         |   |   |   |  |

| ADDR  |   |     |   | F45H ar | nd F4DH |   |   |   |  |

COMP\_ADDR—Compare Address

This 8-bit value is compared to the incoming address bytes.

#### UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (see Table 59 and Table 60 on page 121) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the desired 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the UART BRG interrupt interval is calculated using the following equation:

UART BRG Interrupt Interval(s) = System Clock Period (s) × BRG[15:0]

# **Infrared Encoder/Decoder**

### **Overview**

The 64K Series products contain two fully-functional, high-performance UART to Infrared Encoder/Decoders (Endecs). Each Infrared Endec is integrated with an on-chip UART to allow easy communication between the 64K Series and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers, and other infrared enabled devices.

# Architecture

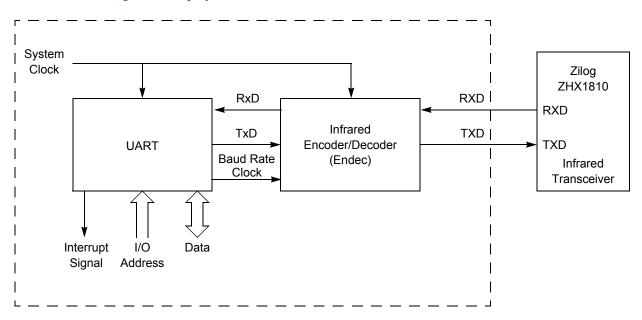

Figure 19 displays the architecture of the Infrared Endec.

Figure 19. Infrared Data Communication System Block Diagram

repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal. This action allows the Endec to tolerate jitter and baud rate errors in the incoming data stream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

### Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in UART Control Register Definitions on page 114.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UARTx Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

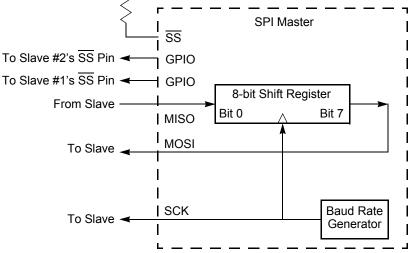

Figure 23. SPI Configured as a Master in a Single Master, Multiple Slave System

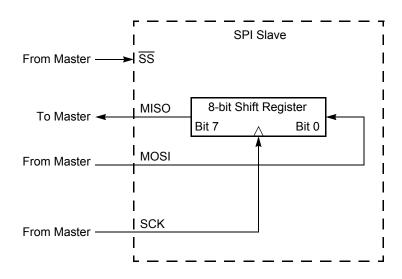

Figure 24. SPI Configured as a Slave

# Operation

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (serial clock, transmit, receive and Slave select). The SPI block consists of a transmit/receive shift register, a Baud Rate (clock) Generator and a control unit.

145

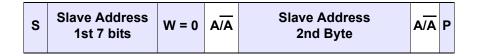

- Master receives from a 7-bit slave

- Master receives from a 10-bit slave

#### SDA and SCL Signals

$I^2C$  sends all addresses, data and acknowledge signals over the SDA line, most-significant bit first. SCL is the common clock for the  $I^2C$  Controller. When the SDA and SCL pin alternate functions are selected for their respective GPIO ports, the pins are automatically configured for open-drain operation.

The master  $(I^2C)$  is responsible for driving the SCL clock signal, although the clock signal can become skewed by a slow slave device. During the low period of the clock, the slave pulls the SCL signal Low to suspend the transaction. The master releases the clock at the end of the low period and notices that the clock remains low instead of returning to a high level. When the slave releases the clock, the I<sup>2</sup>C Controller continues the transaction. All data is transferred in bytes and there is no limit to the amount of data transferred in one operation. When transmitting data or acknowledging read data from the slave, the SDA signal changes in the middle of the low period of SCL and is sampled in the middle of the high period of SCL.

#### I<sup>2</sup>C Interrupts

The I<sup>2</sup>C Controller contains four sources of interrupts—Transmit, Receive, Not Acknowledge and baud rate generator. These four interrupt sources are combined into a single interrupt request signal to the Interrupt Controller. The Transmit interrupt is enabled by the IEN and TXI bits of the Control register. The Receive and Not Acknowledge interrupts are enabled by the IEN bit of the Control register. The baud rate generator interrupt is enabled by the BIRQ and IEN bits of the Control register.

Not Acknowledge interrupts occur when a Not Acknowledge condition is received from the slave or sent by the I<sup>2</sup>C Controller and neither the START or STOP bit is set. The Not Acknowledge event sets the NCKI bit of the I<sup>2</sup>C Status register and can only be cleared by setting the START or STOP bit in the I<sup>2</sup>C Control register. When this interrupt occurs, the I<sup>2</sup>C Controller waits until either the STOP or START bit is set before performing any action. In an interrupt service routine, the NCKI bit should always be checked prior to servicing transmit or receive interrupt conditions because it indicates the transaction is being terminated.

Receive interrupts occur when a byte of data has been received by the I<sup>2</sup>C Controller (master reading data from slave). This procedure sets the RDRF bit of the I<sup>2</sup>C Status register. The RDRF bit is cleared by reading the I<sup>2</sup>C Data register. The RDRF bit is set during the acknowledge phase. The I<sup>2</sup>C Controller pauses after the acknowledge phase until the receive interrupt is cleared before performing any other action.

- 13. The I<sup>2</sup>C Controller shifts the data out of using the SDA signal. After the first bit is sent, the Transmit interrupt is asserted.

- 14. If more bytes remain to be sent, return to step 9.

- 15. Software responds by setting the STOP bit of the I<sup>2</sup>C Control register (or START bit to initiate a new transaction). In the STOP case, software clears the TXI bit of the I<sup>2</sup>C Control register at the same time.

- 16. The I<sup>2</sup>C Controller completes transmission of the data on the SDA signal.

- 17. The slave may either Acknowledge or Not Acknowledge the last byte. Because either the STOP or START bit is already set, the NCKI interrupt does not occur.

- The I<sup>2</sup>C Controller sends the STOP (or RESTART) condition to the I<sup>2</sup>C bus. The STOP or START bit is cleared.

#### Address Only Transaction with a 10-bit Address

In the situation where software wants to determine if a slave with a 10-bit address is responding without sending or receiving data, a transaction can be done which only consists of an address phase. Figure 30 displays this 'address only' transaction to determine if a slave with 10-bit address will acknowledge. As an example, this transaction can be used after a 'write' has been done to a EEPROM to determine when the EEPROM completes its internal write operation and is once again responding to I<sup>2</sup>C transactions. If the slave does not Acknowledge the transaction can be repeated until the slave is able to Acknowledge.

#### Figure 30. 10-Bit Address Only Transaction Format

Follow the steps below for an address only transaction to a 10-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control register to enable Transmit interrupts.

- 3. The I<sup>2</sup>C interrupt asserts, because the I<sup>2</sup>C Data register is empty (TDRE = 1)

- 4. Software responds to the TDRE interrupt by writing the first slave address byte. The least-significant bit must be 0 for the write operation.

- 5. Software asserts the START bit of the  $I^2C$  Control register.

- 6. The  $I^2C$  Controller sends the START condition to the  $I^2C$  slave.

### **Information Area**

Table 91 describes the 64K Series Information Area. This 512-byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into Flash Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, LDC instructions return data from the Information Area. CPU instruction fetches always comes from Flash Memory regardless of the Information Area access bit. Access to the Information Area is read-only.

| Flash Memory Address (Hex) | Function                                                                                    |

|----------------------------|---------------------------------------------------------------------------------------------|

| FE00H-FE3FH                | Reserved                                                                                    |

| FE40H-FE53H                | Part Number<br>20-character ASCII alphanumeric code<br>Left justified and filled with zeros |

| FE54H-FFFFH                | Reserved                                                                                    |

Table 91. Z8 Encore! XP 64K Series Flash Microcontrollers Information Area Map

### Operation

The Flash Controller provides the proper signals and timing for Byte Programming, Page Erase, and Mass Erase of the Flash memory. The Flash Controller contains a protection mechanism, via the Flash Control register (FCTL), to prevent accidental programming or erasure. The following subsections provide details on the various operations (Lock, Unlock, Sector Protect, Byte Programming, Page Erase, and Mass Erase).

#### 226

# **On-Chip Peripheral AC and DC Electrical Characteristics**

#### $T_A = -40 \ ^{\circ}C \ to \ 125 \ ^{\circ}C$ Minimum Typical<sup>1</sup> Symbol Parameter Maximum Units Conditions V<sub>POR</sub> Power-On Reset 2.40 2.70 2.90 V $V_{DD} = V_{POR}$ Voltage Threshold Voltage Brownout Reset $V_{DD} = V_{VBO}$ V<sub>VBO</sub> 2.30 2.60 2.85 V Voltage Threshold $V_{\text{POR}}$ to $V_{\text{VBO}}$ 50 100 mV hysteresis Starting V<sub>DD</sub> voltage to ensure valid Power-On $V_{SS}$ V \_ Reset. T<sub>ANA</sub> Power-On Reset Analog 50 V<sub>DD</sub> > V<sub>POR</sub>; T<sub>POR</sub> Digital μS \_ Reset delay follows TANA Delay Power-On Reset Digital 66 WDT Oscillator cycles T<sub>POR</sub> 6.6 ms \_ \_ (10 kHz) + 16 System Clock Delay cycles (20 MHz) Voltage Brownout Pulse $V_{DD} < V_{VBO}$ to generate a 10 T<sub>VBO</sub> \_ μS \_ **Rejection Period** Reset. Time for VDD to T<sub>RAMP</sub> 0.10 100 ms \_ transition from $V_{SS}$ to V<sub>POR</sub> to ensure valid Reset

#### Table 107. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

<sup>1</sup>Data in the typical column is from characterization at 3.3 V and 0 °C. These values are provided for design guidance only and are not tested in production.

zilog

239

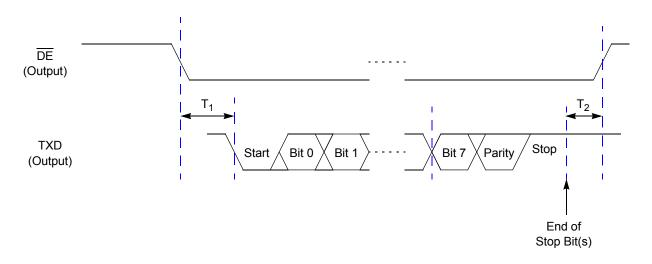

Figure 57 and Table 121 provide timing information for UART pins for the case where the Clear To Send input signal ( $\overline{\text{CTS}}$ ) is not used for flow control. In this example, it is assumed that the Driver Enable polarity has been configured to be Active Low and is represented here by  $\overline{\text{DE}}$ .  $\overline{\text{DE}}$  asserts after the UART Transmit Data Register has been written.  $\overline{\text{DE}}$  remains asserted for multiple characters as long as the Transmit Data register is written with the next character before the current character has completed.

| Table 121 | . UART | Timing | without | CTS |

|-----------|--------|--------|---------|-----|

|-----------|--------|--------|---------|-----|

|                |                                                                | Delay (ns      |                                  |  |  |  |  |

|----------------|----------------------------------------------------------------|----------------|----------------------------------|--|--|--|--|

| Parameter      | Abbreviation                                                   | Minimum        | Maximum                          |  |  |  |  |

| T <sub>1</sub> | DE Assertion to TXD Falling Edge (Start)<br>Delay              | 1 Bit period   | 1 Bit period +<br>1 * XIN period |  |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to $\overline{\text{DE}}$ Deassertion Delay | 1 * XIN period | 2 * XIN period                   |  |  |  |  |

#### Table 123. Additional Symbols

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

#### **Condition Codes**

The C, Z, S and V Flags control the operation of the conditional jump (JP cc and JR cc) instructions. Sixteen frequently useful functions of the Flag settings are encoded in a 4-bit field called the condition code (cc), which forms Bits 7:4 of the conditional jump instructions. The condition codes are summarized in Table 124. Some binary condition codes can be created using more than one assembly code mnemonic. The result of the Flag test operation decides if the conditional jump is executed.

| Binary | Hex | Assembly<br>Mnemonic | Definition         | Flag Test Operation  |

|--------|-----|----------------------|--------------------|----------------------|

| 0000   | 0   | F                    | Always False       | -                    |

| 0001   | 1   | LT                   | Less Than          | (S XOR V) = 1        |

| 0010   | 2   | LE                   | Less Than or Equal | (Z OR (S XOR V)) = 1 |

#### Table 124. Condition Codes

| Assembly      |                                                      |     | ress<br>ode | _ Opcode(s) | Flags |   |   |   |   |   | - Fetch | Instr. |

|---------------|------------------------------------------------------|-----|-------------|-------------|-------|---|---|---|---|---|---------|--------|

| Mnemonic      | Symbolic Operation                                   | dst | src         | (Hex)       | С     | Ζ | S | V | D | Н | Cycles  |        |

| RRC dst       |                                                      | R   |             | C0          | *     | * | * | * | - | - | 2       | 2      |

|               | ► <u>D7 D6 D5 D4 D3 D2 D1 D0</u> ► <u>C</u><br>dst   | IR  |             | C1          | •     |   |   |   |   |   | 2       | 3      |

| SBC dst, src  | $dst \gets dst - src - C$                            | r   | r           | 32          | *     | * | * | * | 1 | * | 2       | 3      |

|               | -                                                    | r   | lr          | 33          | •     |   |   |   |   |   | 2       | 4      |

|               | -                                                    | R   | R           | 34          | •     |   |   |   |   |   | 3       | 3      |

|               | -                                                    | R   | IR          | 35          | •     |   |   |   |   |   | 3       | 4      |

|               | -                                                    | R   | IM          | 36          | •     |   |   |   |   |   | 3       | 3      |

|               | -                                                    | IR  | IM          | 37          | •     |   |   |   |   |   | 3       | 4      |

| SBCX dst, src | $dst \leftarrow dst - src - C$                       | ER  | ER          | 38          | *     | * | * | * | 1 | * | 4       | 3      |

|               | -                                                    | ER  | IM          | 39          | •     |   |   |   |   |   | 4       | 3      |

| SCF           | C ← 1                                                |     |             | DF          | 1     | - | - | - | - | - | 1       | 2      |

| SRA dst       | - <b>v</b> v                                         | R   |             | D0          | *     | * | * | 0 | - | - | 2       | 2      |

|               | — D7D6D5D4D3D2D1D0 → C<br>dst                        | IR  |             | D1          |       |   |   |   |   |   | 2       | 3      |

| SRL dst       | ) <b>-&gt;</b> D7D6D5D4D3D2D1D0 <mark>-&gt;</mark> C | R   |             | 1F C0       | *     | * | 0 | * | - | - | 3       | 2      |

|               | dst                                                  | IR  |             | 1F C1       | •     |   |   |   |   |   | 3       | 3      |

| SRP src       | $RP \leftarrow src$                                  |     | IM          | 01          | -     | - | - | - | - | - | 2       | 2      |

| STOP          | STOP Mode                                            |     |             | 6F          | -     | - | - | - | - | - | 1       | 2      |

| SUB dst, src  | $dst \gets dst - src$                                | r   | r           | 22          | *     | * | * | * | 1 | * | 2       | 3      |

|               | -                                                    | r   | lr          | 23          | •     |   |   |   |   |   | 2       | 4      |

|               | -                                                    | R   | R           | 24          | •     |   |   |   |   |   | 3       | 3      |

|               | -                                                    | R   | IR          | 25          | •     |   |   |   |   |   | 3       | 4      |

|               | -                                                    | R   | IM          | 26          |       |   |   |   |   |   | 3       | 3      |

|               | -                                                    | IR  | IM          | 27          |       |   |   |   |   |   | 3       | 4      |

| SUBX dst, src | dst ← dst – src                                      | ER  | ER          | 28          | *     | * | * | * | 1 | * | 4       | 3      |

|               | -                                                    | ER  | IM          | 29          | •     |   |   |   |   |   | 4       | 3      |

### Table 133. eZ8 CPU Instruction Summary (Continued)

263

|   |                         |                           |                              |                             |                            |                             | Le                            | ower Nil                       | bble (He                      | x)                             |                            |                          |                           |                           |                         |                          |

|---|-------------------------|---------------------------|------------------------------|-----------------------------|----------------------------|-----------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|--------------------------|

|   | 0                       | 1                         | 2                            | 3                           | 4                          | 5                           | 6                             | 7                              | 8                             | 9                              | А                          | В                        | С                         | D                         | Е                       | F                        |

| 0 | 1.2<br>BRK              | 2.2<br>SRP<br>IM          | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br><b>ADD</b><br>r1,lr2 | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br><b>ADD</b><br>IR2,R1 | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br><b>ADD</b><br>IR1,IM    | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1 | 2.3<br><b>RLC</b><br>IR1  | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2        | 3.3<br><b>ADC</b><br>R2,R1 | 3.4<br>ADC<br>IR2,R1        | 3.3<br><b>ADC</b><br>R1,IM    | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                           |                           |                         | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1         | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br>SUB<br>r1,lr2        | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br><b>SUB</b><br>IR2,R1 | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM           | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                           |                           |                         | 1,2<br><b>ATM</b>        |

| 3 | 2.2<br><b>DEC</b><br>R1 | 2.3<br><b>DEC</b><br>IR1  | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2        | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br>SBC<br>IR2,R1        | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                           |                           |                         |                          |

| 4 | 2.2<br><b>DA</b><br>R1  | 2.3<br><b>DA</b><br>IR1   | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br>OR<br>r1,lr2         | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br>ORX<br>ER2,ER1         | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                           |                           |                         |                          |

| 5 | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1  | 2.3<br><b>AND</b><br>r1,r2   | 2.4<br><b>AND</b><br>r1,lr2 | 3.3<br><b>AND</b><br>R2,R1 | 3.4<br><b>AND</b><br>IR2,R1 | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                           |                           |                         | <b>WDT</b>               |

| 6 | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1         | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2 | 3.3<br><b>TCM</b><br>R2,R1 | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                           |                           |                         | STOP                     |

| 7 | 2.2<br>PUSH<br>R2       | 2.3<br>PUSH<br>IR2        | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2  | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.2<br>HALT              |

| 8 | 2.5<br>DECW<br>RR1      | 2.6<br>DECW<br>IRR1       | 2.5<br>LDE<br>r1,Irr2        | 2.9<br>LDEI<br>Ir1,Irr2     | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2       | 3.4<br>LDX<br>IRR2,R1         | 3.5<br><b>LDX</b><br>IRR2,IR1  | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X         |                            |                          |                           |                           |                         | 1.2<br>DI                |

| 9 | 2.2                     | 2.3<br>RL<br>IR1          | 2.5<br>LDE<br>r2,Irr1        | 2.9<br>LDEI<br>Ir2,Irr1     | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br>LDX<br>R2,IRR1         | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br>LEA<br>r1,r2,X         | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                           |                           |                         | 1.2<br>El                |

| А | 2.5                     | 2.6<br>INCW               | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2  | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.4<br>RET               |

| В | 2.2                     | 2.3<br>CLR<br>IR1         | 2.3<br>XOR<br>r1,r2          | 2.4<br>XOR<br>r1,lr2        | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br>XOR<br>IR2,R1        | 3.3<br>XOR<br>R1,IM           | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                          |                           |                           |                         | 1.5<br>IRET              |

| С | 2.2                     | 2.3<br>RRC<br>IR1         | 2.5<br>LDC<br>r1,lrr2        | 2.9<br>LDCI<br>Ir1,Irr2     | 2.3<br>JP<br>IRR1          | 2.9<br>LDC<br>lr1,lrr2      | ,                             | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           | ,                              |                            |                          |                           |                           |                         | 1.2<br>RCF               |

| C | 2.2                     | 2.3<br><b>SRA</b><br>IR1  | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br>LDCI<br>Ir2,Irr1     | 2.6<br>CALL<br>IRR1        | 2.2<br><b>BSWAP</b><br>R1   | 3.3<br>CALL<br>DA             | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                           |                           |                         | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1  | 2.3<br><b>RR</b><br>IR1   | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2  | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br><b>LDX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1       | 2.3<br><b>SWAP</b><br>IR1 | 2.6<br>TRAP<br>Vector        | 2.3<br><b>LD</b><br>lr1,r2  | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | V                          | V                        | V                         | V                         | V                       |                          |

Figure 60. First Opcode Map

For technical and customer support, hardware and software development tools, refer to the  $Zilog^{\mathbb{R}}$  website at <u>www.zilog.com</u>. The latest released version of ZDS can be downloaded from this website.

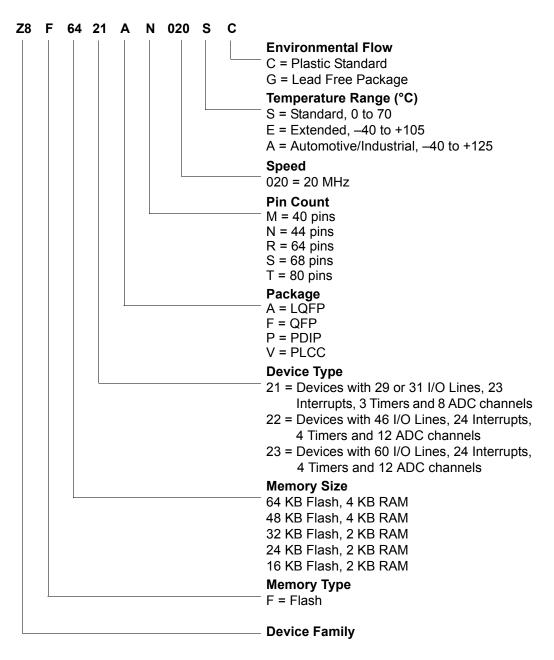

#### Part Number Suffix Designations