Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 29                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f3221pm020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Program Memory Address (Hex)              | Function                 |

|-------------------------------------------|--------------------------|

| 0000-0001                                 | Option Bits              |

| 0002-0003                                 | Reset Vector             |

| 0004-0005                                 | WDT Interrupt Vector     |

| 0006-0007                                 | Illegal Instruction Trap |

| 0008-0037                                 | Interrupt Vectors*       |

| 0038-BFFF                                 | Program Memory           |

| Z8F642x Products                          |                          |

| 0000-0001                                 | Option Bits              |

| 0002-0003                                 | Reset Vector             |

| 0004-0005                                 | WDT Interrupt Vector     |

| 0006-0007                                 | Illegal Instruction Trap |

| 0008-0037                                 | Interrupt Vectors*       |

| 0038-FFFF                                 | Program Memory           |

| *See Table 23 on page 68 for a list of th | ne interrupt vectors.    |

#### Table 5. Z8 Encore! XP 64K Series Flash Microcontrollers Program Memory Maps (Continued)

#### **Data Memory**

The Z8 Encore! XP 64K Series Flash Microcontrollers does not use the eZ8 CPU's 64 KB Data Memory address space.

#### **Information Area**

Table 6 on page 22 describes the Z8 Encore! XP 64K Series Flash Microcontrollers Information Area. This 512 byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into the Program Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, execution of LDC and LDCI instruction from these Program Memory addresses return the Information Area data rather than the Program Memory data. Reads of these addresses through the On-Chip Debugger also returns the Information Area data. Execution of code from these addresses continues to correctly use the Program Memory. Access to the Information Area is read-only.

# zilog

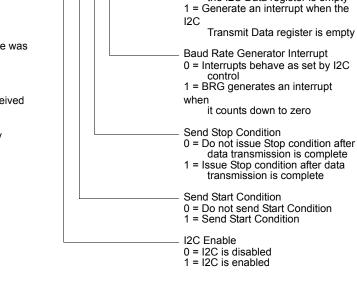

I2C Signal Filter Enable 0 = Digital filtering disabled

1 = Clears I2C Data register

0 = Do not send NAK 1 = Send NAK after next byte

from slave

Enable TDRE Interrupts

0 = Do not generate an interrupt

the I2C Data register is empty

Flush Data

Send NAK

received

when

0 = No effect

1 = Low-pass digital filters enabled on SDA and SCL input signals

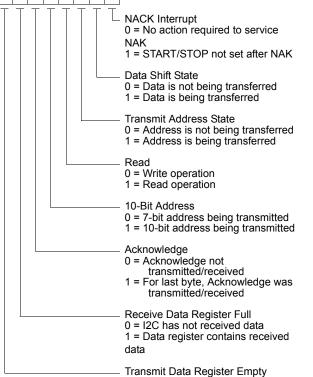

#### I<sup>2</sup>C Status I2CSTAT (F51H - Read Only) D7 D6 D5 D4 D3 D2 D1 D0

0 = Data register is full

1 = Data register is empty

I<sup>2</sup>C Control

I2CCTL (F52H - Read/Write)

D7 D6 D5 D4 D3 D2 D1 D0

#### **I2C Baud Rate Generator High Byte**

I2CBRH (F53H - Read/Write)

I2C Baud Rate divisor [15:8]

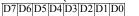

#### I2C Baud Rate Generator Low Byte I2CBRL (F54H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0

I2C Baud Rate divisor [7:0]

## zilog

#### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the WDT Control register is set.

#### **Stop Mode Recovery**

STOP mode is entered by the eZ8 executing a STOP instruction. For detailed STOP mode information, see Low-Power Modes on page 47. During Stop Mode Recovery, the devices are held in reset for 66 cycles of the Watchdog Timer oscillator followed by 16 cycles of the system clock. Stop Mode Recovery only affects the contents of the Watchdog Timer Control register. Stop Mode Recovery does not affect any other values in the Register File, including the Stack Pointer, Register Pointer, Flags, peripheral control registers, and general-purpose RAM.

The eZ8<sup>™</sup> CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the STOP bit in the Watchdog Timer Control Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions.

| Operating Mode | Stop Mode Recovery Source                                                         | Action                                                               |

|----------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP mode      | Watchdog Timer time-out when configured for Reset                                 | Stop Mode Recovery                                                   |

|                | Watchdog Timer time-out when configured for interrupt                             | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO Port pin<br>enabled as a Stop Mode Recovery<br>source | Stop Mode Recovery                                                   |

#### Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Watchdog Timer Control register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the 64K Series devices are configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A–H Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A–H Output Control Sub-Registers

The Port A–H Output Control sub-register (Table 18) is accessed through the Port A–H Control register by writing 03H to the Port A–H Address register. Setting the bits in the Port A–H Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

#### Table 18. Port A-H Output Control Sub-Registers

| BITS  | 7      | 6             | 5           | 4             | 3             | 2            | 1            | 0      |  |  |

|-------|--------|---------------|-------------|---------------|---------------|--------------|--------------|--------|--|--|

| FIELD | POC7   | POC6          | POC5        | POC4          | POC3          | POC2         | POC1         | POC0   |  |  |

| RESET | 0      |               |             |               |               |              |              |        |  |  |

| R/W   |        | R/W           |             |               |               |              |              |        |  |  |

| ADDR  | lf 03F | l in Port A–ł | H Address R | egister, acce | essible throu | igh Port A–⊦ | I Control Re | gister |  |  |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and disables the drains if set to 1.

0 = The drains are enabled for any output mode.

1 = The drain of the associated pin is disabled (open-drain mode).

#### Port A-H High Drive Enable Sub-Registers

The Port A–H High Drive Enable sub-register (Table 19) is accessed through the Port A–H Control register by writing 04H to the Port A–H Address register. Setting the bits in the Port A–H High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–H High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

One-Shot time-out, first set the TPOL bit in the Timer Control 1 Register to the start value before beginning ONE-SHOT mode. Then, after starting the timer, set TPOL to the opposite bit value.

Follow the steps below for configuring a timer for ONE-SHOT mode and initiating the count:

- 1. Write to the Timer Control 1 register to:

- Disable the timer

- Configure the timer for ONE-SHOT mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function

- 6. Write to the Timer Control 1 register to enable the timer and initiate counting

In ONE-SHOT mode, the system clock always provides the timer input. The timer period is given by the following equation:

ONE-SHOT Mode Time-Out Period (s) =  $\frac{(\text{Reload Value} - \text{Start Value}) \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon timer Reload.

Follow the steps below for configuring a timer for CONTINUOUS mode and initiating the count:

- 1. Write to the Timer Control 1 register to:

- Disable the timer

- Configure the timer for CONTINUOUS mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

The timer continues counting up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt and continues counting.

Follow the steps below for configuring a timer for CAPTURE mode and initiating the count:

- 1. Write to the Timer Control 1 register to:

- Disable the timer

- Configure the timer for CAPTURE mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, then the interrupt was generated by a Reload.

- 5. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control 1 register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### COMPARE Mode

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

### Table 42. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7 | 6   | 5 | 4          | 3          | 2 | 1 | 0 |  |  |

|-------|---|-----|---|------------|------------|---|---|---|--|--|

| FIELD |   | TRL |   |            |            |   |   |   |  |  |

| RESET |   | 1   |   |            |            |   |   |   |  |  |

| R/W   |   | R/W |   |            |            |   |   |   |  |  |

| ADDR  |   |     | F | 03H, F0BH, | F13H, F1BI | Н |   |   |  |  |

TRH and TRL-Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two byte form the 16-bit Compare value.

## Timer 0-3 PWM High and Low Byte Registers

The Timer 0-3 PWM High and Low Byte (TxPWMH and TxPWML) registers (see Table 43 and Table 44 on page 92) are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the Capture and Capture/COM-PARE modes.

### Table 43. Timer 0-3 PWM High Byte Register (TxPWMH)

| BITS  | 7    | 6   | 5 | 4          | 3         | 2 | 1 | 0 |  |

|-------|------|-----|---|------------|-----------|---|---|---|--|

| FIELD | PWMH |     |   |            |           |   |   |   |  |

| RESET | 0    |     |   |            |           |   |   |   |  |

| R/W   |      | R/W |   |            |           |   |   |   |  |

| ADDR  |      |     | F | 04H, F0CH, | F14H, F1C | Н |   |   |  |

### Table 44. Timer 0-3 PWM Low Byte Register (TxPWML)

| BITS  | 7    | 6   | 5 | 4          | 3         | 2 | 1 | 0 |  |  |

|-------|------|-----|---|------------|-----------|---|---|---|--|--|

| FIELD | PWML |     |   |            |           |   |   |   |  |  |

| RESET |      | 0   |   |            |           |   |   |   |  |  |

| R/W   |      | R/W |   |            |           |   |   |   |  |  |

| ADDR  |      |     | F | 05H, F0DH, | F15H, F1D | Н |   |   |  |  |

92

## zilog

5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All steps of the Watchdog Timer Reload Unlock sequence must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur, unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## Watchdog Timer Control Register Definitions

### Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register (Table 48) is a Read-Only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

Writing the 55H, AAH unlock sequence to the Watchdog Timer Control (WDTCTL) register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

| BITS  | 7     | 6                      | 5   | 4   | 3 2 1    |   |  | 0  |  |

|-------|-------|------------------------|-----|-----|----------|---|--|----|--|

| FIELD | POR   | STOP                   | WDT | EXT | Reserved |   |  | SM |  |

| RESET | See d | See descriptions below |     |     |          | 0 |  |    |  |

| R/W   |       | R                      |     |     |          |   |  |    |  |

| ADDR  |       |                        |     | FF  | 0H       |   |  |    |  |

| Table 48. V | Natchdog ' | Timer Control | Register | (WDTCTL) |

|-------------|------------|---------------|----------|----------|

|-------------|------------|---------------|----------|----------|

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCDCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

100

#### Table 55. UART Status 1 Register (UxSTAT1)

| BITS  | 7                    | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |

|-------|----------------------|---|---|---------|---------|---|---|---|--|

| FIELD | Reserved NEWFRM MPRX |   |   |         |         |   |   |   |  |

| RESET | 0                    |   |   |         |         |   |   |   |  |

| R/W   | R R/W R              |   |   |         |         |   | 2 |   |  |

| ADDR  |                      |   |   | F44H ar | nd F4CH |   |   |   |  |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

#### MPRX—Multiprocessor Receive

Returns the value of the last multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

#### **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (see Table 56 and Table 57 on page 118) configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

| BITS  | 7   | 6             | 5    | 4   | 3    | 2    | 1    | 0    |  |  |  |  |

|-------|-----|---------------|------|-----|------|------|------|------|--|--|--|--|

| FIELD | TEN | REN           | CTSE | PEN | PSEL | SBRK | STOP | LBEN |  |  |  |  |

| RESET |     | 0             |      |     |      |      |      |      |  |  |  |  |

| R/W   |     | R/W           |      |     |      |      |      |      |  |  |  |  |

| ADDR  |     | F42H and F4AH |      |     |      |      |      |      |  |  |  |  |

Table 56. UART Control 0 Register (UxCTL0)

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled.

1 = Transmitter enabled.

Table 64. SPI Control Register (SPICTL)

| BITS  | 7    | 6   | 5    | 4     | 3      | 2   | 1    | 0     |  |  |  |  |  |  |  |  |  |

|-------|------|-----|------|-------|--------|-----|------|-------|--|--|--|--|--|--|--|--|--|

| FIELD | IRQE | STR | BIRQ | PHASE | CLKPOL | WOR | MMEN | SPIEN |  |  |  |  |  |  |  |  |  |

| RESET |      | 0   |      |       |        |     |      |       |  |  |  |  |  |  |  |  |  |

| R/W   |      | R/W |      |       |        |     |      |       |  |  |  |  |  |  |  |  |  |

| ADDR  |      |     |      | F6    | 1H     |     |      | F61H  |  |  |  |  |  |  |  |  |  |

IRQE—Interrupt Request Enable

0 = SPI interrupts are disabled. No interrupt requests are sent to the Interrupt Controller.

1 = SPI interrupts are enabled. Interrupt requests are sent to the Interrupt Controller.

STR—Start an SPI Interrupt Request

0 = No effect.

1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART. Writing a 1 to the IRQ bit in the SPI Status register clears this bit to 0.

BIRQ-BRG Timer Interrupt Request

If the SPI is enabled, this bit has no effect. If the SPI is disabled:

0 = The Baud Rate Generator timer function is disabled.

1 = The Baud Rate Generator timer function and time-out interrupt are enabled.

PHASE—Phase Select

Sets the phase relationship of the data to the clock. For more information on operation of the PHASE bit, see SPI Clock Phase and Polarity Control on page 132.

CLKPOL—Clock Polarity

0 = SCK idles Low (0).

1 = SCK idle High (1).

WOR-Wire-OR (OPEN-DRAIN) Mode Enabled

0 = SPI signal pins not configured for open-drain.

$1 = \text{All four SPI signal pins (SCK, \overline{SS}, MISO, MOSI)}$  configured for open-drain function. This setting is typically used for multi-master and/or multi-slave configurations.

MMEN-SPI Master Mode Enable

0 = SPI configured in Slave mode.

1 = SPI configured in Master mode.

SPIEN—SPI Enable

0 = SPI disabled.

1 = SPI enabled.

## zilog

- 15. The  $I^2C$  Controller sends the repeated START condition.

- 16. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register (third address transfer).

- 17. The I<sup>2</sup>C Controller sends 11110B followed by the two most significant bits of the slave read address and a 1 (read).

- 18. The I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal Low during the next high period of SCL

If the slave were to Not Acknowledge at this point (this should not happen because the slave did acknowledge the first two address bytes), software would respond by setting the STOP and FLUSH bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore the following steps).

- 19. The I<sup>2</sup>C Controller shifts in a byte of data from the I<sup>2</sup>C slave on the SDA signal. The I<sup>2</sup>C Controller sends a Not Acknowledge to the I<sup>2</sup>C slave if the NAK bit is set (last byte), else it sends an Acknowledge.

- 20. The I<sup>2</sup>C Controller asserts the Receive interrupt (RDRF bit set in the Status register).

- 21. Software responds by reading the I<sup>2</sup>C Data register which clears the RDRF bit. If there is only one more byte to receive, set the NAK bit of the I<sup>2</sup>C Control register.

- 22. If there are one or more bytes to transfer, return to step 19.

- 23. After the last byte is shifted in, a Not Acknowledge interrupt is generated by the I<sup>2</sup>C Controller.

- 24. Software responds by setting the STOP bit of the  $I^2C$  Control register.

- 25. A STOP condition is sent to the  $I^2C$  slave and the STOP and NCKI bits are cleared.

## I<sup>2</sup>C Control Register Definitions

## I<sup>2</sup>C Data Register

The I<sup>2</sup>C Data register (see Table 70 on page 157) holds the data that is to be loaded into the I<sup>2</sup>C Shift register during a write to a slave. This register also holds data that is loaded from the I<sup>2</sup>C Shift register during a read from a slave. The I<sup>2</sup>C Shift Register is not accessible in the Register File address space, but is used only to buffer incoming and outgoing data.

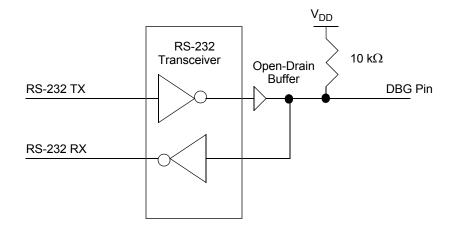

#### Figure 38. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

#### **DEBUG Mode**

The operating characteristics of the 64K Series devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The device enters DEBUG mode following any of the following operations:

- Writing the DBGMODE bit in the OCD Control Register to 1 using the OCD interface.

- eZ8 CPU execution of a BRK (Breakpoint) instruction (when enabled).

- If the DBG pin is Low when the device exits Reset, the On-Chip Debugger automatically puts the device into DEBUG mode.

#### **Exiting DEBUG Mode**

The device exits DEBUG mode following any of the following operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0.

- Power-On Reset

- Voltage Brownout reset

Table 110 list the Flash Memory electrical characteristics and timing.

| Table 110. Flash Memor | y Electrical Characteristics and | I Timing |

|------------------------|----------------------------------|----------|

|------------------------|----------------------------------|----------|

|                                               | V <sub>DD</sub> = 3.0-<br>T <sub>A</sub> = -40 ° |   | с       |        |                                                                                                                                                                   |  |  |  |

|-----------------------------------------------|--------------------------------------------------|---|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                     | Minimum Typical                                  |   | Maximum | Units  | Notes                                                                                                                                                             |  |  |  |

| Flash Byte Read Time                          | 50                                               | - | -       | ns     |                                                                                                                                                                   |  |  |  |

| Flash Byte Program Time                       | 20                                               | - | 40      | μs     |                                                                                                                                                                   |  |  |  |

| Flash Page Erase Time                         | 10                                               | _ | -       | ms     |                                                                                                                                                                   |  |  |  |

| Flash Mass Erase Time                         | 200                                              | - | _       | ms     |                                                                                                                                                                   |  |  |  |

| Writes to Single Address<br>Before Next Erase | _                                                | _ | 2       |        |                                                                                                                                                                   |  |  |  |

| Flash Row Program Time                        | _                                                | _ | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |  |  |  |

| Data Retention                                | 100                                              | - | -       | years  | 25 °C                                                                                                                                                             |  |  |  |

| Endurance, -40 °C to 105 °C                   | 10,000                                           | - | -       | cycles | Program/erase cycles                                                                                                                                              |  |  |  |

| Endurance, 106 °C to 125 °C                   | 1,000                                            | - | -       | cycles | Program/erase cycles                                                                                                                                              |  |  |  |

Table 111 lists the Watchdog Timer electrical characteristics and timing.

| Table 111. Watchdog | <b>Timer Electrica</b> | I Characteristics a | nd Timing |

|---------------------|------------------------|---------------------|-----------|

|---------------------|------------------------|---------------------|-----------|

|                  |                                                            | V <sub>DD</sub> = 3.0-<br>T <sub>A</sub> = -40 ° | -3.6 V<br>C to 125 ° | С       |       |            |  |

|------------------|------------------------------------------------------------|--------------------------------------------------|----------------------|---------|-------|------------|--|

| Symbol           | Parameter                                                  | Minimum                                          | Typical              | Maximum | Units | Conditions |  |

| F <sub>WDT</sub> | WDT Oscillator Frequency                                   | 5                                                | 10                   | 20      | kHz   |            |  |

| I <sub>WDT</sub> | WDT Oscillator Current<br>including internal RC oscillator | -                                                | < 1                  | 5       | μΑ    |            |  |

Table 112 provides electrical characteristics and timing information for the Analog-to-Digital Converter. Figure 49 displays the input frequency response of the ADC.

## **AC Characteristics**

The section provides information on the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs. Table 113 lists the 64K Series AC characteristics and timing.

#### Table 113. AC Characteristics

|                     |                                    |          | 3.0–3.6V<br>C to 125 °C |       |                                                                                                          |  |  |

|---------------------|------------------------------------|----------|-------------------------|-------|----------------------------------------------------------------------------------------------------------|--|--|

| Symbol              | Parameter                          | Minimum  | Maximum                 | Units | Conditions                                                                                               |  |  |

| F <sub>sysclk</sub> | System Clock Frequency             | _        | 20.0                    | MHz   | Read-only from Flash memory.                                                                             |  |  |

|                     |                                    | 0.032768 | 20.0                    | MHz   | Program or erasure of the Flash memory.                                                                  |  |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency       | 0.032768 | 20.0                    | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an external<br>clock driver. |  |  |

| T <sub>XIN</sub>    | Crystal Oscillator Clock<br>Period | 50       | -                       | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                 |  |  |

| T <sub>XINH</sub>   | System Clock High Time             | 20       |                         | ns    |                                                                                                          |  |  |

| T <sub>XINL</sub>   | System Clock Low Time              | 20       |                         | ns    |                                                                                                          |  |  |

| T <sub>XINR</sub>   | System Clock Rise Time             | -        | 3                       | ns    | T <sub>CLK</sub> = 50 ns. Slower rise times<br>can be tolerated with longer<br>clock periods.            |  |  |

| T <sub>XINF</sub>   | System Clock Fall Time             | -        | 3                       | ns    | T <sub>CLK</sub> = 50 ns. Slower fall times<br>can be tolerated with longer<br>clock periods.            |  |  |

## zilog

259

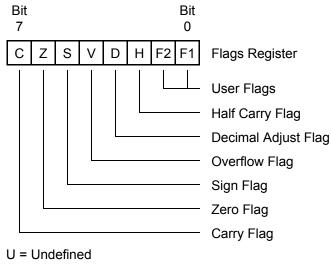

### **Flags Register**

The Flags Register contains the status information regarding the most recent arithmetic, logical, bit manipulation or rotate and shift operation. The Flags Register contains six bits of status information that are set or cleared by CPU operations. Four of the bits (C, V, Z and S) can be tested for use with conditional jump instructions. Two Flags (H and D) cannot be tested and are used for Binary-Coded Decimal (BCD) arithmetic.

The two remaining bits, User Flags (F1 and F2), are available as general-purpose status bits. User Flags are unaffected by arithmetic operations and must be set or cleared by instructions. The User Flags cannot be used with conditional Jumps. They are undefined at initial power-up and are unaffected by Reset. Figure 58 displays the Flags and their bit positions in the Flags Register.

Figure 58. Flags Register

Interrupts, the Software Trap (TRAP) instruction, and Illegal Instruction Traps all write the value of the Flags Register to the stack. Executing an Interrupt Return (IRET) instruction restores the value saved on the stack into the Flags Register.

263

|   | Lower Nibble (Hex)      |                           |                              |                                |                            |                             |                               |                                |                               |                                |                            |                          |                           |                           |                         |                          |

|---|-------------------------|---------------------------|------------------------------|--------------------------------|----------------------------|-----------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|--------------------------|

|   | 0                       | 1                         | 2                            | 3                              | 4                          | 5                           | 6                             | 7                              | 8                             | 9                              | А                          | В                        | С                         | D                         | Е                       | F                        |

| 0 | 1.2<br>BRK              | 2.2<br>SRP<br>IM          | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br><b>ADD</b><br>r1,lr2    | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br><b>ADD</b><br>IR2,R1 | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br><b>ADD</b><br>IR1,IM    | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1 | 2.3<br><b>RLC</b><br>IR1  | 2.3<br>ADC<br>r1,r2          | 2.4<br><b>ADC</b><br>r1,lr2    | 3.3<br><b>ADC</b><br>R2,R1 | 3.4<br>ADC<br>IR2,R1        | 3.3<br><b>ADC</b><br>R1,IM    | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                           |                           |                         | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1         | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br><b>SUB</b><br>IR2,R1 | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM           | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                           |                           |                         | 1,2<br><b>ATM</b>        |

| 3 | 2.2<br><b>DEC</b><br>R1 | 2.3<br><b>DEC</b><br>IR1  | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br>SBC<br>IR2,R1        | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                           |                           |                         |                          |

| 4 | 2.2<br><b>DA</b><br>R1  | 2.3<br><b>DA</b><br>IR1   | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br>ORX<br>ER2,ER1         | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                           |                           |                         |                          |

| 5 | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1  | 2.3<br><b>AND</b><br>r1,r2   | 2.4<br><b>AND</b><br>r1,lr2    | 3.3<br><b>AND</b><br>R2,R1 | 3.4<br><b>AND</b><br>IR2,R1 | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                           |                           |                         | <b>WDT</b>               |

| 6 | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1         | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1 | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                           |                           |                         | STOP                     |

| 7 | 2.2<br>PUSH<br>R2       | 2.3<br><b>PUSH</b><br>IR2 | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.2<br>HALT              |

| 8 | 2.5<br>DECW<br>RR1      | 2.6<br>DECW<br>IRR1       | 2.5<br>LDE<br>r1,Irr2        | 2.9<br>LDEI<br>Ir1,Irr2        | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2       | 3.4<br>LDX<br>IRR2,R1         | 3.5<br><b>LDX</b><br>IRR2,IR1  | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X         |                            |                          |                           |                           |                         | 1.2<br>DI                |

| 9 | 2.2                     | 2.3<br>RL<br>IR1          | 2.5<br>LDE<br>r2,Irr1        | 2.9<br>LDEI<br>Ir2,Irr1        | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br>LDX<br>R2,IRR1         | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br>LEA<br>r1,r2,X         | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                           |                           |                         | 1.2<br>El                |

| А | 2.5                     | 2.6<br>INCW               | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.4<br>RET               |

| В | 2.2                     | 2.3<br>CLR<br>IR1         | 2.3<br>XOR<br>r1,r2          | 2.4<br>XOR<br>r1,lr2           | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br>XOR<br>IR2,R1        | 3.3<br>XOR<br>R1,IM           | 3.4<br>XOR<br>IR1,IM           | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                          |                           |                           |                         | 1.5<br>IRET              |

| С | 2.2                     | 2.3<br>RRC<br>IR1         | 2.5<br>LDC<br>r1,lrr2        | 2.9<br>LDCI<br>Ir1,Irr2        | 2.3<br><b>JP</b><br>IRR1   | 2.9<br>LDC<br>lr1,lrr2      | ,                             | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           | ,                              |                            |                          |                           |                           |                         | 1.2<br>RCF               |

| C | 2.2                     | 2.3<br><b>SRA</b><br>IR1  | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>Ir2,Irr1 | 2.6<br>CALL<br>IRR1        | 2.2<br><b>BSWAP</b><br>R1   | 3.3<br>CALL<br>DA             | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                           |                           |                         | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1  | 2.3<br><b>RR</b><br>IR1   | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br><b>LDX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1       | 2.3<br><b>SWAP</b><br>IR1 | 2.6<br>TRAP<br>Vector        | 2.3<br><b>LD</b><br>lr1,r2     | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | ¥                          | ¥                        | V                         | V                         | V                       |                          |

Figure 60. First Opcode Map

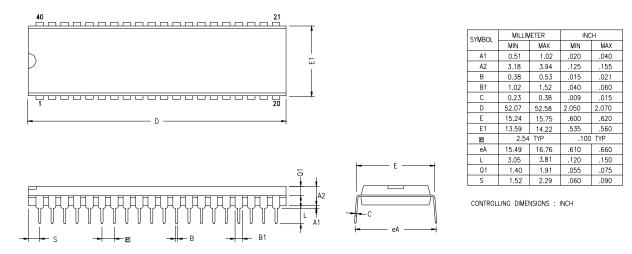

## Packaging

Figure 62 displays the 40-pin Plastic Dual-inline Package (PDIP) available for the Z8X1601, Z8X2401, Z8X3201, Z8X4801, and Z8X6401 devices.

Figure 62. 40-Lead Plastic Dual-Inline Package (PDIP)

283

Operational Description 103 OR 248 ordering information 270 ORX 248 oscillator signals 15

## Ρ

p 243 packaging LQFP 44 lead 266 64 lead 267 **PDIP 265** PLCC 44 lead 267 68 lead 268 **OFP 269** part number description 275 part selection guide 2 PC 244 **PDIP 265** peripheral AC and DC electrical characteristics 226 PHASE=0 timing (SPI) 133 PHASE=1 timing (SPI) 134 pin characteristics 16 PLCC 44 lead 267 68-lead 268 polarity 243 POP 248 pop using extended addressing 248 **POPX 248** port availability, device 57 port input timing (GPIO) 232 port output timing, GPIO 233 power supply signals 16 power-down, automatic (ADC) 176 power-on and voltage brown-out 226 power-on reset (POR) 49 program control instructions 249 program counter 244 program memory 20 **PUSH 248**

push using extended addressing 248 PUSHX 248 PWM mode 94 PxADDR register 61 PxCTL register 62

## Q

QFP 269

## R

R 243 r 243 RA register address 243 RCF 247 receive 10-bit data format (I2C) 154 7-bit data transfer format (I2C) 153 IrDA data 127 receive interrupt 145 receiving UART data-interrupt-driven method 108 receiving UART data-polled method 107 register 140, 169, 243 ADC control (ADCCTL) 179 ADC data high byte (ADCDH) 180 ADC data low bits (ADCDL) 180 baud low and high byte (I2C) 160, 161, 163 baud rate high and low byte (SPI) 142 control (SPI) 137 control, I2C 158 data, SPI 137 DMA status (DMAA STAT) 173 DMA ADC address 171 DMA ADC control DMAACTL) 172 DMAx address high nibble (DMAxH) 169 DMAx control (DMAxCTL) 167 DMAx end/address low byte (DMAxEND) 170 DMAx start/current address low byte register (DMAxSTART) 170 flash control (FCTL) 190 flash high and low byte (FFREQH and FRE-EQL) 192

## **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <a href="http://www.zilog.com/kb">http://www.zilog.com/kb</a>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.