Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 29                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f3221pm020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Manual Objectives xi                                                                                                            | ii     |

|---------------------------------------------------------------------------------------------------------------------------------|--------|

| About This Manualxi                                                                                                             |        |

| Manual Conventionsxi                                                                                                            |        |

| Introduction                                                                                                                    | 1      |

| Features       2         Part Selection Guide       2         Block Diagram       3         CPU and Peripheral Overview       3 | 2<br>3 |

| eZ8 <sup>™</sup> CPU Features                                                                                                   |        |

| General-Purpose Input/Output                                                                                                    |        |

| Flash Controller    4      10-Bit Analog-to-Digital Converter    4                                                              |        |

| UARTs                                                                                                                           |        |

| I <sup>2</sup> C Serial Peripheral Interface                                                                                    |        |

| Timers                                                                                                                          | 5      |

| Reset Controller    8      On-Chip Debugger    8      DMA Controller    8                                                       | 5<br>5 |

| Signal and Pin Descriptions                                                                                                     |        |

| Overview       7         Available Packages       7         Pin Configurations       8                                          | 7<br>7 |

| Pin Configurations       14         Signal Descriptions       14         Pin Characteristics       16                           | 4      |

| Address Space                                                                                                                   | 9      |

| Overview       19         Register File       19         Program Memory       20         Data Memory       21                   | 9<br>0 |

| Data Memory 2'                                                                                                                  | 1      |

# zilog

# Table 6. Z8 Encore! XP 64K Series Flash Microcontrollers Information Area Map

| Program Memory<br>Address (Hex) | Function                                                                                                           |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------|

| FE00H-FE3FH                     | Reserved                                                                                                           |

| FE40H-FE53H                     | Part Number<br>20-character ASCII alphanumeric code<br>Left justified and filled with zeros (ASCII Null character) |

| FE54H-FFFFH                     | Reserved                                                                                                           |

22

# zilog

26

|             | De vieten De e evintier                 | -<br>M   |             | Dana Ma |

|-------------|-----------------------------------------|----------|-------------|---------|

|             | Register Description                    | Mnemonic | Reset (Hex) | Page No |

| FCD         | Interrupt Edge Select                   | IRQES    | 00          | 78      |

| FCE         | Interrupt Port Select                   | IRQPS    | 00          | 78      |

| FCF         | Interrupt Control                       | IRQCTL   | 00          | 79      |

| GPIO Port A |                                         |          |             |         |

| FD0         | Port A Address                          | PAADDR   | 00          | 61      |

| FD1         | Port A Control                          | PACTL    | 00          | 62      |

| FD2         | Port A Input Data                       | PAIN     | XX          | 66      |

| FD3         | Port A Output Data                      | PAOUT    | 00          | 66      |

| GPIO Port B |                                         |          |             |         |

| FD4         | Port B Address                          | PBADDR   | 00          | 61      |

| FD5         | Port B Control                          | PBCTL    | 00          | 62      |

| FD6         | Port B Input Data                       | PBIN     | XX          | 66      |

| FD7         | Port B Output Data                      | PBOUT    | 00          | 66      |

| GPIO Port C |                                         |          |             |         |

| FD8         | Port C Address                          | PCADDR   | 00          | 61      |

| FD9         | Port C Control                          | PCCTL    | 00          | 62      |

| FDA         | Port C Input Data                       | PCIN     | XX          | 66      |

| FDB         | Port C Output Data                      | PCOUT    | 00          | 66      |

| GPIO Port D |                                         |          |             |         |

| FDC         | Port D Address                          | PDADDR   | 00          | 61      |

| FDD         | Port D Control                          | PDCTL    | 00          | 62      |

| FDE         | Port D Input Data                       | PDIN     | XX          | 66      |

| FDF         | Port D Output Data                      | PDOUT    | 00          | 66      |

| GPIO Port E |                                         |          |             |         |

| FE0         | Port E Address                          | PEADDR   | 00          | 61      |

| FE1         | Port E Control                          | PECTL    | 00          | 62      |

| FE2         | Port E Input Data                       | PEIN     | XX          | 66      |

| FE3         | Port E Output Data                      | PEOUT    | 00          | 66      |

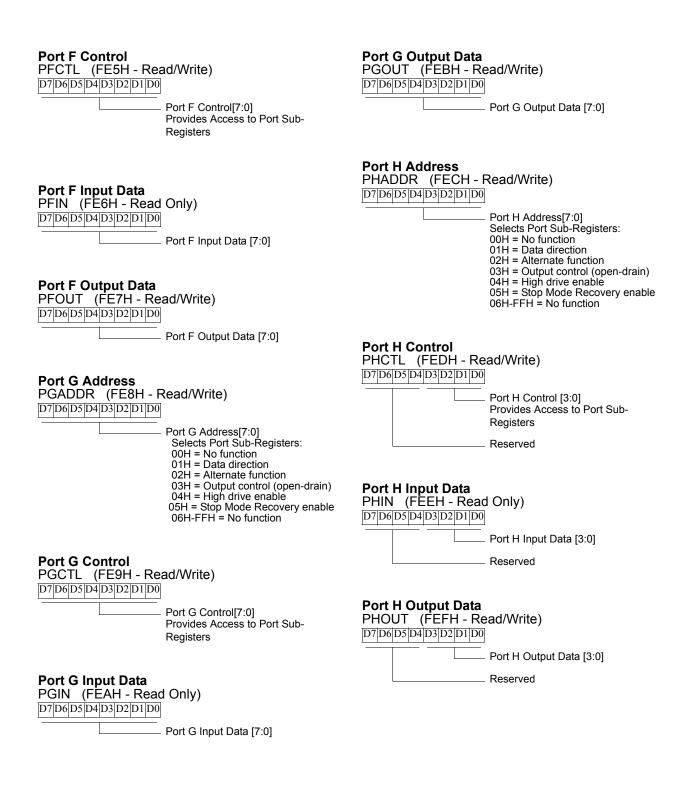

| GPIO Port F |                                         |          |             |         |

| FE4         | Port F Address                          | PFADDR   | 00          | 61      |

| FE5         | Port F Control                          | PFCTL    | 00          | 62      |

| FE6         | Port F Input Data                       | PFIN     | XX          | 66      |

| FE7         | Port F Output Data                      | PFOUT    | 00          | 66      |

| GPIO Port G | · · · · · · · · · · · · · · · · · · ·   |          |             |         |

| FE8         | Port G Address                          | PGADDR   | 00          | 61      |

| FE9         | Port G Control                          | PGCTL    | 00          | 62      |

| FEA         | Port G Input Data                       | PGIN     | XX          | 66      |

| FEB         | Port G Output Data                      | PGOUT    | 00          | 66      |

| GPIO Port H | · ·                                     |          |             |         |

| FEC         | Port H Address                          | PHADDR   | 00          | 61      |

| FED         | Port H Control                          | PHCTL    | 00          | 62      |

| FEE         | Port H Input Data                       | PHIN     | XX          | 66      |

|             | - · · · · · · · · · · · · · · · · · · · |          |             |         |

Table 7. Z8 Encore! XP 64K Series Flash Microcontrollers Register File Address Map (Continued)

## Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

# zilog

## Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

|                       | Reset Characteristics and Latency      |                       |                                                   |  |  |  |  |

|-----------------------|----------------------------------------|-----------------------|---------------------------------------------------|--|--|--|--|

| Reset Type            | Control Registers                      | eZ8 <sup>TM</sup> CPU | Reset Latency (Delay)                             |  |  |  |  |

| System reset          | Reset (as applicable)                  | Reset                 | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except<br>WDT_CTL register | Reset                 | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |  |

### System Reset

During a system reset, the 64K Series devices are held in Reset for 66 cycles of the Watchdog Timer oscillator followed by 16 cycles of the system clock. At the beginning of Reset, all GPIO pins are configured as inputs.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run. The system clock begins operating following the Watchdog Timer oscillator cycle count. The eZ8 CPU and on-chip peripherals remain idle through the 16 cycles of the system clock.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

# **Reset Sources**

Table 9 lists the reset sources as a function of the operating mode. The text following provides more detailed information on the individual Reset sources. A Power-On Reset/Voltage Brownout event always takes priority over all other possible reset sources to ensure a full system reset occurs.

# **Low-Power Modes**

# **Overview**

The 64K Series products contain power-saving features. The highest level of power reduction is provided by STOP mode. The next level of power reduction is provided by the HALT mode.

# **STOP Mode**

Execution of the eZ8<sup>™</sup> CPU's STOP instruction places the device into STOP mode. In STOP mode, the operating characteristics are:

- Primary crystal oscillator is stopped; the XIN pin is driven High and the XOUT pin is driven Low.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- The Watchdog Timer and its internal RC oscillator continue to operate, if enabled for operation during STOP mode.

- The Voltage Brownout protection circuit continues to operate, if enabled for operation in STOP mode using the associated Option Bit.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND), the Voltage Brownout protection must be disabled, and the Watchdog Timer must be disabled. The devices can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 47.

**Caution:** STOP mode must not be used when driving the 64K Series devices with an external clock driver source.

# **General-Purpose I/O**

# **Overview**

The 64K Series products support a maximum of seven 8-bit ports (Ports A–G) and one 4-bit port (Port H) for general-purpose input/output (GPIO) operations. Each port consists of control and data registers. The GPIO control registers are used to determine data direction, open-drain, output drive current and alternate pin functions. Each port pin is individually programmable. All ports (except B and H) support 5 V-tolerant inputs.

# **GPIO Port Availability By Device**

Table 11 lists the port pins available with each device and package type.

| Device  | Packages       | Port A | Port B | Port C | Port D               | Port E | Port F | Port G | Port H |

|---------|----------------|--------|--------|--------|----------------------|--------|--------|--------|--------|

| Z8X1621 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | <u>[6:3,</u><br>1:0] | -      | -      | -      | -      |

| Z8X1621 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]                | -      | -      | -      | -      |

| Z8X1622 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]                | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8X2421 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | <u>[6:3,</u><br>1:0] | -      | -      | -      |        |

| Z8X2421 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]                | -      | -      | -      | -      |

| Z8X2422 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]                | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8X3221 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | <u>[6:3,</u><br>1:0] | -      | -      | -      | -      |

| Z8X3221 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]                | -      | -      | -      | -      |

| Z8X3222 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]                | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8X4821 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | <u>[6:3,</u><br>1:0] | -      | -      | -      | -      |

| Z8X4821 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]                | -      | -      | -      | -      |

| Z8X4822 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]                | [7:0]  | [7]    | [3]    | [3:0]  |

#### Table 11. Port Availability by Device and Package Type

| Port   | Pin     | Mnemonic   | Alternate Function Description               |

|--------|---------|------------|----------------------------------------------|

| Port C | PC0     | T1IN       | Timer 1 Input                                |

|        | PC1     | T1OUT      | Timer 1 Output                               |

|        | PC2     | SS         | SPI Slave Select                             |

|        | PC3     | SCK        | SPI Serial Clock                             |

|        | PC4     | MOSI       | SPI Master Out/Slave In                      |

|        | PC5     | MISO       | SPI Master In/Slave Out                      |

|        | PC6     | T2IN       | Timer 2 In                                   |

|        | PC7     | T2OUT      | Timer 2 Out                                  |

| Port D | PD0     | T3IN       | Timer 3 In (unavailable in 44-pin packages)  |

|        | PD1     | T3OUT      | Timer 3 Out (unavailable in 44-pin packages) |

|        | PD2     | N/A        | No alternate function                        |

|        | PD3     | DE1        | UART 1 Driver Enable                         |

|        | PD4     | RXD1/IRRX1 | UART 1/IrDA 1 Receive Data                   |

|        | PD5     | TXD1/IRTX1 | UART 1/IrDA 1 Transmit Data                  |

|        | PD6     | CTS1       | UART 1 Clear to Send                         |

|        | PD7     | RCOUT      | Watchdog Timer RC Oscillator Output          |

| Port E | PE[7:0] | N/A        | No alternate functions                       |

| Port F | PF[7:0] | N/A        | No alternate functions                       |

| Port G | PG[7:0] | N/A        | No alternate functions                       |

| Port H | PH0     | ANA8       | ADC Analog Input 8                           |

|        | PH1     | ANA9       | ADC Analog Input 9                           |

|        | PH2     | ANA10      | ADC Analog Input 10                          |

|        | PH3     | ANA11      | ADC Analog Input 11                          |

| -      |         |            |                                              |

Table 12. Port Alternate Function Mapping (Continued)

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins may be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupts generate an interrupt when any edge occurs (both rising and falling). For more information on interrupts using the GPIO pins, see Interrupt Controller on page 67.

PADxI—Port A or Port D Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Port D pin *x*.

1 = An interrupt request from GPIO Port A or Port D pin x is awaiting service.

where *x* indicates the specific GPIO Port pin number (0 through 7). For each pin, only 1 of either Port A or Port D can be enabled for interrupts at any one time. Port selection (A or D) is determined by the values in the Interrupt Port Select Register.

### Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) register (Table 26) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

| BITS  | 7   | 6     | 5     | 4    | 3    | 2    | 1    | 0    |  |

|-------|-----|-------|-------|------|------|------|------|------|--|

| FIELD | T3I | U1RXI | U1TXI | DMAI | PC3I | PC2I | PC1I | PC0I |  |

| RESET | 0   |       |       |      |      |      |      |      |  |

| R/W   | R/W |       |       |      |      |      |      |      |  |

| ADDR  |     |       |       | FC   | 6H   |      |      |      |  |

Table 26. Interrupt Request 2 Register (IRQ2)

T3I—Timer 3 Interrupt Request

0 = No interrupt request is pending for Timer 3.

1 = An interrupt request from Timer 3 is awaiting service.

U1RXI—UART 1 Receive Interrupt Request

0 = No interrupt request is pending for the UART1 receiver.

1 = An interrupt request from UART1 receiver is awaiting service.

U1TXI-UART 1 Transmit Interrupt Request

0 = No interrupt request is pending for the UART 1 transmitter.

1 = An interrupt request from the UART 1 transmitter is awaiting service.

DMAI—DMA Interrupt Request

0 = No interrupt request is pending for the DMA.

1 = An interrupt request from the DMA is awaiting service.

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x.

1 = An interrupt request from GPIO Port C pin x is awaiting service.

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control 1 register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the *first* external Timer Input transition. The desired transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control 1 Register. The timer input is the system clock.

Every subsequent desired transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control 1 register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 01 = The UART generates an interrupt request only on received address bytes.

- 10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

- 11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—MULTIPROCESSOR Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled.

- 0 = Send a 0 in the multiprocessor bit location of the data stream (9<sup>th</sup> bit).

- 1 = Send a 1 in the multiprocessor bit location of the data stream (9<sup>th</sup> bit).

#### DEPOL—Driver Enable Polarity

- 0 = DE signal is Active High.

- 1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes different UART behavior depending on whether the UART receiver is enabled (REN = 1 in the UART Control 0 Register).

When the UART receiver is not enabled, this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value

1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled, this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

- 0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.

- 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the High Byte when the Low Byte is read.

RDAIRQ—Receive Data Interrupt Enable

- 0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

- 1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 =Infrared Encoder/Decoder is disabled. UART operates normally operation.

# zilog

- 120

- 1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

# **UART Address Compare Register**

The UART Address Compare register (Table 58) stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

## Table 58. UART Address Compare Register (UxADDR)

| BITS  | 7 | 6         | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|-------|---|-----------|---|---------|---------|---|---|---|--|--|

| FIELD |   | COMP_ADDR |   |         |         |   |   |   |  |  |

| RESET | 0 |           |   |         |         |   |   |   |  |  |

| R/W   |   | R/W       |   |         |         |   |   |   |  |  |

| ADDR  |   |           |   | F45H ar | nd F4DH |   |   |   |  |  |

COMP\_ADDR—Compare Address

This 8-bit value is compared to the incoming address bytes.

# UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (see Table 59 and Table 60 on page 121) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the desired 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the UART BRG interrupt interval is calculated using the following equation:

UART BRG Interrupt Interval(s) = System Clock Period (s) × BRG[15:0]

# Table 59. UART Baud Rate High Byte Register (UxBRH)

| BITS  | 7 | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|-------|---|-----|---|---------|---------|---|---|---|--|--|

| FIELD |   | BRH |   |         |         |   |   |   |  |  |

| RESET |   | 1   |   |         |         |   |   |   |  |  |

| R/W   |   | R/W |   |         |         |   |   |   |  |  |

| ADDR  |   |     |   | F46H ar | nd F4EH |   |   |   |  |  |

# Table 60. UART Baud Rate Low Byte Register (UxBRL)

| BITS  | 7   | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |

|-------|-----|-----|---|---------|---------|---|---|---|--|

| FIELD | BRL |     |   |         |         |   |   |   |  |

| RESET | 1   |     |   |         |         |   |   |   |  |

| R/W   |     | R/W |   |         |         |   |   |   |  |

| ADDR  |     |     |   | F47H ar | nd F4FH |   |   |   |  |

For a given UART data rate, the integer baud rate divisor value is calculated using the following equation:

UART Baud Rate Divisor Value (BRG) =  $Round\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the desired baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 61 provides information on data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

# zilog

defined to be 1 through 8 bits by the NUMBITS field in the SPI Mode register. In slave mode it is not necessary for  $\overline{SS}$  to deassert between characters to generate the interrupt. The SPI in Slave mode can also generate an interrupt if the  $\overline{SS}$  signal deasserts prior to transfer of all the bits in a character (see description of slave abort error above). Writing a 1 to the IRQ bit in the SPI Status Register clears the pending SPI interrupt request. The IRQ bit must be cleared to 0 by the Interrupt Service Routine to generate future interrupts. To start the transfer process, an SPI interrupt may be forced by software writing a 1 to the STR bit in the SPICTL register.

If the SPI is disabled, an SPI interrupt can be generated by a Baud Rate Generator timeout. This timer function must be enabled by setting the BIRQ bit in the SPICTL register. This Baud Rate Generator time-out does not set the IRQ bit in the SPISTAT register, just the SPI interrupt bit in the interrupt controller.

#### **SPI Baud Rate Generator**

In SPI Master mode, the Baud Rate Generator creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the Baud Rate Generator is the system clock. The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The SPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$

Minimum baud rate is obtained by setting BRG[15:0] to 0000H for a clock divisor value of (2 X 65536 = 131072).

When the SPI is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the SPI by clearing the SPIEN bit in the SPI Control register to 0.

- 2. Load the desired 16-bit count value into the SPI Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the SPI Control register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

Transmit interrupts occur when the TDRE bit of the  $I^2C$  Status register sets and the TXI bit in the  $I^2C$  Control register is set. Transmit interrupts occur under the following conditions when the transmit data register is empty:

- The I<sup>2</sup>C Controller is enabled.

- The first bit of the byte of an address is shifting out and the RD bit of the I<sup>2</sup>C Status register is deasserted.

- The first bit of a 10-bit address shifts out.

- The first bit of write data shifts out.

**Note:** Writing to the  $l^2C$  Data register always clears the TRDE bit to 0. When TDRE is asserted, the  $l^2C$  Controller pauses at the beginning of the Acknowledge cycle of the byte currently shifting out until the Data register is written with the next value to send or the STOP or START bits are set indicating the current byte is the last one to send.

The fourth interrupt source is the baud rate generator. If the I<sup>2</sup>C Controller is disabled (IEN bit in the I2CCTL register = 0) and the BIRQ bit in the I2CCTL register = 1, an interrupt is generated when the baud rate generator counts down to 1. This allows the I<sup>2</sup>C baud rate generator to be used by software as a general purpose timer when IEN = 0.

# Software Control of I<sup>2</sup>C Transactions

Software can control  $I^2C$  transactions by using the  $I^2C$  Controller interrupt, by polling the  $I^2C$  Status register or by DMA. Note that not all products include a DMA Controller.

To use interrupts, the  $I^2C$  interrupt must be enabled in the Interrupt Controller. The TXI bit in the  $I^2C$  Control register must be set to enable transmit interrupts.

To control transactions by polling, the interrupt bits (TDRE, RDRF and NCKI) in the I<sup>2</sup>C Status register should be polled. The TDRE bit asserts regardless of the state of the TXI bit.

Either or both transmit and receive data movement can be controlled by the DMA Controller. The DMA Controller channel(s) must be initialized to select the I<sup>2</sup>C transmit and receive requests. Transmit DMA requests require that the TXI bit in the I<sup>2</sup>C Control register be set.

**Caution:** A transmit (write) DMA operation hangs if the slave responds with a Not Acknowledge before the last byte has been sent. After receiving the Not Acknowledge, the I<sup>2</sup>C Controller sets the NCKI bit in the Status register and pauses until either the STOP or START bits in the Control register are set.

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

# 236

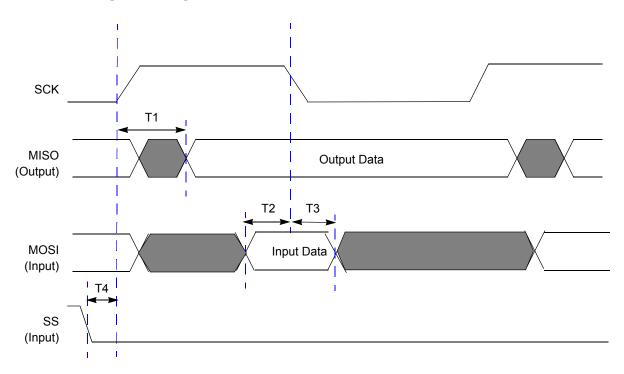

# **SPI Slave Mode Timing**

Figure 54 and Table 118 provide timing information for the SPI slave mode pins. Timing is shown with SCK rising edge used to source MISO output data, SCK falling edge used to sample MOSI input data.

# Figure 54. SPI Slave Mode Timing

### Table 118. SPI Slave Mode Timing

| Parameter      |                                                | Delay (ns)        |                                |  |  |

|----------------|------------------------------------------------|-------------------|--------------------------------|--|--|

|                | Abbreviation                                   | Minimum           | Maximum                        |  |  |

| SPI Slave      |                                                |                   |                                |  |  |

| T <sub>1</sub> | SCK (transmit edge) to MISO output Valid Delay | 2 * Xin<br>period | 3 * Xin<br>period +<br>20 nsec |  |  |

| T <sub>2</sub> | MOSI input to SCK (receive edge) Setup Time    | 0                 |                                |  |  |

| T <sub>3</sub> | MOSI input to SCK (receive edge) Hold Time     | 3 * Xin<br>period |                                |  |  |

| T <sub>4</sub> | SS input assertion to SCK setup                | 1 * Xin<br>period |                                |  |  |

| Assembly<br>Mnemonic        | Symbolic Operation                                                                                                                        | Address<br>Mode |     | _ Opcode(s) |   |   | Fla | ags | - Fetch | Inchr |        |                  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-------------|---|---|-----|-----|---------|-------|--------|------------------|

|                             |                                                                                                                                           | dst             | src | (Hex)       | С | Ζ | S   | V   | D       | Н     | Cycles | Instr.<br>Cycles |

| COM dst                     | dst ← ~dst                                                                                                                                | R               |     | 60          | - | * | *   | 0   | -       | -     | 2      | 2                |

|                             | -                                                                                                                                         | IR              |     | 61          |   |   |     |     |         |       | 2      | 3                |

| CP dst, src                 | dst - src                                                                                                                                 | r               | r   | A2          | * | * | *   | *   | -       | -     | 2      | 3                |

|                             | -                                                                                                                                         | r               | lr  | A3          | • |   |     |     |         |       | 2      | 4                |

|                             |                                                                                                                                           | R               | R   | A4          | • |   |     |     |         |       | 3      | 3                |

|                             |                                                                                                                                           | R               | IR  | A5          | • |   |     |     |         |       | 3      | 4                |

|                             |                                                                                                                                           | R               | IM  | A6          | • |   |     |     |         |       | 3      | 3                |

|                             |                                                                                                                                           | IR              | IM  | A7          | • |   |     |     |         |       | 3      | 4                |

| CPC dst, src                | dst - src - C                                                                                                                             | r               | r   | 1F A2       | * | * | *   | *   | -       | -     | 3      | 3                |

|                             |                                                                                                                                           | r               | lr  | 1F A3       | • |   |     |     |         |       | 3      | 4                |

|                             |                                                                                                                                           | R               | R   | 1F A4       | • |   |     |     |         |       | 4      | 3                |

|                             | -                                                                                                                                         | R               | IR  | 1F A5       | • |   |     |     |         |       | 4      | 4                |

|                             |                                                                                                                                           | R               | IM  | 1F A6       | • |   |     |     |         |       | 4      | 3                |

|                             |                                                                                                                                           | IR              | IM  | 1F A7       | • |   |     |     |         |       | 4      | 4                |

| CPCX dst, src dst - src - C |                                                                                                                                           | ER              | ER  | 1F A8       | * | * | *   | *   | -       | -     | 5      | 3                |

|                             |                                                                                                                                           | ER              | IM  | 1F A9       | • |   |     |     |         |       | 5      | 3                |

| CPX dst, src                | dst - src                                                                                                                                 | ER              | ER  | A8          | * | * | *   | *   | -       | -     | 4      | 3                |

|                             |                                                                                                                                           | ER              | IM  | A9          | • |   |     |     |         |       | 4      | 3                |

| DA dst                      | $dst \leftarrow DA(dst)$                                                                                                                  | R               |     | 40          | * | * | *   | Х   | -       | -     | 2      | 2                |

|                             |                                                                                                                                           | IR              |     | 41          | • |   |     |     |         |       | 2      | 3                |

| DEC dst                     | dst ← dst - 1                                                                                                                             | R               |     | 30          | - | * | *   | *   | -       | -     | 2      | 2                |

|                             | -                                                                                                                                         | IR              |     | 31          | • |   |     |     |         |       | 2      | 3                |

| DECW dst                    | dst ← dst - 1                                                                                                                             | RR              |     | 80          | - | * | *   | *   | -       | -     | 2      | 5                |

|                             | -                                                                                                                                         | IRR             |     | 81          | • |   |     |     |         |       | 2      | 6                |

| DI                          | $IRQCTL[7] \leftarrow 0$                                                                                                                  |                 |     | 8F          | - | - | -   | -   | -       | -     | 1      | 2                |

| DJNZ dst, RA                | $\begin{array}{l} \text{dst} \leftarrow \text{dst} - 1 \\ \text{if } \text{dst} \neq 0 \\ \text{PC} \leftarrow \text{PC} + X \end{array}$ | r               |     | 0A-FA       | - | - | -   | -   | -       | -     | 2      | 3                |

# Table 133. eZ8 CPU Instruction Summary (Continued)

270

# **Ordering Information**

| Part Number                                                  | Flash | RAM  | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I²C | SPI | UARTs with IrDA | Description         |  |

|--------------------------------------------------------------|-------|------|-----------|------------|---------------------|---------------------|-----|-----|-----------------|---------------------|--|

| Z8F642x with 64 KB Flash, 10-Bit Analog-to-Digital Converter |       |      |           |            |                     |                     |     |     |                 |                     |  |

| Standard Temperature: 0 °C                                   |       |      |           |            |                     |                     |     |     |                 |                     |  |

| Z8F6421PM020SC                                               | 64 KB | 4 KB | 29        | 23         | 3                   | 8                   | 1   | 1   | 2               | PDIP 40-pin package |  |

| Z8F6421AN020SC                                               | 64 KB | 4 KB | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | LQFP 44-pin package |  |

| Z8F6421VN020SC                                               | 64 KB | 4 KB | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | PLCC 44-pin package |  |

| Z8F6422AR020SC                                               | 64 KB | 4 KB | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | LQFP 64-pin package |  |

| Z8F6422VS020SC                                               | 64 KB | 4 KB | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | PLCC 68-pin package |  |

| Z8F6423FT020SC                                               | 64 KB | 4 KB | 60        | 24         | 4                   | 12                  | 1   | 1   | 2               | QFP 80-pin package  |  |

| Extended Temperature: -40 °C to +105 °C                      |       |      |           |            |                     |                     |     |     |                 |                     |  |

| Z8F6421PM020EC                                               | 64 KB | 4 KB | 29        | 23         | 3                   | 8                   | 1   | 1   | 2               | PDIP 40-pin package |  |

| Z8F6421AN020EC                                               | 64 KB | 4 KB | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | LQFP 44-pin package |  |

| Z8F6421VN020EC                                               | 64 KB | 4 KB | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | PLCC 44-pin package |  |

| Z8F6422AR020EC                                               | 64 KB | 4 KB | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | LQFP 64-pin package |  |

| Z8F6422VS020EC                                               | 64 KB | 4 KB | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | PLCC 68-pin package |  |

| Z8F6423FT020EC                                               | 64 KB | 4 KB | 60        | 24         | 4                   | 12                  | 1   | 1   | 2               | QFP 80-pin package  |  |

| Automotive/Industrial Temperature: -40 °C to +125 °C         |       |      |           |            |                     |                     |     |     |                 |                     |  |

| Z8F6421PM020AC                                               | 64 KB | 4 KB | 29        | 23         | 3                   | 8                   | 1   | 1   | 2               | PDIP 40-pin package |  |

| Z8F6421AN020AC                                               | 64 KB | 4 KB | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | LQFP 44-pin package |  |

| Z8F6421VN020AC                                               | 64 KB | 4 KB | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | PLCC 44-pin package |  |

| Z8F6422AR020AC                                               | 64 KB | 4 KB | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | LQFP 64-pin package |  |

| Z8F6422VS020AC                                               | 64 KB | 4 KB | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | PLCC 68-pin package |  |

| Z8F6423FT020AC                                               | 64 KB | 4 KB | 60        | 24         | 4                   | 12                  | 1   | 1   | 2               | QFP 80-pin package  |  |

Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

280

I2CBRL register 161 I2CCTL register 158 I2CDATA register 157 I2CSTAT register 157 IM 243 immediate data 243 immediate operand prefix 244 **INC 246** increment 246 increment word 246 **INCW 246** indexed 243 indirect address prefix 244 indirect register 243 indirect register pair 243 indirect working register 243 indirect working register pair 243 infrared encoder/decoder (IrDA) 125 instruction set, ez8 CPU 241 instructions ADC 246 ADCX 246 ADD 246 ADDX 246 AND 248 **ANDX 248** arithmetic 246 **BCLR 246** BIT 246 bit manipulation 246 block transfer 247 **BRK 249** BSET 246 BSWAP 247, 249 BTJ 249 **BT.INZ 249 BTJZ 249 CALL 249** CCF 247 **CLR 248** COM 248 CP 246 CPC 246 **CPCX 246**

CPU control 247 CPX 246 DA 246 **DEC 246 DECW 246** DI 247 **DJNZ 249** EI 247 HALT 247 **INC 246** INCW 246 **IRET 249** JP 249 LD 248 LDC 248 LDCI 247, 248 LDE 248 **LDEI 247** LDX 248 LEA 248 load 248 logical 248 **MULT 246** NOP 247 OR 248 **ORX 248** POP 248 **POPX 248** program control 249 **PUSH 248** PUSHX 248 **RCF 247 RET 249** RL 249 RLC 249 rotate and shift 249 RR 249 **RRC 249** SBC 246 SCF 247 SRA 249 SRL 250 SRP 247 **STOP 248**