Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | •                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | · .                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f3222ar020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Signal Descriptions**

Table 3 describes the Z8 Encore! XP signals. To determine the signals available for the specific package styles, see Pin Configurations on page 8.

# Table 3. Signal Descriptions

| Signal<br>Mnemonic          | I/O        | Description                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purp                | ose I/O Po | rts A-H                                                                                                                                                                                                                                                                                                                                                 |

| PA[7:0]                     | I/O        | Port A[7:0]. These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                                                                                               |

| PB[7:0]                     | I/O        | Port B[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                                                               |

| PC[7:0]                     | I/O        | Port C[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs                                                                                                                                                                                                                   |

| PD[7:0]                     | I/O        | Port D[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs                                                                                                                                                                                                                   |

| PE[7:0]                     | I/O        | Port E[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                                                  |

| PF[7:0]                     | I/O        | Port F[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                                                  |

| PG[7:0]                     | I/O        | Port G[7:0]. These pins are used for general-purpose I/O. These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                                                  |

| PH[3:0]                     | I/O        | Port H[3:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                                                               |

| I <sup>2</sup> C Controller |            |                                                                                                                                                                                                                                                                                                                                                         |

| SCL                         | 0          | Serial Clock. This is the output clock for the I <sup>2</sup> C. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SCL function, this pin is open-drain.                                                                                                      |

| SDA                         | I/O        | Serial Data. This open-drain pin transfers data between the I <sup>2</sup> C and a slave. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SDA function, this pin is open-drain.                                                                             |

| SPI Controller              | r          |                                                                                                                                                                                                                                                                                                                                                         |

| SS                          | I/O        | Slave Select. This signal can be an output or an input. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI master, this pin may be configured as the Slave Select output. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI slave, this pin is the input slave select. It is multiplexed with a general-purpose I/O pin. |

# zilog

# Table 3. Signal Descriptions (Continued)

| Signal<br>Mnemonic          | I/O | Description                                                                                                                                                                                                                                                                                            |

|-----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK                         | I/O | SPI Serial Clock. The SPI master supplies this pin. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI master, this pin is an output. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI slave, this pin is an input. It is multiplexed with a general-purpose I/O pin.  |

| MOSI                        | I/O | Master-Out/Slave-In. This signal is the data output from the SPI master device and the data input to the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                                           |

| MISO                        | I/O | Master-In/Slave-Out. This pin is the data input to the SPI master device and the data output from the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                                              |

| UART Controlle              | ers |                                                                                                                                                                                                                                                                                                        |

| TXD0 / TXD1                 | 0   | Transmit Data. These signals are the transmit outputs from the UARTs. The TXD signals are multiplexed with general-purpose I/O pins.                                                                                                                                                                   |

| RXD0/RXD1 I                 |     | Receive Data. These signals are the receiver inputs for the UARTs and IrDAs. The RXD signals are multiplexed with general-purpose I/O pins.                                                                                                                                                            |

| CTS0 / CTS1                 | Ι   | Clear To Send. These signals are control inputs for the UARTs. The $\overline{\text{CTS}}$ signals are multiplexed with general-purpose I/O pins.                                                                                                                                                      |

| DE0 / DE1                   | 0   | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the Transmit Empty (TXE) bit in the UART Status 0 register. The DE signal may be used to ensure an external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                      |     |                                                                                                                                                                                                                                                                                                        |

| T0OUT/T1OUT/<br>T2OUT/T3OUT | 0   | Timer Output 0-3. These signals are output pins from the timers. The Timer Output signals are multiplexed with general-purpose I/O pins. T3OUT is not available in 44-pin package devices.                                                                                                             |

| T0IN/T1IN/<br>T2IN/T3IN     | Ι   | Timer Input 0-3. These signals are used as the capture, gating and counter inputs. The Timer Input signals are multiplexed with general-purpose I/O pins. T3IN is not available in 44-pin package devices.                                                                                             |

| Analog                      |     |                                                                                                                                                                                                                                                                                                        |

| ANA[11:0]                   | Ι   | Analog Input. These signals are inputs to the ADC. The ADC analog inputs are multiplexed with general-purpose I/O pins.                                                                                                                                                                                |

| VREF                        | Ι   | Analog-to-Digital converter reference voltage input. The VREF pin must be left unconnected (or capacitively coupled to analog ground) if the internal voltage reference is selected as the ADC reference voltage.                                                                                      |

| Oscillators                 |     |                                                                                                                                                                                                                                                                                                        |

15

### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

# zilog

37

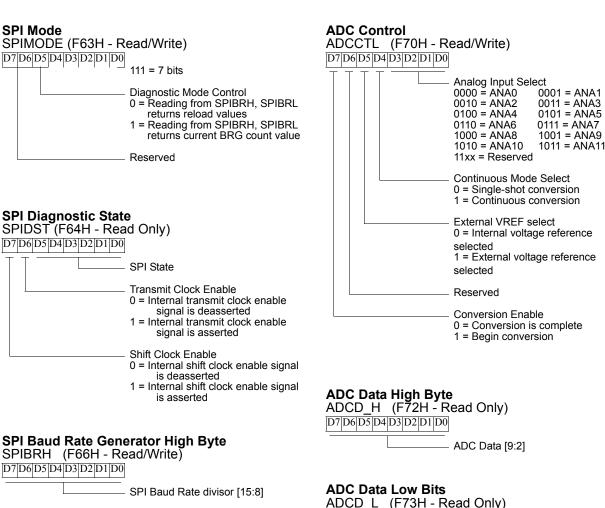

#### SPI Baud Rate Generator Low Byte SPIBRL (F67H - Read/Write)

D7 D6 D5 D4 D3 D2 D1 D0

\_\_\_\_\_ SPI Baud Rate divisor [7:0]

ADCD\_L (F73H - Read Only) D7D6D5D4D3D2D1D0 \_\_\_\_\_

Reserved

\_\_\_\_\_ ADC Data [1:0]

#### **Operating Mode Reset Source Reset Type** NORMAL or HALT Power-On Reset/Voltage system reset modes Brownout Watchdog Timer time-out system reset when configured for Reset RESET pin assertion system reset On-Chip Debugger initiated Reset system reset except the On-Chip Debugger is (OCDCTL[0] set to 1) unaffected by the reset Power-On Reset/Voltage STOP mode system reset Brownout **RESET** pin assertion system reset DBG pin driven Low system reset

#### Table 9. Reset Sources and Resulting Reset Type

#### **Power-On Reset**

Each device in the 64K Series contains an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 66 cycles of the Watchdog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The devices are held in the Reset state until both the POR Counter and XTAL counter have timed out. After the 64K Series devices exit the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watchdog Timer Control (WDTCTL) register is set to 1.

Figure 8 displays Power-On Reset operation. For the POR threshold voltage ( $V_{POR}$ ), see Electrical Characteristics on page 215.

**Caution:** The following style of coding to generate software interrupts by setting bits in the Interrupt Request registers is NOT recommended. All incoming interrupts that are received between execution of the first LDX command and the last LDX command are lost.

Poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

To avoid missing interrupts, the following style of coding to set bits in the Interrupt Request registers is recommended:

Good coding style that avoids lost interrupt requests:

ORX IRQO, MASK

# Interrupt Control Register Definitions

For all interrupts other than the Watchdog Timer interrupt, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

### Interrupt Request 0 Register

The Interrupt Request 0 (IRO0) register (Table 24) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8<sup>™</sup> CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending

|       |     |     | - J ( |       |       |      |      |      |  |  |  |

|-------|-----|-----|-------|-------|-------|------|------|------|--|--|--|

| BITS  | 7   | 6   | 5     | 4     | 3     | 2    | 1    | 0    |  |  |  |

| FIELD | T2I | T1I | TOI   | U0RXI | U0TXI | I2CI | SPII | ADCI |  |  |  |

| RESET |     | 0   |       |       |       |      |      |      |  |  |  |

| R/W   |     | R/W |       |       |       |      |      |      |  |  |  |

| ADDR  |     |     |       | FC    | 0H    |      |      |      |  |  |  |

Table 24. Interrupt Request 0 Register (IRQ0)

T2I—Timer 2 Interrupt Request

0 = No interrupt request is pending for Timer 2.

1 = An interrupt request from Timer 2 is awaiting service.

PADxI—Port A or Port D Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Port D pin *x*.

1 = An interrupt request from GPIO Port A or Port D pin x is awaiting service.

where *x* indicates the specific GPIO Port pin number (0 through 7). For each pin, only 1 of either Port A or Port D can be enabled for interrupts at any one time. Port selection (A or D) is determined by the values in the Interrupt Port Select Register.

#### Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) register (Table 26) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

| BITS  | 7   | 6     | 5     | 4    | 3    | 2    | 1    | 0    |  |

|-------|-----|-------|-------|------|------|------|------|------|--|

| FIELD | T3I | U1RXI | U1TXI | DMAI | PC3I | PC2I | PC1I | PC0I |  |

| RESET | 0   |       |       |      |      |      |      |      |  |

| R/W   |     | R/W   |       |      |      |      |      |      |  |

| ADDR  |     |       |       | FC   | 6H   |      |      |      |  |

Table 26. Interrupt Request 2 Register (IRQ2)

T3I—Timer 3 Interrupt Request

0 = No interrupt request is pending for Timer 3.

1 = An interrupt request from Timer 3 is awaiting service.

U1RXI—UART 1 Receive Interrupt Request

0 = No interrupt request is pending for the UART1 receiver.

1 = An interrupt request from UART1 receiver is awaiting service.

U1TXI-UART 1 Transmit Interrupt Request

0 = No interrupt request is pending for the UART 1 transmitter.

1 = An interrupt request from the UART 1 transmitter is awaiting service.

DMAI—DMA Interrupt Request

0 = No interrupt request is pending for the DMA.

1 = An interrupt request from the DMA is awaiting service.

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x.

1 = An interrupt request from GPIO Port C pin x is awaiting service.

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |  |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|--|

| FIELD | PAD7ENH | PAD6ENH | PAD5ENH | PAD4ENH | PAD3ENH | PAD2ENH | PAD1ENH | PAD0ENH |  |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |  |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |  |

| ADDR  |         | FC4H    |         |         |         |         |         |         |  |

#### Table 31. IRQ1 Enable High Bit Register (IRQ1ENH)

PADxENH—Port A or Port D Bit[x] Interrupt Request Enable High Bit. For selection of either Port A or Port D as the interrupt source, see Interrupt Port Select Register on page 78.

Table 32. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| FIELD | PAD7ENL | PAD6ENL | PAD5ENL | PAD4ENL | PAD3ENL | PAD2ENL | PAD1ENL | PAD0ENL |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ADDR  |         |         |         | FC      | 5H      |         |         |         |

PADxENL—Port A or Port D Bit[x] Interrupt Request Enable Low Bit For selection of either Port A or Port D as the interrupt source, see Interrupt Port Select Register on page 78.

# **IRQ2 Enable High and Low Bit Registers**

The IRQ2 Enable High and Low Bit registers (see Table 34 and Table 35 on page 77) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register. Table 33 describes the priority control for IRQ2.

| Table 33 | IRQ2 | Enable | and | Priority | <sup>,</sup> Encoding |

|----------|------|--------|-----|----------|-----------------------|

|----------|------|--------|-----|----------|-----------------------|

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control 1 register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the *first* external Timer Input transition. The desired transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control 1 Register. The timer input is the system clock.

Every subsequent desired transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control 1 register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control 1 register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In m/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

# **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Output Signal Operation**

Timer Output is a GPIO Port pin alternate function. Generally, the Timer Output is toggled every time the counter is reloaded.

#### **Timer Control Register Definitions**

Timers 0-2 are available in all packages. Timer 3 is only available in the 64-, 68-, and 80-pin packages.

#### Timer 0-3 High and Low Byte Registers

The Timer 0-3 High and Low Byte (TxH and TxL) registers (see Table 39 and Table 40 on page 91) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TMRL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TMRL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

Timer 3 is unavailable in the 40- and 44-pin packages.

# zilog

- 15. The  $I^2C$  Controller sends the repeated START condition.

- 16. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register (third address transfer).

- 17. The I<sup>2</sup>C Controller sends 11110B followed by the two most significant bits of the slave read address and a 1 (read).

- 18. The I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal Low during the next high period of SCL

If the slave were to Not Acknowledge at this point (this should not happen because the slave did acknowledge the first two address bytes), software would respond by setting the STOP and FLUSH bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore the following steps).

- 19. The I<sup>2</sup>C Controller shifts in a byte of data from the I<sup>2</sup>C slave on the SDA signal. The I<sup>2</sup>C Controller sends a Not Acknowledge to the I<sup>2</sup>C slave if the NAK bit is set (last byte), else it sends an Acknowledge.

- 20. The I<sup>2</sup>C Controller asserts the Receive interrupt (RDRF bit set in the Status register).

- 21. Software responds by reading the I<sup>2</sup>C Data register which clears the RDRF bit. If there is only one more byte to receive, set the NAK bit of the I<sup>2</sup>C Control register.

- 22. If there are one or more bytes to transfer, return to step 19.

- 23. After the last byte is shifted in, a Not Acknowledge interrupt is generated by the I<sup>2</sup>C Controller.

- 24. Software responds by setting the STOP bit of the  $I^2C$  Control register.

- 25. A STOP condition is sent to the  $I^2C$  slave and the STOP and NCKI bits are cleared.

# I<sup>2</sup>C Control Register Definitions

# I<sup>2</sup>C Data Register

The I<sup>2</sup>C Data register (see Table 70 on page 157) holds the data that is to be loaded into the I<sup>2</sup>C Shift register during a write to a slave. This register also holds data that is loaded from the I<sup>2</sup>C Shift register during a read from a slave. The I<sup>2</sup>C Shift Register is not accessible in the Register File address space, but is used only to buffer incoming and outgoing data.

156

#### 183

# **Flash Memory**

# **Overview**

The products in the Z8 Encore! XP 64K Series Flash Microcontrollers feature up to 64 KB (65,536 bytes) of non-volatile Flash memory with read/write/erase capability. The Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in 512-byte per page. The 512-byte page is the minimum Flash block size that can be erased. The Flash memory is also divided into 8 sectors which can be protected from programming and erase operations on a per sector basis.

Table 89 describes the Flash memory configuration for each device in the 64K Series. Table 90 on page 184 lists the sector address ranges. Figure 35 on page 184 displays the Flash memory arrangement.

| Part Number | Flash Size   | Number<br>of Pages | Flash Memory<br>Addresses | Sector Size | Number of<br>Sectors | Pages<br>per<br>Sector |

|-------------|--------------|--------------------|---------------------------|-------------|----------------------|------------------------|

| Z8F162x     | 16K (16,384) | 32                 | 0000H - 3FFFH             | 2K (2048)   | 8                    | 4                      |

| Z8F242x     | 24K (24,576) | 48                 | 0000H - 5FFFH             | 4K (4096)   | 6                    | 8                      |

| Z8F322x     | 32K (32,768) | 64                 | 0000H - 7FFFH             | 4K (4096)   | 8                    | 8                      |

| Z8F482x     | 48K (49,152) | 96                 | 0000H - BFFFH             | 8K (8192)   | 6                    | 16                     |

| Z8F642x     | 64K (65,536) | 128                | 0000H - FFFFH             | 8K (8192)   | 8                    | 16                     |

#### **Table 89. Flash Memory Configurations**

Reserved These bits are reserved and must be 0.

FSTAT—Flash Controller Status

$00_{0000} =$ Flash Controller locked

00\_0001 = First unlock command received

$00_{010} =$  Second unlock command received

00\_0011 = Flash Controller unlocked

00\_0100 = Flash Sector Protect register selected

00\_1xxx = Program operation in progress

01\_0xxx = Page erase operation in progress

10\_0xxx = Mass erase operation in progress

# Page Select Register

The Page Select (FPS) register (Table 94) selects one of the 128 available Flash memory pages to be erased or programmed. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory locations with the 7 most significant bits of the address given by the PAGE field are erased to FFH.

The Page Select register shares its Register File address with the Flash Sector Protect Register. The Page Select register cannot be accessed when the Flash Sector Protect register is enabled.

| BITS  | 7       | 6          | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|---------|------------|---|----|----|---|---|---|--|

| FIELD | INFO_EN | FO_EN PAGE |   |    |    |   |   |   |  |

| RESET |         | 0          |   |    |    |   |   |   |  |

| R/W   |         | R/W        |   |    |    |   |   |   |  |

| ADDR  |         |            |   | FF | 9H |   |   |   |  |

Table 94. Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area is not selected.

1 = Information Area is selected. The Information area is mapped into the Flash Memory address space at addresses FE00H through FFFFH.

PAGE—Page Select

This 7-bit field selects the Flash memory page for Programming and Page Erase operations. Flash Memory Address[15:9] = PAGE[6:0].

# **Option Bits**

# Overview

Option Bits allow user configuration of certain aspects of the 64K Series operation. The feature configuration data is stored in the Flash Memory and read during Reset. The features available for control via the Option Bits are:

- Watchdog Timer time-out response selection-interrupt or Reset.

- Watchdog Timer enabled at Reset.

- The ability to prevent unwanted read access to user code in Flash Memory.

- The ability to prevent accidental programming and erasure of the user code in Flash Memory.

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption.

- Oscillator mode selection-for high, medium, and low power crystal oscillators, or external RC oscillator.

# Operation

### **Option Bit Configuration By Reset**

Each time the Option Bits are programmed or erased, the device must be Reset for the change to take place. During any reset operation (System Reset, Reset, or Stop Mode Recovery), the Option Bits are automatically read from the Flash Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the 64K Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

# **Option Bit Address Space**

The first two bytes of Flash Memory at addresses 0000H (see Table 98 on page 196) and 0001H (see Table 99 on page 197) are reserved for the user Option Bits. The byte at Flash Memory address 0000H configures user options. The byte at Flash Memory address 0001H is reserved for future use and must remain unprogrammed.

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

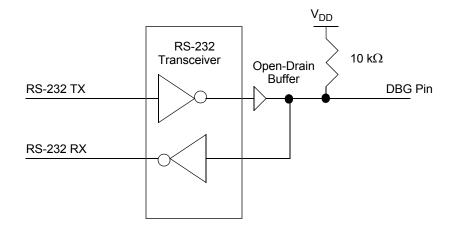

#### Figure 38. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

### **DEBUG Mode**

The operating characteristics of the 64K Series devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The device enters DEBUG mode following any of the following operations:

- Writing the DBGMODE bit in the OCD Control Register to 1 using the OCD interface.

- eZ8 CPU execution of a BRK (Breakpoint) instruction (when enabled).

- If the DBG pin is Low when the device exits Reset, the On-Chip Debugger automatically puts the device into DEBUG mode.

#### **Exiting DEBUG Mode**

The device exits DEBUG mode following any of the following operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0.

- Power-On Reset

- Voltage Brownout reset

210

eZ8 CPU loops on the BRK instruction. 0 = BRK instruction sets DBGMODE to 1. 1 = eZ8 CPU loops on BRK instruction.

Reserved

These bits are reserved and must be 0.

RST—Reset

Setting this bit to 1 resets the 64K Series devices. The devices go through a normal Power-On Reset sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 when the reset finishes.

0 = No effect

1 =Reset the 64K Series device

### **OCD Status Register**

The OCD Status register (Table 103) reports status information about the current state of the debugger and the system.

| BITS  | 7    | 6    | 5    | 4        | 3 | 3 2 1 |  |  |  |  |  |  |

|-------|------|------|------|----------|---|-------|--|--|--|--|--|--|

| FIELD | IDLE | HALT | RPEN | Reserved |   |       |  |  |  |  |  |  |

| RESET |      |      |      | 0        |   |       |  |  |  |  |  |  |

| R/W   |      |      |      | R        |   |       |  |  |  |  |  |  |

#### IDLE—CPU idling

This bit is set if the part is in DEBUG mode (DBGMODE is 1), or if a BRK instruction occurred since the last time OCDCTL was written. This can be used to determine if the CPU is running or if it is idling.

0 = The eZ8 CPU is running.

1 = The eZ8 CPU is either stopped or looping on a BRK instruction.

HALT—HALT Mode

0 = The device is not in HALT mode.

1 = The device is in HALT mode.

RPEN—Read Protect Option Bit Enabled

0 = The Read Protect Option Bit is disabled (1).

1 = The Read Protect Option Bit is enabled (0), disabling many OCD commands.

#### Reserved

These bits are always 0.

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

zilog

225

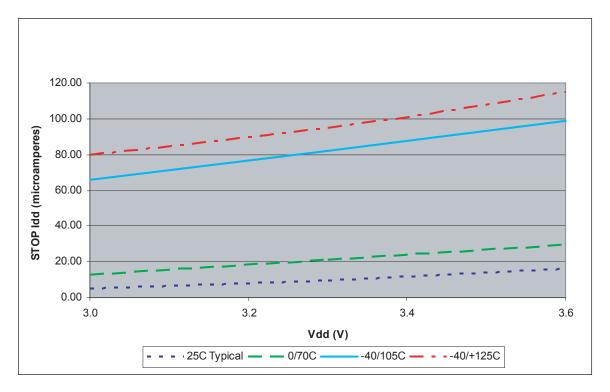

Figure 48 displays the maximum current consumption in STOP mode with the VBO disabled and Watchdog Timer enabled versus the power supply voltage. All GPIO pins are configured as outputs and driven High. Disabling the Watchdog Timer and its internal RC oscillator in STOP mode will provide some additional reduction in STOP mode current consumption. This small current reduction would be indistinguishable on the scale of Figure 48.

#### Figure 48. Maximum STOP Mode Idd with VBO Disabled versus Power Supply Voltage

|                  |                                                                                                                                                                                                                                                                                               | T <sub>A</sub> = -40 °       | °C to 125 ° | С       |       |                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------|---------|-------|------------------------------------|--|--|--|

| Symbol Parameter |                                                                                                                                                                                                                                                                                               | Minimum Typical <sup>1</sup> |             | Maximum | Units | Conditions                         |  |  |  |

| V <sub>DD</sub>  | Operating Voltage<br>Range                                                                                                                                                                                                                                                                    | 2.70 <sup>1</sup>            | _           | -       | V     |                                    |  |  |  |

| R <sub>EXT</sub> | External Resistance from XIN to VDD                                                                                                                                                                                                                                                           | 40                           | 45          | 200     | kΩ    | V <sub>DD</sub> = V <sub>VBO</sub> |  |  |  |

| C <sub>EXT</sub> | External Capacitance<br>from XIN to VSS                                                                                                                                                                                                                                                       | 0                            | 20          | 1000    | pF    |                                    |  |  |  |

| F <sub>OSC</sub> | External RC Oscillation<br>Frequency                                                                                                                                                                                                                                                          | _                            | _           | 4       | MHz   |                                    |  |  |  |

| 2.7 V, but       | <sup>1</sup> When using the external RC oscillator mode, the oscillator may stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the voltage brown-out threshold. The oscillator will resume oscillation as soon as the supply voltage exceeds 2.7 V. |                              |             |         |       |                                    |  |  |  |

# Table 108. External RC Oscillator Electrical Characteristics and Timing

# Table 109. Reset and Stop Mode Recovery Pin Timing

|                    |                                                     | T <sub>A</sub> = -40 ° | °C to 125 | C       |                  |                                                                 |  |

|--------------------|-----------------------------------------------------|------------------------|-----------|---------|------------------|-----------------------------------------------------------------|--|

| Symbol             | Parameter                                           | Minimum Typical        |           | Maximum | Units            | Conditions                                                      |  |

| T <sub>RESET</sub> | RESET pin assertion to initiate a system reset.     | 4                      | _         | -       | T <sub>CLK</sub> | Not in STOP Mode.<br>T <sub>CLK</sub> = System Clock<br>period. |  |

| T <sub>SMR</sub>   | Stop Mode Recovery<br>pin Pulse Rejection<br>Period | 10                     | 20        | 40      | ns               | RESET, DBG, and GPIO<br>pins configured as SMR<br>sources.      |  |

; value 01H, is the source. The value 01H is written into the ; Register at address 234H.

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if you prefer manual program coding or intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0 - R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

Refer to the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status Flags, and address modes are represented by a notational shorthand that is described in Table 122.

# Table 130. Logical Instructions (Continued)

| Mnemonic Operands |          | Instruction                                       |

|-------------------|----------|---------------------------------------------------|

| XOR               | dst, src | Logical Exclusive OR                              |

| XORX              | dst, src | Logical Exclusive OR using Extended<br>Addressing |

Table 131. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

| Part Number                | Flash     | RAM      | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | 1 <sup>2</sup> C | SPI | UARTs with IrDA | Description         |

|----------------------------|-----------|----------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|---------------------|

| Z8F482x with 48 KB Flas    |           |          | -to-D     | ligita     |                     | nver                | ter              |     |                 |                     |

| Standard Temperature: 0 °  |           |          |           |            |                     |                     |                  |     |                 |                     |

| Z8F4821PM020SC             | 48 KB     | 4 KB     | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F4821AN020SC             | 48 KB     | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F4821VN020SC             | 48 KB     | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F4822AR020SC             | 48 KB     | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F4822VS020SC             | 48 KB     | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F4823FT020SC             | 48 KB     | 4 KB     | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

| Extended Temperature: -4   | 0 °C to + | 105 °C   |           |            |                     |                     |                  |     |                 |                     |

| Z8F4821PM020EC             | 48 KB     | 4 KB     | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F4821AN020EC             | 48 KB     | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F4821VN020EC             | 48 KB     | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F4822AR020EC             | 48 KB     | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F4822VS020EC             | 48 KB     | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F4823FT020EC             | 48 KB     | 4 KB     | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

| Automotive/Industrial Temp | perature: | –40 °C 1 | to +1:    | 25 °C      | 2                   |                     |                  |     |                 |                     |

| Z8F4821PM020AC             | 48 KB     | 4 KB     | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F4821AN020AC             | 48 KB     | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F4821VN020AC             | 48 KB     | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F4822AR020AC             | 48 KB     | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F4822VS020AC             | 48 KB     | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F4823FT020AC             | 48 KB     | 4 KB     | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |