Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |  |

|----------------------------|---------------------------------------------------------------|--|

| Product Status             | Obsolete                                                      |  |

| Core Processor             | eZ8                                                           |  |

| Core Size                  | 8-Bit                                                         |  |

| Speed                      | 20MHz                                                         |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |  |

| Number of I/O              | 46                                                            |  |

| Program Memory Size        | 32KB (32K x 8)                                                |  |

| Program Memory Type        | FLASH                                                         |  |

| EEPROM Size                | -                                                             |  |

| RAM Size                   | 2K x 8                                                        |  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |  |

| Data Converters            | A/D 12x10b                                                    |  |

| Oscillator Type            | Internal                                                      |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |  |

| Mounting Type              | Surface Mount                                                 |  |

| Package / Case             | 68-LCC (J-Lead)                                               |  |

| Supplier Device Package    | -                                                             |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f3222vs020sc00tr |  |

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

| nformation Area                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register File Address Map 2                                                                                                                                                                                                                                                                                                                                                   |

| Control Register Summary                                                                                                                                                                                                                                                                                                                                                      |

| Reset and Stop Mode Recovery                                                                                                                                                                                                                                                                                                                                                  |

| Overview       4         Reset Types       4         Reset Sources       4         Power-On Reset       4         Voltage Brownout Reset       5         Watchdog Timer Reset       5         External Pin Reset       5         On-Chip Debugger Initiated Reset       5         Stop Mode Recovery       5         Stop Mode Recovery Using Watchdog Timer Time-Out       5 |

| Stop Mode Recovery Using a GPIO Port Pin Transition HALT 5                                                                                                                                                                                                                                                                                                                    |

| Low-Power Modes                                                                                                                                                                                                                                                                                                                                                               |

| Overview         5           STOP Mode         5           HALT Mode         5                                                                                                                                                                                                                                                                                                |

| General-Purpose I/O                                                                                                                                                                                                                                                                                                                                                           |

| Overview         5           GPIO Port Availability By Device         5           Architecture         5           GPIO Alternate Functions         5           GPIO Interrupts         6           GPIO Control Register Definitions         6                                                                                                                               |

| Port A–H Address Registers 6 Port A–H Control Registers 6 Port A–H Input Data Registers 6 Port A–H Output Data Register 6                                                                                                                                                                                                                                                     |

| nterrupt Controller                                                                                                                                                                                                                                                                                                                                                           |

| Overview       6         Interrupt Vector Listing       6         Architecture       6         Operation       6                                                                                                                                                                                                                                                              |

PS019919-1207 Table of Contents

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers **Product Specification**

| ı | L | U | y | i |

|---|---|---|---|---|

|   |   |   |   |   |

| DMA_ADC Operation                            | 166 |

|----------------------------------------------|-----|

| Configuring DMA_ADC for Data Transfer        | 167 |

| DMA Control Register Definitions             | 167 |

| DMAx Control Register                        | 167 |

| DMAx I/O Address Register                    | 168 |

| DMAx Address High Nibble Register            | 169 |

| DMAx Start/Current Address Low Byte Register | 170 |

| DMAx End Address Low Byte Register           |     |

| DMA_ADC Address Register                     | 171 |

| DMA_ADC Control Register                     | 172 |

| DMA Status Register                          | 173 |

| Analog-to-Digital Converter                  | 176 |

|                                              |     |

| Overview                                     |     |

| Architecture                                 |     |

| Operation                                    |     |

| Automatic Power-Down                         |     |

| Single-Shot Conversion                       |     |

| Continuous Conversion                        |     |

| DMA Control of the ADC                       |     |

| ADC Control Register Definitions             |     |

| ADC Control Register                         |     |

| ADC Data High Byte Register                  |     |

| ADC Data Low Bits Register                   | 180 |

| Flash Memory                                 | 183 |

| Overview                                     | 183 |

| Information Area                             |     |

| Operation                                    |     |

| Timing Using the Flash Frequency Registers   |     |

| Flash Read Protection                        |     |

| Flash Write/Erase Protection                 |     |

| Byte Programming                             | 187 |

| Page Erase                                   | 188 |

| Mass Erase                                   | 189 |

| Flash Controller Bypass                      | 189 |

| Flash Controller Behavior in Debug Mode      | 189 |

| Flash Control Register Definitions           | 190 |

| Flash Control Register                       | 190 |

|                                              |     |

PS019919-1207 **Table of Contents**

Table 7. Z8 Encore! XP 64K Series Flash Microcontrollers Register File Address Map (Continued)

| Address (Hex) |                       | Mnemonic | Reset (Hex) | Page No |

|---------------|-----------------------|----------|-------------|---------|

| FCD           | Interrupt Edge Select | IRQES    | 00          | 78      |

| FCE           | Interrupt Port Select | IRQPS    | 00          | 78      |

| FCF           | Interrupt Control     | IRQCTL   | 00          | 79      |

| GPIO Port A   |                       |          |             |         |

| FD0           | Port A Address        | PAADDR   | 00          | 61      |

| FD1           | Port A Control        | PACTL    | 00          | 62      |

| FD2           | Port A Input Data     | PAIN     | XX          | 66      |

| FD3           | Port A Output Data    | PAOUT    | 00          | 66      |

| GPIO Port B   |                       |          |             |         |

| FD4           | Port B Address        | PBADDR   | 00          | 61      |

| FD5           | Port B Control        | PBCTL    | 00          | 62      |

| FD6           | Port B Input Data     | PBIN     | XX          | 66      |

| FD7           | Port B Output Data    | PBOUT    | 00          | 66      |

| GPIO Port C   |                       |          |             |         |

| FD8           | Port C Address        | PCADDR   | 00          | 61      |

| FD9           | Port C Control        | PCCTL    | 00          | 62      |

| FDA           | Port C Input Data     | PCIN     | XX          | 66      |

| FDB           | Port C Output Data    | PCOUT    | 00          | 66      |

| GPIO Port D   |                       |          |             |         |

| FDC           | Port D Address        | PDADDR   | 00          | 61      |

| FDD           | Port D Control        | PDCTL    | 00          | 62      |

| FDE           | Port D Input Data     | PDIN     | XX          | 66      |

| FDF           | Port D Output Data    | PDOUT    | 00          | 66      |

| GPIO Port E   |                       |          |             |         |

| FE0           | Port E Address        | PEADDR   | 00          | 61      |

| FE1           | Port E Control        | PECTL    | 00          | 62      |

| FE2           | Port E Input Data     | PEIN     | XX          | 66      |

| FE3           | Port E Output Data    | PEOUT    | 00          | 66      |

| GPIO Port F   |                       |          |             |         |

| FE4           | Port F Address        | PFADDR   | 00          | 61      |

| FE5           | Port F Control        | PFCTL    | 00          | 62      |

| FE6           | Port F Input Data     | PFIN     | XX          | 66      |

| FE7           | Port F Output Data    | PFOUT    | 00          | 66      |

| GPIO Port G   |                       |          |             |         |

| FE8           | Port G Address        | PGADDR   | 00          | 61      |

| FE9           | Port G Control        | PGCTL    | 00          | 62      |

| FEA           | Port G Input Data     | PGIN     | XX          | 66      |

| FEB           | Port G Output Data    | PGOUT    | 00          | 66      |

| GPIO Port H   |                       |          |             |         |

|               | Port H Address        | PHADDR   | 00          | 61      |

| FEC           |                       |          |             |         |

| FEC<br>FED    | Port H Control        | PHCTL    | 00          | 62      |

34

1 = Current byte is start of new

frame Reserved

Figure 8. Power-On Reset Operation

## **Voltage Brownout Reset**

The devices in the 64K Series provide low Voltage Brownout protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage remains below the Power-On Reset voltage threshold ( $V_{POR}$ ), the VBO block holds the device in the Reset state.

After the supply voltage again exceeds the Power-On Reset voltage threshold, the devices progress through a full system reset sequence, as described in the Power-On Reset section. Following Power-On Reset, the POR status bit in the Watchdog Timer Control (WDTCTL) register is set to 1. Figure 9 displays Voltage Brownout operation. For the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ), see Electrical Characteristics on page 215.

The Voltage Brownout circuit can be either enabled or disabled during STOP mode. Operation during STOP mode is set by the VBO\_AO Option Bit. For information on configuring VBO\_AO, see Option Bits page 195.

AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A-H Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

### Port A-H Output Control Sub-Registers

The Port A–H Output Control sub-register (Table 18) is accessed through the Port A-H Control register by writing 03H to the Port A-H Address register. Setting the bits in the Port A–H Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

Table 18. Port A-H Output Control Sub-Registers

| вітѕ  | 7      | 6             | 5           | 4             | 3             | 2           | 1            | 0      |  |  |  |

|-------|--------|---------------|-------------|---------------|---------------|-------------|--------------|--------|--|--|--|

| FIELD | POC7   | POC6          | POC5        | POC4          | POC3          | POC2        | POC1         | POC0   |  |  |  |

| RESET |        | 0             |             |               |               |             |              |        |  |  |  |

| R/W   |        | R/W           |             |               |               |             |              |        |  |  |  |

| ADDR  | If 03⊢ | I in Port A-F | H Address R | egister, acce | essible throu | gh Port A-F | l Control Re | gister |  |  |  |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and disables the drains if set to 1.

0 = The drains are enabled for any output mode.

1 = The drain of the associated pin is disabled (open-drain mode).

### Port A-H High Drive Enable Sub-Registers

The Port A–H High Drive Enable sub-register (Table 19) is accessed through the Port A– H Control register by writing 04H to the Port A-H Address register. Setting the bits in the Port A–H High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A-H High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

PS019919-1207 General-Purpose I/O

- Executing a Trap instruction.

- Illegal Instruction trap.

# **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all of the interrupts were enabled with identical interrupt priority (all as Level 2 interrupts, for example), then interrupt priority would be assigned from highest to lowest as specified in Table 23 on page 68. Level 3 interrupts always have higher priority than Level 2 interrupts which, in turn, always have higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 23 on page 68. Reset, Watchdog Timer interrupt (if enabled), and Illegal Instruction Trap always have highest priority.

# Interrupt Assertion

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

**Caution:** The following style of coding to clear bits in the Interrupt Request registers is NOT recommended. All incoming interrupts that are received between execution of the first LDX command and the last LDX command are lost.

### Poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

AND r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, the following style of coding to clear bits in the Interrupt Request 0 register is recommended:

### Good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

# **Software Interrupt Assertion**

Program code can generate interrupts directly. Writing a 1 to the desired bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

PS019919-1207 Interrupt Controller

Table 42. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6   | 5 | 4          | 3          | 2 | 1 | 0 |  |  |  |

|-------|-----|-----|---|------------|------------|---|---|---|--|--|--|

| FIELD | TRL |     |   |            |            |   |   |   |  |  |  |

| RESET |     | 1   |   |            |            |   |   |   |  |  |  |

| R/W   |     | R/W |   |            |            |   |   |   |  |  |  |

| ADDR  |     |     | F | 03H, F0BH, | F13H, F1BI | Н |   |   |  |  |  |

TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two byte form the 16-bit Compare value.

# Timer 0-3 PWM High and Low Byte Registers

The Timer 0-3 PWM High and Low Byte (TxPWMH and TxPWML) registers (see Table 43 and Table 44 on page 92) are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the Capture and Capture/COMPARE modes.

Table 43. Timer 0-3 PWM High Byte Register (TxPWMH)

| BITS  | 7 | 6    | 5 | 4          | 3         | 2 | 1 | 0 |  |  |  |

|-------|---|------|---|------------|-----------|---|---|---|--|--|--|

| FIELD |   | PWMH |   |            |           |   |   |   |  |  |  |

| RESET |   | 0    |   |            |           |   |   |   |  |  |  |

| R/W   |   | R/W  |   |            |           |   |   |   |  |  |  |

| ADDR  |   |      | F | 04H, F0CH, | F14H, F1C | Н |   |   |  |  |  |

# Table 44. Timer 0-3 PWM Low Byte Register (TxPWML)

| BITS  | 7 | 6    | 5 | 4          | 3         | 2 | 1 | 0 |  |  |  |

|-------|---|------|---|------------|-----------|---|---|---|--|--|--|

| FIELD |   | PWML |   |            |           |   |   |   |  |  |  |

| RESET |   | 0    |   |            |           |   |   |   |  |  |  |

| R/W   |   | R/W  |   |            |           |   |   |   |  |  |  |

| ADDR  |   |      | F | 05H, F0DH, | F15H, F1D | Н |   |   |  |  |  |

PS019919-1207 Timers

Table 47. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value |          | e Time-Out Delay<br>WDT oscillator frequency) |

|------------------|------------------|----------|-----------------------------------------------|

| (Hex)            | (Decimal)        | Typical  | Description                                   |

| 000004           | 4                | 400 μs   | Minimum time-out delay                        |

| FFFFFF           | 16,777,215       | 1677.5 s | Maximum time-out delay                        |

# Watchdog Timer Refresh

When first enabled, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer then counts down to 000000H unless a WDT instruction is executed by the eZ8<sup>TM</sup> CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When the 64K Series devices are operating in DEBUG Mode (through the On-Chip Debugger), the Watchdog Timer is continuously refreshed to prevent spurious Watchdog Timer time-outs.

### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a Reset. The WDT\_RES Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Option Bit, see Option Bits on page 195.

### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

### **WDT Interrupt in STOP Mode**

If configured to generate an interrupt when a time-out occurs and the 64K Series devices are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 47.

PS019919-1207 Watchdog Timer

### Table 55. UART Status 1 Register (UxSTAT1)

| BITS  | 7                    | 6       | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |

|-------|----------------------|---------|---|---------|---------|---|---|---|--|--|--|

| FIELD | Reserved NEWFRM MPRX |         |   |         |         |   |   |   |  |  |  |

| RESET |                      | 0       |   |         |         |   |   |   |  |  |  |

| R/W   |                      | R R/W R |   |         |         |   |   |   |  |  |  |

| ADDR  |                      |         |   | F44H ar | nd F4CH |   |   |   |  |  |  |

Reserved—Must be 0.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

MPRX—Multiprocessor Receive

Returns the value of the last multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

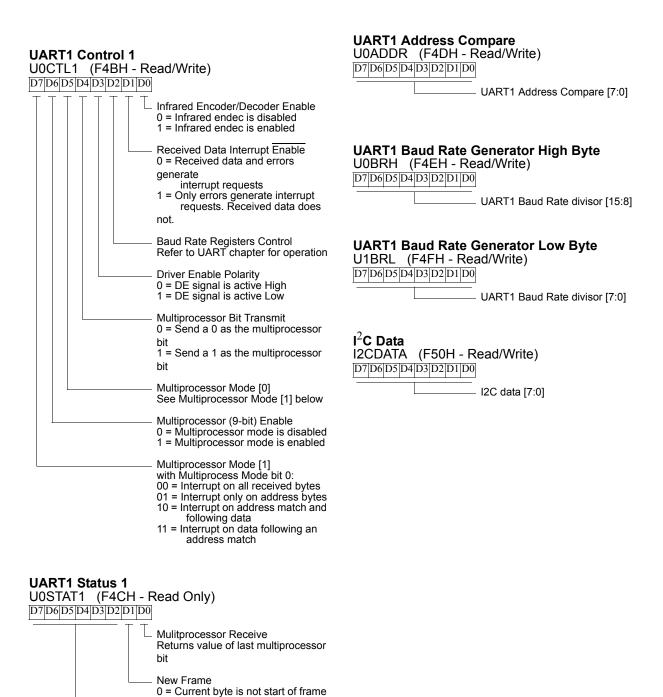

# **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (see Table 56 and Table 57 on page 118) configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

Table 56. UART Control 0 Register (UxCTL0)

| BITS  | 7   | 6   | 5    | 4       | 3       | 2    | 1    | 0    |

|-------|-----|-----|------|---------|---------|------|------|------|

| FIELD | TEN | REN | CTSE | PEN     | PSEL    | SBRK | STOP | LBEN |

| RESET |     |     |      | (       | )       |      |      |      |

| R/W   |     |     |      | R/      | W       |      |      |      |

| ADDR  |     |     |      | F42H ar | nd F4AH |      |      |      |

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{CTS}$  signal and the CTSE bit. If the  $\overline{CTS}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled.

1 = Transmitter enabled.

PS019919-1207 UART

- 13. The I<sup>2</sup>C Controller shifts the data out of using the SDA signal. After the first bit is sent, the Transmit interrupt is asserted.

- 14. If more bytes remain to be sent, return to step 9.

- 15. Software responds by setting the STOP bit of the I<sup>2</sup>C Control register (or START bit to initiate a new transaction). In the STOP case, software clears the TXI bit of the I<sup>2</sup>C Control register at the same time.

- 16. The I<sup>2</sup>C Controller completes transmission of the data on the SDA signal.

- 17. The slave may either Acknowledge or Not Acknowledge the last byte. Because either the STOP or START bit is already set, the NCKI interrupt does not occur.

- 18. The I<sup>2</sup>C Controller sends the STOP (or RESTART) condition to the I<sup>2</sup>C bus. The STOP or START bit is cleared.

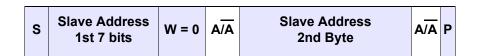

# Address Only Transaction with a 10-bit Address

In the situation where software wants to determine if a slave with a 10-bit address is responding without sending or receiving data, a transaction can be done which only consists of an address phase. Figure 30 displays this 'address only' transaction to determine if a slave with 10-bit address will acknowledge. As an example, this transaction can be used after a 'write' has been done to a EEPROM to determine when the EEPROM completes its internal write operation and is once again responding to I<sup>2</sup>C transactions. If the slave does not Acknowledge the transaction can be repeated until the slave is able to Acknowledge.

Figure 30. 10-Bit Address Only Transaction Format

Follow the steps below for an address only transaction to a 10-bit addressed slave:

- 1. Software asserts the IEN bit in the I<sup>2</sup>C Control register.

- 2. Software asserts the TXI bit of the I<sup>2</sup>C Control register to enable Transmit interrupts.

- 3. The  $I^2C$  interrupt asserts, because the  $I^2C$  Data register is empty (TDRE = 1)

- 4. Software responds to the TDRE interrupt by writing the first slave address byte. The least-significant bit must be 0 for the write operation.

- 5. Software asserts the START bit of the I<sup>2</sup>C Control register.

- 6. The I<sup>2</sup>C Controller sends the START condition to the I<sup>2</sup>C slave.

PS019919-1207 I2C Controller

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

zilog

182

185

### **Information Area**

Table 91 describes the 64K Series Information Area. This 512-byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into Flash Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, LDC instructions return data from the Information Area. CPU instruction fetches always comes from Flash Memory regardless of the Information Area access bit. Access to the Information Area is readonly.

Table 91. Z8 Encore! XP 64K Series Flash Microcontrollers Information Area Map

| Flash Memory Address (Hex) | Function                                                                                    |

|----------------------------|---------------------------------------------------------------------------------------------|

| FE00H-FE3FH                | Reserved                                                                                    |

| FE40H-FE53H                | Part Number<br>20-character ASCII alphanumeric code<br>Left justified and filled with zeros |

| FE54H-FFFFH                | Reserved                                                                                    |

# **Operation**

The Flash Controller provides the proper signals and timing for Byte Programming, Page Erase, and Mass Erase of the Flash memory. The Flash Controller contains a protection mechanism, via the Flash Control register (FCTL), to prevent accidental programming or erasure. The following subsections provide details on the various operations (Lock, Unlock, Sector Protect, Byte Programming, Page Erase, and Mass Erase).

PS019919-1207 Flash Memory

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

zilog

194

PS019919-1207 Flash Memory

```

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1-65536 bytes at a time (65536 bytes can be written by setting size to zero). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, the data is discarded.

```

DBG ← 0AH

DBG ← Program Memory Address[15:8]

DBG ← Program Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG ← 1-65536 data bytes

```

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1-65536 bytes at a time (65536 bytes can be read by setting size to zero). If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, this command returns FFH for the data.

```

DBG ← 0BH

DBG ← Program Memory Address[15:8]

DBG ← Program Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG → 1-65536 data bytes

```

Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1-65536 bytes at a time (65536 bytes can be written by setting size to zero). If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, the data is discarded.

```

DBG ← 0CH

DBG ← Data Memory Address[15:8]

DBG ← Data Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG ← 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1-65536 bytes at a time (65536 bytes can be read by setting size to zero). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG ← ODH

DBG ← Data Memory Address[15:8]

```

PS019919-1207 On-Chip Debugger

eZ8 CPU loops on the BRK instruction.

0 = BRK instruction sets DBGMODE to 1.

1 = eZ8 CPU loops on BRK instruction.

#### Reserved

These bits are reserved and must be 0.

### RST—Reset

Setting this bit to 1 resets the 64K Series devices. The devices go through a normal Power-On Reset sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 when the reset finishes.

0 = No effect

1 = Reset the 64K Series device

# **OCD Status Register**

The OCD Status register (Table 103) reports status information about the current state of the debugger and the system.

# Table 103. OCD Status Register (OCDSTAT)

| BITS  | 7    | 6    | 5    | 4 | 3 | 2        | 1 | 0 |

|-------|------|------|------|---|---|----------|---|---|

| FIELD | IDLE | HALT | RPEN |   |   | Reserved |   |   |

| RESET | 0    |      |      |   |   |          |   |   |

| R/W   |      |      |      | F | २ |          |   |   |

IDLE—CPU idling

This bit is set if the part is in DEBUG mode (DBGMODE is 1), or if a BRK instruction occurred since the last time OCDCTL was written. This can be used to determine if the CPU is running or if it is idling.

0 =The eZ8 CPU is running.

1 = The eZ8 CPU is either stopped or looping on a BRK instruction.

### HALT—HALT Mode

0 =The device is not in HALT mode.

1 = The device is in HALT mode.

### RPEN—Read Protect Option Bit Enabled

0 = The Read Protect Option Bit is disabled (1).

1 = The Read Protect Option Bit is enabled (0), disabling many OCD commands.

### Reserved

These bits are always 0.

PS019919-1207 On-Chip Debugger

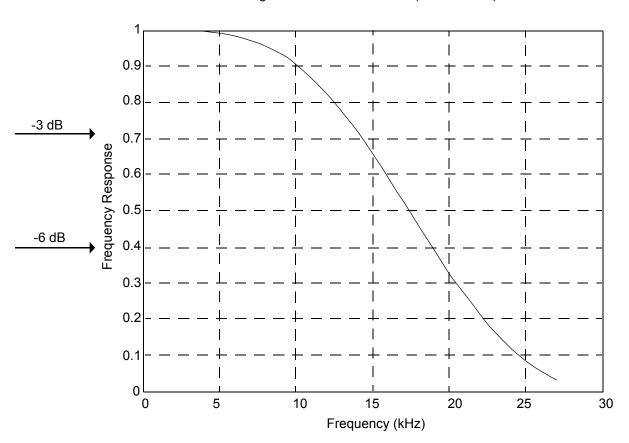

# ADC Magnitude Transfer Function (Linear Scale)

Figure 49. Analog-to-Digital Converter Frequency Response

PS019919-1207 Electrical Characteristics

; value 01H, is the source. The value 01H is written into the

; Register at address 234H.

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if you prefer manual program coding or intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

# **Assembly Language Syntax Example 1**

| Assembly Language<br>Code | ADD | 43H, | H80 | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 80   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0-255 or, using Escaped Mode Addressing, a Working Register R0 - R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### **Assembly Language Syntax Example 2**

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

Refer to the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

## **eZ8 CPU Instruction Notation**

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status Flags, and address modes are represented by a notational shorthand that is described in Table 122.

eZ8<sup>™</sup> CPU Instruction Set PS019919-1207

**Table 123. Additional Symbols**

| Definition                |  |

|---------------------------|--|

| Destination Operand       |  |

| Source Operand            |  |

| Indirect Address Prefix   |  |

| Stack Pointer             |  |

| Program Counter           |  |

| Flags Register            |  |

| Register Pointer          |  |

| Immediate Operand Prefix  |  |

| Binary Number Suffix      |  |

| Hexadecimal Number Prefix |  |

| Hexadecimal Number Suffix |  |

|                           |  |

Assignment of a value is indicated by an arrow. For example,

$$dst \leftarrow dst + src$$

indicates the source data is added to the destination data and the result is stored in the destination location.

## **Condition Codes**

The C, Z, S and V Flags control the operation of the conditional jump (JP cc and JR cc) instructions. Sixteen frequently useful functions of the Flag settings are encoded in a 4-bit field called the condition code (cc), which forms Bits 7:4 of the conditional jump instructions. The condition codes are summarized in Table 124. Some binary condition codes can be created using more than one assembly code mnemonic. The result of the Flag test operation decides if the conditional jump is executed.

**Table 124. Condition Codes**

| Binary | Hex | Assembly<br>Mnemonic | Definition         | Flag Test Operation  |

|--------|-----|----------------------|--------------------|----------------------|

| 0000   | 0   | F                    | Always False       | _                    |

| 0001   | 1   | LT                   | Less Than          | (S XOR V) = 1        |

| 0010   | 2   | LE                   | Less Than or Equal | (Z OR (S XOR V)) = 1 |

eZ8<sup>™</sup> CPU Instruction Set PS019919-1207

**Table 130. Logical Instructions (Continued)**

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

**Table 131. Program Control Instructions**

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

|          |                 |                               |

**Table 132. Rotate and Shift Instructions**

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

eZ8<sup>™</sup> CPU Instruction Set PS019919-1207