Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 29                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4821pm020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# zilog

# LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

## As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

## **Document Disclaimer**

©2007 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

# **Revision History**

Each instance in the Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages or appropriate links given in the table below.

| Date             | Revision<br>Level | Description                                                                                                                                                                                                | Page<br>No  |  |

|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| December<br>2007 | 19                | Updated Zilog logo, Disclaimer section, and implemented<br>style guide. Updated Table 112. Changed Z8 Encore! 64K<br>Series to Z8 Encore! XP 64K Series Flash<br>Microcontrollers throughout the document. | All         |  |

| December<br>2006 | 18                | Updated Table 110 and Ordering Information.                                                                                                                                                                | 228,<br>270 |  |

| November<br>2006 | 17                | Updated Part Number Suffix Designations.                                                                                                                                                                   | 275         |  |

| June 2006        | 16                | Updated Timer 0-3 Control 1 Registers.                                                                                                                                                                     | 94          |  |

| October<br>2005  | 15                | The paragraph tag for Ordering Information has been changed from H1 Heading to Chapter Title.                                                                                                              | 270         |  |

| Master Interrupt Enable 69                                   |

|--------------------------------------------------------------|

| Interrupt Vectors and Priority 70                            |

| Interrupt Assertion                                          |

| Software Interrupt Assertion                                 |

| Interrupt Control Register Definitions                       |

| Interrupt Request 0 Register 71                              |

| Interrupt Request 1 Register 72                              |

| Interrupt Request 2 Register 73                              |

| IRQ0 Enable High and Low Bit Registers                       |

| IRQ1 Enable High and Low Bit Registers                       |

| IRQ2 Enable High and Low Bit Registers                       |

| Interrupt Edge Select Register                               |

| Interrupt Port Select Register                               |

| Interrupt Control Register                                   |

| Timers                                                       |

| Overview                                                     |

| Architecture                                                 |

| Operation                                                    |

| Timer Operating Modes                                        |

| Reading the Timer Count Values                               |

| Timer Output Signal Operation                                |

| Timer Control Register Definitions                           |

| Timer 0-3 High and Low Byte Registers                        |

| Timer Reload High and Low Byte Registers                     |

| Timer 0-3 PWM High and Low Byte Registers                    |

| Timer 0-3 Control 0 Registers                                |

| Timer 0-3 Control 1 Registers                                |

| <b>v</b>                                                     |

| Watchdog Timer                                               |

| Overview                                                     |

| Operation                                                    |

| Watchdog Timer Refresh 98                                    |

| Watchdog Timer Time-Out Response 98                          |

| Watchdog Timer Reload Unlock Sequence                        |

| Watchdog Timer Control Register Definitions                  |

| Watchdog Timer Control Register 100                          |

| Watchdog Timer Reload Upper, High and Low Byte Registers 101 |

Data Register

PS019919-1207

# Architecture

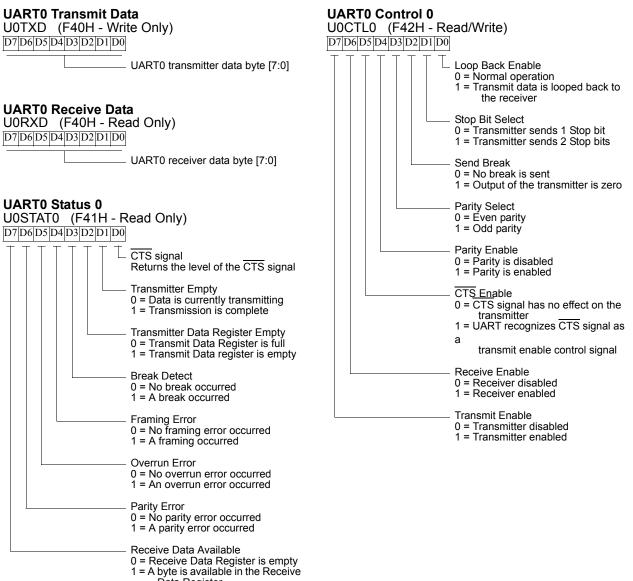

Figure 11 displays a block diagram of the interrupt controller.

Figure 11. Interrupt Controller Block Diagram

# Operation

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Executing an Enable Interrupt (EI) instruction.

- Executing an Return from Interrupt (IRET) instruction.

- Writing a 1 to the IRQE bit in the Interrupt Control register.

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction.

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller.

- Writing a 0 to the IRQE bit in the Interrupt Control register.

- Reset.

# Zilog <sub>74</sub>

where *x* indicates the specific GPIO Port C pin number (0 through 3).

## **IRQ0 Enable High and Low Bit Registers**

The IRQ0 Enable High and Low Bit registers (see Table 28 and Table 29 on page 75) form a priority encoded enabling for interrupts in the Interrupt Request 0 register. Priority is generated by setting bits in each register. Table 27 describes the priority control for IRQ0.

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

### Table 27. IRQ0 Enable and Priority Encoding

Note: where x indicates the register bits from 0 through 7.

#### Table 28. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7     | 6     | 5            | 4             | 3      | 2      | 1      | 0      |  |  |  |

|-------|-------|-------|--------------|---------------|--------|--------|--------|--------|--|--|--|

| FIELD | T2ENH | T1ENH | <b>T0ENH</b> | <b>U0RENH</b> | U0TENH | I2CENH | SPIENH | ADCENH |  |  |  |

| RESET | 0     |       |              |               |        |        |        |        |  |  |  |

| R/W   |       | R/W   |              |               |        |        |        |        |  |  |  |

| ADDR  | FC1H  |       |              |               |        |        |        |        |  |  |  |

T2ENH—Timer 2 Interrupt Request Enable High Bit T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit I2CENH—I<sup>2</sup>C Interrupt Request Enable High Bit SPIENH—SPI Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

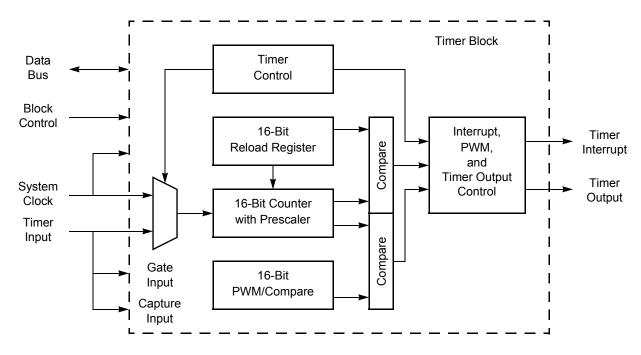

Figure 12. Timer Block Diagram

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

### **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. Then, the timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is desired to have the Timer Output make a permanent state change upon

# zilog

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

# WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the Reset state. The WDT status bit in the Watchdog Timer Control register is set to 1. For more information on Reset, see Reset and Stop Mode Recovery on page 47.

# WDT Reset in STOP Mode

If enabled in STOP mode and configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following WDT time-out in STOP mode. Default operation is for the WDT and its RC oscillator to be enabled during STOP mode.

# WDT RC Disable in STOP Mode

To minimize power consumption in STOP Mode, the WDT and its RC oscillator can be disabled in STOP mode. The following sequence configures the WDT to be disabled when the 64K Series devices enter STOP Mode following execution of a STOP instruction:

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write 81H to the Watchdog Timer Control register (WDTCTL) to configure the WDT and its oscillator to be disabled during STOP Mode. Alternatively, write 00H to the Watchdog Timer Control register (WDTCTL) as the third step in this sequence to reconfigure the WDT and its oscillator to be enabled during STOP mode.

This sequence only affects WDT operation in STOP mode.

# Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. Follow the steps below to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

# zilog 105

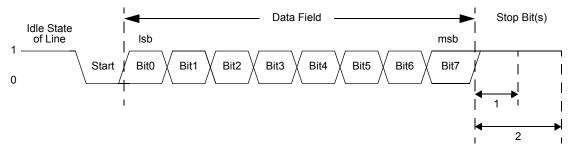

Figure 14. UART Asynchronous Data Format without Parity

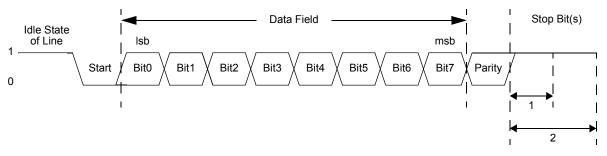

Figure 15. UART Asynchronous Data Format with Parity

# Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. If MULTIPROCESSOR mode is desired, write to the UART Control 1 register to enable MULTIPROCESSOR (9-bit) mode functions.

- Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- 4. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- If parity is desired and MULTIPROCESSOR mode is not enabled, set the parity enable bit (PEN) and select either Even or Odd parity (PSEL).

- 3. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and await more data.

# Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this would typically be done during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

## **MULTIPROCESSOR (9-bit) Mode**

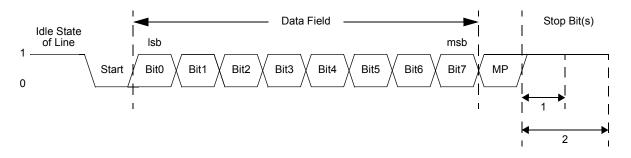

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTI-PROCESSOR mode (also referred to as 9-Bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 16. The character format is:

### Figure 16. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the MUL-TIPROCESSOR control bit. The UART Control 1 and Status 1 registers provide MULTI-PROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor

- 01 = The UART generates an interrupt request only on received address bytes.

- 10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

- 11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—MULTIPROCESSOR Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled.

- 0 = Send a 0 in the multiprocessor bit location of the data stream (9<sup>th</sup> bit).

- 1 = Send a 1 in the multiprocessor bit location of the data stream (9<sup>th</sup> bit).

#### DEPOL—Driver Enable Polarity

- 0 = DE signal is Active High.

- 1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes different UART behavior depending on whether the UART receiver is enabled (REN = 1 in the UART Control 0 Register).

When the UART receiver is not enabled, this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value

1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled, this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

- 0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.

- 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the High Byte when the Low Byte is read.

RDAIRQ—Receive Data Interrupt Enable

- 0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

- 1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 =Infrared Encoder/Decoder is disabled. UART operates normally operation.

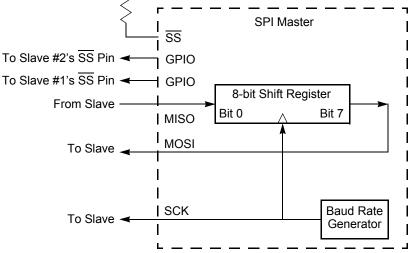

Figure 23. SPI Configured as a Master in a Single Master, Multiple Slave System

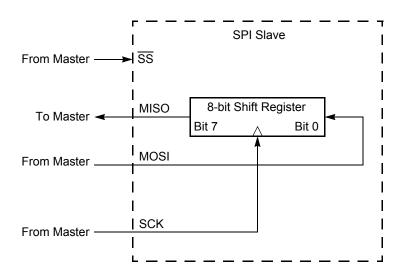

Figure 24. SPI Configured as a Slave

# Operation

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (serial clock, transmit, receive and Slave select). The SPI block consists of a transmit/receive shift register, a Baud Rate (clock) Generator and a control unit.

Table 64. SPI Control Register (SPICTL)

| BITS  | 7    | 6    | 5    | 4     | 3      | 2   | 1    | 0     |  |  |  |

|-------|------|------|------|-------|--------|-----|------|-------|--|--|--|

| FIELD | IRQE | STR  | BIRQ | PHASE | CLKPOL | WOR | MMEN | SPIEN |  |  |  |

| RESET | 0    |      |      |       |        |     |      |       |  |  |  |

| R/W   |      | R/W  |      |       |        |     |      |       |  |  |  |

| ADDR  |      | F61H |      |       |        |     |      |       |  |  |  |

IRQE—Interrupt Request Enable

0 = SPI interrupts are disabled. No interrupt requests are sent to the Interrupt Controller.

1 = SPI interrupts are enabled. Interrupt requests are sent to the Interrupt Controller.

STR—Start an SPI Interrupt Request

0 = No effect.

1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART. Writing a 1 to the IRQ bit in the SPI Status register clears this bit to 0.

BIRQ-BRG Timer Interrupt Request

If the SPI is enabled, this bit has no effect. If the SPI is disabled:

0 = The Baud Rate Generator timer function is disabled.

1 = The Baud Rate Generator timer function and time-out interrupt are enabled.

PHASE—Phase Select

Sets the phase relationship of the data to the clock. For more information on operation of the PHASE bit, see SPI Clock Phase and Polarity Control on page 132.

CLKPOL—Clock Polarity

0 = SCK idles Low (0).

1 = SCK idle High (1).

WOR-Wire-OR (OPEN-DRAIN) Mode Enabled

0 = SPI signal pins not configured for open-drain.

$1 = \text{All four SPI signal pins (SCK, \overline{SS}, MISO, MOSI)}$  configured for open-drain function. This setting is typically used for multi-master and/or multi-slave configurations.

MMEN—SPI Master Mode Enable

0 = SPI configured in Slave mode.

1 = SPI configured in Master mode.

SPIEN—SPI Enable

0 = SPI disabled.

1 = SPI enabled.

# zilog

While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Interrupts that occur when a Programming operation is in progress are serviced once the Programming operation is complete. To exit Programming mode and lock the Flash Controller, write 00H to the Flash Control register.

User code cannot program Flash Memory on a page that lies in a protected sector. When user code writes memory locations, only addresses located in the unlocked page are programmed. Memory writes outside of the unlocked page are ignored.

**Caution:** Each memory location must not be programmed more than twice before an erase occurs.

Follow the steps below to program the Flash from user code:

- 1. Write 00H to the Flash Control register to reset the Flash Controller.

- 2. Write the page of memory to be programmed to the Page Select register.

- 3. Write the first unlock command 73H to the Flash Control register.

- 4. Write the second unlock command 8CH to the Flash Control register.

- 5. Re-write the page written in step 2 to the Page Select register.

- 6. Write Flash Memory using LDC or LDCI instructions to program the Flash.

- 7. Repeat step 6 to program additional memory locations on the same page.

- 8. Write 00H to the Flash Control register to lock the Flash Controller.

# Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Page Select register identifies the page to be erased. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. Interrupts that occur when the Page Erase operation is in progress are serviced once the Page Erase operation is complete. When the Page Erase operation is complete, the Flash Controller returns to its locked state. Only pages located in unprotected sectors can be erased.

Follow the steps below to perform a Page Erase operation:

- 1. Write 00H to the Flash Control register to reset the Flash Controller.

- 2. Write the page to be erased to the Page Select register.

- 3. Write the first unlock command 73H to the Flash Control register.

- 4. Write the second unlock command 8CH to the Flash Control register.

zilog

225

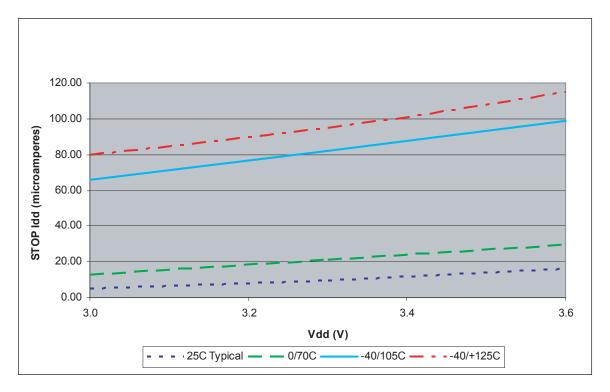

Figure 48 displays the maximum current consumption in STOP mode with the VBO disabled and Watchdog Timer enabled versus the power supply voltage. All GPIO pins are configured as outputs and driven High. Disabling the Watchdog Timer and its internal RC oscillator in STOP mode will provide some additional reduction in STOP mode current consumption. This small current reduction would be indistinguishable on the scale of Figure 48.

### Figure 48. Maximum STOP Mode Idd with VBO Disabled versus Power Supply Voltage

zilog

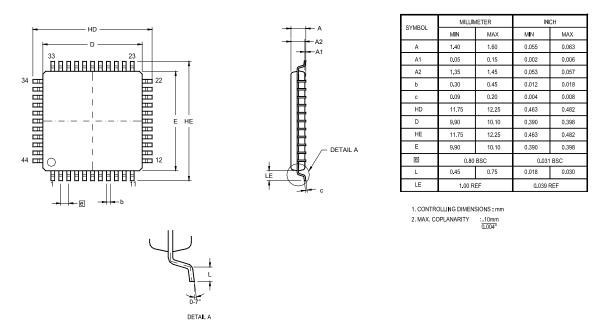

Figure 63 displays the 44-pin Low Profile Quad Flat Package (LQFP) available for the Z8X1621, Z8X2421, Z8X3221, Z8X4821, and Z8X6421 devices.

Figure 63. 44-Lead Low-Profile Quad Flat Package (LQFP)

| Part Number                                        | Flash      | RAM   | ) Lines           | nterrupts | 6-Bit Timers w/PWM | 10-Bit A/D Channels | 0                | -   | <b>UARTs with IrDA</b> | Description         |

|----------------------------------------------------|------------|-------|-------------------|-----------|--------------------|---------------------|------------------|-----|------------------------|---------------------|

| مّ<br>Z8F322x with 32 KB Flas                      |            |       | <u>♀</u><br>-to-D | _         | 1                  | -                   | I <sup>2</sup> C | SPI | )<br>)                 | ă                   |

| Standard Temperature: 0 °                          |            |       | -10-D             | igite     |                    |                     |                  |     |                        |                     |

| Z8F3221PM020SC                                     | 32 KB      | 2 KB  | 29                | 23        | 3                  | 8                   | 1                | 1   | 2                      | PDIP 40-pin package |

| Z8F3221AN020SC                                     | 32 KB      | 2 KB  | 31                | 23        | 3                  | 8                   | 1                | 1   | 2                      |                     |

|                                                    | -          |       | -                 |           | -                  | -                   |                  |     | _                      | LQFP 44-pin package |

| Z8F3221VN020SC                                     | 32 KB      | 2 KB  | 31                | 23        | 3                  | 8                   | 1                | 1   | 2                      | PLCC 44-pin package |

| Z8F3222AR020SC                                     | 32 KB      | 2 KB  | 46                | 24        | 4                  | 12                  | 1                | 1   | 2                      | LQFP 64-pin package |

| Z8F3222VS020SC                                     | 32 KB      | 2 KB  | 46                | 24        | 4                  | 12                  | 1                | 1   | 2                      | PLCC 68-pin package |

| Extended Temperature: -4                           | 0 °C to 10 | 05 °C |                   |           |                    |                     |                  |     |                        |                     |

| Z8F3221PM020EC                                     | 32 KB      | 2 KB  | 29                | 23        | 3                  | 8                   | 1                | 1   | 2                      | PDIP 40-pin package |

| Z8F3221AN020EC                                     | 32 KB      | 2 KB  | 31                | 23        | 3                  | 8                   | 1                | 1   | 2                      | LQFP 44-pin package |

| Z8F3221VN020EC                                     | 32 KB      | 2 KB  | 31                | 23        | 3                  | 8                   | 1                | 1   | 2                      | PLCC 44-pin package |

| Z8F3222AR020EC                                     | 32 KB      | 2 KB  | 46                | 24        | 4                  | 12                  | 1                | 1   | 2                      | LQFP 64-pin package |

| Z8F3222VS020EC                                     | 32 KB      | 2 KB  | 46                | 24        | 4                  | 12                  | 1                | 1   | 2                      | PLCC 68-pin package |

| Automotive/Industrial Temperature: –40 °C to 125°C |            |       |                   |           |                    |                     |                  |     |                        |                     |

| Z8F3221PM020AC                                     | 32 KB      | 2 KB  | 29                | 23        | 3                  | 8                   | 1                | 1   | 2                      | PDIP 40-pin package |

| Z8F3221AN020AC                                     | 32 KB      | 2 KB  | 31                | 23        | 3                  | 8                   | 1                | 1   | 2                      | LQFP 44-pin package |

| Z8F3221VN020AC                                     | 32 KB      | 2 KB  | 31                | 23        | 3                  | 8                   | 1                | 1   | 2                      | PLCC 44-pin package |

| Z8F3222AR020AC                                     | 32 KB      | 2 KB  | 46                | 24        | 4                  | 12                  | 1                | 1   | 2                      | LQFP 64-pin package |

| Z8F3222VS020AC                                     | 32 KB      | 2 KB  | 46                | 24        | 4                  | 12                  | 1                | 1   | 2                      | PLCC 68-pin package |

272

# Index

# **Symbols**

# 244 % 244 @ 244

# **Numerics**

10-bit ADC 4 40-lead plastic dual-inline package 265 44-lead low-profile quad flat package 266 44-lead plastic lead chip carrier package 267 64-lead low-profile quad flat package 267 68-lead plastic lead chip carrier package 268 80-lead quad flat package 269

# Α

absolute maximum ratings 215 AC characteristics 231 ADC 246 architecture 175 automatic power-down 176 block diagram 176 continuous conversion 177 control register 179 control register definitions 179 data high byte register 180 data low bits register 180 DMA control 178 electrical characteristics and timing 229 operation 176 single-shot conversion 177 ADCCTL register 179 ADCDH register 180 ADCDL register 180 ADCX 246 ADD 246 add - extended addressing 246 add with carry 246 add with carry - extended addressing 246

additional symbols 244 address space 19 ADDX 246 analog signals 15 analog-to-digital converter (ADC) 175 AND 248 ANDX 248 arithmetic instructions 246 assembly language programming 241 assembly language syntax 242

# В

B 244 b 243 baud rate generator, UART 113 BCLR 246 binary number suffix 244 **BIT 246** bit 243 clear 246 manipulation instructions 246 set 246 set or clear 246 swap 247 test and jump 249 test and jump if non-zero 249 test and jump if zero 249 bit jump and test if non-zero 249 bit swap 249 block diagram 3 block transfer instructions 247 **BRK 249 BSET 246** BSWAP 247, 249 **BTJ 249** BTJNZ 249 BTJZ 249

# С

CALL procedure 249 capture mode 95 capture/compare mode 95

283

Operational Description 103 OR 248 ordering information 270 ORX 248 oscillator signals 15

# Ρ

p 243 packaging LQFP 44 lead 266 64 lead 267 **PDIP 265** PLCC 44 lead 267 68 lead 268 **OFP 269** part number description 275 part selection guide 2 PC 244 **PDIP 265** peripheral AC and DC electrical characteristics 226 PHASE=0 timing (SPI) 133 PHASE=1 timing (SPI) 134 pin characteristics 16 PLCC 44 lead 267 68-lead 268 polarity 243 POP 248 pop using extended addressing 248 **POPX 248** port availability, device 57 port input timing (GPIO) 232 port output timing, GPIO 233 power supply signals 16 power-down, automatic (ADC) 176 power-on and voltage brown-out 226 power-on reset (POR) 49 program control instructions 249 program counter 244 program memory 20 **PUSH 248**

push using extended addressing 248 PUSHX 248 PWM mode 94 PxADDR register 61 PxCTL register 62

# Q

QFP 269

# R

R 243 r 243 RA register address 243 RCF 247 receive 10-bit data format (I2C) 154 7-bit data transfer format (I2C) 153 IrDA data 127 receive interrupt 145 receiving UART data-interrupt-driven method 108 receiving UART data-polled method 107 register 140, 169, 243 ADC control (ADCCTL) 179 ADC data high byte (ADCDH) 180 ADC data low bits (ADCDL) 180 baud low and high byte (I2C) 160, 161, 163 baud rate high and low byte (SPI) 142 control (SPI) 137 control, I2C 158 data, SPI 137 DMA status (DMAA STAT) 173 DMA ADC address 171 DMA ADC control DMAACTL) 172 DMAx address high nibble (DMAxH) 169 DMAx control (DMAxCTL) 167 DMAx end/address low byte (DMAxEND) 170 DMAx start/current address low byte register (DMAxSTART) 170 flash control (FCTL) 190 flash high and low byte (FFREQH and FRE-EQL) 192