Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4821vn020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| Manual Objectives xi                                                                                                            | ii     |

|---------------------------------------------------------------------------------------------------------------------------------|--------|

| About This Manualxi                                                                                                             |        |

| Manual Conventionsxi                                                                                                            |        |

| Introduction                                                                                                                    | 1      |

| Features       2         Part Selection Guide       2         Block Diagram       3         CPU and Peripheral Overview       3 | 2<br>3 |

| eZ8 <sup>™</sup> CPU Features                                                                                                   |        |

| General-Purpose Input/Output                                                                                                    |        |

| Flash Controller    4      10-Bit Analog-to-Digital Converter    4                                                              |        |

| UARTs                                                                                                                           |        |

| I <sup>2</sup> C Serial Peripheral Interface                                                                                    |        |

| Timers                                                                                                                          | 5      |

| Reset Controller    8      On-Chip Debugger    8      DMA Controller    8                                                       | 5<br>5 |

| Signal and Pin Descriptions                                                                                                     |        |

| Overview       7         Available Packages       7         Pin Configurations       8                                          | 7<br>7 |

| Pin Configurations       14         Signal Descriptions       14         Pin Characteristics       16                           | 4      |

| Address Space                                                                                                                   | 9      |

| Overview       19         Register File       19         Program Memory       20         Data Memory       21                   | 9<br>0 |

| Data Memory 2'                                                                                                                  | 1      |

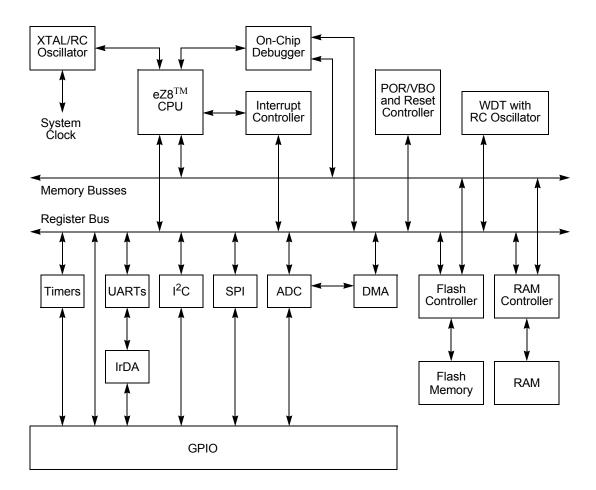

## **Block Diagram**

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP 64K Series Flash Microcontrollers.

## **CPU and Peripheral Overview**

## eZ8<sup>™</sup> CPU Features

The latest 8-bit eZ8 CPU meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{\mathbb{R}}$  instruction set.

| Program Memory Address (Hex)              | Function                 |

|-------------------------------------------|--------------------------|

| 0000-0001                                 | Option Bits              |

| 0002-0003                                 | Reset Vector             |

| 0004-0005                                 | WDT Interrupt Vector     |

| 0006-0007                                 | Illegal Instruction Trap |

| 0008-0037                                 | Interrupt Vectors*       |

| 0038-BFFF                                 | Program Memory           |

| Z8F642x Products                          |                          |

| 0000-0001                                 | Option Bits              |

| 0002-0003                                 | Reset Vector             |

| 0004-0005                                 | WDT Interrupt Vector     |

| 0006-0007                                 | Illegal Instruction Trap |

| 0008-0037                                 | Interrupt Vectors*       |

| 0038-FFFF                                 | Program Memory           |

| *See Table 23 on page 68 for a list of th | ne interrupt vectors.    |

#### Table 5. Z8 Encore! XP 64K Series Flash Microcontrollers Program Memory Maps (Continued)

### **Data Memory**

The Z8 Encore! XP 64K Series Flash Microcontrollers does not use the eZ8 CPU's 64 KB Data Memory address space.

### **Information Area**

Table 6 on page 22 describes the Z8 Encore! XP 64K Series Flash Microcontrollers Information Area. This 512 byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into the Program Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, execution of LDC and LDCI instruction from these Program Memory addresses return the Information Area data rather than the Program Memory data. Reads of these addresses through the On-Chip Debugger also returns the Information Area data. Execution of code from these addresses continues to correctly use the Program Memory. Access to the Information Area is read-only.

# zilog

| Address (Hex)   | · · ·                              | Mnemonic  | Reset (Hex) | Page No |

|-----------------|------------------------------------|-----------|-------------|---------|

| -61             | SPI Control                        | SPICTL    | 00          | 137     |

| F62             | SPI Status                         | SPISTAT   | 01          | 139     |

| F63             | SPI Mode                           | SPIMODE   | 00          | 140     |

| F64             | SPI Diagnostic State               | SPIDST    | 00          | 141     |

| F65             | Reserved                           | _         | XX          |         |

| F66             | SPI Baud Rate High Byte            | SPIBRH    | FF          | 142     |

| F67             | SPI Baud Rate Low Byte             | SPIBRL    | FF          | 142     |

| F68-F6F         | Reserved                           | _         | XX          |         |

| Analog-to-Digit | tal Converter                      |           |             |         |

| F70             | ADC Control                        | ADCCTL    | 20          | 179     |

| F71             | Reserved                           | _         | XX          |         |

| F72             | ADC Data High Byte                 | ADCD_H    | XX          | 180     |

| F73             | ADC Data Low Bits                  | ADCD_L    | XX          | 180     |

| F74-FAF         | Reserved                           | _         | XX          |         |

| DMA 0           |                                    |           |             |         |

| FB0             | DMA0 Control                       | DMA0CTL   | 00          | 167     |

| FB1             | DMA0 I/O Address                   | DMA0IO    | XX          | 169     |

| FB2             | DMA0 End/Start Address High Nibble | DMA0H     | XX          | 169     |

| FB3             | DMA0 Start Address Low Byte        | DMA0START | XX          | 170     |

| FB4             | DMA0 End Address Low Byte          | DMA0END   | XX          | 170     |

| DMA 1           |                                    |           |             |         |

| FB8             | DMA1 Control                       | DMA1CTL   | 00          | 167     |

| FB9             | DMA1 I/O Address                   | DMA1IO    | XX          | 169     |

| FBA             | DMA1 End/Start Address High Nibble | DMA1H     | XX          | 169     |

| FBB             | DMA1 Start Address Low Byte        | DMA1START | XX          | 170     |

| FBC             | DMA1 End Address Low Byte          | DMA1END   | XX          | 170     |

| DMA ADC         |                                    |           |             |         |

| FBD             | DMA ADC Address                    | DMAA_ADDR | XX          | 171     |

| FBE             | DMA ADC Control                    | DMAACTL   | 00          | 172     |

| FBF             | DMA ADC Status                     | DMAASTAT  | 00          | 173     |

| Interrupt Contr |                                    | _         |             | -       |

| FC0             | Interrupt Request 0                | IRQ0      | 00          | 71      |

| FC1             | IRQ0 Enable High Bit               | IRQ0ENH   | 00          | 74      |

| FC2             | IRQ0 Enable Low Bit                | IRQ0ENL   | 00          | 74      |

| FC3             | Interrupt Request 1                | IRQ1      | 00          | 72      |

| FC4             | IRQ1 Enable High Bit               | IRQ1ENH   | 00          | 75      |

| FC5             | IRQ1 Enable Low Bit                | IRQ1ENL   | 00          | 75      |

| FC6             | Interrupt Request 2                | IRQ2      | 00          | 73      |

| FC7             | IRQ2 Enable High Bit               | IRQ2ENH   | 00          | 76      |

| FC8             | IRQ2 Enable Low Bit                | IRQ2ENL   | 00          | 76      |

| FC9-FCC         | Reserved                           |           | XX          |         |

Table 7. Z8 Encore! XP 64K Series Flash Microcontrollers Register File Address Map (Continued)

Reserved

## zilog

T1I—Timer 1 Interrupt Request

0 = No interrupt request is pending for Timer 1.

1 = An interrupt request from Timer 1 is awaiting service.

T0I—Timer 0 Interrupt Request

0 = No interrupt request is pending for Timer 0.

1 = An interrupt request from Timer 0 is awaiting service.

U0RXI—UART 0 Receiver Interrupt Request

0 = No interrupt request is pending for the UART 0 receiver.

1 = An interrupt request from the UART 0 receiver is awaiting service.

U0TXI-UART 0 Transmitter Interrupt Request

0 = No interrupt request is pending for the UART 0 transmitter.

1 = An interrupt request from the UART 0 transmitter is awaiting service.

I<sup>2</sup>CI— I<sup>2</sup>C Interrupt Request

0 = No interrupt request is pending for the I<sup>2</sup>C.

1 = An interrupt request from the I<sup>2</sup>C is awaiting service.

SPII—SPI Interrupt Request

0 = No interrupt request is pending for the SPI.

1 = An interrupt request from the SPI is awaiting service.

ADCI—ADC Interrupt Request

0 = No interrupt request is pending for the Analog-to-Digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

## Interrupt Request 1 Register

The Interrupt Request 1 (IRQ1) register (Table 25) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

| BITS  | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| FIELD | PAD7I | PAD6I | PAD5I | PAD4I | PAD3I | PAD2I | PAD1I | PAD0I |  |  |  |

| RESET |       |       |       | (     | )     |       |       |       |  |  |  |

| R/W   |       | R/W   |       |       |       |       |       |       |  |  |  |

| ADDR  |       |       |       | FC    | 3H    |       |       |       |  |  |  |

| Table 25. | Interrupt | <b>Request 1</b> | Register | (IRQ1) |

|-----------|-----------|------------------|----------|--------|

|-----------|-----------|------------------|----------|--------|

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H), affecting only the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control 1 register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation must be used to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO Port pin Timer Input alternate function. The TPOL bit in the Timer Control 1 Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** *The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency.*

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control 1 register to:

- Disable the timer

- Configure the timer for COUNTER mode

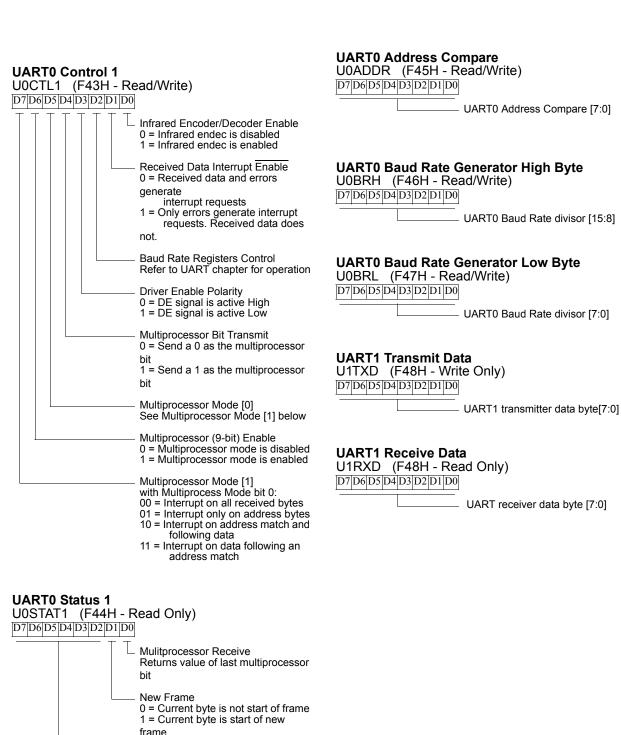

## Table 59. UART Baud Rate High Byte Register (UxBRH)

| BITS  | 7   | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |  |

|-------|-----|-----|---|---------|---------|---|---|---|--|--|--|--|

| FIELD | BRH |     |   |         |         |   |   |   |  |  |  |  |

| RESET |     | 1   |   |         |         |   |   |   |  |  |  |  |

| R/W   |     | R/W |   |         |         |   |   |   |  |  |  |  |

| ADDR  |     |     |   | F46H ar | nd F4EH |   |   |   |  |  |  |  |

## Table 60. UART Baud Rate Low Byte Register (UxBRL)

| BITS  | 7   | 6   | 5 | 4       | 3       | 2 | 1 | 0 |  |  |

|-------|-----|-----|---|---------|---------|---|---|---|--|--|

| FIELD | BRL |     |   |         |         |   |   |   |  |  |

| RESET |     |     |   |         | 1       |   |   |   |  |  |

| R/W   |     | R/W |   |         |         |   |   |   |  |  |

| ADDR  |     |     |   | F47H ar | nd F4FH |   |   |   |  |  |

For a given UART data rate, the integer baud rate divisor value is calculated using the following equation:

UART Baud Rate Divisor Value (BRG) =  $Round\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the desired baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 61 provides information on data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

## **Architecture**

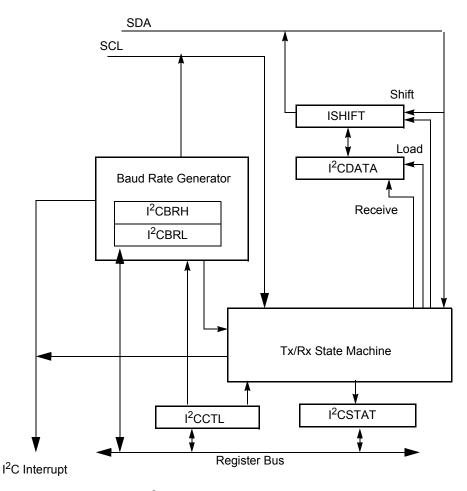

Figure 27 displays the architecture of the I<sup>2</sup>C Controller.

## Operation

The I<sup>2</sup>C Controller operates in MASTER mode to transmit and receive data. Only a single master is supported. Arbitration between two masters must be accomplished in software. I<sup>2</sup>C supports the following operations:

- Master transmits to a 7-bit slave •

- Master transmits to a 10-bit slave •

## Table 70. I<sup>2</sup>C Data Register (I2CDATA)

| BITS  | 7    | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|-------|------|-----|---|----|----|---|---|---|--|--|--|--|

| FIELD | DATA |     |   |    |    |   |   |   |  |  |  |  |

| RESET |      | 0   |   |    |    |   |   |   |  |  |  |  |

| R/W   |      | R/W |   |    |    |   |   |   |  |  |  |  |

| ADDR  |      |     |   | F5 | 0H |   |   |   |  |  |  |  |

## I<sup>2</sup>C Status Register

The Read-only I<sup>2</sup>C Status register (Table 71) indicates the status of the I<sup>2</sup>C Controller.

| Table 71. I <sup>2</sup> C Statu | s Register (I2CSTAT) |

|----------------------------------|----------------------|

|----------------------------------|----------------------|

| BITS  | 7    | 6    | 5   | 4   | 3  | 2   | 1   | 0    |  |  |  |

|-------|------|------|-----|-----|----|-----|-----|------|--|--|--|

| FIELD | TDRE | RDRF | ACK | 10B | RD | TAS | DSS | NCKI |  |  |  |

| RESET | 1    |      |     |     | 0  |     |     |      |  |  |  |

| R/W   |      | R    |     |     |    |     |     |      |  |  |  |

| ADDR  |      |      |     | F5  | 1H |     |     |      |  |  |  |

#### TDRE—Transmit Data Register Empty

When the I<sup>2</sup>C Controller is enabled, this bit is 1 when the I<sup>2</sup>C Data register is empty. When this bit is set, an interrupt is generated if the TXI bit is set, except when the I<sup>2</sup>C Controller is shifting in data during the reception of a byte or when shifting an address and the RD bit is set. This bit is cleared by writing to the I2CDATA register.

#### RDRF—Receive Data Register Full

This bit is set = 1 when the I<sup>2</sup>C Controller is enabled and the I<sup>2</sup>C Controller has received a byte of data. When asserted, this bit causes the I<sup>2</sup>C Controller to generate an interrupt. This bit is cleared by reading the I<sup>2</sup>C Data register (unless the read is performed using execution of the On-Chip Debugger's Read Register command).

#### ACK—Acknowledge

This bit indicates the status of the Acknowledge for the last byte transmitted or received. When set, this bit indicates that an Acknowledge occurred for the last byte transmitted or received. This bit is cleared when IEN = 0 or when a Not Acknowledge occurred for the last byte transmitted or received. It is not reset at the beginning of each transaction and is not reset when this register is read.

## zilog

160

## I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers (Tables 73 and 73) combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator.

When the  $I^2C$  is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the  $I^2C$  by clearing the IEN bit in the  $I^2C$  Control register to 0.

- 2. Load the desired 16-bit count value into the I<sup>2</sup>C Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the I<sup>2</sup>C Control register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

## Table 73. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH)

| BITS  | 7   | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|-----|-----|---|----|----|---|---|---|--|--|--|

| FIELD | BRH |     |   |    |    |   |   |   |  |  |  |

| RESET |     |     |   | FF | ۶H |   |   |   |  |  |  |

| R/W   |     | R/W |   |    |    |   |   |   |  |  |  |

| ADDR  |     |     |   | F5 | 3H |   |   |   |  |  |  |

$BRH = I^2C$  Baud Rate High Byte

Most significant byte, BRG[15:8], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRH register returns the current value of the  $I^2C$  Baud Rate Counter[15:8].

162

| TXRXSTATE | State Description                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0_000     | Idle State                                                                                                                              |

| 0_0001    | START State                                                                                                                             |

| 0_0010    | Send/Receive data bit 7                                                                                                                 |

| 0_0011    | Send/Receive data bit 6                                                                                                                 |

| 0_0100    | Send/Receive data bit 5                                                                                                                 |

| 0_0101    | Send/Receive data bit 4                                                                                                                 |

| 0_0110    | Send/Receive data bit 3                                                                                                                 |

| 0_0111    | Send/Receive data bit 2                                                                                                                 |

| 0_1000    | Send/Receive data bit 1                                                                                                                 |

| 0_1001    | Send/Receive data bit 0                                                                                                                 |

| 0_1010    | Data Acknowledge State                                                                                                                  |

| 0_1011    | Second half of data Acknowledge State used only for not acknowledge                                                                     |

| 0_1100    | First part of STOP state                                                                                                                |

| 0_1101    | Second part of STOP state                                                                                                               |

| 0_1110    | 10-bit addressing: Acknowledge State for 2nd address byte<br>7-bit addressing: Address Acknowledge State                                |

| 0_1111    | 10-bit address: Bit 0 (Least significant bit) of 2nd address byte<br>7-bit address: Bit 0 (Least significant bit) (R/W) of address byte |

| 1_0000    | 10-bit addressing: Bit 7 (Most significant bit) of 1st address byte                                                                     |

| 1_0001    | 10-bit addressing: Bit 6 of 1st address byte                                                                                            |

| 1_0010    | 10-bit addressing: Bit 5 of 1st address byte                                                                                            |

| 1_0011    | 10-bit addressing: Bit 4 of 1st address byte                                                                                            |

| 1_0100    | 10-bit addressing: Bit 3 of 1st address byte                                                                                            |

| 1_0101    | 10-bit addressing: Bit 2 of 1st address byte                                                                                            |

| 1_0110    | 10-bit addressing: Bit 1 of 1st address byte                                                                                            |

| 1_0111    | 10-bit addressing: Bit 0 (R/W) of 1st address byte                                                                                      |

| 1_1000    | 10-bit addressing: Acknowledge state for 1st address byte                                                                               |

| 1_1001    | 10-bit addressing: Bit 7 of 2nd address byte<br>7-bit addressing: Bit 7 of address byte                                                 |

| 1_1010    | 10-bit addressing: Bit 6 of 2nd address byte<br>7-bit addressing: Bit 6 of address byte                                                 |

| 1_1011    | 10-bit addressing: Bit 5 of 2nd address byte<br>7-bit addressing: Bit 5 of address byte                                                 |

| 1_1100    | 10-bit addressing: Bit 4 of 2nd address byte<br>7-bit addressing: Bit 4 of address byte                                                 |

| ົ | n | E |

|---|---|---|

| 2 | υ | J |

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Read Protect Option Bit                                                                                                                            |  |  |  |  |

|----------------------------|-----------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Write Program Counter      | 06H             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Read Program Counter       | 07H             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Write Register             | 08H             | -                                     | Only writes of the Flash Memory Contr<br>registers are allowed. Additionally, or<br>the Mass Erase command is allowed<br>be written to the Flash Control register |  |  |  |  |

| Read Register              | 09H             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Write Program Memory       | 0AH             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Read Program Memory        | 0BH             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Write Data Memory          | 0CH             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Read Data Memory           | 0DH             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Read Program Memory<br>CRC | 0EH             | -                                     | -                                                                                                                                                                 |  |  |  |  |

| Reserved                   | 0FH             | -                                     | -                                                                                                                                                                 |  |  |  |  |

| Step Instruction           | 10H             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Stuff Instruction          | 11H             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Execute Instruction        | 12H             | -                                     | Disabled                                                                                                                                                          |  |  |  |  |

| Reserved                   | 13H - FFH       | -                                     | -                                                                                                                                                                 |  |  |  |  |

#### Table 101. On-Chip Debugger Commands (Continued)

In the following list of OCD Commands, data and commands sent from the host to the On-Chip Debugger are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the On-Chip Debugger back to the host is identified by 'DBG  $\rightarrow$  Data'

• **Read OCD Revision (00H)**—The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

DBG  $\leftarrow$  00H DBG  $\rightarrow$  OCDREV[15:8] (Major revision number) DBG  $\rightarrow$  OCDREV[7:0] (Minor revision number)

• **Read OCD Status Register (02H)**—The Read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 105 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, unused inputs must be tied to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +125    | С     |       |

| Storage temperature                                 | -65     | +150    | С     |       |

| Voltage on any pin with respect to $V_{SS}$         | -0.3    | +5.5    | V     | 1     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 80-Pin QFP Maximum Ratings at –40 °C to 70 °C       |         |         |       |       |

| Total power dissipation                             |         | 550     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 150     | mA    |       |

| 80-Pin QFP Maximum Ratings at 70 °C to 125 °C       |         |         |       |       |

| Total power dissipation                             |         | 200     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 56      | mA    |       |

| 68-Pin PLCC Maximum Ratings at –40 °C to 70 °C      |         |         |       |       |

| Total power dissipation                             |         | 1000    | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 275     | mA    |       |

| 68-Pin PLCC Maximum Ratings at 70 °C to 125 °C      |         |         |       |       |

| Total power dissipation                             |         | 500     | mW    |       |

|                                                     |         |         |       |       |

#### Table 105. Absolute Maximum Ratings

zilog

225

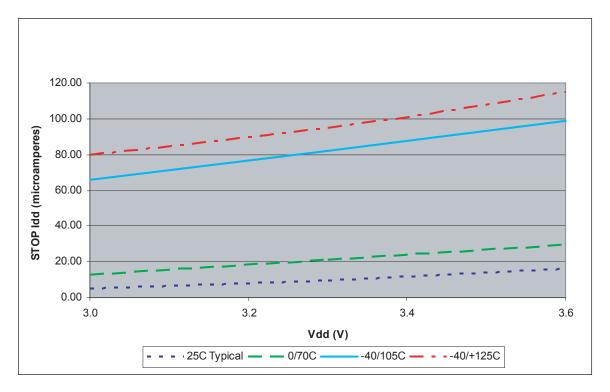

Figure 48 displays the maximum current consumption in STOP mode with the VBO disabled and Watchdog Timer enabled versus the power supply voltage. All GPIO pins are configured as outputs and driven High. Disabling the Watchdog Timer and its internal RC oscillator in STOP mode will provide some additional reduction in STOP mode current consumption. This small current reduction would be indistinguishable on the scale of Figure 48.

#### Figure 48. Maximum STOP Mode Idd with VBO Disabled versus Power Supply Voltage

#### Table 123. Additional Symbols

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

## **Condition Codes**

The C, Z, S and V Flags control the operation of the conditional jump (JP cc and JR cc) instructions. Sixteen frequently useful functions of the Flag settings are encoded in a 4-bit field called the condition code (cc), which forms Bits 7:4 of the conditional jump instructions. The condition codes are summarized in Table 124. Some binary condition codes can be created using more than one assembly code mnemonic. The result of the Flag test operation decides if the conditional jump is executed.

| Binary | Hex | Assembly<br>Mnemonic | Definition         | Flag Test Operation  |

|--------|-----|----------------------|--------------------|----------------------|

| 0000   | 0   | F                    | Always False       | -                    |

| 0001   | 1   | LT                   | Less Than          | (S XOR V) = 1        |

| 0010   | 2   | LE                   | Less Than or Equal | (Z OR (S XOR V)) = 1 |

#### Table 124. Condition Codes

| Assembly                                                                                                   | Symbolic Operation            | Address<br>Mode |     | _ Opcode(s) | Flags |            |               |   |   |   | - Fetch | Instr. |

|------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|-----|-------------|-------|------------|---------------|---|---|---|---------|--------|

| Mnemonic                                                                                                   |                               | dst             | src | (Hex)       | С     | Ζ          | S             | V | D | Н |         | Cycles |

| XOR dst, src                                                                                               | $dst \gets dst \: XOR \: src$ | r               | r   | B2          | -     | *          | *             | 0 | - | - | 2       | 3      |

|                                                                                                            | -                             | r               | lr  | B3          |       |            |               |   |   |   | 2       | 4      |

|                                                                                                            | -                             | R               | R   | B4          |       |            |               |   |   |   | 3       | 3      |

|                                                                                                            | -                             | R               | IR  | B5          |       |            |               |   |   |   | 3       | 4      |

|                                                                                                            | -                             | R               | IM  | B6          |       |            |               |   |   |   | 3       | 3      |

|                                                                                                            | -                             | IR              | IM  | B7          |       |            |               |   |   |   | 3       | 4      |

| XORX dst, src dst $\leftarrow$ dst XOR src                                                                 |                               | ER              | ER  | B8          | -     | *          | *             | 0 | - | - | 4       | 3      |

|                                                                                                            | -                             | ER              | IM  | B9          |       |            |               |   |   |   | 4       | 3      |

| Flags Notation: * = Value is a function of the result of the operation.<br>- = Unaffected<br>X = Undefined |                               |                 |     |             | -     | Res<br>Set | et to<br>to 1 | 0 |   |   |         |        |

## Table 133. eZ8 CPU Instruction Summary (Continued)