Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4821vn020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# zilog

| Signal    |       |          |                                                                                                                                                                                                                                                                                                                                 |

|-----------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonio  | C     | I/O      | Description                                                                                                                                                                                                                                                                                                                     |

| XIN       |       | Ι        | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. This signal is usable with external RC networks and an external clock driver.                                                                                    |

| XOUT      |       | 0        | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the XIN pin to form the oscillator. When the system clock is referred to in this manual, it refers to the frequency of the signal at this pin. This pin must be left unconnected when not using a crystal. |

| RCOUT     |       | 0        | RC Oscillator Output. This signal is the output of the RC oscillator. It is multiplexed with a general-purpose I/O pin. This signal must be left unconnected when not using a crystal.                                                                                                                                          |

| On-Chip E | Debug | ger      |                                                                                                                                                                                                                                                                                                                                 |

| DBG       |       | I/O      | Debug. This pin is the control and data input and output to and from the On-<br>Chip Debugger. This pin is open-drain.                                                                                                                                                                                                          |

|           |       | Caution: | For operation of the On-Chip Debugger, all power pins ( $V_{DD}$ and $AV_{DD}$ ) must be supplied with power and all ground pins ( $V_{SS}$ and $AV_{SS}$ ) must be properly grounded.                                                                                                                                          |

|           |       |          | The DBG pin is open-drain and must have an external pull-up resistor to ensure proper operation.                                                                                                                                                                                                                                |

| Reset     |       |          |                                                                                                                                                                                                                                                                                                                                 |

| RESET     |       | Ι        | RESET. Generates a Reset when asserted (driven Low).                                                                                                                                                                                                                                                                            |

| Power Su  | pply  |          |                                                                                                                                                                                                                                                                                                                                 |

| VDD       |       | Ι        | Power Supply.                                                                                                                                                                                                                                                                                                                   |

| AVDD      |       | Ι        | Analog Power Supply.                                                                                                                                                                                                                                                                                                            |

| VSS       |       | Ι        | Ground.                                                                                                                                                                                                                                                                                                                         |

| AVSS      |       | Ι        | Analog Ground.                                                                                                                                                                                                                                                                                                                  |

## Table 3. Signal Descriptions (Continued)

## **Pin Characteristics**

Table 4 on page 17 provides detailed information on the characteristics for each pin available on the 64K Series products and the data is sorted alphabetically by the pin symbol mnemonic.

# Zilog 24

| Address (Hex)    | Register Description                 | Mnemonic      | Reset (Hex) | Page No |

|------------------|--------------------------------------|---------------|-------------|---------|

| Timer 3 (unava   | ailable in the 44-pin packages)      |               |             |         |

| F18              | Timer 3 High Byte                    | T3H           | 00          | 90      |

| F19              | Timer 3 Low Byte                     | T3L           | 01          | 90      |

| F1A              | Timer 3 Reload High Byte             | T3RH          | FF          | 91      |

| F1B              | Timer 3 Reload Low Byte              | T3RL          | FF          | 91      |

| F1C              | Timer 3 PWM High Byte                | T3PWMH        | 00          | 92      |

| F1D              | Timer 3 PWM Low Byte                 | T3PWML        | 00          | 92      |

| F1E              | Timer 3 Control 0                    | T3CTL0        | 00          | 93      |

| F1F              | Timer 3 Control 1                    | T3CTL1        | 00          | 94      |

| 20-3F            | Reserved                             | _             | XX          |         |

| UART 0           |                                      |               |             |         |

| F40              | UART0 Transmit Data                  | U0TXD         | XX          | 114     |

|                  | UART0 Receive Data                   | U0RXD         | XX          | 115     |

| F41              | UART0 Status 0                       | U0STAT0       | 0000011Xb   | 115     |

| F42              | UART0 Control 0                      | U0CTL0        | 00          | 117     |

| F43              | UART0 Control 1                      | U0CTL1        | 00          | 117     |

| F44              | UART0 Status 1                       | U0STAT1       | 00          | 115     |

| F45              | UART0 Address Compare Register       | <b>U0ADDR</b> | 00          | 120     |

| F46              | UART0 Baud Rate High Byte            | U0BRH         | FF          | 120     |

| F47              | UART0 Baud Rate Low Byte             | U0BRL         | FF          | 120     |

| UART 1           |                                      |               |             |         |

| F48              | UART1 Transmit Data                  | U1TXD         | XX          | 114     |

| -                | UART1 Receive Data                   | U1RXD         | XX          | 115     |

| F49              | UART1 Status 0                       | U1STAT0       | 0000011Xb   | 115     |

| F4A              | UART1 Control 0                      | U1CTL0        | 00          | 117     |

| F4B              | UART1 Control 1                      | U1CTL1        | 00          | 117     |

| F4C              | UART1 Status 1                       | U1STAT1       | 00          | 115     |

| F4D              | UART1 Address Compare Register       | U1ADDR        | 00          | 120     |

| F4E              | UART1 Baud Rate High Byte            | U1BRH         | FF          | 120     |

| F4F              | UART1 Baud Rate Low Byte             | U1BRL         | FF          | 120     |

| I <sup>2</sup> C | ,                                    |               |             |         |

| F50              | I <sup>2</sup> C Data                | I2CDATA       | 00          | 156     |

| F51              | I <sup>2</sup> C Status              | I2CSTAT       | 80          | 157     |

| F52              | I <sup>2</sup> C Control             | I2CCTL        | 00          | 158     |

| F53              | I <sup>2</sup> C Baud Rate High Byte | I2CBRH        | FF          | 160     |

| F54              | I <sup>2</sup> C Baud Rate Low Byte  | I2CBRL        | FF          | 160     |

| F55              | I <sup>2</sup> C Diagnostic State    | I2CDST        | <u> </u>    | 161     |

| F56              | I <sup>2</sup> C Diagnostic Control  | I2CDIAG       | 00          | 163     |

| F57-F5F          | Reserved                             |               | XX          |         |

|                  | ral Interface (SPI)                  |               |             |         |

| F60              | SPI Data                             | SPIDATA       | XX          | 137     |

| 1.00             | JET Dala                             | SFIDAIA       | ~~          | 107     |

Table 7. Z8 Encore! XP 64K Series Flash Microcontrollers Register File Address Map (Continued)

|          | $\sim$ | 1. | -        |

|----------|--------|----|----------|

|          | 11     | 1  |          |

| 27       |        | 6  | <u> </u> |

| <b>Z</b> |        |    |          |

| Address (Hex)    | Register Description                  | Mnemonic | Reset (Hex) | Page No             |

|------------------|---------------------------------------|----------|-------------|---------------------|

| FEF              | Port H Output Data                    | PHOUT    | 00          | 66                  |

| Watchdog Time    | er                                    |          |             |                     |

| FF0              | Watchdog Timer Control                | WDTCTL   | XXX00000b   | 100                 |

| FF1              | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | 101                 |

| FF2              | Watchdog Timer Reload High Byte       | WDTH     | FF          | 101                 |

| FF3              | Watchdog Timer Reload Low Byte        | WDTL     | FF          | 101                 |

| FF4-FF7          | Reserved                              | _        | XX          |                     |

| Flash Memory     | Controller                            |          |             |                     |

| FF8              | Flash Control                         | FCTL     | 00          | 190                 |

| FF8              | Flash Status                          | FSTAT    | 00          | 190                 |

| FF9              | Page Select                           | FPS      | 00          | 191                 |

| FF9 (if enabled) | Flash Sector Protect                  | FPROT    | 00          | 192                 |

| FFA              | Flash Programming Frequency High Byte | FFREQH   | 00          | 192                 |

| FFB              | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 192                 |

| FF4-FF8          | Reserved                              | —        | XX          |                     |

| Read-Only Men    | nory Controller                       |          |             |                     |

| FF9              | Page Select                           | RPS      | 00          |                     |

| FFA-FFB          | Reserved                              | _        | XX          |                     |

| eZ8 CPU          |                                       |          |             |                     |

| FFC              | Flags                                 | _        | XX          | Refer to $eZ8^{TM}$ |

| FFD              | Register Pointer                      | RP       | XX          | CPU Core            |

| FFE              | Stack Pointer High Byte               | SPH      | XX          | User Manual         |

| FFF              | Stack Pointer Low Byte                | SPL      | XX          | (UM0128)            |

| Note: XX=Undefin | ned                                   |          |             |                     |

Table 7. Z8 Encore! XP 64K Series Flash Microcontrollers Register File Address Map (Continued)

## zilog ,

#### Table 33. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 1          | 1          | Level 3  | High        |

**Note:** where *x* indicates the register bits from 0 through 7.

#### Table 34. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|--|

| FIELD | T3ENH | U1RENH | U1TENH | DMAENH | C3ENH | C2ENH | C1ENH | C0ENH |  |

| RESET |       | 0      |        |        |       |       |       |       |  |

| R/W   |       | R/W    |        |        |       |       |       |       |  |

| ADDR  |       |        |        | FC     | 7H    |       |       |       |  |

T3ENH—Timer 3 Interrupt Request Enable High Bit U1RENH—UART 1 Receive Interrupt Request Enable High Bit U1TENH—UART 1 Transmit Interrupt Request Enable High Bit DMAENH—DMA Interrupt Request Enable High Bit C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 35. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |  |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|--|--|

| FIELD | T3ENL | U1RENL | U1TENL | DMAENL | C3ENL | C2ENL | C1ENL | C0ENL |  |  |

| RESET |       | 0      |        |        |       |       |       |       |  |  |

| R/W   |       | R/W    |        |        |       |       |       |       |  |  |

| ADDR  |       |        |        | FC     | 8H    |       |       |       |  |  |

T3ENL—Timer 3 Interrupt Request Enable Low Bit U1RENL—UART 1 Receive Interrupt Request Enable Low Bit U1TENL—UART 1 Transmit Interrupt Request Enable Low Bit DMAENL—DMA Interrupt Request Enable Low Bit C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit

C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 36) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port input pin. The Interrupt Port Select register selects between Port A and Port D for the individual interrupts.

#### Table 36. Interrupt Edge Select Register (IRQES)

| BITS  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-------|------|------|------|------|------|------|------|------|--|

| FIELD | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |

| RESET |      | 0    |      |      |      |      |      |      |  |

| R/W   |      | R/W  |      |      |      |      |      |      |  |

| ADDR  |      |      |      | FC   | DH   |      |      |      |  |

IES*x*—Interrupt Edge Select *x*

The minimum pulse width should be greater than 1 system clock to guarantee capture of the edge triggered interrupt. Shorter pulses may be captured but not guaranteed. 0 = An interrupt request is generated on the falling edge of the PAx/PDx input.

1 = An interrupt request is generated on the rising edge of the PAx/PDx input.

where *x* indicates the specific GPIO Port pin number (0 through 7).

## Interrupt Port Select Register

The Port Select (IRQPS) register (Table 37) determines the port pin that generates the PAx/PDx interrupts. This register allows either Port A or Port D pins to be used as interrupts. The Interrupt Edge Select register controls the active interrupt edge.

| BITS  | 7     | 6     | 5     | 4     | 3     | 2     | 1     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| FIELD | PAD7S | PAD6S | PAD5S | PAD4S | PAD3S | PAD2S | PAD1S |

| RESET |       |       |       | (     | )     |       |       |

## Table 37. Interrupt Port Select Register (IRQPS)

0

PAD0S

Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

## zilog

- Select either the rising edge or falling edge of the Timer Input signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function does not have to be enabled

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. Generally, in COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control 1 register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

#### **PWM Mode**

In PWM mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO Port pin. The timer input is the system clock. The timer first counts up to the 16bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control 1 register is set to 1, the Timer Output signal begins as a High (1) and then transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control 1 register is set to 0, the Timer Output signal begins as a Low (0) and then transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

## Table 42. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7 | 6   | 5 | 4          | 3          | 2 | 1 | 0 |  |  |

|-------|---|-----|---|------------|------------|---|---|---|--|--|

| FIELD |   | TRL |   |            |            |   |   |   |  |  |

| RESET |   | 1   |   |            |            |   |   |   |  |  |

| R/W   |   | R/W |   |            |            |   |   |   |  |  |

| ADDR  |   |     | F | 03H, F0BH, | F13H, F1BI | Н |   |   |  |  |

TRH and TRL-Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two byte form the 16-bit Compare value.

## Timer 0-3 PWM High and Low Byte Registers

The Timer 0-3 PWM High and Low Byte (TxPWMH and TxPWML) registers (see Table 43 and Table 44 on page 92) are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the Capture and Capture/COM-PARE modes.

## Table 43. Timer 0-3 PWM High Byte Register (TxPWMH)

| BITS  | 7 | 6    | 5 | 4          | 3         | 2 | 1 | 0 |  |  |

|-------|---|------|---|------------|-----------|---|---|---|--|--|

| FIELD |   | PWMH |   |            |           |   |   |   |  |  |

| RESET |   | 0    |   |            |           |   |   |   |  |  |

| R/W   |   | R/W  |   |            |           |   |   |   |  |  |

| ADDR  |   |      | F | 04H, F0CH, | F14H, F1C | Н |   |   |  |  |

## Table 44. Timer 0-3 PWM Low Byte Register (TxPWML)

| BITS  | 7   | 6                      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|------------------------|---|---|---|---|---|---|

| FIELD |     | PWML                   |   |   |   |   |   |   |

| RESET | 0   |                        |   |   |   |   |   |   |

| R/W   | R/W |                        |   |   |   |   |   |   |

| ADDR  |     | F05H, F0DH, F15H, F1DH |   |   |   |   |   |   |

- 3. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and await more data.

## Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this would typically be done during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

## **MULTIPROCESSOR (9-bit) Mode**

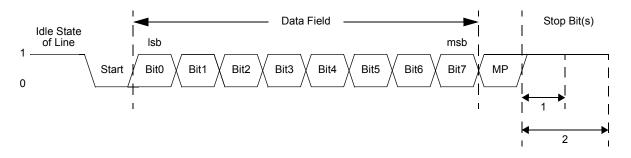

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTI-PROCESSOR mode (also referred to as 9-Bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 16. The character format is:

#### Figure 16. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the MUL-TIPROCESSOR control bit. The UART Control 1 and Status 1 registers provide MULTI-PROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor

5.5296 MHz System Clock

## Table 61. UART Baud Rates (Continued)

| 1.20 | 868  | 1.20 | 0.01 | 1.20 | 576  | 1.20 | 0.00 |

|------|------|------|------|------|------|------|------|

| 0.60 | 1736 | 0.60 | 0.01 | 0.60 | 1152 | 0.60 | 0.00 |

| 0.30 | 3472 | 0.30 | 0.01 | 0.30 | 2304 | 0.30 | 0.00 |

10.0 MHz System Clock

| <b>Desired Rate</b> | BRG Divisor | Actual Rate | Error  |

|---------------------|-------------|-------------|--------|

| (kHz)               | (Decimal)   | (kHz)       | (%)    |

| 1250.0              | N/A         | N/A         | N/A    |

| 625.0               | 1           | 625.0       | 0.00   |

| 250.0               | 3           | 208.33      | -16.67 |

| 115.2               | 5           | 125.0       | 8.51   |

| 57.6                | 11          | 56.8        | -1.36  |

| 38.4                | 16          | 39.1        | 1.73   |

| 19.2                | 33          | 18.9        | 0.16   |

| 9.60                | 65          | 9.62        | 0.16   |

| 4.80                | 130         | 4.81        | 0.16   |

| 2.40                | 260         | 2.40        | -0.03  |

| 1.20                | 521         | 1.20        | -0.03  |

| 0.60                | 1042        | 0.60        | -0.03  |

| 0.30                | 2083        | 0.30        | 0.2    |

| Desired | BRG       |             |       |

|---------|-----------|-------------|-------|

| Rate    | Divisor   | Actual Rate | Error |

| (kHz)   | (Decimal) | (kHz)       | (%)   |

| 1250.0  | N/A       | N/A         | N/A   |

| 625.0   | N/A       | N/A         | N/A   |

| 250.0   | 1         | 345.6       | 38.24 |

| 115.2   | 3         | 115.2       | 0.00  |

| 57.6    | 6         | 57.6        | 0.00  |

| 38.4    | 9         | 38.4        | 0.00  |

| 19.2    | 18        | 19.2        | 0.00  |

| 9.60    | 36        | 9.60        | 0.00  |

| 4.80    | 72        | 4.80        | 0.00  |

| 2.40    | 144       | 2.40        | 0.00  |

| 1.20    | 288       | 1.20        | 0.00  |

| 0.60    | 576       | 0.60        | 0.00  |

| 0.30    | 1152      | 0.30        | 0.00  |

|         |           |             |       |

## 3.579545 MHz System Clock

| Desired Rate | BRG Divisor | Actual Rate | Error  | Desired<br>Rate |

|--------------|-------------|-------------|--------|-----------------|

| (kHz)        | (Decimal)   | (kHz)       | (%)    | (kHz)           |

| 1250.0       | N/A         | N/A         | N/A    | 1250.0          |

| 625.0        | N/A         | N/A         | N/A    | 625.0           |

| 250.0        | 1           | 223.72      | -10.51 | 250.0           |

| 115.2        | 2           | 111.9       | -2.90  | 115.2           |

| 57.6         | 4           | 55.9        | -2.90  | 57.6            |

| 38.4         | 6           | 37.3        | -2.90  | 38.4            |

| 19.2         | 12          | 18.6        | -2.90  | 19.2            |

### 1.8432 MHz System Clock

| Desired<br>Rate | BRG<br>Divisor | Actual Rate | Error |

|-----------------|----------------|-------------|-------|

| (kHz)           | (Decimal)      | (kHz)       | (%)   |

| 1250.0          | N/A            | N/A         | N/A   |

| 625.0           | N/A            | N/A         | N/A   |

| 250.0           | N/A            | N/A         | N/A   |

| 115.2           | 1              | 115.2       | 0.00  |

| 57.6            | 2              | 57.6        | 0.00  |

| 38.4            | 3              | 38.4        | 0.00  |

| 19.2            | 6              | 19.2        | 0.00  |

## zilog

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

#### **SPI Signals**

The four basic SPI signals are:

- Master-In/Slave-Out

- Master-Out/Slave-In

- Serial Clock

- Slave Select

Each signal is described in both Master and Slave modes.

#### Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### **Serial Clock**

The Serial Clock (SCK) synchronizes data movement both in and out of the device through its MOSI and MISO pins. In MASTER mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted. When configured as a slave, the SPI block requires a minimum SCK period of greater than or equal to 8 times the system (XIN) clock period.

The Master and Slave are each capable of exchanging a character of data during a sequence of NUMBITS clock cycles (see NUMBITS field in the SPI Mode Register on page 140). In both Master and Slave SPI devices, data is shifted on one edge of the SCK and is sampled on the opposite edge where data is stable. Edge polarity is determined by the SPI phase and polarity control.

#### **Slave Select**

The active Low Slave Select ( $\overline{SS}$ ) input signal selects a Slave SPI device.  $\overline{SS}$  must be Low prior to all data communication to and from the Slave device.  $\overline{SS}$  must stay Low for the full duration of each character transferred. The  $\overline{SS}$  signal may stay Low during the transfer of multiple characters or may deassert between each character.

When the SPI is configured as the only Master in an SPI system, the  $\overline{SS}$  pin can be set as either an input or an output. For communication between the Z8F642x family Z8R642x family device's SPI Master and external Slave devices, the  $\overline{SS}$  signal, as an output, can assert the  $\overline{SS}$  input pin on one of the Slave devices. Other GPIO output pins can also be employed to select external SPI Slave devices.

When the SPI is configured as one Master in a multi-master SPI system, the  $\overline{SS}$  pin must be set as an input. The  $\overline{SS}$  input signal on the Master must be High. If the  $\overline{SS}$  signal goes Low (indicating another Master is driving the SPI bus), a Collision error Flag is set in the SPI Status register.

## SPI Clock Phase and Polarity Control

The SPI supports four combinations of serial clock phase and polarity using two bits in the SPI Control register. The clock polarity bit, CLKPOL, selects an active high or active Low clock and has no effect on the transfer format. Table 62 lists the SPI Clock Phase and Polarity Operation parameters. The clock phase bit, PHASE, selects one of two fundamentally different transfer formats. For proper data transmission, the clock phase and polarity must be identical for the SPI Master and the SPI Slave. The Master always places data on the MOSI line a half-cycle before the receive clock edge (SCK signal), in order for the Slave to latch the data.

| PHASE | CLKPOL | SCK Transmit<br>Edge | SCK Receive<br>Edge | SCK Idle<br>State |

|-------|--------|----------------------|---------------------|-------------------|

| 0     | 0      | Falling              | Rising              | Low               |

| 0     | 1      | Rising               | Falling             | High              |

| 1     | 0      | Rising               | Falling             | Low               |

| 1     | 1      | Falling              | Rising              | High              |

| Table 62. SPI Clock Phase | (PHASE) and Clock Pola | rity (CLKPOL) Operation |

|---------------------------|------------------------|-------------------------|

|---------------------------|------------------------|-------------------------|

Table 64. SPI Control Register (SPICTL)

| BITS  | 7    | 6    | 5    | 4     | 3      | 2   | 1    | 0     |  |

|-------|------|------|------|-------|--------|-----|------|-------|--|

| FIELD | IRQE | STR  | BIRQ | PHASE | CLKPOL | WOR | MMEN | SPIEN |  |

| RESET |      | 0    |      |       |        |     |      |       |  |

| R/W   |      | R/W  |      |       |        |     |      |       |  |

| ADDR  |      | F61H |      |       |        |     |      |       |  |

IRQE—Interrupt Request Enable

0 = SPI interrupts are disabled. No interrupt requests are sent to the Interrupt Controller.

1 = SPI interrupts are enabled. Interrupt requests are sent to the Interrupt Controller.

STR—Start an SPI Interrupt Request

0 = No effect.

1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART. Writing a 1 to the IRQ bit in the SPI Status register clears this bit to 0.

BIRQ-BRG Timer Interrupt Request

If the SPI is enabled, this bit has no effect. If the SPI is disabled:

0 = The Baud Rate Generator timer function is disabled.

1 = The Baud Rate Generator timer function and time-out interrupt are enabled.

PHASE—Phase Select

Sets the phase relationship of the data to the clock. For more information on operation of the PHASE bit, see SPI Clock Phase and Polarity Control on page 132.

CLKPOL—Clock Polarity

0 = SCK idles Low (0).

1 = SCK idle High (1).

WOR-Wire-OR (OPEN-DRAIN) Mode Enabled

0 = SPI signal pins not configured for open-drain.

$1 = \text{All four SPI signal pins (SCK, \overline{SS}, MISO, MOSI)}$  configured for open-drain function. This setting is typically used for multi-master and/or multi-slave configurations.

MMEN-SPI Master Mode Enable

0 = SPI configured in Slave mode.

1 = SPI configured in Master mode.

SPIEN—SPI Enable

0 = SPI disabled.

1 = SPI enabled.

## Write Transaction with a 7-Bit Address

Figure 29 displays the data transfer format for a 7-bit addressed slave. Shaded regions indicate data transferred from the I<sup>2</sup>C Controller to slaves and unshaded regions indicate data transferred from the slaves to the I<sup>2</sup>C Controller.

| S | Slave Address | W = 0 | Α | Data | Α | Data | Α | Data | A/A | P/S |

|---|---------------|-------|---|------|---|------|---|------|-----|-----|

|---|---------------|-------|---|------|---|------|---|------|-----|-----|

## Figure 29. 7-Bit Addressed Slave Data Transfer Format

Follow the steps below for a transmit operation to a 7-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control register to enable Transmit interrupts.

- 3. The  $I^2C$  interrupt asserts, because the  $I^2C$  Data register is empty

- 4. Software responds to the TDRE bit by writing a 7-bit slave address plus write bit (=0) to the  $I^2C$  Data register.

- 5. Software asserts the START bit of the  $I^2C$  Control register.

- 6. The  $I^2C$  Controller sends the START condition to the  $I^2C$  slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register.

- 8. After one bit of address has been shifted out by the SDA signal, the Transmit interrupt is asserted (TDRE = 1).

- 9. Software responds by writing the transmit data into the  $I^2C$  Data register.

- 10. The  $I^2C$  Controller shifts the rest of the address and write bit out by the SDA signal.

- If the I<sup>2</sup>C slave sends an acknowledge (by pulling the SDA signal low) during the next high period of SCL the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status register. Continue with step 12.

If the slave does not acknowledge, the Not Acknowledge interrupt occurs (NCKI bit is set in the Status register, ACK bit is cleared). Software responds to the Not Acknowledge interrupt by setting the STOP and FLUSH bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore the following steps).

12. The I<sup>2</sup>C Controller loads the contents of the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register.

| TXRXSTATE | State Description                                                                       |

|-----------|-----------------------------------------------------------------------------------------|

| 1_1101    | 10-bit addressing: Bit 3 of 2nd address byte<br>7-bit addressing: Bit 3 of address byte |

| 1_1110    | 10-bit addressing: Bit 2 of 2nd address byte<br>7-bit addressing: Bit 2 of address byte |

| 1_1111    | 10-bit addressing: Bit 1 of 2nd address byte<br>7-bit addressing: Bit 1 of address byte |

## I<sup>2</sup>C Diagnostic Control Register

The I<sup>2</sup>C Diagnostic register (Table 76) provides control over diagnostic modes. This register is a read/write register used for I<sup>2</sup>C diagnostics.

## Table 76. I<sup>2</sup>C Diagnostic Control Register (I2CDIAG)

| BITS  | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------|----------|---|---|---|---|---|---|-----|

| FIELD | Reserved |   |   |   |   |   |   |     |

| RESET | 0        |   |   |   |   |   |   |     |

| R/W   | R R/W    |   |   |   |   |   |   | R/W |

| ADDR  | F56H     |   |   |   |   |   |   |     |

DIAG = Diagnostic Control Bit - Selects read back value of the Baud Rate Reload registers.

- 0 = NORMAL mode. Reading the Baud Rate High and Low Byte registers returns the baud rate reload value.

- 1 = DIAGNOSTIC mode. Reading the Baud Rate High and Low Byte registers returns the baud rate counter value.

169

DMAx\_IO[7:0]}. When the DMA is configured for two-byte word transfers, the DMAx I/O Address register must contain an even numbered address.

Table 78. DMAx I/O Address Register (DMAxIO)

| BITS  | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| FIELD | DMA_IO     |   |   |   |   |   |   |   |

| RESET | x          |   |   |   |   |   |   |   |

| R/W   | R/W        |   |   |   |   |   |   |   |

| ADDR  | FB1H, FB9H |   |   |   |   |   |   |   |

DMA\_IO—DMA on-chip peripheral control register address This byte sets the low byte of the on-chip peripheral control register address on Register File Page FH (addresses F00H to FFFH).

## DMAx Address High Nibble Register

The DMAx Address High register (Table 79) specifies the upper four bits of address for the Start/Current and End Addresses of DMAx.

| BITS  | 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------------------|---|---|---|---|---|---|---|--|

| FIELD | DMA_END_H DMA_START_H |   |   |   |   |   |   |   |  |

| RESET | X                     |   |   |   |   |   |   |   |  |

| R/W   | R/W                   |   |   |   |   |   |   |   |  |

| ADDR  | FB2H, FBAH            |   |   |   |   |   |   |   |  |

DMA\_END\_H—DMAx End Address High Nibble

These bits, used with the DMAx End Address Low register, form a 12-bit End Address. The full 12-bit address is given by {DMA\_END\_H[3:0], DMA\_END[7:0]}.

DMA\_START\_H—DMAx Start/Current Address High Nibble These bits, used with the DMAx Start/Current Address Low register, form a 12-bit Start/Current Address. The full 12-bit address is given by {DMA\_START\_H[3:0], DMA\_START[7:0]}.

## **Analog-to-Digital Converter**

## **Overview**

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- 12 analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Internal voltage reference generator

- Direct Memory Access (DMA) controller can automatically initiate data conversion and transfer of the data from 1 to 12 of the analog inputs

## Architecture

Figure 34 displays the three major functional blocks (converter, analog multiplexer, and voltage reference generator) of the ADC. The ADC converts an analog input signal to its digital representation. The 12-input analog multiplexer selects one of the 12 analog input sources. The ADC requires an input reference voltage for the conversion. The voltage reference for the conversion may be input through the external VREF pin or generated internally by the voltage reference generator.

## Operation

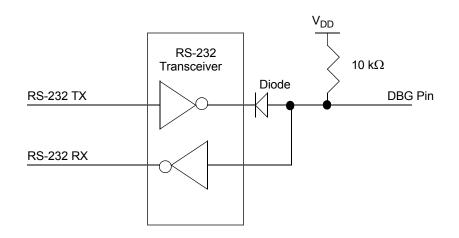

## **OCD** Interface

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bi-directional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the 64K Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are depicted in Figure 37 and Figure 38 on page 201.

**Caution:** For operation of the On-Chip Debugger, all power pins  $(V_{DD} \text{ and } AV_{DD})$  must be supplied with power, and all ground pins  $(V_{SS} \text{ and } AV_{SS})$  must be properly grounded.

The DBG pin is open-drain and must always be connected to  $V_{DD}$  through an external pull-up resistor to ensure proper operation.

Figure 37. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

### OCD Serial Errors

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low).

- Framing Error (received Stop bit is Low).

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD).

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a Serial Break 4096 system clock cycles long back to the host, and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the 64K Series devices or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

#### **Breakpoints**

Execution Breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If Breakpoints are enabled, the OCD idles the eZ8 CPU and enters DEBUG mode. If Breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP.

If breakpoints are enabled, the OCD can be configured to automatically enter DEBUG mode, or to loop on the break instruction. If the OCD is configured to loop on the BRK instruction, then the CPU is still enabled to service DMA and interrupt requests.

The loop on BRK instruction can be used to service interrupts in the background. For interrupts to be serviced in the background, there cannot be any breakpoints in the interrupt service routine. Otherwise, the CPU stops on the breakpoint in the interrupt routine. For interrupts to be serviced in the background, interrupts must also be enabled. Debugging software should not automatically enable interrupts when using this feature, since interrupts are typically disabled during critical sections of code where interrupts should not occur (such as adjusting the stack pointer or modifying shared data).

Software can poll the IDLE bit of the OCDSTAT register to determine if the OCD is looping on a BRK instruction. When software wants to stop the CPU on the BRK instruction it is looping on, software should not set the DBGMODE bit of the OCDCTL register. The CPU may have vectored to and be in the middle of an interrupt service routine when this bit gets set. Instead, software must clear the BRKLP bit. This action allows the CPU to

| y | 219 |

|---|-----|

|---|-----|

|                  |                                                   | T <sub>A</sub> = –40 °C to 125 °C |         |         |       |                                                             |

|------------------|---------------------------------------------------|-----------------------------------|---------|---------|-------|-------------------------------------------------------------|

| Symbol           | Parameter                                         | Minimum                           | Typical | Maximum | Units | Conditions                                                  |

| I <sub>DDS</sub> | Stop Mode Supply<br>Current<br>(See Figure 47 and | _                                 | 520     | 700     | μΑ    | V <sub>DD</sub> = 3.6 V, VBO and WDT<br>Enabled             |

|                  |                                                   |                                   |         | 650     |       | V <sub>DD</sub> = 3.3 V                                     |

|                  | Figure 48) GPIO pins configured as outputs        | _                                 | 10      | 25      | μΑ    | $V_{DD}$ = 3.6 V, $T_A$ = 0 to 70 °C VBO                    |

|                  |                                                   |                                   |         |         |       | Disabled                                                    |

|                  |                                                   |                                   |         | 20      |       | WDT                                                         |

|                  |                                                   |                                   |         |         |       | Enabled<br>V <sub>DD</sub> = 3.3 V                          |

|                  |                                                   | -                                 |         | 80      | μΑ    | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = −40 to<br>+105 °C |

|                  |                                                   |                                   |         | 70      |       | VBO                                                         |

|                  |                                                   |                                   |         | 70      |       | Disabled<br>WDT                                             |

|                  |                                                   |                                   |         |         |       | Enabled<br>V <sub>DD</sub> = 3.3 V                          |

|                  |                                                   | _                                 |         | 250     | μΑ    | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = -40 to<br>+125 °C |

|                  |                                                   |                                   |         |         |       | VBO                                                         |

|                  |                                                   |                                   |         | 150     |       | Disabled                                                    |

|                  |                                                   |                                   |         |         |       | WDT                                                         |

|                  |                                                   |                                   |         |         |       | $V_{DD} = 3.3 V$                                            |

## Table 106. DC Characteristics (Continued)

<sup>1</sup>This condition excludes all pins that have on-chip pull-ups, when driven Low.

<sup>2</sup>These values are provided for design guidance only and are not tested in production.