Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 46                                                            |

| Program Memory Size        | 48KB (48K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 64-LQFP                                                       |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4822ar020ec00tr |

# **Table of Contents**

| Manual Objectives xii                     |

|-------------------------------------------|

| About This Manualxii Intended Audiencexii |

| Manual Conventions                        |

| Introduction 1                            |

| Features                                  |

| Part Selection Guide                      |

| Block Diagram 3                           |

| CPU and Peripheral Overview               |

| eZ8 <sup>™</sup> CPU Features             |

| General-Purpose Input/Output              |

| Flash Controller                          |

| 10-Bit Analog-to-Digital Converter        |

| UARTs                                     |

| I <sup>2</sup> C                          |

| Timers                                    |

| Interrupt Controller                      |

| Reset Controller                          |

| On-Chip Debugger                          |

| DMA Controller                            |

| Signal and Pin Descriptions               |

| Overview                                  |

| Available Packages                        |

| Pin Configurations                        |

| Signal Descriptions                       |

| Pin Characteristics                       |

| Address Space                             |

| Overview                                  |

| Register File                             |

| Program Memory                            |

| Data Memory                               |

PS019919-1207 Table of Contents

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

| Flash Status Register  Page Select Register  Flash Sector Protect Register  Flash Frequency High and Low Byte Registers                                                                                    | 191<br>192                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Option Bits                                                                                                                                                                                                | 195                                                                |

| Overview Operation Option Bit Configuration By Reset Option Bit Address Space Flash Memory Address 0000H Flash Memory Address 0001H                                                                        | 195<br>195<br>195<br>196                                           |

| On-Chip Debugger                                                                                                                                                                                           | 199                                                                |

| Overview Architecture Operation OCD Interface DEBUG Mode OCD Data Format OCD Auto-Baud Detector/Generator OCD Serial Errors Breakpoints On-Chip Debugger Commands OCD Control Register OCD Status Register | 199<br>200<br>200<br>201<br>202<br>203<br>203<br>204<br>209<br>209 |

| On-Chip Oscillator                                                                                                                                                                                         | 211                                                                |

| Overview                                                                                                                                                                                                   | 211<br>211                                                         |

| Electrical Characteristics                                                                                                                                                                                 | 215                                                                |

| Absolute Maximum Ratings                                                                                                                                                                                   | 217<br>226                                                         |

| AC Characteristics                                                                                                                                                                                         |                                                                    |

PS019919-1207 Table of Contents

# **Signal and Pin Descriptions**

# Overview

The Z8 Encore! XP 64K Series Flash Microcontrollers product are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information on physical package specifications, see Packaging on page 265.

### **Available Packages**

Table 2 identifies the package styles that are available for each device within the Z8 Encore! XP 64K Series Flash Microcontrollers product line.

Table 2. Z8 Encore! XP 64K Series Flash Microcontrollers Package Options

| Part Number | 40-Pin<br>PDIP | 44-pin<br>LQFP | 44-pin<br>PLCC | 64-pin<br>LQFP | 68-pin<br>PLCC | 80-pin<br>QFP |

|-------------|----------------|----------------|----------------|----------------|----------------|---------------|

| Z8F1621     | Х              | Х              | Х              |                |                |               |

| Z8F1622     |                |                |                | Х              | Х              |               |

| Z8F2421     | Х              | Х              | X              |                |                |               |

| Z8F2422     |                |                |                | Х              | Χ              |               |

| Z8F3221     | X              | Х              | Х              |                |                |               |

| Z8F3222     |                |                |                | Х              | Х              |               |

| Z8F4821     | Χ              | Х              | Х              |                |                |               |

| Z8F4822     |                |                |                | Х              | Х              |               |

| Z8F4823     |                |                |                |                |                | X             |

| Z8F6421     | X              | Х              | X              |                |                |               |

| Z8F6422     |                |                |                | Х              | Х              |               |

| Z8F6423     |                |                |                |                |                | X             |

|             |                |                |                |                |                |               |

**Table 3. Signal Descriptions (Continued)**

| Signal<br>Mnemonic         | I/O | Description                                                                                                                                                                                                                                                                                            |

|----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK                        | I/O | SPI Serial Clock. The SPI master supplies this pin. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI master, this pin is an output. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI slave, this pin is an input. It is multiplexed with a general-purpose I/O pin.  |

| MOSI                       | I/O | Master-Out/Slave-In. This signal is the data output from the SPI master device and the data input to the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                                           |

| MISO                       | I/O | Master-In/Slave-Out. This pin is the data input to the SPI master device and the data output from the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                                              |

| UART Controll              | ers |                                                                                                                                                                                                                                                                                                        |

| TXD0 / TXD1                | О   | Transmit Data. These signals are the transmit outputs from the UARTs. The TXD signals are multiplexed with general-purpose I/O pins.                                                                                                                                                                   |

| RXD0 / RXD1                | I   | Receive Data. These signals are the receiver inputs for the UARTs and IrDAs. The RXD signals are multiplexed with general-purpose I/O pins.                                                                                                                                                            |

| CTS0 / CTS1                | I   | Clear To Send. These signals are control inputs for the UARTs. The CTS signals are multiplexed with general-purpose I/O pins.                                                                                                                                                                          |

| DE0 / DE1                  | 0   | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the Transmit Empty (TXE) bit in the UART Status 0 register. The DE signal may be used to ensure an external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                     |     |                                                                                                                                                                                                                                                                                                        |

| T0OUT/T1OUT<br>T2OUT/T3OUT |     | Timer Output 0-3. These signals are output pins from the timers. The Timer Output signals are multiplexed with general-purpose I/O pins. T3OUT is not available in 44-pin package devices.                                                                                                             |

| T0IN/T1IN/<br>T2IN/T3IN    | I   | Timer Input 0-3. These signals are used as the capture, gating and counter inputs. The Timer Input signals are multiplexed with general-purpose I/O pins. T3IN is not available in 44-pin package devices.                                                                                             |

| Analog                     |     |                                                                                                                                                                                                                                                                                                        |

| ANA[11:0]                  | Ι   | Analog Input. These signals are inputs to the ADC. The ADC analog inputs are multiplexed with general-purpose I/O pins.                                                                                                                                                                                |

| VREF                       | I   | Analog-to-Digital converter reference voltage input. The VREF pin must be left unconnected (or capacitively coupled to analog ground) if the internal voltage reference is selected as the ADC reference voltage.                                                                                      |

| Oscillators                |     |                                                                                                                                                                                                                                                                                                        |

Table 5. Z8 Encore! XP 64K Series Flash Microcontrollers Program Memory Maps (Continued)

| Program Memory Address (Hex)                                  | Function                 |  |  |  |  |  |  |

|---------------------------------------------------------------|--------------------------|--|--|--|--|--|--|

| 0000-0001                                                     | Option Bits              |  |  |  |  |  |  |

| 0002-0003                                                     | Reset Vector             |  |  |  |  |  |  |

| 0004-0005                                                     | WDT Interrupt Vector     |  |  |  |  |  |  |

| 0006-0007                                                     | Illegal Instruction Trap |  |  |  |  |  |  |

| 0008-0037                                                     | Interrupt Vectors*       |  |  |  |  |  |  |

| 0038-BFFF                                                     | Program Memory           |  |  |  |  |  |  |

| Z8F642x Products                                              |                          |  |  |  |  |  |  |

| 0000-0001                                                     | Option Bits              |  |  |  |  |  |  |

| 0002-0003                                                     | Reset Vector             |  |  |  |  |  |  |

| 0004-0005                                                     | WDT Interrupt Vector     |  |  |  |  |  |  |

| 0006-0007                                                     | Illegal Instruction Trap |  |  |  |  |  |  |

| 0008-0037                                                     | Interrupt Vectors*       |  |  |  |  |  |  |

| 0038-FFFF                                                     | Program Memory           |  |  |  |  |  |  |

| *See Table 23 on page 68 for a list of the interrupt vectors. |                          |  |  |  |  |  |  |

### **Data Memory**

The Z8 Encore! XP 64K Series Flash Microcontrollers does not use the eZ8 CPU's 64 KB Data Memory address space.

#### **Information Area**

Table 6 on page 22 describes the Z8 Encore! XP 64K Series Flash Microcontrollers Information Area. This 512 byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into the Program Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, execution of LDC and LDCI instruction from these Program Memory addresses return the Information Area data rather than the Program Memory data. Reads of these addresses through the On-Chip Debugger also returns the Information Area data. Execution of code from these addresses continues to correctly use the Program Memory. Access to the Information Area is read-only.

PS019919-1207 Address Space

0 = Current byte is not start of frame 1 = Current byte is start of new

frame Reserved

DMA1 Peripheral Register Address Low byte of on-chip peripheral control registers on Register File page FH

PS019919-1207

D7|D6|D5|D4|D3|D2|D1|D0|

#### **HALT Mode**

Execution of the eZ8 CPU's HALT instruction places the device into HALT mode. In HALT mode, the operating characteristics are:

- Primary crystal oscillator is enabled and continues to operate.

- System clock is enabled and continues to operate.

- eZ8 CPU is stopped.

- Program Counter stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate.

- The Watchdog Timer continues to operate, if enabled.

- All other on-chip peripherals continue to operate.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout Reset

- External RESET pin assertion

To minimize current in HALT mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

PS019919-1207 Low-Power Modes

Table 11. Port Availability by Device and Package Type (Continued)

| Device  | Packages       | Port A | Port B | Port C | Port D        | Port E | Port F | Port G | Port H |

|---------|----------------|--------|--------|--------|---------------|--------|--------|--------|--------|

| Z8X4823 | 80-pin         | [7:0]  | [7:0]  | [7:0]  | [7:0]         | [7:0]  | [7:0]  | [7:0]  | [3:0]  |

| Z8X6421 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | [6:3,<br>1:0] | -      | -      | -      | -      |

| Z8X6421 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]         | -      | -      | -      | -      |

| Z8X6422 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]         | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8X6423 | 80-pin         | [7:0]  | [7:0]  | [7:0]  | [7:0]         | [7:0]  | [7:0]  | [7:0]  | [3:0]  |

#### **Architecture**

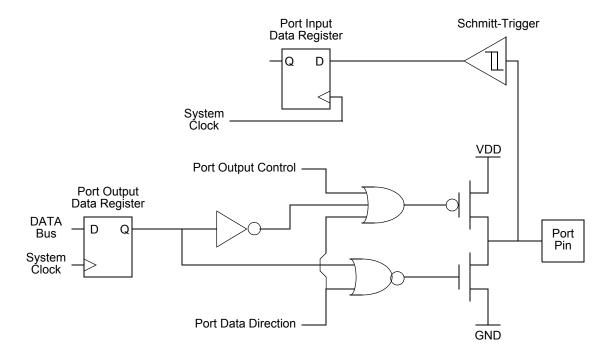

Figure 10 displays a simplified block diagram of a GPIO port pin. In Figure 10, the ability to accommodate alternate functions and variable port current drive strength are not illustrated.

Figure 10. GPIO Port Pin Block Diagram

PS019919-1207 General-Purpose I/O

**Table 23. Interrupt Vectors in Order of Priority**

| Priority | Program Memory<br>Vector Address | Interrupt Source                                 |

|----------|----------------------------------|--------------------------------------------------|

| Highest  | 0002H                            | Reset (not an interrupt)                         |

|          | 0004H                            | Watchdog Timer (see Watchdog Timer on page 97)   |

|          | 0006H                            | Illegal Instruction Trap (not an interrupt)      |

|          | H8000                            | Timer 2                                          |

|          | 000AH                            | Timer 1                                          |

|          | 000CH                            | Timer 0                                          |

|          | 000EH                            | UART 0 receiver                                  |

|          | 0010H                            | UART 0 transmitter                               |

|          | 0012H                            | I <sup>2</sup> C                                 |

|          | 0014H                            | SPI                                              |

|          | 0016H                            | ADC                                              |

|          | 0018H                            | Port A7 or Port D7, rising or falling input edge |

|          | 001AH                            | Port A6 or Port D6, rising or falling input edge |

|          | 001CH                            | Port A5 or Port D5, rising or falling input edge |

|          | 001EH                            | Port A4 or Port D4, rising or falling input edge |

|          | 0020H                            | Port A3 or Port D3, rising or falling input edge |

|          | 0022H                            | Port A2 or Port D2, rising or falling input edge |

|          | 0024H                            | Port A1 or Port D1, rising or falling input edge |

|          | 0026H                            | Port A0 or Port D0, rising or falling input edge |

|          | 0028H                            | Timer 3 (not available in 44-pin packages)       |

|          | 002AH                            | UART 1 receiver                                  |

|          | 002CH                            | UART 1 transmitter                               |

|          | 002EH                            | DMA                                              |

|          | 0030H                            | Port C3, both input edges                        |

|          | 0032H                            | Port C2, both input edges                        |

|          | 0034H                            | Port C1, both input edges                        |

| Lowest   | 0036H                            | Port C0, both input edges                        |

PS019919-1207 Interrupt Controller

zilog

ጸበ

PS019919-1207 Interrupt Controller

# **Timers**

#### Overview

The 64K Series products contain up to four 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse width modulated signals. The timers' features include:

- 16-bit reload counter

- Programmable prescaler with prescale values from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin

- Timer interrupt

In addition to the timers described in this chapter, the Baud Rate Generators for any unused UART, SPI, or I<sup>2</sup>C peripherals may also be used to provide basic timing functionality. For information on using the Baud Rate Generators as timers, see the respective serial communication peripheral. Timer 3 is unavailable in the 44-pin package devices.

#### **Architecture**

Figure 12 displays the architecture of the timers.

PS019919-1207 Timers

zilog

124

Table 61. UART Baud Rates (Continued)

| 12 9.60 0.00  |

|---------------|

| 12 9.60 0.00  |

| 24 4.80 0.00  |

| 48 2.40 0.00  |

| 96 1.20 0.00  |

| 192 0.60 0.00 |

| 384 0.30 0.00 |

| )             |

PS019919-1207 UART

#### **Transfer Format PHASE Equals Zero**

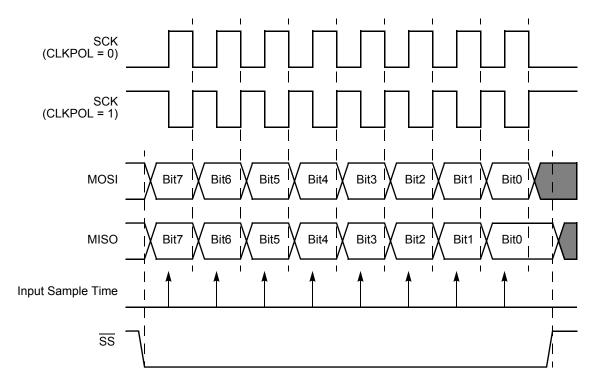

Figure 25 displays the timing diagram for an SPI transfer in which PHASE is cleared to 0. The two SCK waveforms show polarity with CLKPOL reset to 0 and with CLKPOL set to one. The diagram may be interpreted as either a Master or Slave timing diagram because the SCK Master-In/Slave-Out (MISO) and Master-Out/Slave-In (MOSI) pins are directly connected between the Master and the Slave.

Figure 25. SPI Timing When PHASE is 0

#### Transfer Format PHASE Equals One

Figure 26 on page 134 displays the timing diagram for an SPI transfer in which PHASE is one. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

- $0 = \overline{SS}$  input pin is asserted (Low).

- $1 = \overline{SS}$  input is not asserted (High).

If SPI enabled as a Master, this bit is not applicable.

## **SPI Mode Register**

The SPI Mode register (Table 66) configures the character bit width and the direction and value of the  $\overline{SS}$  pin.

#### Table 66. SPI Mode Register (SPIMODE)

| BITS  | 7    | 6     | 5    | 4                 | 3 | 1 | 0 |  |  |

|-------|------|-------|------|-------------------|---|---|---|--|--|

| FIELD | Rese | erved | DIAG | NUMBITS[2:0] SSIO |   |   |   |  |  |

| RESET |      | 0     |      |                   |   |   |   |  |  |

| R/W   | F    | ₹     | R/W  |                   |   |   |   |  |  |

| ADDR  |      | F63H  |      |                   |   |   |   |  |  |

Reserved—Must be 0.

DIAG—Diagnostic Mode Control bit

This bit is for SPI diagnostics. Setting this bit allows the Baud Rate Generator value to be read using the SPIBRH and SPIBRL register locations.

- 0 = Reading SPIBRH, SPIBRL returns the value in the SPIBRH and SPIBRL registers

- 1 = Reading SPIBRH returns bits [15:8] of the SPI Baud Rate Generator; and reading SPIBRL returns bits [7:0] of the SPI Baud Rate Counter. The Baud Rate Counter High and Low byte values are not buffered.

**Caution:** *Exercise caution if reading the values while the BRG is counting.*

NUMBITS[2:0]—Number of Data Bits Per Character to Transfer

This field contains the number of bits to shift for each character transfer. For information on valid bit positions when the character length is less than 8-bits, see SPI Data Register description.

000 = 8 bits

001 = 1 bit

010 = 2 bits

011 = 3 bits

100 = 4 bits

101 = 5 bits

110 = 6 bits

111 = 7 bits

148

reading the I<sup>2</sup>C Data register. Once the I<sup>2</sup>C data register has been read, the I<sup>2</sup>C reads the next data byte.

#### Address Only Transaction with a 7-bit Address

In the situation where software determines if a slave with a 7-bit address is responding without sending or receiving data, a transaction can be done which only consists of an address phase. Figure 28 displays this 'address only' transaction to determine if a slave with a 7-bit address will acknowledge. As an example, this transaction can be used after a 'write' has been done to a EEPROM to determine when the EEPROM completes its internal write operation and is once again responding to I<sup>2</sup>C transactions. If the slave does not Acknowledge, the transaction can be repeated until the slave does Acknowledge.

Figure 28. 7-Bit Address Only Transaction Format

Follow the steps below for an address only transaction to a 7-bit addressed slave:

- 1. Software asserts the IEN bit in the I<sup>2</sup>C Control register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control register to enable Transmit interrupts.

- 3. The  $I^2C$  interrupt asserts, because the  $I^2C$  Data register is empty (TDRE = 1)

- 4. Software responds to the TDRE bit by writing a 7-bit slave address plus write bit (=0) to the I<sup>2</sup>C Data register. As an alternative this could be a read operation instead of a write operation.

- 5. Software sets the START and STOP bits of the I<sup>2</sup>C Control register and clears the TXI bit.

- 6. The I<sup>2</sup>C Controller sends the START condition to the I<sup>2</sup>C slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register.

- 8. Software polls the STOP bit of the I<sup>2</sup>C Control register. Hardware deasserts the STOP bit when the address only transaction is completed.

- 9. Software checks the ACK bit of the I<sup>2</sup>C Status register. If the slave acknowledged, the ACK bit is = 1. If the slave does not acknowledge, the ACK bit is = 0. The NCKI interrupt does not occur in the not acknowledge case because the STOP bit was set.

PS019919-1207 I2C Controller

160

### I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers (Tables 73 and 73) combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator.

When the I<sup>2</sup>C is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the  $I^2C$  by clearing the IEN bit in the  $I^2C$  Control register to 0.

- 2. Load the desired 16-bit count value into the I<sup>2</sup>C Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the  $I^2C$  Control register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

Table 73. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH)

| BITS  | 7    | 6 5 4 3 |  |  |  |  | 1 | 0 |  |

|-------|------|---------|--|--|--|--|---|---|--|

| FIELD |      | BRH     |  |  |  |  |   |   |  |

| RESET | FFH  |         |  |  |  |  |   |   |  |

| R/W   | R/W  |         |  |  |  |  |   |   |  |

| ADDR  | F53H |         |  |  |  |  |   |   |  |

BRH =  $I^2C$  Baud Rate High Byte Most significant byte, BRG[15:8], of the  $I^2C$  Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $l^2C$  Diagnostic Control Register is set to 1, a read of the  $l^2C$  BRH register returns the current value of the  $l^2C$  Baud Rate Counter[15:8].

PS019919-1207 I2C Controller

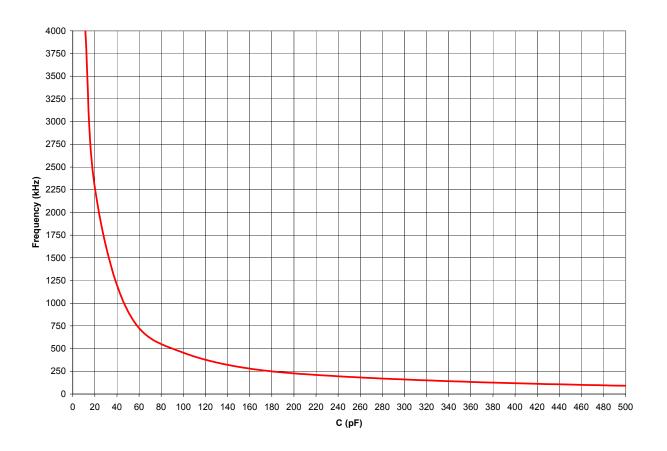

Figure 42. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 k $\Omega$  Resistor

**Caution:** When using the external RC oscillator mode, the oscillator may stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the voltage brown-out threshold. The oscillator will resume oscillation as soon as the supply voltage exceeds 2.7 V.

PS019919-1207 On-Chip Oscillator

# **Ordering Information**

| Part Number                | Flash      | RAM      | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | 1 <sup>2</sup> C | SPI | UARTS with IrDA | Description         |

|----------------------------|------------|----------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|---------------------|

| Z8F642x with 64 KB Flash   |            |          | -to-D     | igita      | I Co                | nvert               | er               |     |                 |                     |

| Standard Temperature: 0 °C |            |          |           |            |                     |                     |                  |     |                 |                     |

| Z8F6421PM020SC             | 64 KB      | 4 KB     | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020SC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020SC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020SC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020SC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020SC             | 64 KB      | 4 KB     | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

| Extended Temperature: -4   | 0 °C to +  | 105 °C   |           |            |                     |                     |                  |     |                 |                     |

| Z8F6421PM020EC             | 64 KB      | 4 KB     | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020EC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020EC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020EC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020EC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020EC             | 64 KB      | 4 KB     | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

| Automotive/Industrial Temp | erature: - | –40 °C t | :o +1     | 25 °C      | )                   |                     |                  |     |                 |                     |

| Z8F6421PM020AC             | 64 KB      | 4 KB     | 29        | 23         | 3                   | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020AC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020AC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020AC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020AC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020AC             | 64 KB      | 4 KB     | 60        | 24         | 4                   | 12                  | 1                | 1   | 2               | QFP 80-pin package  |

PS019919-1207 Ordering Information

| SUB 246                           | IRQ0 enable high and low bit registers 74             |

|-----------------------------------|-------------------------------------------------------|

| SUBX 246                          | IRQ1 enable high and low bit registers 75             |

| SWAP 250                          | IRQ2 enable high and low bit registers 76             |

| TCM 247                           | IRR 243                                               |

| TCMX 247                          | Irr 243                                               |

| TM 247                            |                                                       |

| TMX 247                           |                                                       |

| TRAP 249                          | J                                                     |

| watch-dog timer refresh 248       | JP 249                                                |

| XOR 249                           | jump, conditional, relative, and relative conditional |

| XORX 249                          | 249                                                   |

| instructions, eZ8 classes of 245  |                                                       |

| interrupt control register 79     |                                                       |

| interrupt controller 5, 67        | L                                                     |

| architecture 67                   | LD 248                                                |

| interrupt assertion types 70      | LDC 248                                               |

| interrupt vectors and priority 70 | LDCI 247, 248                                         |

| operation 69                      | LDE 248                                               |

| register definitions 71           | LDEI 247, 248                                         |

| software interrupt assertion 70   | LDX 248                                               |

| interrupt edge select register 78 | LEA 248                                               |

| interrupt port select register 78 | load 248                                              |

| interrupt request 0 register 71   | load constant 247                                     |

| interrupt request 1 register 72   | load constant to/from program memory 248              |

| interrupt request 2 register 73   | load constant with auto-increment addresses 248       |

| interrupt return 249              | load effective address 248                            |

| interrupt vector listing 67       | load external data 248                                |

| interrupts                        | load external data to/from data memory and auto-      |

| not acknowledge 145               | increment addresses 247                               |

| receive 145                       | load external to/from data memory and auto-incre-     |

| SPI 135                           | ment addresses 248                                    |

| transmit 145                      | load instructions 248                                 |

| UART 111                          | load using extended addressing 248                    |

| introduction 1                    | logical AND 248                                       |

| IR 243                            | logical AND/extended addressing 248                   |

| Ir 243                            | logical exclusive OR 249                              |

| IrDA                              | logical exclusive OR/extended addressing 249          |

| architecture 125                  | logical instructions 248                              |

| block diagram 125                 | logical OR 248                                        |

| control register definitions 128  | logical OR/extended addressing 248                    |

| operation 126                     | low power modes 55                                    |

| receiving data 127                | LQFP                                                  |

| transmitting data 126             | 44 lead 266                                           |

| IRET 249                          | 64 lead 267                                           |

PS019919-1207 Index