Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4822ar020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# zilog

## **Manual Objectives**

This Product Specification provides detailed operating information for the Flash devices within Zilog's Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Microcontroller (MCU) products. Within this document, the Z8F642x, Z8F482x, Z8F322x, Z8F242x, and Z8F162x devices are referred to collectively as the Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers unless specifically stated otherwise.

## **About This Manual**

Zilog<sup>®</sup> recommends that you read and understand everything in this manual before setting up and using the product. However, we recognize that there are different styles of learning. Therefore, we have designed this Product Specification to be used either as a *how to* procedural manual or a reference guide to important data.

#### Intended Audience

This document is written for Zilog customers who are experienced at working with microcontrollers, integrated circuits, or printed circuit assemblies.

#### **Manual Conventions**

The following assumptions and conventions are adopted to provide clarity and ease of use:

#### **Courier Typeface**

Commands, code lines and fragments, bits, equations, hexadecimal addresses, and various executable items are distinguished from general text by the use of the Courier typeface. Where the use of the font is not indicated, as in the Index, the name of the entity is presented in upper case.

• Example: FLAGS[1] is smrf.

#### **Hexadecimal Values**

Hexadecimal values are designated by uppercase *H* suffix and appear in the Courier typeface.

• Example: R1 is set to F8H.

#### **Brackets**

The square brackets, [], indicate a register or bus.

• Example: For the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant bit, and R1[0] is the least significant bit.

## Part Selection Guide

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore! XP product line.

## Table 1. Z8 Encore! XP 64K Series Flash Microcontrollers Part Selection Guide

| Part<br>Number    | Flash<br>(KB)                 | RAM<br>(KB) | I/O | 16-bit<br>Timers<br>with PWM | ADC<br>Inputs | UARTs<br>with IrDA | I <sup>2</sup> C | SPI |   | 64/68-pin<br>packages | 80-pin<br>package |

|-------------------|-------------------------------|-------------|-----|------------------------------|---------------|--------------------|------------------|-----|---|-----------------------|-------------------|

| Z8F1621           | 16                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F1622           | 16                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F2421           | 24                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F2422           | 24                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F3221           | 32                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F3222           | 32                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F4821           | 48                            | 4           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F4822           | 48                            | 4           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F4823           | 48                            | 4           | 60  | 4                            | 12            | 2                  | 1                | 1   |   |                       | Х                 |

| Z8F6421           | 64                            | 4           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F6422           | 64                            | 4           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F6423           | 64                            | 4           | 60  | 4                            | 12            | 2                  | 1                | 1   |   |                       | Х                 |

| Die Form<br>Sales | Contact<br>Zilog <sup>®</sup> |             |     |                              |               |                    |                  |     |   |                       |                   |

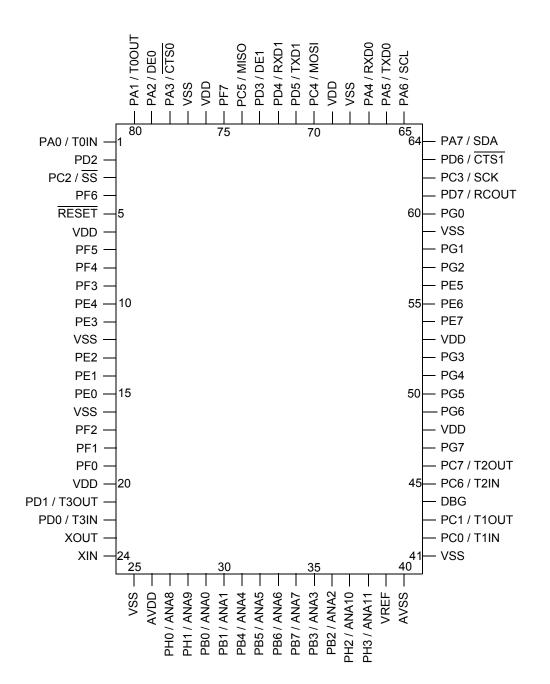

Figure 7. Z8 Encore! XP 64K Series Flash Microcontrollers in 80-Pin Quad Flat Package (QFP)

# zilog

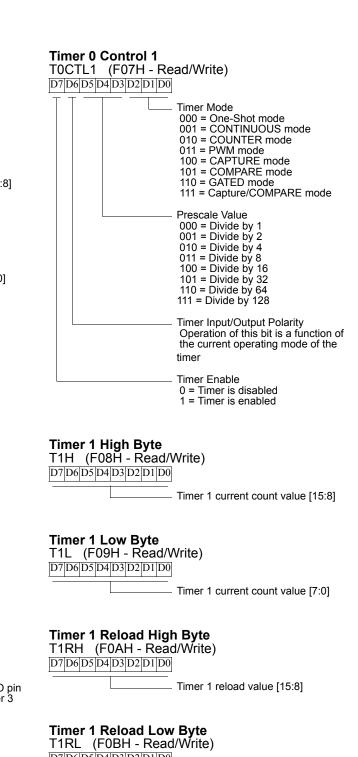

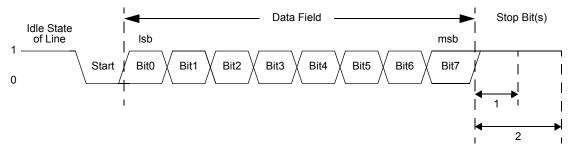

## Control Register Summary

**Timer 0 High Byte** T0H (F00H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Timer 0 current count value [15:8] **Timer 0 Low Byte** T0L (F01H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Timer 0 current count value [7:0] Timer 0 Reload High Byte T0RH (F02H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Timer 0 reload value [15:8] **Timer 0 Reload Low Byte** TORL (HF03 - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Timer 0 reload value [7:0] **Timer 0 PWM High Byte** T0PWMH (F04H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 — Timer 0 PWM value [15:8] Timer 0 Control 0 T0CTL0 (F06H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Reserved Cascade Timer 0 = Timer 0 Input signal is GPIO pin 1 = Timer 0 Input signal is Timer 3 out Reserved

D7|D6|D5|D4|D3|D2|D1|D0| Timer 1 reload value [7:0]

PS019919-1207

## **Timer 0-3 Control 1 Registers**

The Timer 0-3 Control 1 (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

#### Table 46. Timer 0-3 Control 1 Register (TxCTL1)

| BITS  | 7   | 6    | 5          | 4           | 3          | 2 | 1 | 0 |  |  |  |

|-------|-----|------|------------|-------------|------------|---|---|---|--|--|--|

| FIELD | TEN | TPOL | PRES TMODE |             |            |   |   |   |  |  |  |

| RESET |     | 0    |            |             |            |   |   |   |  |  |  |

| R/W   |     |      |            | R/          | W          |   |   |   |  |  |  |

| ADDR  |     |      | F          | F07H, F0FH, | F17H, F1FI | 1 |   |   |  |  |  |

TEN—Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL—Timer Input/Output Polarity Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT** mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS** mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

## COUNTER mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

- 0 = Count occurs on the rising edge of the Timer Input signal.

- 1 = Count occurs on the falling edge of the Timer Input signal.

#### **PWM** mode

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

# zilog

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

## WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the Reset state. The WDT status bit in the Watchdog Timer Control register is set to 1. For more information on Reset, see Reset and Stop Mode Recovery on page 47.

## WDT Reset in STOP Mode

If enabled in STOP mode and configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following WDT time-out in STOP mode. Default operation is for the WDT and its RC oscillator to be enabled during STOP mode.

## WDT RC Disable in STOP Mode

To minimize power consumption in STOP Mode, the WDT and its RC oscillator can be disabled in STOP mode. The following sequence configures the WDT to be disabled when the 64K Series devices enter STOP Mode following execution of a STOP instruction:

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write 81H to the Watchdog Timer Control register (WDTCTL) to configure the WDT and its oscillator to be disabled during STOP Mode. Alternatively, write 00H to the Watchdog Timer Control register (WDTCTL) as the third step in this sequence to reconfigure the WDT and its oscillator to be enabled during STOP mode.

This sequence only affects WDT operation in STOP mode.

## Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. Follow the steps below to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

# zilog 105

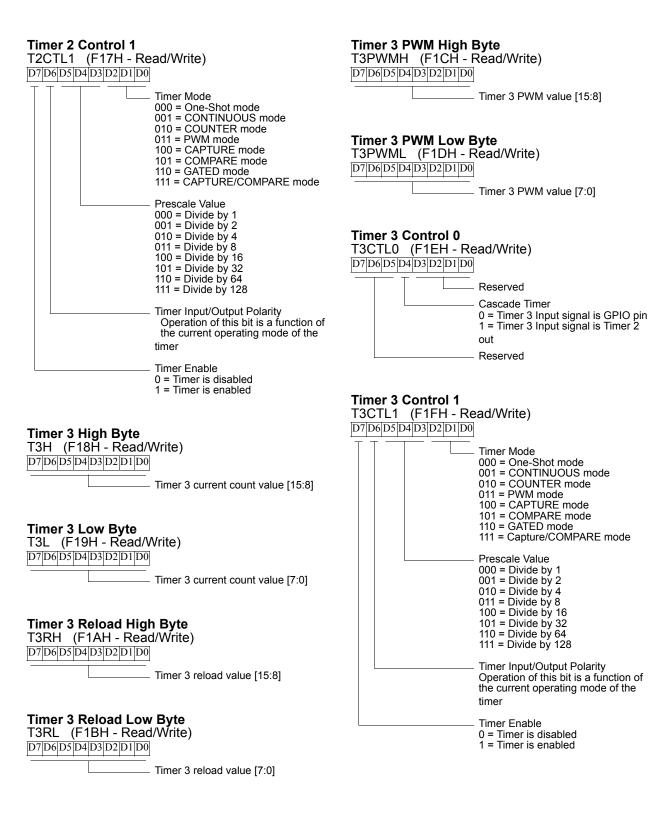

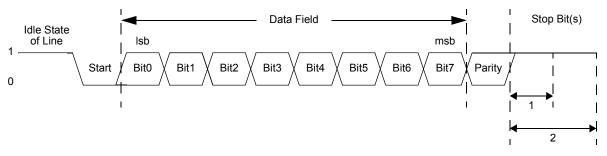

Figure 14. UART Asynchronous Data Format without Parity

Figure 15. UART Asynchronous Data Format with Parity

## Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. If MULTIPROCESSOR mode is desired, write to the UART Control 1 register to enable MULTIPROCESSOR (9-bit) mode functions.

- Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- 4. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- If parity is desired and MULTIPROCESSOR mode is not enabled, set the parity enable bit (PEN) and select either Even or Odd parity (PSEL).

8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine performs the following:

- 1. Write the UART Control 1 register to select the outgoing address bit:

- Set the MULTIPROCESSOR Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 3. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 4. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data register to again become empty.

#### **Receiving Data using the Polled Method**

Follow the steps below to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register to enable MULTIPROCESSOR mode functions, if desired.

- 4. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception.

- Enable parity, if desired and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- 5. Check the RDA bit in the UART Status 0 register to determine if the Receive Data register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to step 6. If the Receive Data register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

- Read data from the UART Receive Data register. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 7. Return to step 5 to receive additional data.

| 9.60 | 23  | 9.73 | 1.32  | <br>9.60 | 12  | 9.60 | 0.00 |

|------|-----|------|-------|----------|-----|------|------|

| 4.80 | 47  | 4.76 | -0.83 | <br>4.80 | 24  | 4.80 | 0.00 |

| 2.40 | 93  | 2.41 | 0.23  | <br>2.40 | 48  | 2.40 | 0.00 |

| 1.20 | 186 | 1.20 | 0.23  | <br>1.20 | 96  | 1.20 | 0.00 |

| 0.60 | 373 | 0.60 | -0.04 | <br>0.60 | 192 | 0.60 | 0.00 |

| 0.30 | 746 | 0.30 | -0.04 | <br>0.30 | 384 | 0.30 | 0.00 |

## Table 61. UART Baud Rates (Continued)

124

The first seven bits transmitted in the first byte are 11110xx. The two bits xx are the two most-significant bits of the 10-bit address. The lowest bit of the first byte transferred is the read/write control bit (=0). The transmit operation is carried out in the same manner as 7-bit addressing.

Follow the steps below for a transmit operation on a 10-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control register to enable Transmit interrupts.

- 3. The  $I^2C$  interrupt asserts because the  $I^2C$  Data register is empty.

- 4. Software responds to the TDRE interrupt by writing the first slave address byte to the  $I^2C$  Data register. The least-significant bit must be 0 for the write operation.

- 5. Software asserts the START bit of the  $I^2C$  Control register.

- 6. The  $I^2C$  Controller sends the START condition to the  $I^2C$  slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register.

- 8. After one bit of address is shifted out by the SDA signal, the Transmit interrupt is asserted.

- 9. Software responds by writing the second byte of address into the contents of the I<sup>2</sup>C Data register.

- 10. The I<sup>2</sup>C Controller shifts the rest of the first byte of address and write bit out the SDA signal.

- If the I<sup>2</sup>C slave acknowledges the first address byte by pulling the SDA signal low during the next high period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status register. Continue with step 12.

If the slave does not acknowledge the first address byte, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status register. Software responds to the Not Acknowledge interrupt by setting the STOP and FLUSH bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore the following steps).

- 12. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register.

- 13. The I<sup>2</sup>C Controller shifts the second address byte out the SDA signal. After the first bit has been sent, the Transmit interrupt is asserted.

- 14. Software responds by writing a data byte to the  $I^2C$  Data register.

- 15. The I<sup>2</sup>C Controller completes shifting the contents of the shift register on the SDA signal.

- 0 = DMA0 is not the source of the interrupt from the DMA Controller.

- 1 = DMA0 completed transfer of data to/from the End Address and generated an interrupt.

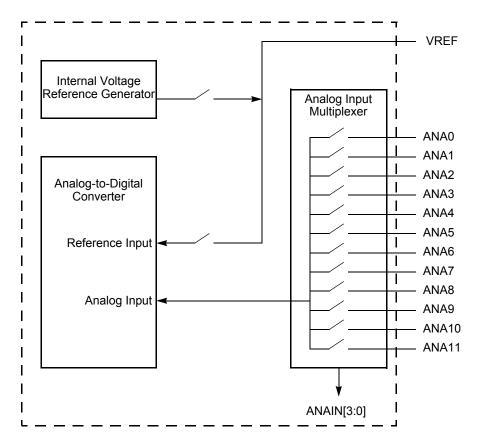

Figure 34. Analog-to-Digital Converter Block Diagram

The sigma-delta ADC architecture provides alias and image attenuation below the amplitude resolution of the ADC in the frequency range of DC to one-half the ADC clock rate (one-fourth the system clock rate). The ADC provides alias free conversion for frequencies up to one-half the ADC clock rate. Thus the sigma-delta ADC exhibits high noise immunity making it ideal for embedded applications. In addition, monotonicity (no missing codes) is guaranteed by design.

## Operation

## **Automatic Power-Down**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered-down. From this power-down state, the ADC requires 40 system clock cycles to power-up. The ADC powers up when a conversion is requested using the ADC Control register.

- 5. Re-write the page written in step 2 to the Page Select register.

- 6. Write the Page Erase command 95H to the Flash Control register.

## Mass Erase

The Flash memory cannot be Mass Erased by user code.

## **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Programming algorithms by controlling the Flash programming signals directly.

Flash Controller Bypass is recommended for gang programming applications and large volume customers who do not require in-circuit programming of the Flash memory.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore! available for download at <u>www.zilog.com</u>.

## Flash Controller Behavior in Debug Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select register.

- Bits in the Flash Sector Protect register can be written to one or zero.

- The second write of the Page Select register to unlock the Flash Controller is not necessary.

- The Page Select register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control register.

Caution: For security reasons, Flash controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the Flash controller must go through the unlock sequence again to select another page.

## Table 96. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|--|--|

| FIELD |   | FFREQH |   |    |    |   |   |   |  |  |  |  |

| RESET |   |        |   | (  | )  |   |   |   |  |  |  |  |

| R/W   |   |        |   | R/ | W  |   |   |   |  |  |  |  |

| ADDR  |   |        |   | FF | AH |   |   |   |  |  |  |  |

## Table 97. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|--|

| FIELD |   | FFREQL |   |    |    |   |   |   |  |  |  |

| RESET |   | 0      |   |    |    |   |   |   |  |  |  |

| R/W   |   | R/W    |   |    |    |   |   |   |  |  |  |

| ADDR  |   |        |   | FF | BH |   |   |   |  |  |  |

FFREQH and FFREQL—Flash Frequency High and Low Bytes

These 2 bytes, {FFREQH[7:0], FFREQL[7:0]}, contain the 16-bit Flash Frequency value.

#### 196

#### Flash Memory Address 0000H

| BITS        | 7            | 6            | 5            | 4          | 3          | 2        | 1   | 0 |  |  |  |  |

|-------------|--------------|--------------|--------------|------------|------------|----------|-----|---|--|--|--|--|

| FIELD       | WDT_RE<br>S  | WDT_AO       | OSC_S        | SEL[1:0]   | RP         | Reserved | FWP |   |  |  |  |  |

| RESET       |              | U            |              |            |            |          |     |   |  |  |  |  |

| R/W         |              |              |              | R          | W          |          |     |   |  |  |  |  |

| ADDR        |              |              |              | Program Me | mory 0000H |          |     |   |  |  |  |  |

| Note: U = U | Unchanged by | y Reset. R/W | = Read/Write | e.         |            |          |     |   |  |  |  |  |

#### Table 98. Flash Option Bits At Flash Memory Address 0000H

WDT RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a Short Reset. This setting is the default for unprogrammed (erased) Flash.

#### WDT\_AO—Watchdog Timer Always On

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled except during STOP Mode (if configured to power down during STOP Mode).

1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

OSC\_SEL[1:0]—Oscillator Mode Selection

00 = On-chip oscillator configured for use with external RC networks (<4 MHz).

01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0 MHz).

10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 10.0 MHz).

11 = Maximum power for use with high frequency crystals (8.0 MHz to 20.0 MHz). This setting is the default for unprogrammed (erased) Flash.

VBO\_AO—Voltage Brownout Protection Always On

- 0 = Voltage Brownout Protection is disabled in STOP mode to reduce total power consumption.

- 1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

RP-Read Protect

0 = User program code is inaccessible. Limited control features are available through

264

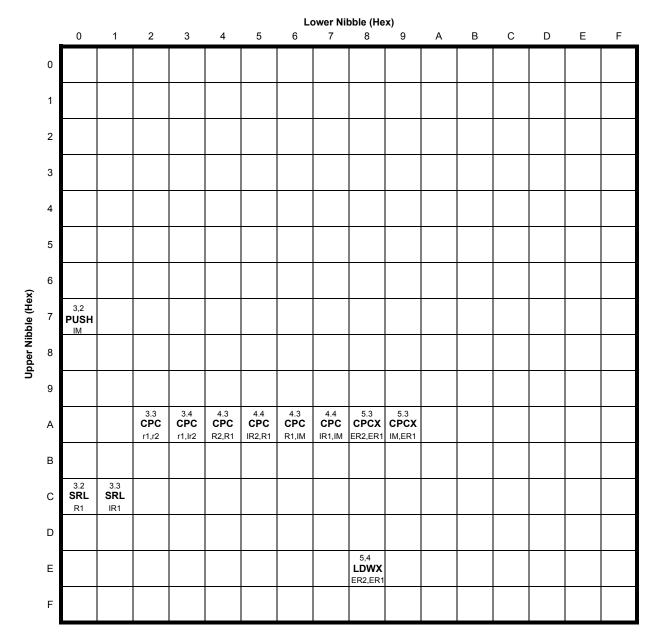

Figure 61. Second Opcode Map after 1FH

270

## **Ordering Information**

| Part Number                | Flash      | RAM      | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I²C | SPI | UARTs with IrDA | Description         |

|----------------------------|------------|----------|-----------|------------|---------------------|---------------------|-----|-----|-----------------|---------------------|

| Z8F642x with 64 KB Flash   | •          | -        | -to-D     | igita      | l Co                | onvert              | ter |     |                 |                     |

| Standard Temperature: 0 °C |            |          |           |            |                     |                     |     |     |                 |                     |

| Z8F6421PM020SC             | 64 KB      | 4 KB     | 29        | 23         | 3                   | 8                   | 1   | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020SC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020SC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020SC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020SC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020SC             | 64 KB      | 4 KB     | 60        | 24         | 4                   | 12                  | 1   | 1   | 2               | QFP 80-pin package  |

| Extended Temperature: -40  | 0 °C to +  | 105 °C   |           |            |                     |                     |     |     |                 |                     |

| Z8F6421PM020EC             | 64 KB      | 4 KB     | 29        | 23         | 3                   | 8                   | 1   | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020EC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020EC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020EC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020EC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020EC             | 64 KB      | 4 KB     | 60        | 24         | 4                   | 12                  | 1   | 1   | 2               | QFP 80-pin package  |

| Automotive/Industrial Temp | erature: · | –40 °C t | :0 +1:    | 25 °(      | 2                   |                     |     |     |                 |                     |

| Z8F6421PM020AC             | 64 KB      | 4 KB     | 29        | 23         | 3                   | 8                   | 1   | 1   | 2               | PDIP 40-pin package |

| Z8F6421AN020AC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | LQFP 44-pin package |

| Z8F6421VN020AC             | 64 KB      | 4 KB     | 31        | 23         | 3                   | 8                   | 1   | 1   | 2               | PLCC 44-pin package |

| Z8F6422AR020AC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | LQFP 64-pin package |

| Z8F6422VS020AC             | 64 KB      | 4 KB     | 46        | 24         | 4                   | 12                  | 1   | 1   | 2               | PLCC 68-pin package |

| Z8F6423FT020AC             | 64 KB      | 4 KB     | 60        | 24         | 4                   | 12                  | 1   | 1   | 2               | QFP 80-pin package  |

| aquina<br>N<br>Z<br>Z8F242x with 24 KB Flas | ч<br>se<br>ц<br>н, 10-Bit | WY<br>Analog | -to-D | Interrupts | C 16-Bit Timers w/PWM | 10-Bit A/D Channels | 1 <sup>2</sup> C | SPI | UARTs with IrDA | Description         |

|---------------------------------------------|---------------------------|--------------|-------|------------|-----------------------|---------------------|------------------|-----|-----------------|---------------------|

| Standard Temperature: 0 °                   | C to 70 °0                | C            |       |            |                       |                     |                  |     |                 |                     |

| Z8F2421PM020SC                              | 24 KB                     | 2 KB         | 29    | 23         | 3                     | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F2421AN020SC                              | 24 KB                     | 2 KB         | 31    | 23         | 3                     | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F2421VN020SC                              | 24 KB                     | 2 KB         | 31    | 23         | 3                     | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F2422AR020SC                              | 24 KB                     | 2 KB         | 46    | 24         | 4                     | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F2422VS020SC                              | 24 KB                     | 2 KB         | 46    | 24         | 4                     | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Extended Temperature: -4                    | 0 °C to 10                | 05 °C        |       |            |                       |                     |                  |     |                 |                     |

| Z8F2421PM020EC                              | 24 KB                     | 2 KB         | 29    | 23         | 3                     | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F2421AN020EC                              | 24 KB                     | 2 KB         | 31    | 23         | 3                     | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F2421VN020EC                              | 24 KB                     | 2 KB         | 31    | 23         | 3                     | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F2422AR020EC                              | 24 KB                     | 2 KB         | 46    | 24         | 4                     | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F2422VS020EC                              | 24 KB                     | 2 KB         | 46    | 24         | 4                     | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

| Automotive/Industrial Temp                  | perature:                 | –40 °C 1     | to 12 | 5 °C       |                       |                     |                  |     |                 |                     |

| Z8F2421PM020AC                              | 24 KB                     | 2 KB         | 29    | 23         | 3                     | 8                   | 1                | 1   | 2               | PDIP 40-pin package |

| Z8F2421AN020AC                              | 24 KB                     | 2 KB         | 31    | 23         | 3                     | 8                   | 1                | 1   | 2               | LQFP 44-pin package |

| Z8F2421VN020AC                              | 24 KB                     | 2 KB         | 31    | 23         | 3                     | 8                   | 1                | 1   | 2               | PLCC 44-pin package |

| Z8F2422AR020AC                              | 24 KB                     | 2 KB         | 46    | 24         | 4                     | 12                  | 1                | 1   | 2               | LQFP 64-pin package |

| Z8F2422VS020AC                              | 24 KB                     | 2 KB         | 46    | 24         | 4                     | 12                  | 1                | 1   | 2               | PLCC 68-pin package |

273

284

flash page select (FPS) 191 flash status (FSTAT) 190 GPIO port A-H address (PxADDR) 61 GPIO port A-H alternate function sub-registers 63 GPIO port A-H control address (PxCTL) 62 GPIO port A-H data direction sub-registers 63 I2C baud rate high (I2CBRH) 160, 161, 163 I2C control (I2CCTL) 158 I2C data (I2CDATA) 157 I2C status 157 I2C status (I2CSTAT) 157 I2Cbaud rate low (I2CBRL) 161 mode, SPI 140 OCD control 209 OCD status 210 SPI baud rate high byte (SPIBRH) 142 SPI baud rate low byte (SPIBRL) 142 SPI control (SPICTL) 138 SPI data (SPIDATA) 137 SPI status (SPISTAT) 139 status, I2C 157 status, SPI 139 UARTx baud rate high byte (UxBRH) 121 UARTx baud rate low byte (UxBRL) 121 UARTx Control 0 (UxCTL0) 117, 120 UARTx control 1 (UxCTL1) 118 UARTx receive data (UxRXD) 115 UARTx status 0 (UxSTAT0) 115 UARTx status 1 (UxSTAT1) 117 UARTx transmit data (UxTXD) 114 watch-dog timer control (WDTCTL) 100 watch-dog timer reload high byte (WDTH) 102 watch-dog timer reload low byte (WDTL) 102 watch-dog timer reload upper byte (WDTU) 102 register file 19 register file address map 23 register pair 243 register pointer 244 reset and STOP mode characteristics 48 carry flag 247 controller 5

sources 48 RET 249 return 249 RL 249 RLC 249 rotate and shift instructions 249 rotate left 249 rotate left through carry 249 rotate right 249 rotate right through carry 249 RP 244 RR 243, 249 rr 243 RRC 249

## S

**SBC 246** SCF 247 SDA and SCL (IrDA) signals 145 second opcode map after 1FH 264 serial clock 131 serial peripheral interface (SPI) 129 set carry flag 247 set register pointer 247 shift right arithmetic 249 shift right logical 250 signal descriptions 14 single-shot conversion (ADC) 177 SIO 5 slave data transfer formats (I2C) 151 slave select 132 software trap 249 source operand 244 SP 244 SPI architecture 129 baud rate generator 136 baud rate high and low byte register 142 clock phase 132 configured as slave 130 control register 137 control register definitions 137 data register 137