## E·XFL

#### Zilog - Z8F4822AR020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 46                                                            |

| Program Memory Size        | 48KB (48K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 64-LQFP                                                       |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4822ar020sc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers **Product Specification**

| General-Purpose I/O Port Output Timing     | 233 |

|--------------------------------------------|-----|

| On-Chip Debugger Timing                    | 234 |

| SPI Master Mode Timing 2                   | 235 |

| SPI Slave Mode Timing 2                    | 236 |

| I2C Timing                                 | 237 |

| UART Timing                                | 238 |

| eZ8 <sup>™</sup> CPU Instruction Set       | 241 |

| Assembly Language Programming Introduction | 241 |

| Assembly Language Syntax 2                 | 242 |

| eZ8 CPU Instruction Notation 2             | 242 |

| Condition Codes                            | 244 |

| eZ8 CPU Instruction Classes                | 245 |

| eZ8 CPU Instruction Summary 2              |     |

| Flags Register                             | 259 |

| Opcode Maps                                | 261 |

| Packaging                                  | 265 |

| Ordering Information                       | 270 |

| Part Number Suffix Designations            | 275 |

| Index                                      | 277 |

| Customer Support                           | 287 |

#### xiii

#### Braces

The curly braces, { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• Example: The 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most-significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

#### Parentheses

The parentheses, (), indicate an indirect register address lookup.

• Example: (R1) is the memory location referenced by the address contained in the Working Register R1.

#### **Parentheses/Bracket Combinations**

The parentheses, (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• Example: Assume PC[15:0] contains the value 1234h. (PC[15:0]) then refers to the contents of the memory location at address 1234h.

#### Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words reset or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* may not be included; however, it is implied.

#### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register [n:n].

• Example: ADDR[15:0] refers to bits 15 through bit 0 of the Address.

#### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least* significant byte and most significant byte, respectively. The lowercase forms, *lsb* and *msb*, mean *least* significant bit and most significant bit, respectively.

#### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings and conditions in general text.

- Example 1: The receiver forces the SCL line to Low.

- Example 2: The Master can generate a Stop condition to abort the transfer.

### **Address Space**

#### **Overview**

The eZ8<sup>™</sup> CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O port control registers.

- The Program Memory contains addresses for all memory locations having executable code and/or data.

- The Data Memory consists of the addresses for all memory locations that hold only data.

These three address spaces are covered briefly in the following subsections. For more information on eZ8 CPU and its address space, refer to  $eZ8^{TM}$  CPU Core User Manual (UM0128) available for download at www.zilog.com.

#### **Register File**

The Register File address space in the 64K Series is 4 KB (4096 bytes). The Register File is composed of two sections—control registers and general-purpose registers. When instructions are executed, registers are read from when defined as sources and written to when defined as destinations. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256-byte control register section are reserved (unavailable). Reading from an reserved Register File addresses returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The 64K Series provide 2 KB to 4 KB of on-chip RAM depending upon the device. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect. To determine the amount of RAM available for the specific 64K Series device, see Part Selection Guide on page 2.

#### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers **Product Specification**

| DMA1 Control<br>DMA1CTL (FB8H -<br>D7]D6]D5]D4]D3]D2]D1]D0 | Read/Write)                                                                                                                                                    | DMA1 Address Hig<br>DMA1H (FBAH - Re<br>D7D6D5D4D3D2D1D0        | ead/Write)                |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------|

|                                                            | - Request Trigger Source Select                                                                                                                                |                                                                 | DMA1 Start Address [11:8] |

|                                                            | 000 = Timer 0<br>001 = Timer 1<br>010 = Timer 2<br>011 = Timer 3<br>100 = UART0 Transmit Data register                                                         |                                                                 | DMA1 End Address [11:8]   |

|                                                            | is empty<br>101 = UART1 Transmit Data register<br>is empty<br>110 = I2C Transmit Data register                                                                 | <b>DMA1 Start/Current</b><br>DMA1START (FBB<br>D7D6D5D4D3D2D1D0 | H - Read/Write)           |

|                                                            | is empty<br>111 = Reserved                                                                                                                                     |                                                                 | DMA1 Start Address [7:0]  |

|                                                            | <ul> <li>Word Select</li> <li>0 = DMA transfers 1 byte per request</li> <li>1 = DMA transfers 2 bytes per request</li> </ul>                                   | DMA1 End Address<br>DMA1END (FBCH -<br>D7 D6 D5 D4 D3 D2 D1 D0  | - Read/Ŵrite)             |

|                                                            | <ul> <li>DMA1 Interrupt Enable</li> <li>0 = DMA1 does not generate</li> <li>interrupts</li> </ul>                                                              |                                                                 | DMA1 End Address [7:0]    |

|                                                            | 1 = DMA1 generates an interrupt<br>when<br>End Address data is transferred                                                                                     | DMA_ADC Address<br>DMAA_ADDR (FBL<br>D7 D6 D5 D4 D3 D2 D1 D0    | )H - Read/Write)          |

|                                                            | <ul> <li>DMA1 Data Transfer Direction</li> <li>0 = Register File to peripheral</li> <li>registers</li> </ul>                                                   |                                                                 | Reserved                  |

|                                                            | 1 = Peripheral registers to Register<br>File                                                                                                                   |                                                                 | DMA_ADC Address           |

|                                                            | <ul> <li>DMA1 Loop Enable</li> <li>0 = DMA disables after End Address</li> <li>1 = DMA reloads Start Address after<br/>End Address and continues to</li> </ul> |                                                                 |                           |

|                                                            | run<br>- DMA1 Enable<br>0 = DMA1 is disabled<br>1 = DMA1 is enabled                                                                                            |                                                                 |                           |

|                                                            |                                                                                                                                                                |                                                                 |                           |

DMA1 I/O Address DMA1IO (FB9H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0

PS019919-1207

DMA1 Peripheral Register Address Low byte of on-chip peripheral control registers on Register File page FH

#### **Operating Mode Reset Source Reset Type** NORMAL or HALT Power-On Reset/Voltage system reset modes Brownout Watchdog Timer time-out system reset when configured for Reset RESET pin assertion system reset On-Chip Debugger initiated Reset system reset except the On-Chip Debugger is (OCDCTL[0] set to 1) unaffected by the reset Power-On Reset/Voltage STOP mode system reset Brownout **RESET** pin assertion system reset DBG pin driven Low system reset

#### Table 9. Reset Sources and Resulting Reset Type

#### **Power-On Reset**

Each device in the 64K Series contains an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 66 cycles of the Watchdog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The devices are held in the Reset state until both the POR Counter and XTAL counter have timed out. After the 64K Series devices exit the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watchdog Timer Control (WDTCTL) register is set to 1.

Figure 8 displays Power-On Reset operation. For the POR threshold voltage ( $V_{POR}$ ), see Electrical Characteristics on page 215.

AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A–H Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A–H Output Control Sub-Registers

The Port A–H Output Control sub-register (Table 18) is accessed through the Port A–H Control register by writing 03H to the Port A–H Address register. Setting the bits in the Port A–H Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

#### Table 18. Port A-H Output Control Sub-Registers

| BITS  | 7      | 6                                                                                 | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-------|--------|-----------------------------------------------------------------------------------|------|------|------|------|------|------|--|

| FIELD | POC7   | POC6                                                                              | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |  |

| RESET |        | 0                                                                                 |      |      |      |      |      |      |  |

| R/W   |        | R/W                                                                               |      |      |      |      |      |      |  |

| ADDR  | lf 03F | If 03H in Port A–H Address Register, accessible through Port A–H Control Register |      |      |      |      |      |      |  |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and disables the drains if set to 1.

0 = The drains are enabled for any output mode.

1 = The drain of the associated pin is disabled (open-drain mode).

#### Port A-H High Drive Enable Sub-Registers

The Port A–H High Drive Enable sub-register (Table 19) is accessed through the Port A–H Control register by writing 04H to the Port A–H Address register. Setting the bits in the Port A–H High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–H High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

configuration bits. In general, the address compare feature reduces the load on the CPU, since it does not need to access the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes.

- Interrupt on matched address bytes and correctly framed data bytes.

- Interrupt only on correctly framed data bytes.

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all MULTIPROCESSOR modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. At this point, each new incoming byte interrupts the CPU. The software is then responsible for determining the end of the frame. It checks for end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, then set MPMD[0] to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme is enabled by setting MPMD[1:0] to 10b and writing the UART's address into the UART Address Compare Register. This mode introduces more hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. The first data byte in the frame contains the NEWFRM=1 in the UART Status 1 Register. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continue sand the NEWFRM bit is set for the first byte of the new frame. If there is no match, then the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame is still accompanied by a NEWFRM assertion.

#### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 17. The Driver Enable signal asserts

# zilog

- 120

- 1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

#### **UART Address Compare Register**

The UART Address Compare register (Table 58) stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

#### Table 58. UART Address Compare Register (UxADDR)

| BITS  | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---------------|---|---|---|---|---|---|

| FIELD |   | COMP_ADDR     |   |   |   |   |   |   |

| RESET |   | 0             |   |   |   |   |   |   |

| R/W   |   | R/W           |   |   |   |   |   |   |

| ADDR  |   | F45H and F4DH |   |   |   |   |   |   |

COMP\_ADDR—Compare Address

This 8-bit value is compared to the incoming address bytes.

#### UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (see Table 59 and Table 60 on page 121) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the desired 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the UART BRG interrupt interval is calculated using the following equation:

UART BRG Interrupt Interval(s) = System Clock Period (s) × BRG[15:0]

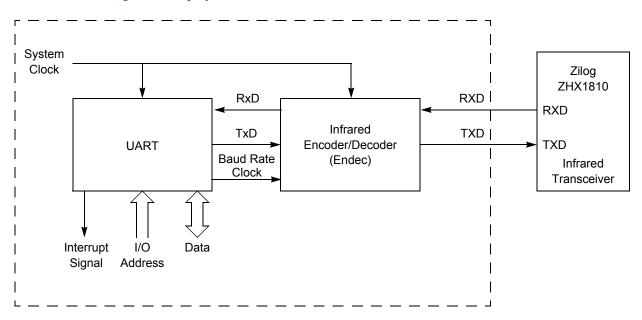

### **Infrared Encoder/Decoder**

#### **Overview**

The 64K Series products contain two fully-functional, high-performance UART to Infrared Encoder/Decoders (Endecs). Each Infrared Endec is integrated with an on-chip UART to allow easy communication between the 64K Series and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers, and other infrared enabled devices.

### Architecture

Figure 19 displays the architecture of the Infrared Endec.

Figure 19. Infrared Data Communication System Block Diagram

# zilog

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

#### SPI Signals

The four basic SPI signals are:

- Master-In/Slave-Out

- Master-Out/Slave-In

- Serial Clock

- Slave Select

Each signal is described in both Master and Slave modes.

#### Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### **Serial Clock**

The Serial Clock (SCK) synchronizes data movement both in and out of the device through its MOSI and MISO pins. In MASTER mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted. When configured as a slave, the SPI block requires a minimum SCK period of greater than or equal to 8 times the system (XIN) clock period.

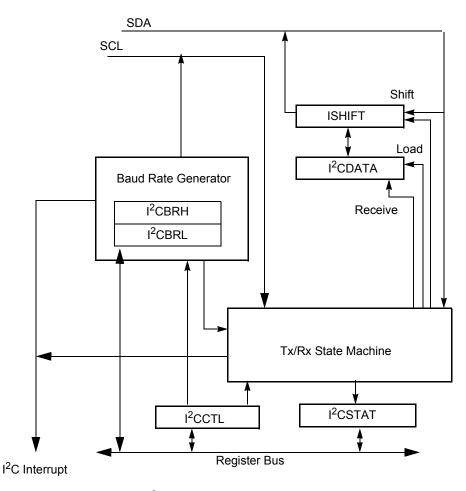

### I<sup>2</sup>C Controller

#### **Overview**

The I<sup>2</sup>C Controller makes the 64K Series products bus-compatible with the I<sup>2</sup>C protocol. The I<sup>2</sup>C Controller consists of two bidirectional bus lines—a serial data signal (SDA) and a serial clock signal (SCL). Features of the I<sup>2</sup>C Controller include:

- Transmit and Receive Operation in MASTER mode

- Maximum data rate of 400 kbit/sec

- 7- and 10-bit addressing modes for Slaves

- Unrestricted number of data bytes transmitted per transfer

The I<sup>2</sup>C Controller in the 64K Series products does not operate in SLAVE mode.

### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers **Product Specification**

### **Architecture**

Figure 27 displays the architecture of the I<sup>2</sup>C Controller.

#### Operation

The I<sup>2</sup>C Controller operates in MASTER mode to transmit and receive data. Only a single master is supported. Arbitration between two masters must be accomplished in software. I<sup>2</sup>C supports the following operations:

- Master transmits to a 7-bit slave •

- Master transmits to a 10-bit slave •

# zilog

16. If the I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal low during the next high period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status register. Continue with step 17.

If the slave does not acknowledge the second address byte or one of the data bytes, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status register. Software responds to the Not Acknowledge interrupt by setting the STOP and FLUSH bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore the following steps).

- 17. The I<sup>2</sup>C Controller shifts the data out by the SDA signal. After the first bit is sent, the Transmit interrupt is asserted.

- 18. If more bytes remain to be sent, return to step 14.

- 19. If the last byte is currently being sent, software sets the STOP bit of the I<sup>2</sup>C Control register (or START bit to initiate a new transaction). In the STOP case, software also clears the TXI bit of the I<sup>2</sup>C Control register at the same time.

- 20. The I<sup>2</sup>C Controller completes transmission of the last data byte on the SDA signal.

- 21. The slave may either Acknowledge or Not Acknowledge the last byte. Because either the STOP or START bit is already set, the NCKI interrupt does not occur.

- 22. The I<sup>2</sup>C Controller sends the STOP (or RESTART) condition to the I<sup>2</sup>C bus and clears the STOP (or START) bit.

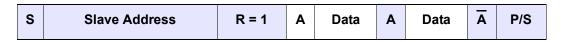

#### **Read Transaction with a 7-Bit Address**

Figure 32 displays the data transfer format for a read operation to a 7-bit addressed slave. The shaded regions indicate data transferred from the  $I^2C$  Controller to slaves and unshaded regions indicate data transferred from the slaves to the  $I^2C$  Controller.

#### Figure 32. Receive Data Transfer Format for a 7-Bit Addressed Slave

Follow the steps below for a read operation to a 7-bit addressed slave:

- 1. Software writes the  $I^2C$  Data register with a 7-bit slave address plus the read bit (=1).

- 2. Software asserts the START bit of the I<sup>2</sup>C Control register.

- 3. If this is a single byte transfer, Software asserts the NAK bit of the I<sup>2</sup>C Control register so that after the first byte of data has been read by the I<sup>2</sup>C Controller, a Not Acknowledge is sent to the I<sup>2</sup>C slave.

| TXRXSTATE | State Description                                                                       |

|-----------|-----------------------------------------------------------------------------------------|

| 1_1101    | 10-bit addressing: Bit 3 of 2nd address byte<br>7-bit addressing: Bit 3 of address byte |

| 1_1110    | 10-bit addressing: Bit 2 of 2nd address byte<br>7-bit addressing: Bit 2 of address byte |

| 1_1111    | 10-bit addressing: Bit 1 of 2nd address byte<br>7-bit addressing: Bit 1 of address byte |

### I<sup>2</sup>C Diagnostic Control Register

The I<sup>2</sup>C Diagnostic register (Table 76) provides control over diagnostic modes. This register is a read/write register used for I<sup>2</sup>C diagnostics.

### Table 76. I<sup>2</sup>C Diagnostic Control Register (I2CDIAG)

| BITS  | 7        | 6    | 5 | 4 | 3 | 2 | 1   | 0    |

|-------|----------|------|---|---|---|---|-----|------|

| FIELD | Reserved |      |   |   |   |   |     | DIAG |

| RESET | 0        |      |   |   |   |   |     |      |

| R/W   | R        |      |   |   |   |   | R/W |      |

| ADDR  |          | F56H |   |   |   |   |     |      |

DIAG = Diagnostic Control Bit - Selects read back value of the Baud Rate Reload registers.

- 0 = NORMAL mode. Reading the Baud Rate High and Low Byte registers returns the baud rate reload value.

- 1 = DIAGNOSTIC mode. Reading the Baud Rate High and Low Byte registers returns the baud rate counter value.

# zilog

#### 170

#### DMAx Start/Current Address Low Byte Register

The DMAx Start/Current Address Low register, in conjunction with the DMAx Address High Nibble register, forms a 12-bit Start/Current Address. Writes to this register set the Start Address for DMA operations. Each time the DMA completes a data transfer, the 12-bit Start/Current Address increments by either 1 (single-byte transfer) or 2 (two-byte word transfer). Reads from this register return the low byte of the Current Address to be used for the next DMA data transfer.

#### Table 80. DMAx Start/Current Address Low Byte Register (DMAxSTART)

| BITS  | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| FIELD |   | DMA_START  |   |   |   |   |   |   |

| RESET |   | X          |   |   |   |   |   |   |

| R/W   |   | R/W        |   |   |   |   |   |   |

| ADDR  |   | FB3H, FBBH |   |   |   |   |   |   |

DMA\_START—DMAx Start/Current Address Low

These bits, with the four lower bits of the DMAx\_H register, form the 12-bit Start/Current address. The full 12-bit address is given by {DMA\_START\_H[3:0], DMA\_START[7:0]}.

#### DMAx End Address Low Byte Register

The DMAx End Address Low Byte register (Table 80), in conjunction with the DMAx\_H register (Table 81), forms a 12-bit End Address.

#### Table 81. DMAx End Address Low Byte Register (DMAxEND)

| BITS  | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| FIELD |   | DMA_END    |   |   |   |   |   |   |

| RESET |   | X          |   |   |   |   |   |   |

| R/W   |   | R/W        |   |   |   |   |   |   |

| ADDR  |   | FB4H, FBCH |   |   |   |   |   |   |

#### DMA\_END—DMAx End Address Low

These bits, with the four upper bits of the DMAx\_H register, form a 12-bit address. This address is the ending location of the DMAx transfer. The full 12-bit address is given by  $\{DMA\_END\_H[3:0], DMA\_END[7:0]\}$ .

### Operation

### **OCD** Interface

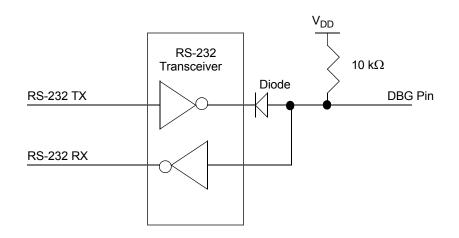

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bi-directional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the 64K Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are depicted in Figure 37 and Figure 38 on page 201.

**Caution:** For operation of the On-Chip Debugger, all power pins  $(V_{DD} \text{ and } AV_{DD})$  must be supplied with power, and all ground pins  $(V_{SS} \text{ and } AV_{SS})$  must be properly grounded.

The DBG pin is open-drain and must always be connected to  $V_{DD}$  through an external pull-up resistor to ensure proper operation.

Figure 37. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

| n | n | E |

|---|---|---|

| 2 | υ | J |

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                    |

|----------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Program Counter      | 06H             | -                                     | Disabled                                                                                                                                                                  |

| Read Program Counter       | 07H             | -                                     | Disabled                                                                                                                                                                  |

| Write Register             | 08H             | -                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register              | 09H             | -                                     | Disabled                                                                                                                                                                  |

| Write Program Memory       | 0AH             | -                                     | Disabled                                                                                                                                                                  |

| Read Program Memory        | 0BH             | -                                     | Disabled                                                                                                                                                                  |

| Write Data Memory          | 0CH             | -                                     | Disabled                                                                                                                                                                  |

| Read Data Memory           | 0DH             | -                                     | Disabled                                                                                                                                                                  |

| Read Program Memory<br>CRC | 0EH             | -                                     | -                                                                                                                                                                         |

| Reserved                   | 0FH             | -                                     | -                                                                                                                                                                         |

| Step Instruction           | 10H             | -                                     | Disabled                                                                                                                                                                  |

| Stuff Instruction          | 11H             | -                                     | Disabled                                                                                                                                                                  |

| Execute Instruction        | 12H             | -                                     | Disabled                                                                                                                                                                  |

| Reserved                   | 13H - FFH       | -                                     | -                                                                                                                                                                         |

#### Table 101. On-Chip Debugger Commands (Continued)

In the following list of OCD Commands, data and commands sent from the host to the On-Chip Debugger are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the On-Chip Debugger back to the host is identified by 'DBG  $\rightarrow$  Data'

• **Read OCD Revision (00H)**—The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

DBG  $\leftarrow$  00H DBG  $\rightarrow$  OCDREV[15:8] (Major revision number) DBG  $\rightarrow$  OCDREV[7:0] (Minor revision number)

• **Read OCD Status Register (02H)**—The Read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

#### Table 122. Notational Shorthand

| Notation | Description                    | Operand | I Rangeb represents a value from 0 to 7 (000B to 111B).                                                                     |  |  |  |  |  |  |

|----------|--------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| b        | Bit                            | b       |                                                                                                                             |  |  |  |  |  |  |

| СС       | Condition Code                 | —       | Refer to Condition Codes overview in the eZ8 CPU User Manual.                                                               |  |  |  |  |  |  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                   |  |  |  |  |  |  |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                       |  |  |  |  |  |  |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                         |  |  |  |  |  |  |

| lr       | Indirect Working Register      | @Rn     | n = 0 –15                                                                                                                   |  |  |  |  |  |  |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H FFH                                                                            |  |  |  |  |  |  |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                            |  |  |  |  |  |  |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                      |  |  |  |  |  |  |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                   |  |  |  |  |  |  |

| r        | Working Register               | Rn      | n = 0 – 15                                                                                                                  |  |  |  |  |  |  |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                         |  |  |  |  |  |  |

| RA       | Relative Address               | Х       | X represents an index in the range of +127 to<br>-128 which is an offset relative to the address of<br>the next instruction |  |  |  |  |  |  |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                            |  |  |  |  |  |  |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range 00H to FEH                                                                      |  |  |  |  |  |  |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                       |  |  |  |  |  |  |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range.     |  |  |  |  |  |  |

Table 123 contains additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Accombly                                   | Symbolic Operation                                                                        | Address<br>Mode |     | <b>O</b> a se da (s) | Flags |   |   |   |   |   | - Fetch | lu - 1           |

|--------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|-----|----------------------|-------|---|---|---|---|---|---------|------------------|

| Assembly<br>Mnemonic                       |                                                                                           | dst             | src | – Opcode(s)<br>(Hex) | С     | Ζ | S | V | D | Н | Cycles  | Instr.<br>Cycles |

| AND dst, src                               | dst ← dst AND src                                                                         | r               | r   | 52                   | -     | * | * | 0 | - | - | 2       | 3                |

|                                            |                                                                                           | r               | lr  | 53                   |       |   |   |   |   |   | 2       | 4                |

|                                            |                                                                                           | R               | R   | 54                   |       |   |   |   |   |   | 3       | 3                |

|                                            |                                                                                           | R               | IR  | 55                   |       |   |   |   |   |   | 3       | 4                |

|                                            |                                                                                           | R               | IM  | 56                   |       |   |   |   |   |   | 3       | 3                |

|                                            | -                                                                                         | IR              | IM  | 57                   |       |   |   |   |   |   | 3       | 4                |

| ANDX dst, src dst $\leftarrow$ dst AND src |                                                                                           | ER              | ER  | 58                   | -     | * | * | 0 | - | - | 4       | 3                |

|                                            | -                                                                                         | ER              | IM  | 59                   |       |   |   |   |   |   | 4       | 3                |

| ATM                                        | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |                 |     | 2F                   | -     | - | - | - | - | - | 1       | 2                |

| BCLR bit, dst                              | dst[bit] ← 0                                                                              | r               |     | E2                   | -     | * | * | 0 | - | - | 2       | 2                |

| BIT p, bit, dst                            | dst[bit] ← p                                                                              | r               |     | E2                   | -     | * | * | 0 | - | - | 2       | 2                |

| BRK                                        | Debugger Break                                                                            |                 |     | 00                   | -     | - | - | - | - | - | 1       | 1                |

| BSET bit, dst                              | dst[bit] ← 1                                                                              | r               |     | E2                   | -     | * | * | 0 | - | - | 2       | 2                |

| BSWAP dst                                  | $dst[7:0] \leftarrow dst[0:7]$                                                            | R               |     | D5                   | Х     | * | * | 0 | - | - | 2       | 2                |

| BTJ p, bit, src,                           | , if src[bit] = p<br>PC ← PC + X                                                          |                 | r   | F6                   | -     | - | - | - | - | - | 3       | 3                |

| dst                                        |                                                                                           |                 | lr  | F7                   |       |   |   |   |   |   | 3       | 4                |

| BTJNZ bit,<br>src, dst                     | if src[bit] = 1<br>PC $\leftarrow$ PC + X                                                 |                 | r   | F6                   | -     | - | - | - | - | - | 3       | 3                |

|                                            |                                                                                           |                 | lr  | F7                   |       |   |   |   |   |   | 3       | 4                |

| BTJZ bit, src,<br>dst                      | if src[bit] = 0<br>PC ← PC + X                                                            |                 | r   | F6                   | -     | - | - | - | - | - | 3       | 3                |

|                                            |                                                                                           |                 | lr  | F7                   |       |   |   |   |   |   | 3       | 4                |

| CALL dst                                   | $SP \leftarrow SP -2$<br>@SP $\leftarrow PC$<br>PC $\leftarrow dst$                       | IRR             |     | D4                   | -     | - | - | - | - | - | 2       | 6                |

|                                            |                                                                                           | DA              |     | D6                   |       |   |   |   |   |   | 3       | 3                |

| CCF                                        | $C \leftarrow \sim C$                                                                     |                 |     | EF                   | *     | - | - | - | - | - | 1       | 2                |

| CLR dst                                    | dst ← 00H                                                                                 | R               |     | B0                   | -     | - | - | - | - | - | 2       | 2                |

|                                            | -                                                                                         | IR              |     | B1                   |       |   |   |   |   |   | 2       | 3                |

#### Table 133. eZ8 CPU Instruction Summary (Continued)

#### Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

zilog

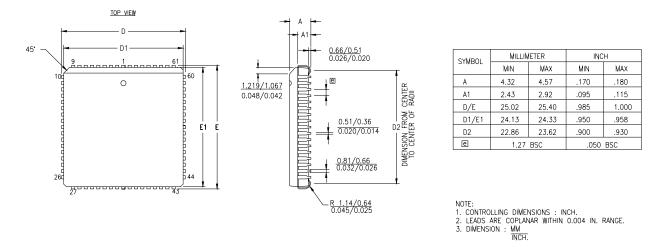

Figure 66. 68-Lead Plastic Lead Chip Carrier Package (PLCC)

Figure 66 displays the 68-pin Plastic Lead Chip Carrier (PLCC) package available for the Z8X1622, Z8X2422, Z8X3222, Z8X4822, and Z8X6422 devices.

268