- - -

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 68-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4822vs020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Information Area                                          | 21 |

|-----------------------------------------------------------|----|

| Register File Address Map 2                               | 23 |

| Control Register Summary 2                                | 28 |

| Reset and Stop Mode Recovery 4                            | 47 |

| Overview                                                  |    |

| Reset Types    4      Reset Sources    4                  |    |

| Power-On Reset                                            |    |

| Voltage Brownout Reset 5                                  |    |

| Watchdog Timer Reset 5                                    |    |

| External Pin Reset                                        |    |

| On-Chip Debugger Initiated Reset                          |    |

| Stop Mode Recovery                                        |    |

| Stop Mode Recovery Using a GPIO Port Pin Transition HALT  |    |

| Low-Power Modes                                           |    |

|                                                           |    |

| Overview         5           STOP Mode         5          |    |

| HALT Mode                                                 |    |

| General-Purpose I/O                                       |    |

| Overview                                                  |    |

| GPIO Port Availability By Device                          |    |

| Architecture                                              |    |

| GPIO Alternate Functions                                  | 59 |

| GPIO Interrupts                                           |    |

| GPIO Control Register Definitions                         |    |

| Port A–H Address Registers 6 Port A–H Control Registers 6 |    |

| Port A–H Input Data Registers                             |    |

| Port A–H Output Data Register                             |    |

| Interrupt Controller                                      | 67 |

| Overview                                                  | 67 |

|                                                           | 67 |

| Architecture                                              | 69 |

| Operation                                                 | 69 |

# zilog

# Introduction

Zilog's Z8 Encore! XP MCU family of products are a line of Zilog<sup>®</sup> microcontroller products based upon the 8-bit eZ8 CPU. The Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers, hereafter referred to collectively as the Z8 Encore! XP or the 64K Series adds Flash memory to Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8<sup>TM</sup> CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich-peripheral set of the Z8 Encore! XP makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

# **Features**

The features of Z8 Encore! XP 64K Series Flash Microcontrollers include:

- 20 MHz eZ8 CPU

- Up to 64 KB Flash with in-circuit programming capability

- Up to 4 KB register RAM

- 12-channel, 10-bit Analog-to-Digital Converter (ADC)

- Two full-duplex 9-bit UARTs with bus transceiver Driver Enable control

- Inter-integrated circuit (I<sup>2</sup>C)

- Serial Peripheral Interface (SPI)

- Two Infrared Data Association (IrDA)-compliant infrared encoder/decoders

- Up to four 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with internal RC oscillator

- Three-channel DMA

- Up to 60 input/output (I/O) pins

- 24 interrupts with configurable priority

- On-Chip Debugger

- Voltage Brownout (VBO) Protection

- Power-On Reset (POR)

- Operating voltage of 3.0 V to 3.6 V with 5 V-tolerant inputs

- 0 °C to +70 °C, -40 °C to +105 °C, and -40 °C to +125 °C operating temperature ranges

# Part Selection Guide

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore! XP product line.

### Table 1. Z8 Encore! XP 64K Series Flash Microcontrollers Part Selection Guide

| Part<br>Number    | Flash<br>(KB)                 | RAM<br>(KB) | I/O | 16-bit<br>Timers<br>with PWM | ADC<br>Inputs | UARTs<br>with IrDA | l <sup>2</sup> C | SPI |   | 64/68-pin<br>packages | 80-pin<br>package |

|-------------------|-------------------------------|-------------|-----|------------------------------|---------------|--------------------|------------------|-----|---|-----------------------|-------------------|

| Z8F1621           | 16                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F1622           | 16                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F2421           | 24                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F2422           | 24                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F3221           | 32                            | 2           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F3222           | 32                            | 2           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F4821           | 48                            | 4           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F4822           | 48                            | 4           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F4823           | 48                            | 4           | 60  | 4                            | 12            | 2                  | 1                | 1   |   |                       | Х                 |

| Z8F6421           | 64                            | 4           | 31  | 3                            | 8             | 2                  | 1                | 1   | Х |                       |                   |

| Z8F6422           | 64                            | 4           | 46  | 4                            | 12            | 2                  | 1                | 1   |   | Х                     |                   |

| Z8F6423           | 64                            | 4           | 60  | 4                            | 12            | 2                  | 1                | 1   |   |                       | Х                 |

| Die Form<br>Sales | Contact<br>Zilog <sup>®</sup> |             |     |                              |               |                    |                  |     |   |                       |                   |

# zilog

# **Program Memory**

The eZ8<sup>™</sup> CPU supports 64 KB of Program Memory address space. The Z8 Encore! XP 64K Series Flash Microcontrollers contains 16 KB to 64 KB of on-chip Flash in the Program Memory address space, depending upon the device. Reading from Program Memory addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory maps for the 64K Series products.

| Program Memory Address | (Hex) Function           |

|------------------------|--------------------------|

| Z8F162x Products       |                          |

| 0000-0001              | Option Bits              |

| 0002-0003              | Reset Vector             |

| 0004-0005              | WDT Interrupt Vector     |

| 0006-0007              | Illegal Instruction Trap |

| 0008-0037              | Interrupt Vectors*       |

| 0038-3FFF              | Program Memory           |

| Z8F242x Products       |                          |

| 0000-0001              | Option Bits              |

| 0002-0003              | Reset Vector             |

| 0004-0005              | WDT Interrupt Vector     |

| 0006-0007              | Illegal Instruction Trap |

| 0008-0037              | Interrupt Vectors*       |

| 0038-5FFF              | Program Memory           |

| Z8F322x Products       |                          |

| 0000-0001              | Option Bits              |

| 0002-0003              | Reset Vector             |

| 0004-0005              | WDT Interrupt Vector     |

| 0006-0007              | Illegal Instruction Trap |

| 0008-0037              | Interrupt Vectors*       |

| 0038-7FFF              | Program Memory           |

| Z8F482x Products       |                          |

# Table 5. Z8 Encore! XP 64K Series Flash Microcontrollers Program Memory Maps

# HALT Mode

Execution of the eZ8 CPU's HALT instruction places the device into HALT mode. In HALT mode, the operating characteristics are:

- Primary crystal oscillator is enabled and continues to operate.

- System clock is enabled and continues to operate.

- eZ8 CPU is stopped.

- Program Counter stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate.

- The Watchdog Timer continues to operate, if enabled.

- All other on-chip peripherals continue to operate.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout Reset

- External **RESET** pin assertion

To minimize current in HALT mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

# **GPIO Control Register Definitions**

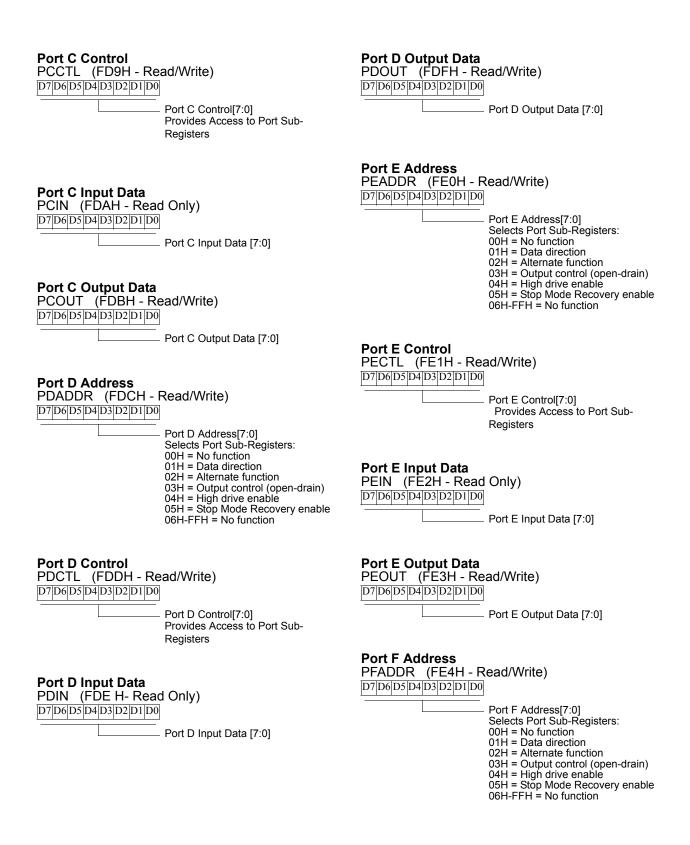

Four registers for each Port provide access to GPIO control, input data, and output data. Table 13 lists these Port registers. Use the Port A–H Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| PxADDR                     | Port A–H Address Register<br>(Selects sub-registers)            |

| PxCTL                      | Port A–H Control Register<br>(Provides access to sub-registers) |

| PxIN                       | Port A–H Input Data Register                                    |

| PxOUT                      | Port A–H Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

|                            |                                                                 |

| PxDD                       | Data Direction                                                  |

| PxDD<br>PxAF               | Data Direction           Alternate Function                     |

| - <u></u>                  |                                                                 |

| PxAF                       | Alternate Function                                              |

#### Table 13. GPIO Port Registers and Sub-Registers

#### Port A–H Address Registers

The Port A–H Address registers select the GPIO Port functionality accessible through the Port A–H Control registers. The Port A–H Address and Control registers combine to provide access to all GPIO Port control (Table 14).

| BITS  | 7          | 6   | 5          | 4         | 3           | 2           | 1   | 0 |  |

|-------|------------|-----|------------|-----------|-------------|-------------|-----|---|--|

| FIELD | PADDR[7:0] |     |            |           |             |             |     |   |  |

| RESET | 00H        |     |            |           |             |             |     |   |  |

| R/W   | R/W        |     |            |           |             |             |     |   |  |

| ADDR  |            | FD0 | H, FD4H, F | D8H, FDCH | , FE0H, FE4 | H, FE8H, FI | ECH |   |  |

# zilog

5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All steps of the Watchdog Timer Reload Unlock sequence must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur, unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Control Register Definitions

# Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register (Table 48) is a Read-Only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

Writing the 55H, AAH unlock sequence to the Watchdog Timer Control (WDTCTL) register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

| BITS  | 7     | 6            | 5     | 4   | 3        | 2 | 1 | 0  |

|-------|-------|--------------|-------|-----|----------|---|---|----|

| FIELD | POR   | STOP         | WDT   | EXT | Reserved |   |   | SM |

| RESET | See d | lescriptions | below | 0   |          |   |   |    |

| R/W   |       | R            |       |     |          |   |   |    |

| ADDR  |       |              |       | FF  | 0H       |   |   |    |

| Table 48. V | Natchdog ' | Timer Control | Register | (WDTCTL) |

|-------------|------------|---------------|----------|----------|

|-------------|------------|---------------|----------|----------|

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCDCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

100

zilog 1

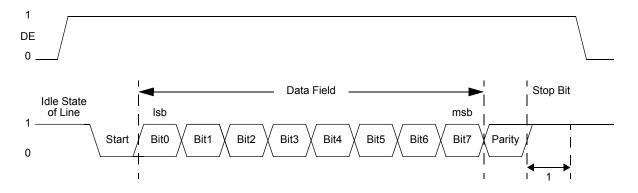

when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This timing allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the last Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

#### Figure 17. UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. At this point, the Transmit Data register may be written with the next character to send. This provides 7 bit periods of latency to load the Transmit Data register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data register clears the TDRE bit to 0.

18.432 MHz System Clock

### 122

#### Table 61. UART Baud Rates

#### 20.0 MHz System Clock

| 20.0 Mil 12 Oy3 | Certi Olock  |             |       | 10.452 10112    | Oystern Oloc   | n           |        |

|-----------------|--------------|-------------|-------|-----------------|----------------|-------------|--------|

| Desired Rate    | BRG Divisor  | Actual Rate | Error | Desired<br>Rate | BRG<br>Divisor | Actual Rate | Error  |

| (kHz)           | (Decimal)    | (kHz)       | (%)   | (kHz)           | (Decimal)      | (kHz)       | (%)    |

| 1250.0          | 1            | 1250.0      | 0.00  | 1250.0          | 1              | 1152.0      | -7.84% |

| 625.0           | 2            | 625.0       | 0.00  | 625.0           | 2              | 576.0       | -7.84% |

| 250.0           | 5            | 250.0       | 0.00  | 250.0           | 5              | 230.4       | -7.84% |

| 115.2           | 11           | 113.6       | -1.36 | 115.2           | 10             | 115.2       | 0.00   |

| 57.6            | 22           | 56.8        | -1.36 | 57.6            | 20             | 57.6        | 0.00   |

| 38.4            | 33           | 37.9        | -1.36 | 38.4            | 30             | 38.4        | 0.00   |

| 19.2            | 65           | 19.2        | 0.16  | 19.2            | 60             | 19.2        | 0.00   |

| 9.60            | 130          | 9.62        | 0.16  | 9.60            | 120            | 9.60        | 0.00   |

| 4.80            | 260          | 4.81        | 0.16  | 4.80            | 240            | 4.80        | 0.00   |

| 2.40            | 521          | 2.40        | -0.03 | 2.40            | 480            | 2.40        | 0.00   |

| 1.20            | 1042         | 1.20        | -0.03 | 1.20            | 960            | 1.20        | 0.00   |

| 0.60            | 2083         | 0.60        | 0.02  | 0.60            | 1920           | 0.60        | 0.00   |

| 0.30            | 4167         | 0.30        | -0.01 | 0.30            | 3840           | 0.30        | 0.00   |

|                 | intern Clask |             |       | 44.0500 MU      | - 0            | -l-         |        |

#### 16.667 MHz System Clock

|     | 0.30        | -0.01  | 0.30            | 3840           |    |

|-----|-------------|--------|-----------------|----------------|----|

| k   |             |        | 11.0592 MHz     | System Clo     | ck |

| sor | Actual Rate | Error  | Desired<br>Rate | BRG<br>Divisor | Ac |

| l)  | (kHz)       | (%)    | (kHz)           | (Decimal)      |    |

|     | 1041.69     | -16.67 | 1250.0          | N/A            |    |

|     | 520.8       | -16.67 | 625.0           | 1              |    |

|     | 260.4       | 4.17   | 250.0           | 3              |    |

|     | 115.7       | 0.47   | 115.2           | 6              |    |

4.80

2.40

|      | Desired | BRG       |             |       |

|------|---------|-----------|-------------|-------|

| ror  | Rate    | Divisor   | Actual Rate | Error |

| %)   | (kHz)   | (Decimal) | (kHz)       | (%)   |

| 6.67 | 1250.0  | N/A       | N/A         | N/A   |

| 5.67 | 625.0   | 1         | 691.2       | 10.59 |

| .17  | 250.0   | 3         | 230.4       | -7.84 |

| .47  | 115.2   | 6         | 115.2       | 0.00  |

| .47  | 57.6    | 12        | 57.6        | 0.00  |

| .47  | 38.4    | 18        | 38.4        | 0.00  |

| .47  | 19.2    | 36        | 19.2        | 0.00  |

| .45  | 9.60    | 72        | 9.60        | 0.00  |

144

288

4.80

2.40

| <b>Desired Rate</b> | BRG Divisor | Actual Rate | Error  |

|---------------------|-------------|-------------|--------|

| (kHz)               | (Decimal)   | (kHz)       | (%)    |

| 1250.0              | 1           | 1041.69     | -16.67 |

| 625.0               | 2           | 520.8       | -16.67 |

| 250.0               | 4           | 260.4       | 4.17   |

| 115.2               | 9           | 115.7       | 0.47   |

| 57.6                | 18          | 57.87       | 0.47   |

| 38.4                | 27          | 38.6        | 0.47   |

| 19.2                | 54          | 19.3        | 0.47   |

| 9.60                | 109         | 9.56        | -0.45  |

| 4.80                | 217         | 4.80        | -0.83  |

434

2.40

0.01

2.40

0.00

0.00

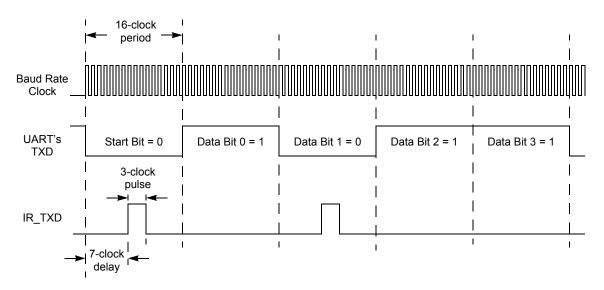

# Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver via the TXD pin. Likewise, data received from the infrared transceiver is passed to the Infrared Endec via the RXD pin, decoded by the Infrared Endec, and then passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 Kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

| Infrared Data Rate (bits/s)   | _ | System Clock Frequency (Hz)                     |

|-------------------------------|---|-------------------------------------------------|

| Inflated Data Rate (bits/s) - | - | $16 \times \text{UART}$ Baud Rate Divisor Value |

# **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clock wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 20 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the 64K Series products while the IR\_TXD signal is output through the TXD pin.

140

$0 = \overline{SS}$  input pin is asserted (Low).  $1 = \overline{SS}$  input is not asserted (High). If SPI enabled as a Master, this bit is not applicable.

### **SPI Mode Register**

The SPI Mode register (Table 66) configures the character bit width and the direction and value of the  $\overline{SS}$  pin.

| Table 6 | 66. SPI | Mode | Register | (SPIMODE)                               |

|---------|---------|------|----------|-----------------------------------------|

|         |         |      |          | (•••••••••••••••••••••••••••••••••••••• |

| BITS  | 7     | 6     | 5                 | 4  | 3  | 2    | 1   | 0 |

|-------|-------|-------|-------------------|----|----|------|-----|---|

| FIELD | Rese  | erved | DIAG NUMBITS[2:0] |    |    | SSIO | SSV |   |

| RESET |       | 0     |                   |    |    |      |     |   |

| R/W   | R R/W |       |                   |    |    |      |     |   |

| ADDR  |       |       |                   | F6 | 3H |      |     |   |

Reserved—Must be 0.

DIAG-Diagnostic Mode Control bit

This bit is for SPI diagnostics. Setting this bit allows the Baud Rate Generator value to be read using the SPIBRH and SPIBRL register locations.

- 0 = Reading SPIBRH, SPIBRL returns the value in the SPIBRH and SPIBRL registers

- 1 = Reading SPIBRH returns bits [15:8] of the SPI Baud Rate Generator; and reading SPIBRL returns bits [7:0] of the SPI Baud Rate Counter. The Baud Rate Counter High and Low byte values are not buffered.

**Caution:** *Exercise caution if reading the values while the BRG is counting.*

NUMBITS[2:0]—Number of Data Bits Per Character to Transfer

This field contains the number of bits to shift for each character transfer. For information on valid bit positions when the character length is less than 8-bits, see SPI Data Register description.

000 = 8 bits 001 = 1 bit 010 = 2 bits 011 = 3 bits 100 = 4 bits 101 = 5 bits 110 = 6 bits 111 = 7 bits

0101 = ADC Analog Inputs 0-5 updated. 0110 = ADC Analog Inputs 0-6 updated. 0111 = ADC Analog Inputs 0-7 updated. 1000 = ADC Analog Inputs 0-8 updated. 1001 = ADC Analog Inputs 0-9 updated. 1010 = ADC Analog Inputs 0-10 updated. 1011 = ADC Analog Inputs 0-11 updated. 1100-1111 = Reserved.

# DMA Status Register

The DMA Status register (Table 85 on page 173) indicates the DMA channel that generated the interrupt and the ADC Analog Input that is currently undergoing conversion. Reads from this register reset the Interrupt Request Indicator bits (IRQA, IRQ1, and IRQ0) to 0. Therefore, software interrupt service routines that read this register must process all three interrupt sources from the DMA.

| BITS  | 7         | 6    | 5 | 4 | 3        | 2    | 1    | 0    |  |

|-------|-----------|------|---|---|----------|------|------|------|--|

| FIELD | CADC[3:0] |      |   |   | Reserved | IRQA | IRQ1 | IRQ0 |  |

| RESET |           | 0    |   |   |          |      |      |      |  |

| R/W   |           | R    |   |   |          |      |      |      |  |

| ADDR  |           | FBFH |   |   |          |      |      |      |  |

#### Table 85. DMA\_ADC Status Register (DMAA\_STAT)

CADC[3:0]—Current ADC Analog Input

This field identifies the Analog Input that the ADC is currently converting.

Reserved

This bit is reserved and must be 0.

IRQA—DMA\_ADC Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

$0 = DMA\_ADC$  is not the source of the interrupt from the DMA Controller.

1 = DMA\_ADC completed transfer of data from the last ADC Analog Input and generated an interrupt.

IRQ1—DMA1 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

0 = DMA1 is not the source of the interrupt from the DMA Controller.

1 = DMA1 completed transfer of data to/from the End Address and generated an interrupt.

IRQ0—DMA0 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

# **Analog-to-Digital Converter**

# **Overview**

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- 12 analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Internal voltage reference generator

- Direct Memory Access (DMA) controller can automatically initiate data conversion and transfer of the data from 1 to 12 of the analog inputs

# Architecture

Figure 34 displays the three major functional blocks (converter, analog multiplexer, and voltage reference generator) of the ADC. The ADC converts an analog input signal to its digital representation. The 12-input analog multiplexer selects one of the 12 analog input sources. The ADC requires an input reference voltage for the conversion. The voltage reference for the conversion may be input through the external VREF pin or generated internally by the voltage reference generator.

# **Flash Sector Protect Register**

The Flash Sector Protect register (Table 95) protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect register shares its Register File address with the Page Select register. The Flash Sector protect register can be accessed only after writing the Flash Control register with 5EH.

User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code).

Table 95. Flash Sector Protect Register (FPROT)

| BITS      | 7              | 6              | 5            | 4              | 3             | 2              | 1              | 0     |  |

|-----------|----------------|----------------|--------------|----------------|---------------|----------------|----------------|-------|--|

| FIELD     | SECT7          | SECT6          | SECT5        | SECT4          | SECT3         | SECT2          | SECT1          | SECT0 |  |

| RESET     |                | 0              |              |                |               |                |                |       |  |

| R/W       | R/W1           |                |              |                |               |                |                |       |  |

| ADDR      | FF9H           |                |              |                |               |                |                |       |  |

| Note: R/W | 1 = Register i | s accessible f | or Read oper | ations. Regist | er can be wri | tten to 1 only | (via user code | e).   |  |

SECT*n*—Sector Protect

0 = Sector *n* can be programmed or erased from user code.

1 =Sector *n* is protected and cannot be programmed or erased from user code.

\* User code can only write bits from 0 to 1.

# Flash Frequency High and Low Byte Registers

The Flash Frequency High and Low Byte registers (Table 96 and Table 97) combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit Flash Frequency registers must be written with the system clock frequency in kHz for Program and Erase operations. Calculate the Flash Frequency value using the following equation:

$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$

Caution: Flash programming and erasure is not supported for system clock frequencies below 20 kHz, above 20 MHz, or outside of the valid operating frequency range for the device. The Flash Frequency High and Low Byte registers must be loaded with the correct value to insure proper program and erase times.

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of putting the device back into normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the device is not in DEBUG mode, the address and data values are discarded. If the Read Protect Option Bit is enabled, then only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

• **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1-256 bytes at a time (256 bytes can be read by setting size to zero). If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

```

| y | 219 |

|---|-----|

|---|-----|

|                  |                                            | T <sub>A</sub> = -40 ° | T <sub>A</sub> = –40 °C to 125 °C |         |       |                                                             |

|------------------|--------------------------------------------|------------------------|-----------------------------------|---------|-------|-------------------------------------------------------------|

| Symbol           | Parameter                                  | Minimum                | Typical                           | Maximum | Units | Conditions                                                  |

| I <sub>DDS</sub> | Stop Mode Supply<br>Current                | _                      | 520                               | 700     | μΑ    | V <sub>DD</sub> = 3.6 V, VBO and WDT<br>Enabled             |

|                  | (See Figure 47 and                         |                        |                                   | 650     |       | V <sub>DD</sub> = 3.3 V                                     |

|                  | Figure 48) GPIO pins configured as outputs | _                      | 10                                | 25      | μΑ    | $V_{DD}$ = 3.6 V, $T_A$ = 0 to 70 °C VBO                    |

|                  |                                            |                        |                                   |         |       | Disabled                                                    |

|                  |                                            |                        |                                   | 20      |       | WDT                                                         |

|                  |                                            |                        |                                   |         |       | Enabled<br>V <sub>DD</sub> = 3.3 V                          |

|                  |                                            | -                      |                                   | 80      | μΑ    | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = −40 to<br>+105 °C |

|                  |                                            |                        |                                   | 70      |       | VBO                                                         |

|                  |                                            |                        |                                   | 70      |       | Disabled<br>WDT                                             |

|                  |                                            |                        |                                   |         |       | Enabled<br>V <sub>DD</sub> = 3.3 V                          |

|                  |                                            | _                      |                                   | 250     | μΑ    | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = -40 to<br>+125 °C |

|                  |                                            |                        |                                   |         |       | VBO                                                         |

|                  |                                            |                        |                                   | 150     |       | Disabled                                                    |

|                  |                                            |                        |                                   |         |       | WDT                                                         |

|                  |                                            |                        |                                   |         |       | V <sub>DD</sub> = 3.3 V                                     |

# Table 106. DC Characteristics (Continued)

<sup>1</sup>This condition excludes all pins that have on-chip pull-ups, when driven Low.

<sup>2</sup>These values are provided for design guidance only and are not tested in production.

zilog 224

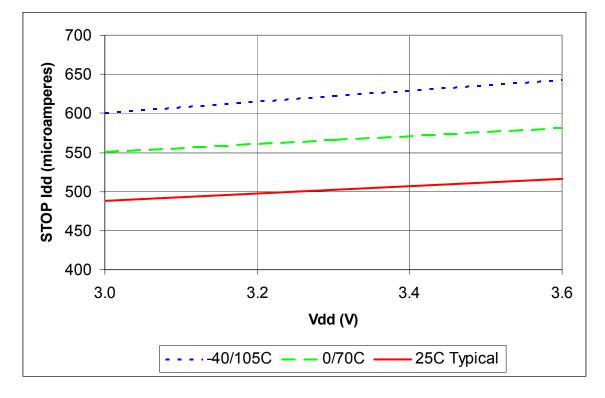

Figure 47 displays the maximum current consumption in STOP mode with the VBO and Watchdog Timer enabled versus the power supply voltage. All GPIO pins are configured as outputs and driven High.

# Figure 47. Maximum STOP Mode Idd with VBO enabled versus Power Supply Voltage

# 236

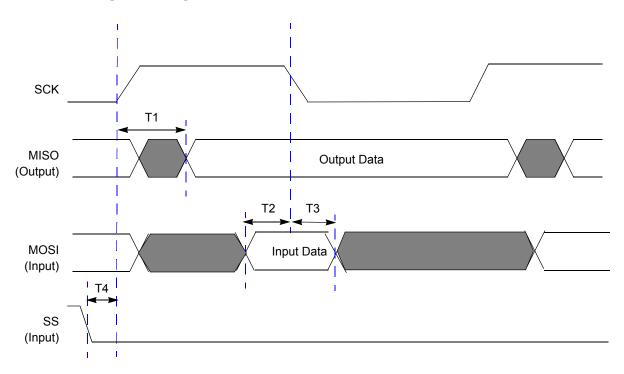

# **SPI Slave Mode Timing**

Figure 54 and Table 118 provide timing information for the SPI slave mode pins. Timing is shown with SCK rising edge used to source MISO output data, SCK falling edge used to sample MOSI input data.

# Figure 54. SPI Slave Mode Timing

#### Table 118. SPI Slave Mode Timing

|                |                                                | Delay (ns)        |                                |  |  |

|----------------|------------------------------------------------|-------------------|--------------------------------|--|--|

| Parameter      | Abbreviation                                   | Minimum           | Maximum                        |  |  |

| SPI Slave      |                                                |                   |                                |  |  |

| T <sub>1</sub> | SCK (transmit edge) to MISO output Valid Delay | 2 * Xin<br>period | 3 * Xin<br>period +<br>20 nsec |  |  |

| T <sub>2</sub> | MOSI input to SCK (receive edge) Setup Time    | 0                 |                                |  |  |

| T <sub>3</sub> | MOSI input to SCK (receive edge) Hold Time     | 3 * Xin<br>period |                                |  |  |

| T <sub>4</sub> | SS input assertion to SCK setup                | 1 * Xin<br>period |                                |  |  |