#### Zilog - Z8F6421AN020EC Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LQFP                                                   |

| Supplier Device Package    | 44-LQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6421an020ec |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### V

#### **Use of All Uppercase Letters**

The use of all uppercase letters designates the names of states, modes, and commands.

- Example 1: The bus is considered BUSY after the Start condition.

- Example 2: A START command triggers the processing of the initialization sequence.

- Example 3: STOP mode.

#### **Bit Numbering**

Bits are numbered from 0 to n-1 where n indicates the total number of bits. For example, the 8 bits of a register are numbered from 0 to 7.

## Safeguards

It is important that you understand the following safety terms, which are defined here.

Indicates a procedure or file may become corrupted if you do not follow directions.

# zilog

## Table 3. Signal Descriptions (Continued)

| Signal<br>Mnemonic          | I/O | Description                                                                                                                                                                                                                                                                                            |

|-----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK                         | I/O | SPI Serial Clock. The SPI master supplies this pin. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI master, this pin is an output. If the Z8 Encore! XP 64K Series Flash Microcontrollers is the SPI slave, this pin is an input. It is multiplexed with a general-purpose I/O pin.  |

| MOSI                        | I/O | Master-Out/Slave-In. This signal is the data output from the SPI master device and the data input to the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                                           |

| MISO                        | I/O | Master-In/Slave-Out. This pin is the data input to the SPI master device and the data output from the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                                              |

| UART Controlle              | ers |                                                                                                                                                                                                                                                                                                        |

| TXD0 / TXD1                 | 0   | Transmit Data. These signals are the transmit outputs from the UARTs. The TXD signals are multiplexed with general-purpose I/O pins.                                                                                                                                                                   |

| RXD0 / RXD1                 | Ι   | Receive Data. These signals are the receiver inputs for the UARTs and IrDAs. The RXD signals are multiplexed with general-purpose I/O pins.                                                                                                                                                            |

| CTS0 / CTS1                 | Ι   | Clear To Send. These signals are control inputs for the UARTs. The $\overline{\text{CTS}}$ signals are multiplexed with general-purpose I/O pins.                                                                                                                                                      |

| DE0 / DE1                   | 0   | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the Transmit Empty (TXE) bit in the UART Status 0 register. The DE signal may be used to ensure an external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                      |     |                                                                                                                                                                                                                                                                                                        |

| T0OUT/T1OUT/<br>T2OUT/T3OUT | 0   | Timer Output 0-3. These signals are output pins from the timers. The Timer Output signals are multiplexed with general-purpose I/O pins. T3OUT is not available in 44-pin package devices.                                                                                                             |

| T0IN/T1IN/<br>T2IN/T3IN     | Ι   | Timer Input 0-3. These signals are used as the capture, gating and counter inputs. The Timer Input signals are multiplexed with general-purpose I/O pins. T3IN is not available in 44-pin package devices.                                                                                             |

| Analog                      |     |                                                                                                                                                                                                                                                                                                        |

| ANA[11:0]                   | Ι   | Analog Input. These signals are inputs to the ADC. The ADC analog inputs are multiplexed with general-purpose I/O pins.                                                                                                                                                                                |

| VREF                        | Ι   | Analog-to-Digital converter reference voltage input. The VREF pin must be left unconnected (or capacitively coupled to analog ground) if the internal voltage reference is selected as the ADC reference voltage.                                                                                      |

| Oscillators                 |     |                                                                                                                                                                                                                                                                                                        |

15

AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A–H Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A–H Output Control Sub-Registers

The Port A–H Output Control sub-register (Table 18) is accessed through the Port A–H Control register by writing 03H to the Port A–H Address register. Setting the bits in the Port A–H Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

#### Table 18. Port A-H Output Control Sub-Registers

| BITS  | 7      | 6             | 5           | 4             | 3             | 2            | 1            | 0      |  |  |

|-------|--------|---------------|-------------|---------------|---------------|--------------|--------------|--------|--|--|

| FIELD | POC7   | POC6          | POC5        | POC4          | POC3          | POC2         | POC1         | POC0   |  |  |

| RESET |        | 0             |             |               |               |              |              |        |  |  |

| R/W   |        | R/W           |             |               |               |              |              |        |  |  |

| ADDR  | lf 03F | l in Port A–ł | H Address R | egister, acce | essible throu | igh Port A–⊦ | I Control Re | gister |  |  |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and disables the drains if set to 1.

0 = The drains are enabled for any output mode.

1 = The drain of the associated pin is disabled (open-drain mode).

#### Port A-H High Drive Enable Sub-Registers

The Port A–H High Drive Enable sub-register (Table 19) is accessed through the Port A–H Control register by writing 04H to the Port A–H Address register. Setting the bits in the Port A–H High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–H High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

| Priority | Program Memory<br>Vector Address | Interrupt Source                                 |

|----------|----------------------------------|--------------------------------------------------|

| Highest  | 0002H                            | Reset (not an interrupt)                         |

|          | 0004H                            | Watchdog Timer (see Watchdog Timer on page 97)   |

|          | 0006H                            | Illegal Instruction Trap (not an interrupt)      |

|          | 0008H                            | Timer 2                                          |

|          | 000AH                            | Timer 1                                          |

|          | 000CH                            | Timer 0                                          |

|          | 000EH                            | UART 0 receiver                                  |

|          | 0010H                            | UART 0 transmitter                               |

|          | 0012H                            | I <sup>2</sup> C                                 |

|          | 0014H                            | SPI                                              |

|          | 0016H                            | ADC                                              |

|          | 0018H                            | Port A7 or Port D7, rising or falling input edge |

|          | 001AH                            | Port A6 or Port D6, rising or falling input edge |

|          | 001CH                            | Port A5 or Port D5, rising or falling input edge |

|          | 001EH                            | Port A4 or Port D4, rising or falling input edge |

|          | 0020H                            | Port A3 or Port D3, rising or falling input edge |

|          | 0022H                            | Port A2 or Port D2, rising or falling input edge |

|          | 0024H                            | Port A1 or Port D1, rising or falling input edge |

|          | 0026H                            | Port A0 or Port D0, rising or falling input edge |

|          | 0028H                            | Timer 3 (not available in 44-pin packages)       |

|          | 002AH                            | UART 1 receiver                                  |

|          | 002CH                            | UART 1 transmitter                               |

|          | 002EH                            | DMA                                              |

|          | 0030H                            | Port C3, both input edges                        |

|          | 0032H                            | Port C2, both input edges                        |

|          | 0034H                            | Port C1, both input edges                        |

| Lowest   | 0036H                            | Port C0, both input edges                        |

## Table 23. Interrupt Vectors in Order of Priority

# Zilog <sub>74</sub>

where *x* indicates the specific GPIO Port C pin number (0 through 3).

#### **IRQ0 Enable High and Low Bit Registers**

The IRQ0 Enable High and Low Bit registers (see Table 28 and Table 29 on page 75) form a priority encoded enabling for interrupts in the Interrupt Request 0 register. Priority is generated by setting bits in each register. Table 27 describes the priority control for IRQ0.

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

#### Table 27. IRQ0 Enable and Priority Encoding

Note: where x indicates the register bits from 0 through 7.

#### Table 28. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7     | 6     | 5            | 4             | 3      | 2      | 1      | 0      |  |

|-------|-------|-------|--------------|---------------|--------|--------|--------|--------|--|

| FIELD | T2ENH | T1ENH | <b>T0ENH</b> | <b>U0RENH</b> | U0TENH | I2CENH | SPIENH | ADCENH |  |

| RESET |       | 0     |              |               |        |        |        |        |  |

| R/W   |       | R/W   |              |               |        |        |        |        |  |

| ADDR  |       |       |              | FC            | 1H     |        |        |        |  |

T2ENH—Timer 2 Interrupt Request Enable High Bit T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit I2CENH—I<sup>2</sup>C Interrupt Request Enable High Bit SPIENH—SPI Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

## Table 42. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7 | 6   | 5 | 4          | 3          | 2 | 1 | 0 |  |

|-------|---|-----|---|------------|------------|---|---|---|--|

| FIELD |   | TRL |   |            |            |   |   |   |  |

| RESET |   | 1   |   |            |            |   |   |   |  |

| R/W   |   | R/W |   |            |            |   |   |   |  |

| ADDR  |   |     | F | 03H, F0BH, | F13H, F1BI | Н |   |   |  |

TRH and TRL-Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two byte form the 16-bit Compare value.

## Timer 0-3 PWM High and Low Byte Registers

The Timer 0-3 PWM High and Low Byte (TxPWMH and TxPWML) registers (see Table 43 and Table 44 on page 92) are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the Capture and Capture/COM-PARE modes.

## Table 43. Timer 0-3 PWM High Byte Register (TxPWMH)

| BITS  | 7 | 6    | 5 | 4          | 3         | 2 | 1 | 0 |  |

|-------|---|------|---|------------|-----------|---|---|---|--|

| FIELD |   | PWMH |   |            |           |   |   |   |  |

| RESET |   | 0    |   |            |           |   |   |   |  |

| R/W   |   | R/W  |   |            |           |   |   |   |  |

| ADDR  |   |      | F | 04H, F0CH, | F14H, F1C | Н |   |   |  |

## Table 44. Timer 0-3 PWM Low Byte Register (TxPWML)

| BITS  | 7 | 6    | 5 | 4          | 3         | 2 | 1 | 0 |  |

|-------|---|------|---|------------|-----------|---|---|---|--|

| FIELD |   | PWML |   |            |           |   |   |   |  |

| RESET |   | 0    |   |            |           |   |   |   |  |

| R/W   |   | R/W  |   |            |           |   |   |   |  |

| ADDR  |   |      | F | 05H, F0DH, | F15H, F1D | Н |   |   |  |

92

110 = Divide by 64 111 = Divide by 128 TMODE—TIMER mode 000 = ONE-SHOT mode 001 = CONTINUOUS mode 010 = COUNTER mode 011 = PWM mode 100 = CAPTURE mode 101 = COMPARE mode 110 = GATED mode

111 = CAPTURE/COMPARE mode

## Watchdog Timer

#### Overview

The Watchdog Timer (WDT) helps protect against corrupt or unreliable software, power faults, and other system-level problems which may place the Z8 Encore! XP into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator.

- A selectable time-out response.

- WDT Time-out response: Reset or interrupt.

- 24-bit programmable time-out value.

## Operation

The Watchdog Timer (WDT) is a retriggerable one-shot timer that resets or interrupts the 64K Series devices when the WDT reaches its terminal count. The Watchdog Timer uses its own dedicated on-chip RC oscillator as its clock source. The Watchdog Timer has only two modes of operation—ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. An enable can be performed by executing the WDT instruction or by setting the WDT\_AO Option Bit. The WDT\_AO bit enables the Watchdog Timer to operate all the time, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the  $eZ8^{TM}$  CPU register space to set the reload value. The nominal WDT time-out period is given by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed once it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 47 provides information on approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value |          | e Time-Out Delay<br>WDT oscillator frequency) |

|------------------|------------------|----------|-----------------------------------------------|

| (Hex)            | (Decimal)        | Typical  | Description                                   |

| 000004           | 4                | 400 μs   | Minimum time-out delay                        |

| FFFFF            | 16,777,215       | 1677.5 s | Maximum time-out delay                        |

#### Table 47. Watchdog Timer Approximate Time-Out Delays

#### Watchdog Timer Refresh

When first enabled, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer then counts down to 000000H unless a WDT instruction is executed by the eZ8<sup>TM</sup> CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When the 64K Series devices are operating in DEBUG Mode (through the On-Chip Debugger), the Watchdog Timer is continuously refreshed to prevent spurious Watchdog Timer time-outs.

#### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a Reset. The WDT\_RES Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Option Bit, see Option Bits on page 195.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the 64K Series devices are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 47.

98

## UART

## **Overview**

The Universal Asynchronous Receiver/Transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two Stop bits

- Separate transmit and receive interrupts

- Framing, parity, overrun and break detection

- Separate transmit and receive enables

- 16-bit Baud Rate Generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes

- Baud Rate Generator timer mode

- Driver Enable output for external bus transceivers

#### Architecture

The UART consists of three primary functional blocks: Transmitter, Receiver, and Baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 13 on page 104 displays the UART architecture.

# zilog

#### 108

#### **Receiving Data using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the desired priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) mode functions, if desired.

- Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- Set the MULTIPROCESSOR Mode Bits, MPMD[1:0], to select the desired address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! devices without a DMA block).

- 7. Write the device address to the Address Compare Register (automatic multiprocessor modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception.

- Enable parity, if desired and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine performs the following:

- 1. Check the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. If the interrupt was caused by data available, read the data from the UART Receive Data register. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

## Table 74. I<sup>2</sup>C Baud Rate Low Byte Register (I2CBRL)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|---|-----|---|----|----|---|---|---|

| FIELD |   | BRL |   |    |    |   |   |   |

| RESET |   | FFH |   |    |    |   |   |   |

| R/W   |   | R/W |   |    |    |   |   |   |

| ADDR  |   |     |   | F5 | 4H |   |   |   |

BRL =  $I^2C$  Baud Rate Low Byte

Least significant byte, BRG[7:0], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRL register returns the current value of the  $I^2C$  Baud Rate Counter[7:0].

## I<sup>2</sup>C Diagnostic State Register

The I<sup>2</sup>C Diagnostic State register (Table 75) provides observability of internal state. This is a read only register used for I<sup>2</sup>C diagnostics and manufacturing test.

| BITS  | 7     | 6     | 5      | 4         | 3  | 2 | 1 | 0 |

|-------|-------|-------|--------|-----------|----|---|---|---|

| FIELD | SCLIN | SDAIN | STPCNT | TXRXSTATE |    |   |   |   |

| RESET | >     | K     |        | 0         |    |   |   |   |

| R/W   |       |       |        | R         |    |   |   |   |

| ADDR  |       |       |        | F5        | 5H |   |   |   |

Table 75. I<sup>2</sup>C Diagnostic State Register (I2CDST)

SCLIN—Value of Serial Clock input signal

SDAIN—Value of the Serial Data input signal

STPCNT—Value of the internal Stop Count control signal

TXRXSTATE—Value of the internal I<sup>2</sup>C state machine

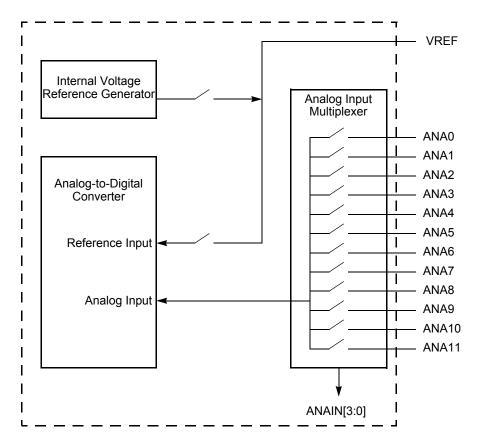

Figure 34. Analog-to-Digital Converter Block Diagram

The sigma-delta ADC architecture provides alias and image attenuation below the amplitude resolution of the ADC in the frequency range of DC to one-half the ADC clock rate (one-fourth the system clock rate). The ADC provides alias free conversion for frequencies up to one-half the ADC clock rate. Thus the sigma-delta ADC exhibits high noise immunity making it ideal for embedded applications. In addition, monotonicity (no missing codes) is guaranteed by design.

## Operation

## **Automatic Power-Down**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered-down. From this power-down state, the ADC requires 40 system clock cycles to power-up. The ADC powers up when a conversion is requested using the ADC Control register.

# zilog

## **Information Area**

Table 91 describes the 64K Series Information Area. This 512-byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into Flash Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, LDC instructions return data from the Information Area. CPU instruction fetches always comes from Flash Memory regardless of the Information Area access bit. Access to the Information Area is read-only.

| Flash Memory Address (Hex) | Function                                                                                    |

|----------------------------|---------------------------------------------------------------------------------------------|

| FE00H-FE3FH                | Reserved                                                                                    |

| FE40H-FE53H                | Part Number<br>20-character ASCII alphanumeric code<br>Left justified and filled with zeros |

| FE54H-FFFFH                | Reserved                                                                                    |

Table 91. Z8 Encore! XP 64K Series Flash Microcontrollers Information Area Map

## Operation

The Flash Controller provides the proper signals and timing for Byte Programming, Page Erase, and Mass Erase of the Flash memory. The Flash Controller contains a protection mechanism, via the Flash Control register (FCTL), to prevent accidental programming or erasure. The following subsections provide details on the various operations (Lock, Unlock, Sector Protect, Byte Programming, Page Erase, and Mass Erase).

## **On-Chip Oscillator**

#### **Overview**

The products in the 64K Series feature an on-chip oscillator for use with external crystals with frequencies from 32 kHz to 20 MHz. In addition, the oscillator can support external RC networks with oscillation frequencies up to 4 MHz or ceramic resonators with oscillation frequencies up to 20 MHz. This oscillator generates the primary system clock for the internal eZ8<sup>TM</sup> CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32 kHz–20 MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected.

When configured for use with crystal oscillators or external clock drivers, the frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock (that is, no internal clock divider). In RC operation, the system clock is driven by a clock divider (divide by 2) to ensure 50% duty cycle.

## **Operating Modes**

The 64K Series products support four different oscillator modes:

- On-chip oscillator configured for use with external RC networks (<4 MHz).

- Minimum power for use with very low frequency crystals (32 kHz to 1.0 MHz).

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 10.0 MHz).

- Maximum power for use with high frequency crystals or ceramic resonators (8.0 MHz to 20.0 MHz).

The oscillator mode is selected through user-programmable Option Bits. For more information, see Option Bits on page 195.

## **Crystal Oscillator Operation**

Figure 40 on page 212 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20 MHz. Recommended 20 MHz crystal specifications are provided in Table 104 on page 212. Resistor R1 is optional and limits total power dissipation by the crystal. The printed circuit board layout

zilog

225

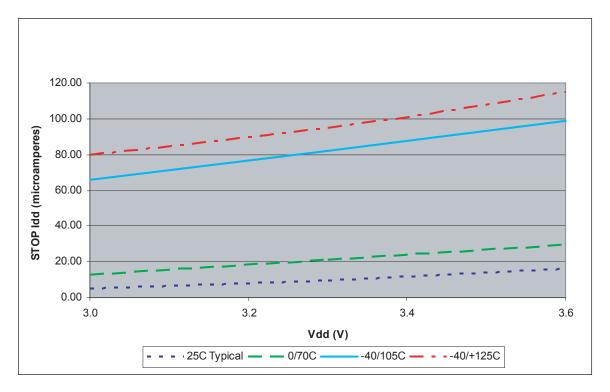

Figure 48 displays the maximum current consumption in STOP mode with the VBO disabled and Watchdog Timer enabled versus the power supply voltage. All GPIO pins are configured as outputs and driven High. Disabling the Watchdog Timer and its internal RC oscillator in STOP mode will provide some additional reduction in STOP mode current consumption. This small current reduction would be indistinguishable on the scale of Figure 48.

#### Figure 48. Maximum STOP Mode Idd with VBO Disabled versus Power Supply Voltage

### 236

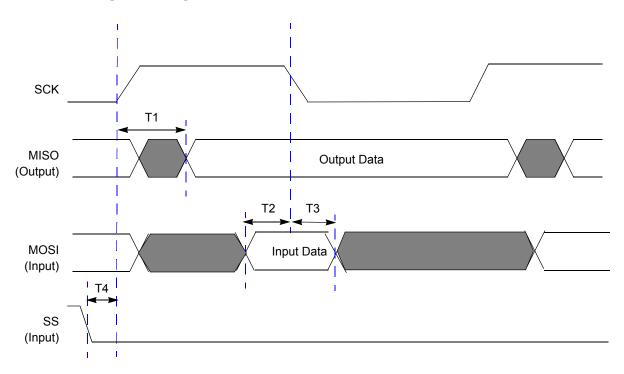

## **SPI Slave Mode Timing**

Figure 54 and Table 118 provide timing information for the SPI slave mode pins. Timing is shown with SCK rising edge used to source MISO output data, SCK falling edge used to sample MOSI input data.

## Figure 54. SPI Slave Mode Timing

#### Table 118. SPI Slave Mode Timing

|                |                                                | Delay (ns)        |                                |  |  |  |  |

|----------------|------------------------------------------------|-------------------|--------------------------------|--|--|--|--|

| Parameter      | Abbreviation                                   | Minimum           | Maximum                        |  |  |  |  |

| SPI Slave      |                                                |                   |                                |  |  |  |  |

| T <sub>1</sub> | SCK (transmit edge) to MISO output Valid Delay | 2 * Xin<br>period | 3 * Xin<br>period +<br>20 nsec |  |  |  |  |

| T <sub>2</sub> | MOSI input to SCK (receive edge) Setup Time    | 0                 |                                |  |  |  |  |

| T <sub>3</sub> | MOSI input to SCK (receive edge) Hold Time     | 3 * Xin<br>period |                                |  |  |  |  |

| T <sub>4</sub> | SS input assertion to SCK setup                | 1 * Xin<br>period |                                |  |  |  |  |

| Assembly<br>Mnemonic | Symbolic Operation                                                       | Address<br>Mode |     | On ende (e)        |   |   | Fla | ags | Fatab | lasta |                                           |                  |

|----------------------|--------------------------------------------------------------------------|-----------------|-----|--------------------|---|---|-----|-----|-------|-------|-------------------------------------------|------------------|

|                      |                                                                          | dst             | src | Opcode(s)<br>(Hex) | С | Ζ | S   | V   | D     | Н     | <ul> <li>Fetch</li> <li>Cycles</li> </ul> | Instr.<br>Cycles |

| OR dst, src          | dst $\leftarrow$ dst OR src                                              | r               | r   | 42                 | - | * | *   | 0   | -     | -     | 2                                         | 3                |

|                      |                                                                          | r               | lr  | 43                 |   |   |     |     |       |       | 2                                         | 4                |

|                      | -                                                                        | R               | R   | 44                 |   |   |     |     |       |       | 3                                         | 3                |

|                      | -                                                                        | R               | IR  | 45                 |   |   |     |     |       |       | 3                                         | 4                |

|                      | -                                                                        | R               | IM  | 46                 |   |   |     |     |       |       | 3                                         | 3                |

|                      | -                                                                        | IR              | IM  | 47                 |   |   |     |     |       |       | 3                                         | 4                |

| ORX dst, src         | $dst \gets dst \: OR \: src$                                             | ER              | ER  | 48                 | - | * | *   | 0   | -     | -     | 4                                         | 3                |

|                      | -                                                                        | ER              | IM  | 49                 |   |   |     |     |       |       | 4                                         | 3                |

| POP dst              | dst $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 1                           | R               |     | 50                 | - | - | -   | -   | -     | -     | 2                                         | 2                |

|                      |                                                                          | IR              |     | 51                 |   |   |     |     |       |       | 2                                         | 3                |

| POPX dst             | dst $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 1                           | ER              |     | D8                 | - | - | -   | -   | -     | -     | 3                                         | 2                |

| PUSH src             | $SP \leftarrow SP - 1$                                                   | R               |     | 70                 | - | - | -   | -   | -     | -     | 2                                         | 2                |

|                      | $@SP \leftarrow src$                                                     | IR              |     | 71                 |   |   |     |     |       |       | 2                                         | 3                |

|                      | -                                                                        | IM              |     | 1F 70              |   |   |     |     |       |       | 3                                         | 2                |

| PUSHX src            | $SP \leftarrow SP - 1$<br>@SP ← src                                      | ER              |     | C8                 | - | - | -   | -   | -     | -     | 3                                         | 2                |

| RCF                  | C ← 0                                                                    |                 |     | CF                 | 0 | - | -   | -   | -     | -     | 1                                         | 2                |

| RET                  | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |                 |     | AF                 | - | - | -   | -   | -     | -     | 1                                         | 4                |

| RL dst               | C ← D7D6D5D4D3D2D1D0 ←                                                   | R               |     | 90                 | * | * | *   | *   | -     | -     | 2                                         | 2                |

|                      |                                                                          | IR              |     | 91                 |   |   |     |     |       |       | 2                                         | 3                |

| RLC dst              |                                                                          | R               |     | 10                 | * | * | *   | *   | -     | -     | 2                                         | 2                |

|                      |                                                                          | IR              |     | 11                 |   |   |     |     |       |       | 2                                         | 3                |

| RR dst               | ►D7D6D5D4D3D2D1D0 ► C<br>dst                                             | R               |     | E0                 | * | * | *   | *   | -     | -     | 2                                         | 2                |

|                      |                                                                          | IR              |     | E1                 |   |   |     |     |       |       | 2                                         | 3                |

## Table 133. eZ8 CPU Instruction Summary (Continued)

| Accombly             |                                                    | Address<br>Mode |     | Openda(a)            |   |   | Fla | ags | Fatab | Inchr |                                           |                  |

|----------------------|----------------------------------------------------|-----------------|-----|----------------------|---|---|-----|-----|-------|-------|-------------------------------------------|------------------|

| Assembly<br>Mnemonic | Symbolic Operation                                 | dst             | src | - Opcode(s)<br>(Hex) | С | Ζ | S   | V   | D     | Н     | <ul> <li>Fetch</li> <li>Cycles</li> </ul> | Instr.<br>Cycles |

| RRC dst              |                                                    | R               |     | C0                   | * | * | *   | *   | -     | -     | 2                                         | 2                |

|                      | ► <u>D7 D6 D5 D4 D3 D2 D1 D0</u> ► <u>C</u><br>dst | IR              |     | C1                   | • |   |     |     |       |       | 2                                         | 3                |

| SBC dst, src         | $dst \gets dst - src - C$                          | r               | r   | 32                   | * | * | *   | *   | 1     | *     | 2                                         | 3                |

|                      | -                                                  | r               | lr  | 33                   | • |   |     |     |       |       | 2                                         | 4                |

|                      | -                                                  | R               | R   | 34                   | • |   |     |     |       |       | 3                                         | 3                |

|                      | -                                                  | R               | IR  | 35                   | • |   |     |     |       |       | 3                                         | 4                |

|                      | -                                                  | R               | IM  | 36                   | • |   |     |     |       |       | 3                                         | 3                |

|                      | -                                                  | IR              | IM  | 37                   | • |   |     |     |       |       | 3                                         | 4                |

| SBCX dst, src        | $dst \leftarrow dst - src - C$                     | ER              | ER  | 38                   | * | * | *   | *   | 1     | *     | 4                                         | 3                |

|                      | -                                                  | ER              | IM  | 39                   | • |   |     |     |       |       | 4                                         | 3                |

| SCF                  | C ← 1                                              |                 |     | DF                   | 1 | - | -   | -   | -     | -     | 1                                         | 2                |

| SRA dst              |                                                    | R               |     | D0                   | * | * | *   | 0   | -     | -     | 2                                         | 2                |

|                      | D7D6D5D4D3D2D1D0 → C<br>dst                        | IR              |     | D1                   |   |   |     |     |       |       | 2                                         | 3                |

| SRL dst              | ) → D7 D6 D5 D4 D3 D2 D1 D0 → C                    | R               |     | 1F C0                | * | * | 0   | *   | -     | -     | 3                                         | 2                |

|                      | dst                                                | IR              |     | 1F C1                | • |   |     |     |       |       | 3                                         | 3                |

| SRP src              | $RP \leftarrow src$                                |                 | IM  | 01                   | - | - | -   | -   | -     | -     | 2                                         | 2                |

| STOP                 | STOP Mode                                          |                 |     | 6F                   | - | - | -   | -   | -     | -     | 1                                         | 2                |

| SUB dst, src         | $dst \gets dst - src$                              | r               | r   | 22                   | * | * | *   | *   | 1     | *     | 2                                         | 3                |

|                      | -                                                  | r               | lr  | 23                   | • |   |     |     |       |       | 2                                         | 4                |

|                      | -                                                  | R               | R   | 24                   | • |   |     |     |       |       | 3                                         | 3                |

|                      | -                                                  | R               | IR  | 25                   | • |   |     |     |       |       | 3                                         | 4                |

|                      | -                                                  | R               | IM  | 26                   |   |   |     |     |       |       | 3                                         | 3                |

|                      | -                                                  | IR              | IM  | 27                   |   |   |     |     |       |       | 3                                         | 4                |

| SUBX dst, src        | $dst \leftarrow dst - src$                         | ER              | ER  | 28                   | * | * | *   | *   | 1     | *     | 4                                         | 3                |

|                      | -                                                  | ER              | IM  | 29                   | • |   |     |     |       |       | 4                                         | 3                |

## Table 133. eZ8 CPU Instruction Summary (Continued)