## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LQFP                                                   |

| Supplier Device Package    | 44-LQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6421an020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| · • • |   |   |   |

|-------|---|---|---|

| v     | I | I | L |

| SPI Baud Rate Generator    13      SPI Control Register Definitions    13      SPI Data Register    13      SPI Control Register    13      SPI Control Register    13      SPI Status Register    13      SPI Mode Register    14      SPI Diagnostic State Register    14      SPI Baud Rate High and Low Byte Registers    14 | 37<br>37<br>39<br>40<br>41<br>42 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| SPI Control Register    13      SPI Status Register    13      SPI Mode Register    14      SPI Diagnostic State Register    14                                                                                                                                                                                                  | 37<br>39<br>40<br>41<br>42       |

| SPI Status Register 13   SPI Mode Register 14   SPI Diagnostic State Register 14                                                                                                                                                                                                                                                 | 39<br>40<br>41<br>42             |

| SPI Mode Register 14   SPI Diagnostic State Register 14                                                                                                                                                                                                                                                                          | 40<br>41<br>42                   |

| SPI Diagnostic State Register 14                                                                                                                                                                                                                                                                                                 | 41<br>42                         |

|                                                                                                                                                                                                                                                                                                                                  | 42                               |

| SPI Baud Rate High and Low Byte Registers                                                                                                                                                                                                                                                                                        |                                  |

|                                                                                                                                                                                                                                                                                                                                  | 43                               |

| I2C Controller                                                                                                                                                                                                                                                                                                                   |                                  |

| Overview                                                                                                                                                                                                                                                                                                                         | 43                               |

| Architecture                                                                                                                                                                                                                                                                                                                     | 44                               |

| Operation                                                                                                                                                                                                                                                                                                                        | 44                               |

| SDA and SCL Signals 14                                                                                                                                                                                                                                                                                                           | 45                               |

| I <sup>2</sup> C Interrupts 14                                                                                                                                                                                                                                                                                                   |                                  |

| Software Control of I2C Transactions 14                                                                                                                                                                                                                                                                                          |                                  |

| Start and Stop Conditions 14                                                                                                                                                                                                                                                                                                     |                                  |

| Master Write and Read Transactions                                                                                                                                                                                                                                                                                               |                                  |

| Address Only Transaction with a 7-bit Address                                                                                                                                                                                                                                                                                    |                                  |

| Write Transaction with a 7-Bit Address                                                                                                                                                                                                                                                                                           |                                  |

| Address Only Transaction with a 10-bit Address                                                                                                                                                                                                                                                                                   |                                  |

| Write Transaction with a 10-Bit Address                                                                                                                                                                                                                                                                                          |                                  |

| Read Transaction with a 7-Bit Address    1      Read Transaction with a 10-Bit Address    1                                                                                                                                                                                                                                      |                                  |

| I2C Control Register Definitions                                                                                                                                                                                                                                                                                                 |                                  |

| I2C Data Register                                                                                                                                                                                                                                                                                                                |                                  |

| I2C Status Register                                                                                                                                                                                                                                                                                                              |                                  |

| I2C Control Register                                                                                                                                                                                                                                                                                                             |                                  |

| I2C Baud Rate High and Low Byte Registers                                                                                                                                                                                                                                                                                        |                                  |

| I2C Diagnostic State Register                                                                                                                                                                                                                                                                                                    | 61                               |

| I2C Diagnostic Control Register 10                                                                                                                                                                                                                                                                                               | 63                               |

| Direct Memory Access Controller                                                                                                                                                                                                                                                                                                  | 65                               |

| -                                                                                                                                                                                                                                                                                                                                | 65                               |

|                                                                                                                                                                                                                                                                                                                                  | 65                               |

| DMA0 and DMA1 Operation                                                                                                                                                                                                                                                                                                          |                                  |

| Configuring DMA0 and DMA1 for Data Transfer                                                                                                                                                                                                                                                                                      |                                  |

| DMA_ADC Operation166Configuring DMA_ADC for Data Transfer167DMA Control Register Definitions167DMAx Control Register167DMAx I/O Address Register168 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| DMAx Address High Nibble Register                                                                                                                   |

| DMAx Start/Current Address Low Byte Register                                                                                                        |

| DMAx End Address Low Byte Register                                                                                                                  |

| DMA_ADC Address Register                                                                                                                            |

| DMA_ADC Control Register 172                                                                                                                        |

| DMA Status Register 173                                                                                                                             |

| Analog-to-Digital Converter                                                                                                                         |

| Overview                                                                                                                                            |

| Architecture                                                                                                                                        |

| Operation                                                                                                                                           |

| Automatic Power-Down                                                                                                                                |

| Single-Shot Conversion                                                                                                                              |

| Continuous Conversion                                                                                                                               |

| DMA Control of the ADC 178                                                                                                                          |

| ADC Control Register Definitions 179                                                                                                                |

| ADC Control Register 179                                                                                                                            |

| ADC Data High Byte Register 180                                                                                                                     |

| ADC Data Low Bits Register 180                                                                                                                      |

| Flash Memory                                                                                                                                        |

| Overview                                                                                                                                            |

| Information Area                                                                                                                                    |

| Operation                                                                                                                                           |

| Timing Using the Flash Frequency Registers                                                                                                          |

| Flash Read Protection                                                                                                                               |

| Flash Write/Erase Protection                                                                                                                        |

| Byte Programming 187                                                                                                                                |

| Page Erase                                                                                                                                          |

| Mass Erase                                                                                                                                          |

| Flash Controller Bypass 189                                                                                                                         |

| Flash Controller Behavior in Debug Mode 189                                                                                                         |

| Flash Control Register Definitions 190                                                                                                              |

| Flash Control Register                                                                                                                              |

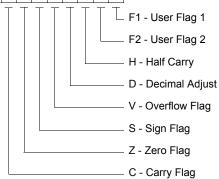

#### Flags FLAGS (FFC - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0

Register Pointer RP (FFDH - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Working Register Page Address

Working Register Group Address

### Stack Pointer High Byte SPH (FFEH - Read/Write)

D7 D6 D5 D4 D3 D2 D1 D0

Stack Pointer [15:8]

### Stack Pointer Low Byte SPL (FFFH - Read/Write)

D7 D6 D5 D4 D3 D2 D1 D0

- Stack Pointer [7:0]

#### Table 39. Timer 0-3 High Byte Register (TxH)

| BITS  | 7 6 5 4 3 2 1 0 |     |   |             |            |   |  |  |  |  |  |  |  |

|-------|-----------------|-----|---|-------------|------------|---|--|--|--|--|--|--|--|

| FIELD |                 | ТН  |   |             |            |   |  |  |  |  |  |  |  |

| RESET |                 | 0   |   |             |            |   |  |  |  |  |  |  |  |

| R/W   |                 | R/W |   |             |            |   |  |  |  |  |  |  |  |

| ADDR  |                 |     | F | F00H, F08H, | F10H, F18H | 4 |  |  |  |  |  |  |  |

#### Table 40. Timer 0-3 Low Byte Register (TxL)

| BITS  | 7 6 5 4 3 2 1 |     |   |             |              |   |  |  |  |  |  |  |

|-------|---------------|-----|---|-------------|--------------|---|--|--|--|--|--|--|

| FIELD | TL            |     |   |             |              |   |  |  |  |  |  |  |

| RESET |               | 0 1 |   |             |              |   |  |  |  |  |  |  |

| R/W   |               | R/W |   |             |              |   |  |  |  |  |  |  |

| ADDR  |               |     | F | F01H, F09H, | , F11H, F19H | 4 |  |  |  |  |  |  |

TH and TL-Timer High and Low Bytes

These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value.

#### **Timer Reload High and Low Byte Registers**

The Timer 0-3 Reload High and Low Byte (TxRH and TxRL) registers (see Table 41and Table 42 on page 92) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In COMPARE mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

| BITS  | 7 | 7 6 5 4 3 2 1 0 |   |            |            |   |  |  |  |  |  |  |  |

|-------|---|-----------------|---|------------|------------|---|--|--|--|--|--|--|--|

| FIELD |   | TRH             |   |            |            |   |  |  |  |  |  |  |  |

| RESET |   | 1               |   |            |            |   |  |  |  |  |  |  |  |

| R/W   |   | R/W             |   |            |            |   |  |  |  |  |  |  |  |

| ADDR  |   |                 | F | 02H, F0AH, | F12H, F1AI | Н |  |  |  |  |  |  |  |

| Table 11 Timer 0.2 Palead H  | igh Byte Degister (TyDU)  |

|------------------------------|---------------------------|

| Table 41. Timer 0-3 Reload H | Igii Dyle Regislei (TXRI) |

#### POR-Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event occurred. This bit is reset to 0 if a WDT timeout or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

#### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery occurred. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurred due to a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

#### WDT-Watchdog Timer Time-Out Indicator

If this bit is set to 1, a WDT time-out occurred. A Power-On Reset resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit.

#### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurred. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

Reserved

These bits are reserved and must be 0.

SM—STOP Mode Configuration Indicator

0 = Watchdog Timer and its internal RC oscillator will continue to operate in STOP Mode.

1 = Watchdog Timer and its internal RC oscillator will be disabled in STOP Mode.

#### Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers (see Table 49 on page 102 through Table 51 on page 102) form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the desired Reload Value. Reading from these registers returns the current Watchdog Timer count value.

| 9.60 | 23  | 9.73 | 1.32  | <br>9.60 | 12  | 9.60 | 0.00 |

|------|-----|------|-------|----------|-----|------|------|

| 4.80 | 47  | 4.76 | -0.83 | <br>4.80 | 24  | 4.80 | 0.00 |

| 2.40 | 93  | 2.41 | 0.23  | <br>2.40 | 48  | 2.40 | 0.00 |

| 1.20 | 186 | 1.20 | 0.23  | <br>1.20 | 96  | 1.20 | 0.00 |

| 0.60 | 373 | 0.60 | -0.04 | <br>0.60 | 192 | 0.60 | 0.00 |

| 0.30 | 746 | 0.30 | -0.04 | <br>0.30 | 384 | 0.30 | 0.00 |

#### Table 61. UART Baud Rates (Continued)

124

## **Infrared Encoder/Decoder**

#### **Overview**

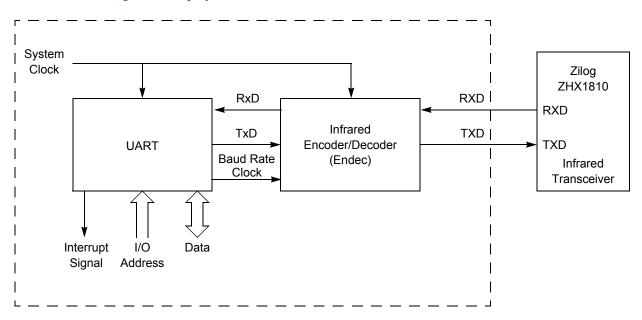

The 64K Series products contain two fully-functional, high-performance UART to Infrared Encoder/Decoders (Endecs). Each Infrared Endec is integrated with an on-chip UART to allow easy communication between the 64K Series and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers, and other infrared enabled devices.

#### Architecture

Figure 19 displays the architecture of the Infrared Endec.

Figure 19. Infrared Data Communication System Block Diagram

# zilog 1

### **SPI Control Register Definitions**

#### SPI Data Register

The SPI Data register (Table 63) stores both the outgoing (transmit) data and the incoming (receive) data. Reads from the SPI Data register always return the current contents of the 8-bit shift register. Data is shifted out starting with bit 7. The last bit received resides in bit position 0.

With the SPI configured as a Master, writing a data byte to this register initiates the data transmission. With the SPI configured as a Slave, writing a data byte to this register loads the shift register in preparation for the next data transfer with the external Master. In either the Master or Slave modes, if a transmission is already in progress, writes to this register are ignored and the Overrun error Flag, OVR, is set in the SPI Status register.

When the character length is less than 8 bits (as set by the NUMBITS field in the SPI Mode register), the transmit character must be left justified in the SPI Data register. A received character of less than 8 bits is right justified (last bit received is in bit position 0). For example, if the SPI is configured for 4-bit characters, the transmit characters must be written to SPIDATA[7:4] and the received characters are read from SPIDATA[3:0].

| BITS  | 7 6 5 4 3 2 1 0 |     |  |    |    |  |  |  |  |  |  |  |  |

|-------|-----------------|-----|--|----|----|--|--|--|--|--|--|--|--|

| FIELD | DATA            |     |  |    |    |  |  |  |  |  |  |  |  |

| RESET |                 | X   |  |    |    |  |  |  |  |  |  |  |  |

| R/W   |                 | R/W |  |    |    |  |  |  |  |  |  |  |  |

| ADDR  |                 |     |  | F6 | 0H |  |  |  |  |  |  |  |  |

#### Table 63. SPI Data Register (SPIDATA)

#### DATA—Data

Transmit and/or receive data.

#### SPI Control Register

The SPI Control register (see Table 64 on page 138) configures the SPI for transmit and receive operations.

SSIO—Slave Select I/O  $0 = \overline{SS}$  pin configured as an input.  $1 = \overline{SS}$  pin configured as an output (Master mode only). SSV—Slave Select Value If SSIO = 1 and SPI configured as a Master:  $0 = \overline{SS}$  pin driven Low (0).  $1 = \overline{SS}$  pin driven High (1).

### This bit has no effect if SSIO = 0 or SPI configured as a Slave.

#### **SPI Diagnostic State Register**

The SPI Diagnostic State register (Table 67) provides observability of internal state. This is a read only register used for SPI diagnostics.

#### Table 67. SPI Diagnostic State Register (SPIDST)

| BITS  | 7     | 6     | 5 4 3 2 1 0 |          |    |  |  |  |  |  |  |

|-------|-------|-------|-------------|----------|----|--|--|--|--|--|--|

| FIELD | SCKEN | TCKEN |             | SPISTATE |    |  |  |  |  |  |  |

| RESET |       |       |             | (        | )  |  |  |  |  |  |  |

| R/W   |       | R     |             |          |    |  |  |  |  |  |  |

| ADDR  |       |       |             | F6       | 4H |  |  |  |  |  |  |

SCKEN—Shift Clock Enable

- 0 = The internal Shift Clock Enable signal is deasserted

- 1 = The internal Shift Clock Enable signal is asserted (shift register is updates on next system clock)

TCKEN—Transmit Clock Enable

- 0 = The internal Transmit Clock Enable signal is deasserted.

- 1 = The internal Transmit Clock Enable signal is asserted. When this is asserted the serial data out is updated on the next system clock (MOSI or MISO).

SPISTATE—SPI State Machine

Defines the current state of the internal SPI State Machine.

In order for a receive (read) DMA transaction to send a Not Acknowledge on the last byte, the receive DMA must be set up to receive n-1 bytes, then software must set the NAK bit and receive the last (nth) byte directly.

#### **Start and Stop Conditions**

The master  $(I^2C)$  drives all Start and Stop signals and initiates all transactions. To start a transaction, the I<sup>2</sup>C Controller generates a START condition by pulling the SDA signal Low while SCL is High. To complete a transaction, the I<sup>2</sup>C Controller generates a Stop condition by creating a low-to-high transition of the SDA signal while the SCL signal is high. The START and STOP bits in the I<sup>2</sup>C Control register control the sending of the Start and Stop conditions. A master is also allowed to end one transaction and begin a new one by issuing a Restart. This is accomplished by setting the START bit at the end of a transaction, rather than the STOP bit. Note that the Start condition not sent until the START bit is set and data has been written to the I<sup>2</sup>C Data register.

#### Master Write and Read Transactions

The following sections provide a recommended procedure for performing I<sup>2</sup>C write and read transactions from the I<sup>2</sup>C Controller (master) to slave I<sup>2</sup>C devices. In general software should rely on the TDRE, RDRF and NCKI bits of the status register (these bits generate interrupts) to initiate software actions. When using interrupts or DMA, the TXI bit is set to start each transaction and cleared at the end of each transaction to eliminate a 'trailing' Transmit interrupt.

Caution should be used in using the ACK status bit within a transaction because it is difficult for software to tell when it is updated by hardware.

When writing data to a slave, the I<sup>2</sup>C pauses at the beginning of the Acknowledge cycle if the data register has not been written with the next value to be sent (TDRE bit in the I<sup>2</sup>C Status register = 1). In this scenario where software is not keeping up with the I<sup>2</sup>C bus (TDRE asserted longer than one byte time), the Acknowledge clock cycle for byte n is delayed until the Data register is written with byte n + 1, and appears to be grouped with the data clock cycles for byte n+1. If either the START or STOP bit is set, the I<sup>2</sup>C does not pause prior to the Acknowledge cycle because no additional data is sent.

When a Not Acknowledge condition is received during a write (either during the address or data phases), the I<sup>2</sup>C Controller generates the Not Acknowledge interrupt (NCKI = 1) and pause until either the STOP or START bit is set. Unless the Not Acknowledge was received on the last byte, the Data register will already have been written with the next address or data byte to send. In this case the FLUSH bit of the Control register should be set at the same time the STOP or START bit is set to remove the stale transmit data and enable subsequent Transmit interrupts.

When reading data from the slave, the I<sup>2</sup>C pauses after the data Acknowledge cycle until the receive interrupt is serviced and the RDRF bit of the status register is cleared by

#### Table 70. I<sup>2</sup>C Data Register (I2CDATA)

| BITS  | 7    | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |  |

|-------|------|-----|---|----|----|---|---|---|--|--|--|--|--|

| FIELD | DATA |     |   |    |    |   |   |   |  |  |  |  |  |

| RESET |      | 0   |   |    |    |   |   |   |  |  |  |  |  |

| R/W   |      | R/W |   |    |    |   |   |   |  |  |  |  |  |

| ADDR  |      |     |   | F5 | 0H |   |   |   |  |  |  |  |  |

#### I<sup>2</sup>C Status Register

The Read-only I<sup>2</sup>C Status register (Table 71) indicates the status of the I<sup>2</sup>C Controller.

| Table 71. I <sup>2</sup> C Statu | s Register (I2CSTAT) |

|----------------------------------|----------------------|

|----------------------------------|----------------------|

| BITS  | 7    | 6    | 5   | 4   | 3  | 2   | 1   | 0    |  |

|-------|------|------|-----|-----|----|-----|-----|------|--|

| FIELD | TDRE | RDRF | ACK | 10B | RD | TAS | DSS | NCKI |  |

| RESET | 1    |      | 0   |     |    |     |     |      |  |

| R/W   | R    |      |     |     |    |     |     |      |  |

| ADDR  |      | F51H |     |     |    |     |     |      |  |

#### TDRE—Transmit Data Register Empty

When the I<sup>2</sup>C Controller is enabled, this bit is 1 when the I<sup>2</sup>C Data register is empty. When this bit is set, an interrupt is generated if the TXI bit is set, except when the I<sup>2</sup>C Controller is shifting in data during the reception of a byte or when shifting an address and the RD bit is set. This bit is cleared by writing to the I2CDATA register.

#### RDRF—Receive Data Register Full

This bit is set = 1 when the I<sup>2</sup>C Controller is enabled and the I<sup>2</sup>C Controller has received a byte of data. When asserted, this bit causes the I<sup>2</sup>C Controller to generate an interrupt. This bit is cleared by reading the I<sup>2</sup>C Data register (unless the read is performed using execution of the On-Chip Debugger's Read Register command).

#### ACK—Acknowledge

This bit indicates the status of the Acknowledge for the last byte transmitted or received. When set, this bit indicates that an Acknowledge occurred for the last byte transmitted or received. This bit is cleared when IEN = 0 or when a Not Acknowledge occurred for the last byte transmitted or received. It is not reset at the beginning of each transaction and is not reset when this register is read.

159

IEN— $I^2C$  Enable 1 = The  $I^2C$  transmitter and receiver are enabled. 0 = The  $I^2C$  transmitter and receiver are disabled.

#### START-Send Start Condition

This bit sends the Start condition. Once asserted, it is cleared by the I<sup>2</sup>C Controller after it sends the START condition or if the IEN bit is deasserted. If this bit is 1, it cannot be cleared to 0 by writing to the register. After this bit is set, the Start condition is sent if there is data in the I<sup>2</sup>C Data or I<sup>2</sup>C Shift register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until the Data register is written. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a START condition after the byte shifts and the acknowledge phase completes. If the STOP bit is also set, it also waits until the STOP condition is sent before the sending the START condition.

#### STOP—Send Stop Condition

This bit causes the I<sup>2</sup>C Controller to issue a Stop condition after the byte in the I<sup>2</sup>C Shift register has completed transmission or after a byte has been received in a receive operation. Once set, this bit is reset by the I<sup>2</sup>C Controller after a Stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by writing to the register.

#### BIRQ—Baud Rate Generator Interrupt Request

This bit allows the I<sup>2</sup>C Controller to be used as an additional timer when the I<sup>2</sup>C Controller is disabled. This bit is ignored when the I<sup>2</sup>C Controller is enabled. 1 = An interrupt occurs every time the baud rate generator counts down to one. 0 = No baud rate generator interrupt occurs.

#### TXI—Enable TDRE interrupts

This bit enables the transmit interrupt when the  $I^2C$  Data register is empty (TDRE = 1).

1 = Transmit interrupt (and DMA transmit request) is enabled.

0 = Transmit interrupt (and DMA transmit request) is disabled.

#### NAK-Send NAK

This bit sends a Not Acknowledge condition after the next byte of data has been read from the  $I^2C$  slave. Once asserted, it is deasserted after a Not Acknowledge is sent or the IEN bit is deasserted. If this bit is 1, it cannot be cleared to 0 by writing to the register.

#### FLUSH-Flush Data

Setting this bit to 1 clears the I<sup>2</sup>C Data register and sets the TDRE bit to 1. This bit allows flushing of the I<sup>2</sup>C Data register when a Not Acknowledge interrupt is received after the data has been sent to the I<sup>2</sup>C Data register. Reading this bit always returns 0.

#### FILTEN—I<sup>2</sup>C Signal Filter Enable

This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.

- 1 =low-pass filters are enabled.

- 0 =low-pass filters are disabled.

If the current ADC Analog Input is not the highest numbered input to be converted, DMA ADC initiates data conversion in the next higher numbered ADC Analog Input.

#### Configuring DMA\_ADC for Data Transfer

Follow the steps below to configure and enable DMA\_ADC:

- 1. Write the DMA\_ADC Address register with the 7 most-significant bits of the Register File address for data transfers.

- 2. Write to the DMA\_ADC Control register to complete the following:

- Enable the DMA ADC interrupt request, if desired

- Select the number of ADC Analog Inputs to convert

- Enable the DMA\_ADC channel

**Caution:** When using the DMA\_ADC to perform conversions on multiple ADC inputs, the Analog-to-Digital Converter must be configured for SINGLE-SHOT mode. If the ADC\_IN field in the DMA\_ADC Control Register is greater than 000b, the ADC must be in SINGLE-SHOT mode.

CONTINUOUS mode operation of the ADC can only be used in conjunction with DMA\_ADC if the ADC\_IN field in the DMA\_ADC Control Register is reset to 000b to enable conversion on ADC Analog Input 0 only.

#### **DMA Control Register Definitions**

#### DMAx Control Register

The DMAx Control register (see Table 77 on page 167) enables and selects the mode of operation for DMAx.

| Table 77. | . DMAx Control | Register | (DMAxCTL) |

|-----------|----------------|----------|-----------|

|-----------|----------------|----------|-----------|

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-----------------------------|---|---|---|---|---|---|

| FIELD | DEN | DEN DLE DDIR IRQEN WSEL RSS |   |   |   |   |   |   |

| RESET |     | 0                           |   |   |   |   |   |   |

| R/W   |     | R/W                         |   |   |   |   |   |   |

| ADDR  |     | FB0H, FB8H                  |   |   |   |   |   |   |

DEN—DMAx Enable

0 = DMAx is disabled and data transfer requests are disregarded.

0100 = ANA4 0101 = ANA5 0110 = ANA6 0111 = ANA7 1000 = ANA8 1001 = ANA9 1010 = ANA10 1011 = ANA1111XX = Reserved.

#### ADC Data High Byte Register

The ADC Data High Byte register (Table 87) contains the upper eight bits of the 10-bit ADC output. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

| Table 87. | ADC Data | High | Byte | Register | (ADCD | _H) |

|-----------|----------|------|------|----------|-------|-----|

|-----------|----------|------|------|----------|-------|-----|

| BITS  | 7      | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|------|---|---|---|---|---|---|

| FIELD | ADCD_H |      |   |   |   |   |   |   |

| RESET | X      |      |   |   |   |   |   |   |

| R/W   |        | R    |   |   |   |   |   |   |

| ADDR  |        | F72H |   |   |   |   |   |   |

#### ADCD\_H—ADC Data High Byte

This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the last conversion output is held in this register. These bits are undefined after a Reset.

#### ADC Data Low Bits Register

The ADC Data Low Bits register (Table 88) contains the lower two bits of the conversion value. The data in the ADC Data Low Bits register is latched each time the ADC Data High Byte register is read. Reading this register always returns the lower two bits of the conversion last read into the ADC High Byte register. Access to the ADC Data Low Bits register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

## zilog

- 3. Write the first unlock command 73H to the Flash Control register.

- 4. Write the second unlock command 8CH to the Flash Control register.

- 5. Re-write the page written in step 2 to the Page Select register.

#### **Flash Sector Protection**

The Flash Sector Protect register can be configured to prevent sectors from being programmed or erased. Once a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect register is cleared after reset and any previously written protection values is lost. User code must write this register in their initialization routine if they want to enable sector protection.

The Flash Sector Protect register shares its Register File address with the Page Select register. The Flash Sector Protect register is accessed by writing the Flash Control register with 5EH. Once the Flash Sector Protect register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect register, bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control register de-selects the Flash Sector Protect register and re-enables access to the Page Select register.

Follow the steps below to setup the Flash Sector Protect register from user code:

- 1. Write 00H to the Flash Control register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control register to select the Flash Sector Protect register.

- 3. Read and/or write the Flash Sector Protect register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control register to return the Flash Controller to its reset state.

#### Flash Write Protection Option Bit

The Flash Write Protect option bit can be enabled to block all program and erase operations from user code. For more information, see Option Bits on page 195.

#### Byte Programming

When the Flash Controller is unlocked, writes to Flash Memory from user code will program a byte into the Flash if the address is located in the unlocked page. An erased Flash byte contains all ones (FFH). The programming operation can only be used to change bits from one to zero. To change a Flash bit (or multiple bits) from zero to one requires a Page Erase or Mass Erase operation.

Byte Programming can be accomplished using the eZ8 CPU's LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to  $eZ8^{TM}$  CPU Core User Manual (UM0128).

# zilog

#### 226

#### **On-Chip Peripheral AC and DC Electrical Characteristics**

#### $T_A = -40 \ ^{\circ}C \ to \ 125 \ ^{\circ}C$ Minimum Typical<sup>1</sup> Symbol Parameter Maximum Units Conditions V<sub>POR</sub> Power-On Reset 2.40 2.70 2.90 V $V_{DD} = V_{POR}$ Voltage Threshold Voltage Brownout Reset $V_{DD} = V_{VBO}$ V<sub>VBO</sub> 2.30 2.60 2.85 V Voltage Threshold $V_{\text{POR}}$ to $V_{\text{VBO}}$ 50 100 mV hysteresis Starting V<sub>DD</sub> voltage to ensure valid Power-On $V_{SS}$ V \_ Reset. T<sub>ANA</sub> Power-On Reset Analog 50 V<sub>DD</sub> > V<sub>POR</sub>; T<sub>POR</sub> Digital μS \_ Reset delay follows TANA Delay Power-On Reset Digital 66 WDT Oscillator cycles T<sub>POR</sub> 6.6 ms \_ \_ (10 kHz) + 16 System Clock Delay cycles (20 MHz) Voltage Brownout Pulse $V_{DD} < V_{VBO}$ to generate a 10 T<sub>VBO</sub> \_ μS \_ **Rejection Period** Reset. Time for VDD to T<sub>RAMP</sub> 0.10 100 ms \_ transition from $V_{SS}$ to V<sub>POR</sub> to ensure valid Reset

#### Table 107. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

<sup>1</sup>Data in the typical column is from characterization at 3.3 V and 0 °C. These values are provided for design guidance only and are not tested in production.

#### Table 130. Logical Instructions (Continued)

| Mnemonic | Operands | Instruction                                       |  |

|----------|----------|---------------------------------------------------|--|

| XOR      | dst, src | Logical Exclusive OR                              |  |

| XORX     | dst, src | Logical Exclusive OR using Extended<br>Addressing |  |

Table 131. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

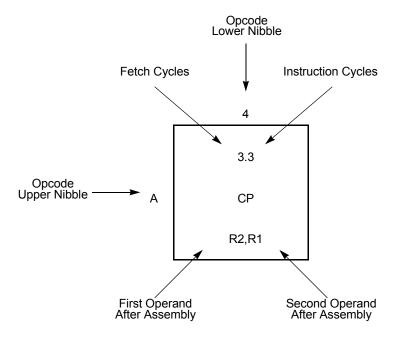

## **Opcode Maps**

A description of the opcode map data and the abbreviations are provided in Figure 59 and Table 134 on page 262. Figure 60 on page 263 and Figure 61 on page 264 provide information on each of the  $eZ8^{TM}$  CPU instructions.

Figure 59. Opcode Map Cell Description

zilog

267

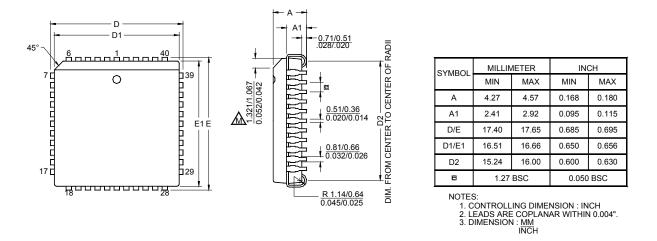

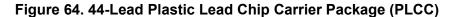

Figure 64 displays the 44-pin Plastic Lead Chip Carrier (PLCC) package available for the Z8X1621, Z8X2421, Z8X3221, Z8X4821, and Z8X6421 devices.

Figure 64 displays the 64-pin Low-Profile Quad Flat Package (LQFP) available for the Z8X1622, Z8X2422, Z8X3222, Z8X4822, and Z8X6422 devices.

Figure 65. 64-Lead Low-Profile Quad Flat Package (LQFP)