Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 29                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6421pm020sc |

# **Table of Contents**

| Manual Objectives xii                                  |

|--------------------------------------------------------|

| About This Manualxii Intended Audiencexii              |

| Manual Conventions                                     |

| Introduction 1                                         |

| Features                                               |

| Part Selection Guide                                   |

| Block Diagram                                          |

| eZ8 <sup>™</sup> CPU Features                          |

| General-Purpose Input/Output 4                         |

| Flash Controller                                       |

| UARTs                                                  |

| I <sup>2</sup> C 5                                     |

| Serial Peripheral Interface                            |

| Timers                                                 |

| Interrupt Controller                                   |

| On-Chip Debugger                                       |

| DMA Controller                                         |

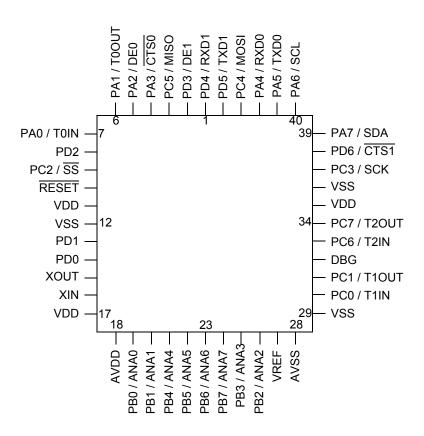

| Signal and Pin Descriptions                            |

| Overview 7                                             |

| Available Packages                                     |

| Pin Configurations                                     |

| Signal Descriptions                                    |

| Address Space 19                                       |

|                                                        |

| Overview         19           Register File         19 |

| Program Memory                                         |

| Data Memory                                            |

PS019919-1207 Table of Contents

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

| Flash Status Register  Page Select Register  Flash Sector Protect Register  Flash Frequency High and Low Byte Registers                                                                                    | 191<br>192                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Option Bits                                                                                                                                                                                                | 195                                                                |

| Overview Operation Option Bit Configuration By Reset Option Bit Address Space Flash Memory Address 0000H Flash Memory Address 0001H                                                                        | 195<br>195<br>195<br>196                                           |

| On-Chip Debugger                                                                                                                                                                                           | 199                                                                |

| Overview Architecture Operation OCD Interface DEBUG Mode OCD Data Format OCD Auto-Baud Detector/Generator OCD Serial Errors Breakpoints On-Chip Debugger Commands OCD Control Register OCD Status Register | 199<br>200<br>200<br>201<br>202<br>203<br>203<br>204<br>209<br>209 |

| On-Chip Oscillator                                                                                                                                                                                         | 211                                                                |

| Overview                                                                                                                                                                                                   | 211<br>211                                                         |

| Electrical Characteristics                                                                                                                                                                                 | 215                                                                |

| Absolute Maximum Ratings                                                                                                                                                                                   | 217<br>226                                                         |

| AC Characteristics                                                                                                                                                                                         |                                                                    |

PS019919-1207 Table of Contents

Figure 3. Z8 Encore! XP 64K Series Flash Microcontrollers in 44-Pin Plastic Leaded Chip Carrier (PLCC)

Table 7. Z8 Encore! XP 64K Series Flash Microcontrollers Register File Address Map (Continued)

| Address (Hex)    | Register Description                 | Mnemonic | Reset (Hex) | Page No |

|------------------|--------------------------------------|----------|-------------|---------|

| •                | ilable in the 44-pin packages)       |          |             |         |

| F18              | Timer 3 High Byte                    | T3H      | 00          | 90      |

| F19              | Timer 3 Low Byte                     | T3L      | 01          | 90      |

| F1A              | Timer 3 Reload High Byte             | T3RH     | FF          | 91      |

| F1B              | Timer 3 Reload Low Byte              | T3RL     | FF          | 91      |

| F1C              | Timer 3 PWM High Byte                | T3PWMH   | 00          | 92      |

| F1D              | Timer 3 PWM Low Byte                 | T3PWML   | 00          | 92      |

| F1E              | Timer 3 Control 0                    | T3CTL0   | 00          | 93      |

| F1F              | Timer 3 Control 1                    | T3CTL1   | 00          | 94      |

| 20-3F            | Reserved                             | _        | XX          |         |

| UART 0           |                                      |          |             |         |

| F40              | UART0 Transmit Data                  | U0TXD    | XX          | 114     |

|                  | UART0 Receive Data                   | U0RXD    | XX          | 115     |

| F41              | UART0 Status 0                       | U0STAT0  | 0000011Xb   | 115     |

| F42              | UART0 Control 0                      | U0CTL0   | 00          | 117     |

| F43              | UART0 Control 1                      | U0CTL1   | 00          | 117     |

| F44              | UART0 Status 1                       | U0STAT1  | 00          | 115     |

| F45              | UART0 Address Compare Register       | U0ADDR   | 00          | 120     |

| F46              | UART0 Baud Rate High Byte            | U0BRH    | FF          | 120     |

| F47              | UART0 Baud Rate Low Byte             | U0BRL    | FF          | 120     |

| UART 1           | ,                                    |          |             |         |

| F48              | UART1 Transmit Data                  | U1TXD    | XX          | 114     |

| 0                | UART1 Receive Data                   | U1RXD    | XX          | 115     |

| F49              | UART1 Status 0                       | U1STAT0  | 0000011Xb   | 115     |

| F4A              | UART1 Control 0                      | U1CTL0   | 00          | 117     |

| F4B              | UART1 Control 1                      | U1CTL1   | 00          | 117     |

| F4C              | UART1 Status 1                       | U1STAT1  | 00          | 115     |

| F4D              | UART1 Address Compare Register       | U1ADDR   | 00          | 120     |

| F4E              | UART1 Baud Rate High Byte            | U1BRH    | FF          | 120     |

| F4F              | UART1 Baud Rate Low Byte             | U1BRL    | FF          | 120     |

| I <sup>2</sup> C |                                      |          |             |         |

| F50              | I <sup>2</sup> C Data                | I2CDATA  | 00          | 156     |

| F51              | I <sup>2</sup> C Status              | I2CSTAT  | 80          | 157     |

| F52              | I <sup>2</sup> C Control             | I2CCTL   | 00          | 158     |

| F53              | I <sup>2</sup> C Baud Rate High Byte | I2CBRH   | FF F        | 160     |

| F54              | I <sup>2</sup> C Baud Rate Low Byte  | I2CBRI   | FF          | 160     |

| F55              | I <sup>2</sup> C Diagnostic State    | I2CDST   | C0          | 161     |

| F56              | I <sup>2</sup> C Diagnostic Control  | I2CDIAG  | 00          | 163     |

| F57-F5F          | Reserved                             | IZUDIAU  | XX          | 100     |

|                  |                                      | <u> </u> | ^^          |         |

|                  | ral Interface (SPI)                  |          | VV          | 407     |

| F60              | SPI Data                             | SPIDATA  | XX          | 137     |

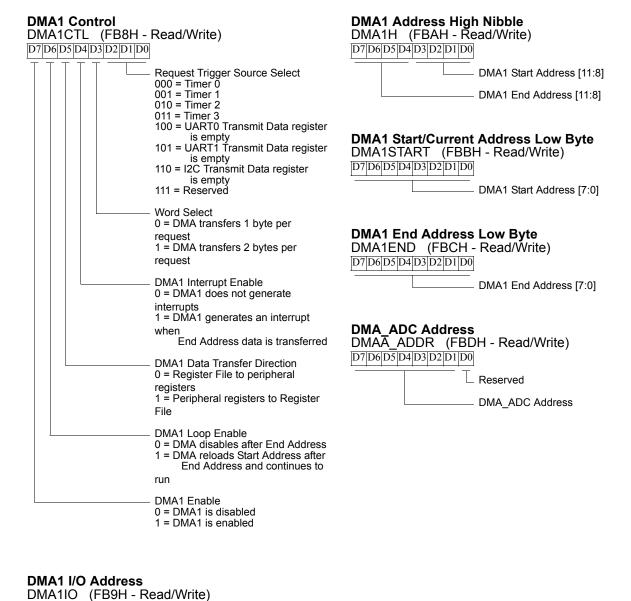

DMA1 Peripheral Register Address Low byte of on-chip peripheral control registers on Register File page FH

PS019919-1207

D7|D6|D5|D4|D3|D2|D1|D0|

**Table 23. Interrupt Vectors in Order of Priority**

| Priority | Program Memory<br>Vector Address | Interrupt Source                                 |

|----------|----------------------------------|--------------------------------------------------|

| Highest  | 0002H                            | Reset (not an interrupt)                         |

|          | 0004H                            | Watchdog Timer (see Watchdog Timer on page 97)   |

|          | 0006H                            | Illegal Instruction Trap (not an interrupt)      |

|          | H8000                            | Timer 2                                          |

|          | 000AH                            | Timer 1                                          |

|          | 000CH                            | Timer 0                                          |

|          | 000EH                            | UART 0 receiver                                  |

|          | 0010H                            | UART 0 transmitter                               |

|          | 0012H                            | I <sup>2</sup> C                                 |

|          | 0014H                            | SPI                                              |

|          | 0016H                            | ADC                                              |

|          | 0018H                            | Port A7 or Port D7, rising or falling input edge |

|          | 001AH                            | Port A6 or Port D6, rising or falling input edge |

|          | 001CH                            | Port A5 or Port D5, rising or falling input edge |

|          | 001EH                            | Port A4 or Port D4, rising or falling input edge |

|          | 0020H                            | Port A3 or Port D3, rising or falling input edge |

|          | 0022H                            | Port A2 or Port D2, rising or falling input edge |

|          | 0024H                            | Port A1 or Port D1, rising or falling input edge |

|          | 0026H                            | Port A0 or Port D0, rising or falling input edge |

|          | 0028H                            | Timer 3 (not available in 44-pin packages)       |

|          | 002AH                            | UART 1 receiver                                  |

|          | 002CH                            | UART 1 transmitter                               |

|          | 002EH                            | DMA                                              |

|          | 0030H                            | Port C3, both input edges                        |

|          | 0032H                            | Port C2, both input edges                        |

|          | 0034H                            | Port C1, both input edges                        |

| Lowest   | 0036H                            | Port C0, both input edges                        |

PS019919-1207 Interrupt Controller

C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 36) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port input pin. The Interrupt Port Select register selects between Port A and Port D for the individual interrupts.

Table 36. Interrupt Edge Select Register (IRQES)

| вітѕ  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |  |

|-------|------|------|------|------|------|------|------|------|--|--|--|--|

| FIELD | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |  |  |  |

| RESET |      | 0    |      |      |      |      |      |      |  |  |  |  |

| R/W   |      | R/W  |      |      |      |      |      |      |  |  |  |  |

| ADDR  |      |      |      | FC   | DH   |      |      |      |  |  |  |  |

IES*x*—Interrupt Edge Select *x*

The minimum pulse width should be greater than 1 system clock to guarantee capture of the edge triggered interrupt. Shorter pulses may be captured but not guaranteed.

0 = An interrupt request is generated on the falling edge of the PAx/PDx input.

1 = An interrupt request is generated on the rising edge of the PAx/PDx input. where x indicates the specific GPIO Port pin number (0 through 7).

#### **Interrupt Port Select Register**

The Port Select (IRQPS) register (Table 37) determines the port pin that generates the PAx/PDx interrupts. This register allows either Port A or Port D pins to be used as interrupts. The Interrupt Edge Select register controls the active interrupt edge.

Table 37. Interrupt Port Select Register (IRQPS)

| BITS  | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| FIELD | PAD7S | PAD6S | PAD5S | PAD4S | PAD3S | PAD2S | PAD1S | PAD0S |  |  |  |

| RESET | 0     |       |       |       |       |       |       |       |  |  |  |

| R/W   | R/W   |       |       |       |       |       |       |       |  |  |  |

| ADDR  |       |       |       | FC    | EH    |       |       |       |  |  |  |

PS019919-1207 Interrupt Controller

- ጸደ

- Select either the rising edge or falling edge of the Timer Input signal for the count.

This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function does not have to be enabled

- Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. Generally, in COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control 1 register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

#### **PWM Mode**

In PWM mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO Port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control 1 register is set to 1, the Timer Output signal begins as a High (1) and then transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control 1 register is set to 0, the Timer Output signal begins as a Low (0) and then transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM mode and initiating the PWM operation:

- 1. Write to the Timer Control 1 register to:

- Disable the timer

- Configure the timer for PWM mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control 1 register to enable the timer and initiate counting.

The PWM period is given by the following equation:

PWM Period (s) =

$$\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation must be used to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is given by:

PWM Output High Time Ratio (%) =

$$\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is given by:

PWM Output High Time Ratio (%) =

$$\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$$

#### **CAPTURE Mode**

In CAPTURE mode, the current timer count value is recorded when the desired external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control 1 register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting.

zilog

Table 39. Timer 0-3 High Byte Register (TxH)

| BITS  | 7   | 6 | 5 | 4           | 3          | 2 | 1 | 0 |  |  |  |

|-------|-----|---|---|-------------|------------|---|---|---|--|--|--|

| FIELD | TH  |   |   |             |            |   |   |   |  |  |  |

| RESET | 0   |   |   |             |            |   |   |   |  |  |  |

| R/W   | R/W |   |   |             |            |   |   |   |  |  |  |

| ADDR  |     |   | F | F00H, F08H, | F10H, F18H | 1 |   |   |  |  |  |

Table 40. Timer 0-3 Low Byte Register (TxL)

| BITS  | 7   | 6 | 5 | 4           | 3          | 2 | 1 | 0 |  |  |  |

|-------|-----|---|---|-------------|------------|---|---|---|--|--|--|

| FIELD | TL  |   |   |             |            |   |   |   |  |  |  |

| RESET | 0   |   |   |             |            |   |   |   |  |  |  |

| R/W   | R/W |   |   |             |            |   |   |   |  |  |  |

| ADDR  |     |   | F | F01H, F09H, | F11H, F19H | 1 |   |   |  |  |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value.

# Timer Reload High and Low Byte Registers

The Timer 0-3 Reload High and Low Byte (TxRH and TxRL) registers (see Table 41 and Table 42 on page 92) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In COMPARE mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

Table 41. Timer 0-3 Reload High Byte Register (TxRH)

| BITS  | 7   | 6 | 5 | 4          | 3         | 2 | 1 | 0 |  |  |  |

|-------|-----|---|---|------------|-----------|---|---|---|--|--|--|

| FIELD | TRH |   |   |            |           |   |   |   |  |  |  |

| RESET | 1   |   |   |            |           |   |   |   |  |  |  |

| R/W   | R/W |   |   |            |           |   |   |   |  |  |  |

| ADDR  |     |   | F | 02H, F0AH, | F12H, F1A | Н |   |   |  |  |  |

110 = Divide by 64

111 = Divide by 128

TMODE—TIMER mode

000 = ONE-SHOT mode

001 = CONTINUOUS mode

010 = COUNTER mode

$011 = PWM \mod e$

100 = CAPTURE mode

101 = COMPARE mode

$110 = GATED \mod e$

111 = CAPTURE/COMPARE mode

#### 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All steps of the Watchdog Timer Reload Unlock sequence must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur, unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## **Watchdog Timer Control Register Definitions**

#### **Watchdog Timer Control Register**

The Watchdog Timer Control (WDTCTL) register (Table 48) is a Read-Only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

Writing the 55H, AAH unlock sequence to the Watchdog Timer Control (WDTCTL) register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

Table 48. Watchdog Timer Control Register (WDTCTL)

| BITS  | 7                        | 6    | 5   | 4   | 3          | 3 2 1 |  |  |  |  |  |

|-------|--------------------------|------|-----|-----|------------|-------|--|--|--|--|--|

| FIELD | POR                      | STOP | WDT | EXT | Reserved S |       |  |  |  |  |  |

| RESET | See descriptions below 0 |      |     |     |            |       |  |  |  |  |  |

| R/W   |                          | R    |     |     |            |       |  |  |  |  |  |

| ADDR  |                          |      |     | FF  | 0H         |       |  |  |  |  |  |

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCDCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

PS019919-1207 Watchdog Timer

## Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver via the TXD pin. Likewise, data received from the infrared transceiver is passed to the Infrared Endec via the RXD pin, decoded by the Infrared Endec, and then passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 Kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

#### **Transmitting IrDA Data**

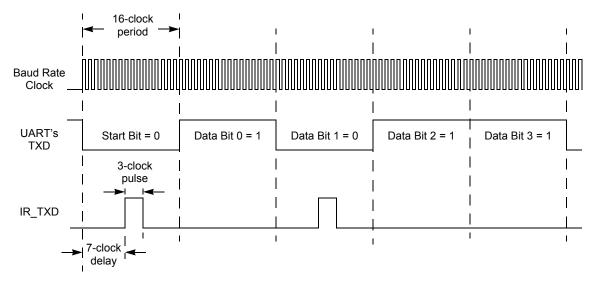

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clock wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 20 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the 64K Series products while the IR TXD signal is output through the TXD pin.

Figure 20. Infrared Data Transmission

PS019919-1207 Infrared Encoder/Decoder

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register.

- 8. After one bit of address is shifted out by the SDA signal, the Transmit interrupt is asserted

- 9. Software responds by writing the second byte of address into the contents of the I<sup>2</sup>C Data register.

- 10. The I<sup>2</sup>C Controller shifts the rest of the first byte of address and write bit out the SDA signal.

- 11. If the I<sup>2</sup>C slave sends an acknowledge by pulling the SDA signal low during the next high period of SCL the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status register. Continue with step 12.

If the slave does not acknowledge the first address byte, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status register. Software responds to the Not Acknowledge interrupt by setting the STOP and FLUSH bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore following steps).

- 12. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data register (2nd byte of address).

- 13. The I<sup>2</sup>C Controller shifts the second address byte out the SDA signal. After the first bit has been sent, the Transmit interrupt is asserted.

- 14. Software responds by setting the STOP bit in the I<sup>2</sup>C Control register. The TXI bit can be cleared at the same time.

- 15. Software polls the STOP bit of the I<sup>2</sup>C Control register. Hardware deasserts the STOP bit when the transaction is completed (STOP condition has been sent).

- 16. Software checks the ACK bit of the  $I^2C$  Status register. If the slave acknowledged, the ACK bit is = 1. If the slave does not acknowledge, the ACK bit is = 0. The NCKI interrupt do not occur because the STOP bit was set.

### Write Transaction with a 10-Bit Address

Figure 31 displays the data transfer format for a 10-bit addressed slave. Shaded regions indicate data transferred from the I<sup>2</sup>C Controller to slaves and unshaded regions indicate data transferred from the slaves to the I<sup>2</sup>C Controller.

| s | Slave Address<br>1st 7 bits | W = 0 | Α | Slave Address<br>2nd Byte | Α | Data | Α | Data | A/A | P/S |  |

|---|-----------------------------|-------|---|---------------------------|---|------|---|------|-----|-----|--|

|---|-----------------------------|-------|---|---------------------------|---|------|---|------|-----|-----|--|

Figure 31. 10-Bit Addressed Slave Data Transfer Format

PS019919-1207 I2C Controller

160

## I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers (Tables 73 and 73) combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator.

When the I<sup>2</sup>C is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the  $I^2C$  by clearing the IEN bit in the  $I^2C$  Control register to 0.

- 2. Load the desired 16-bit count value into the I<sup>2</sup>C Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the  $I^2C$  Control register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

Table 73. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH)

| BITS  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------|---|---|---|---|---|---|---|--|--|

| FIELD | BRH  |   |   |   |   |   |   |   |  |  |

| RESET | FFH  |   |   |   |   |   |   |   |  |  |

| R/W   | R/W  |   |   |   |   |   |   |   |  |  |

| ADDR  | F53H |   |   |   |   |   |   |   |  |  |

BRH =  $I^2C$  Baud Rate High Byte Most significant byte, BRG[15:8], of the  $I^2C$  Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $l^2C$  Diagnostic Control Register is set to 1, a read of the  $l^2C$  BRH register returns the current value of the  $l^2C$  Baud Rate Counter[15:8].

PS019919-1207 I2C Controller

# Table 96. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------|---|---|---|---|---|---|---|--|--|

| FIELD | FFREQH |   |   |   |   |   |   |   |  |  |

| RESET | 0      |   |   |   |   |   |   |   |  |  |

| R/W   | R/W    |   |   |   |   |   |   |   |  |  |

| ADDR  | FFAH   |   |   |   |   |   |   |   |  |  |

# Table 97. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------|---|---|---|---|---|---|---|--|

| FIELD | FFREQL |   |   |   |   |   |   |   |  |

| RESET | 0      |   |   |   |   |   |   |   |  |

| R/W   | R/W    |   |   |   |   |   |   |   |  |

| ADDR  | FFBH   |   |   |   |   |   |   |   |  |

FFREQH and FFREQL—Flash Frequency High and Low Bytes These 2 bytes, {FFREQH[7:0], FFREQL[7:0]}, contain the 16-bit Flash Frequency value.

PS019919-1207 Flash Memory

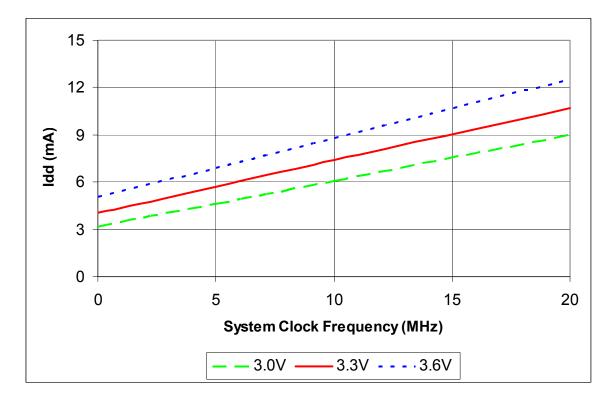

Figure 43 displays the typical active mode current consumption while operating at 25 °C versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 43. Typical Active Mode Idd Versus System Clock Frequency

PS019919-1207 Electrical Characteristics

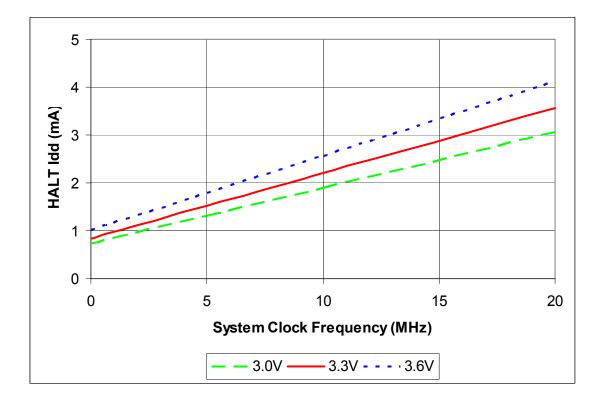

Figure 45 displays the typical current consumption in HALT mode while operating at 25 °C versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 45. Typical HALT Mode Idd Versus System Clock Frequency

PS019919-1207 Electrical Characteristics

Table 108. External RC Oscillator Electrical Characteristics and Timing

|                  |                                      | T <sub>A</sub> = -40 °         | C to 125 ° | С       |       |                    |  |

|------------------|--------------------------------------|--------------------------------|------------|---------|-------|--------------------|--|

| Symbol           | Parameter                            | Minimum Typical <sup>1</sup> M |            | Maximum | Units | Conditions         |  |

| $V_{DD}$         | Operating Voltage<br>Range           | 2.70 <sup>1</sup>              | _          | _       | V     |                    |  |

| R <sub>EXT</sub> | External Resistance from XIN to VDD  | 40                             | 45         | 200     | kΩ    | $V_{DD} = V_{VBO}$ |  |

| C <sub>EXT</sub> | External Capacitance from XIN to VSS | 0                              | 20         | 1000    | pF    |                    |  |

| F <sub>OSC</sub> | External RC Oscillation Frequency    | _                              | _          | 4       | MHz   |                    |  |

$<sup>^{</sup>m I}$ When using the external RC oscillator mode, the oscillator may stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the voltage brown-out threshold. The oscillator will resume oscillation as soon as the supply voltage exceeds 2.7 V.

Table 109. Reset and Stop Mode Recovery Pin Timing

|                    |                                                     | T <sub>A</sub> = -40 °C to 125 °C |    |         |                  |                                                           |  |

|--------------------|-----------------------------------------------------|-----------------------------------|----|---------|------------------|-----------------------------------------------------------|--|

| Symbol Parameter   |                                                     | Minimum Typical                   |    | Maximum | Units            | Conditions                                                |  |

| T <sub>RESET</sub> | RESET pin assertion to initiate a system reset.     | 4                                 | _  | _       | T <sub>CLK</sub> | Not in STOP Mode. T <sub>CLK</sub> = System Clock period. |  |

| T <sub>SMR</sub>   | Stop Mode Recovery<br>pin Pulse Rejection<br>Period | 10                                | 20 | 40      | ns               | RESET, DBG, and GPIO pins configured as SMR sources.      |  |

PS019919-1207 **Electrical Characteristics**

| Operational Description 103<br>OR 248               | push using extended addressing 248<br>PUSHX 248  |

|-----------------------------------------------------|--------------------------------------------------|

| ordering information 270                            | PWM mode 94                                      |

| ORX 248                                             | PxADDR register 61                               |

| oscillator signals 15                               | PxCTL register 62                                |

| Oscillator signals 15                               | TACTE register 02                                |

| P                                                   | Q                                                |

| p 243                                               | QFP 269                                          |

| packaging                                           |                                                  |

| LQFP                                                |                                                  |

| 44 lead 266                                         | R                                                |

| 64 lead 267                                         | R 243                                            |

| PDIP 265                                            | r 243                                            |

| PLCC                                                | RA                                               |

| 44 lead 267                                         | register address 243                             |

| 68 lead 268                                         | RCF 247                                          |

| QFP 269                                             | receive                                          |

| part number description 275                         | 10-bit data format (I2C) 154                     |

| part selection guide 2                              | 7-bit data transfer format (I2C) 153             |

| PC 244                                              | IrDA data 127                                    |

| PDIP 265                                            | receive interrupt 145                            |

| peripheral AC and DC electrical characteristics 226 | receiving UART data-interrupt-driven method 108  |

| PHASE=0 timing (SPI) 133                            | receiving UART data-polled method 107            |

| PHASE=1 timing (SPI) 134                            | register 140, 169, 243                           |

| pin characteristics 16                              | ADC control (ADCCTL) 179                         |

| PLCC                                                | ADC data high byte (ADCDH) 180                   |

| 44 lead 267                                         | ADC data low bits (ADCDL) 180                    |

| 68-lead 268                                         | baud low and high byte (I2C) 160, 161, 163       |

| polarity 243                                        | baud rate high and low byte (SPI) 142            |

| POP 248                                             | control (SPI) 137                                |

| pop using extended addressing 248                   | control, I2C 158                                 |

| POPX 248                                            | data, SPI 137                                    |

| port availability, device 57                        | DMA status (DMAA_STAT) 173                       |

| port input timing (GPIO) 232                        | DMA_ADC address 171                              |

| port output timing, GPIO 233                        | DMA_ADC control DMAACTL) 172                     |

| power supply signals 16                             | DMAx address high nibble (DMAxH) 169             |

| power-down, automatic (ADC) 176                     | DMAx control (DMAxCTL) 167                       |

| power-on and voltage brown-out 226                  | DMAx end/address low byte (DMAxEND) 170          |

| power-on reset (POR) 49                             | DMAx start/current address low byte register     |

| program control instructions 249                    | (DMAxSTART) 170                                  |

| program counter 244                                 | flash control (FCTL) 190                         |

| program memory 20                                   | flash high and low byte (FFREQH and FRE-EOL) 192 |

| PUSH 248                                            | EX.JL.J. 19.4                                    |

PS019919-1207 Index