Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6422ar020ec |

# **Table of Contents**

| Manual Objectives xii                     |

|-------------------------------------------|

| About This Manualxii Intended Audiencexii |

| Manual Conventions                        |

| Introduction 1                            |

| Features                                  |

| Part Selection Guide                      |

| Block Diagram 3                           |

| CPU and Peripheral Overview               |

| eZ8 <sup>™</sup> CPU Features             |

| General-Purpose Input/Output              |

| Flash Controller                          |

| 10-Bit Analog-to-Digital Converter        |

| UARTs                                     |

| I <sup>2</sup> C                          |

| Timers                                    |

| Interrupt Controller                      |

| Reset Controller                          |

| On-Chip Debugger                          |

| DMA Controller                            |

| Signal and Pin Descriptions               |

| Overview                                  |

| Available Packages                        |

| Pin Configurations                        |

| Signal Descriptions                       |

| Pin Characteristics                       |

| Address Space                             |

| Overview                                  |

| Register File                             |

| Program Memory                            |

| Data Memory                               |

PS019919-1207 Table of Contents

## Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

| Flash Status Register  Page Select Register  Flash Sector Protect Register  Flash Frequency High and Low Byte Registers                                                                                    | 191<br>192                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Option Bits                                                                                                                                                                                                | 195                                                                |

| Overview Operation Option Bit Configuration By Reset Option Bit Address Space Flash Memory Address 0000H Flash Memory Address 0001H                                                                        | 195<br>195<br>195<br>196                                           |

| On-Chip Debugger                                                                                                                                                                                           | 199                                                                |

| Overview Architecture Operation OCD Interface DEBUG Mode OCD Data Format OCD Auto-Baud Detector/Generator OCD Serial Errors Breakpoints On-Chip Debugger Commands OCD Control Register OCD Status Register | 199<br>200<br>200<br>201<br>202<br>203<br>203<br>204<br>209<br>209 |

| On-Chip Oscillator                                                                                                                                                                                         | 211                                                                |

| Overview                                                                                                                                                                                                   | 211<br>211                                                         |

| Electrical Characteristics                                                                                                                                                                                 | 215                                                                |

| Absolute Maximum Ratings                                                                                                                                                                                   | 217<br>226                                                         |

| AC Characteristics                                                                                                                                                                                         |                                                                    |

PS019919-1207 Table of Contents

$I^2C$

The I<sup>2</sup>C controller makes the Z8 Encore! XP compatible with the I<sup>2</sup>C protocol. The I<sup>2</sup>C controller consists of two bidirectional bus lines, a serial data (SDA) line and a serial clock (SCL) line.

#### **Serial Peripheral Interface**

The serial peripheral interface allows the Z8 Encore! XP to exchange data between other peripheral devices such as EEPROMs, A/D converters and ISDN devices. The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface.

#### **Timers**

Up to four 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in One-Shot, Continuous, Gated, Capture, Compare, Capture and Compare, and PWM modes. Only 3 timers (Timers 0-2) are available in the 44-pin packages.

#### **Interrupt Controller**

The 64K Series products support up to 24 interrupts. These interrupts consist of 12 internal and 12 GPIO pins. The interrupts have 3 levels of programmable interrupt priority.

#### **Reset Controller**

The Z8 Encore! can be reset using the RESET pin, Power-On Reset, Watchdog Timer, STOP mode exit, or Voltage Brownout (VBO) warning signal.

#### On-Chip Debugger

The Z8 Encore! XP features an integrated On-Chip Debugger. The OCD provides a rich set of debugging capabilities, such as reading and writing registers, programming the Flash, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

#### **DMA Controller**

The 64K Series features three channels of DMA. Two of the channels are for register RAM to and from I/O operations. The third channel automatically controls the transfer of data from the ADC to the memory.

PS019919-1207 Introduction

Table 7. Z8 Encore! XP 64K Series Flash Microcontrollers Register File Address Map (Continued)

| Address (Hex)    | Register Description                 | Mnemonic | Reset (Hex) | Page No |

|------------------|--------------------------------------|----------|-------------|---------|

| •                | ilable in the 44-pin packages)       |          |             |         |

| F18              | Timer 3 High Byte                    | T3H      | 00          | 90      |

| F19              | Timer 3 Low Byte                     | T3L      | 01          | 90      |

| F1A              | Timer 3 Reload High Byte             | T3RH     | FF          | 91      |

| F1B              | Timer 3 Reload Low Byte              | T3RL     | FF          | 91      |

| F1C              | Timer 3 PWM High Byte                | T3PWMH   | 00          | 92      |

| F1D              | Timer 3 PWM Low Byte                 | T3PWML   | 00          | 92      |

| F1E              | Timer 3 Control 0                    | T3CTL0   | 00          | 93      |

| F1F              | Timer 3 Control 1                    | T3CTL1   | 00          | 94      |

| 20-3F            | Reserved                             | _        | XX          |         |

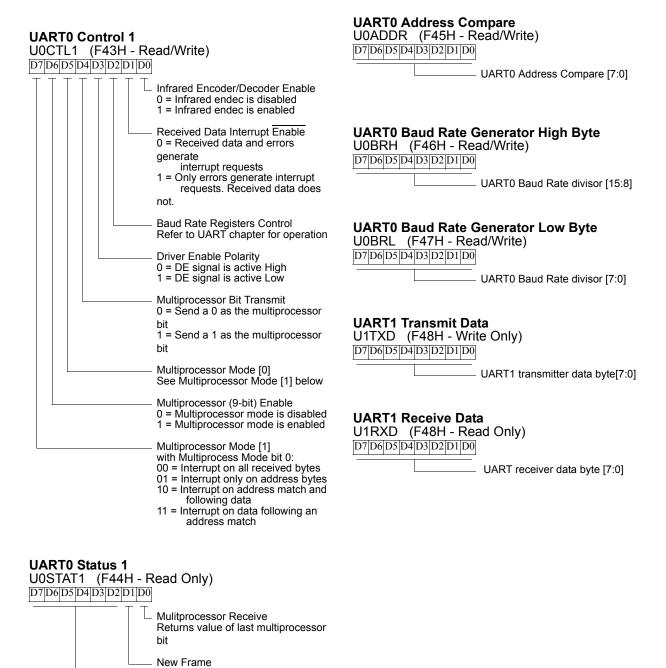

| UART 0           |                                      |          |             |         |

| F40              | UART0 Transmit Data                  | U0TXD    | XX          | 114     |

|                  | UART0 Receive Data                   | U0RXD    | XX          | 115     |

| F41              | UART0 Status 0                       | U0STAT0  | 0000011Xb   | 115     |

| F42              | UART0 Control 0                      | U0CTL0   | 00          | 117     |

| F43              | UART0 Control 1                      | U0CTL1   | 00          | 117     |

| F44              | UART0 Status 1                       | U0STAT1  | 00          | 115     |

| F45              | UART0 Address Compare Register       | U0ADDR   | 00          | 120     |

| F46              | UART0 Baud Rate High Byte            | U0BRH    | FF          | 120     |

| F47              | UART0 Baud Rate Low Byte             | U0BRL    | FF          | 120     |

| UART 1           | •                                    |          |             |         |

| F48              | UART1 Transmit Data                  | U1TXD    | XX          | 114     |

|                  | UART1 Receive Data                   | U1RXD    | XX          | 115     |

| F49              | UART1 Status 0                       | U1STAT0  | 0000011Xb   | 115     |

| F4A              | UART1 Control 0                      | U1CTL0   | 00          | 117     |

| F4B              | UART1 Control 1                      | U1CTL1   | 00          | 117     |

| F4C              | UART1 Status 1                       | U1STAT1  | 00          | 115     |

| F4D              | UART1 Address Compare Register       | U1ADDR   | 00          | 120     |

| F4E              | UART1 Baud Rate High Byte            | U1BRH    | FF          | 120     |

| F4F              | UART1 Baud Rate Low Byte             | U1BRL    | FF          | 120     |

| I <sup>2</sup> C |                                      |          |             |         |

| F50              | I <sup>2</sup> C Data                | I2CDATA  | 00          | 156     |

| F51              | I <sup>2</sup> C Status              | I2CSTAT  | 80          | 157     |

| F52              | I <sup>2</sup> C Control             | I2CCTL   | 00          | 158     |

| F53              | I <sup>2</sup> C Baud Rate High Byte | I2CBRH   | FF F        | 160     |

| F54              | I <sup>2</sup> C Baud Rate Low Byte  | I2CBRI   | FF          | 160     |

| F55              | I <sup>2</sup> C Diagnostic State    | I2CDST   | C0          | 161     |

| F56              | I <sup>2</sup> C Diagnostic Control  | I2CDIAG  | 00          | 163     |

| F57-F5F          | Reserved                             | IZUDIAU  | XX          | 100     |

|                  |                                      | <u> </u> | ^^          |         |

|                  | ral Interface (SPI)                  |          | VV          | 407     |

| F60              | SPI Data                             | SPIDATA  | XX          | 137     |

0 = Current byte is not start of frame 1 = Current byte is start of new

frame Reserved

## Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers **Product Specification**

zilog 54

#### **HALT Mode**

Execution of the eZ8 CPU's HALT instruction places the device into HALT mode. In HALT mode, the operating characteristics are:

- Primary crystal oscillator is enabled and continues to operate.

- System clock is enabled and continues to operate.

- eZ8 CPU is stopped.

- Program Counter stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate.

- The Watchdog Timer continues to operate, if enabled.

- All other on-chip peripherals continue to operate.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout Reset

- External RESET pin assertion

To minimize current in HALT mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

PS019919-1207 Low-Power Modes

PADDR[7:0]—Port Address

The Port Address selects one of the sub-registers accessible through the Port Control register.

| PADDR[7:0] | Port Control sub-register accessible using the Port A–H Control Registers     |

|------------|-------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental Port reconfiguration |

| 01H        | Data Direction                                                                |

| 02H        | Alternate Function                                                            |

| 03H        | Output Control (Open-Drain)                                                   |

| 04H        | High Drive Enable                                                             |

| 05H        | Stop Mode Recovery Source Enable                                              |

| 06H-FFH    | No function                                                                   |

#### Port A-H Control Registers

The Port A-H Control registers set the GPIO port operation. The value in the corresponding Port A–H Address register determines the control sub-registers accessible using the Port A–H Control register (Table 15).

Table 15. Port A-H Control Registers (PxCTL)

| BITS  | 7    | 6                                              | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------|------------------------------------------------|---|---|---|---|---|---|--|

| FIELD | PCTL |                                                |   |   |   |   |   |   |  |

| RESET | 00Н  |                                                |   |   |   |   |   |   |  |

| R/W   | R/W  |                                                |   |   |   |   |   |   |  |

| ADDR  |      | FD1H, FD5H, FD9H, FDDH, FE1H, FE5H, FE9H, FEDH |   |   |   |   |   |   |  |

PCTL[7:0]—Port Control

The Port Control register provides access to all sub-registers that configure the GPIO Port operation.

PS019919-1207 General-Purpose I/O AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A-H Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A-H Output Control Sub-Registers

The Port A–H Output Control sub-register (Table 18) is accessed through the Port A-H Control register by writing 03H to the Port A-H Address register. Setting the bits in the Port A–H Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

Table 18. Port A-H Output Control Sub-Registers

| BITS  | 7                                                                                 | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|-----------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| FIELD | POC7                                                                              | POC6 | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |

| RESET | 0                                                                                 |      |      |      |      |      |      |      |

| R/W   | R/W                                                                               |      |      |      |      |      |      |      |

| ADDR  | If 03H in Port A–H Address Register, accessible through Port A–H Control Register |      |      |      |      |      |      |      |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and disables the drains if set to 1.

0 = The drains are enabled for any output mode.

1 = The drain of the associated pin is disabled (open-drain mode).

#### Port A-H High Drive Enable Sub-Registers

The Port A–H High Drive Enable sub-register (Table 19) is accessed through the Port A– H Control register by writing 04H to the Port A-H Address register. Setting the bits in the Port A–H High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A-H High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

PS019919-1207 General-Purpose I/O register. The IRQE, PHASE, CLKPOL, WOR bits in the SPICTL register and the NUM-BITS field in the SPIMODE register must be set to be consistent with the other SPI devices. The STR bit in the SPICTL register may be used if desired to force a "startup" interrupt. The BIRQ bit in the SPICTL register and the SSV bit in the SPIMODE register are not used in SLAVE mode. The SPI baud rate generator is not used in SLAVE mode so the SPIBRH and SPIBRL registers need not be initialized.

If the slave has data to send to the master, the data must be written to the SPIDAT register before the transaction starts (first edge of SCK when  $\overline{SS}$  is asserted). If the SPIDAT register is not written prior to the slave transaction, the MISO pin outputs whatever value is currently in the SPIDAT register.

Due to the delay resulting from synchronization of the SPI input signals to the internal system clock, the maximum SPICLK baud rate that can be supported in SLAVE mode is the system clock frequency (XIN) divided by 8. This rate is controlled by the SPI master.

#### **Error Detection**

The SPI contains error detection logic to support SPI communication protocols and recognize when communication errors have occurred. The SPI Status register indicates when a data transmission error has been detected.

#### **Overrun (Write Collision)**

An overrun error (write collision) indicates a write to the SPI Data register was attempted while a data transfer is in progress (in either MASTER or SLAVE modes). An overrun sets the OVR bit in the SPI Status register to 1. Writing a 1 to OVR clears this error Flag. The data register is not altered when a write occurs while data transfer is in progress.

#### **Mode Fault (Multi-Master Collision)**

A mode fault indicates when more than one Master is trying to communicate at the same time (a multi-master collision). The mode fault is detected when the enabled Master's  $\overline{SS}$  pin is asserted. A mode fault sets the COL bit in the SPI Status register to 1. Writing a 1 to COL clears this error Flag.

#### **Slave Mode Abort**

In SLAVE mode of operation if the  $\overline{SS}$  pin deasserts before all bits in a character have been transferred, the transaction is aborted. When this condition occurs the ABT bit is set in the SPISTAT register as well as the IRQ bit (indicating the transaction is complete). The next time  $\overline{SS}$  asserts, the MISO pin outputs SPIDAT[7], regardless of where the previous transaction left off. Writing a 1 to ABT clears this error Flag.

#### SPI Interrupts

When SPI interrupts are enabled, the SPI generates an interrupt after character transmission/reception completes in both MASTER and SLAVE modes. A character can be

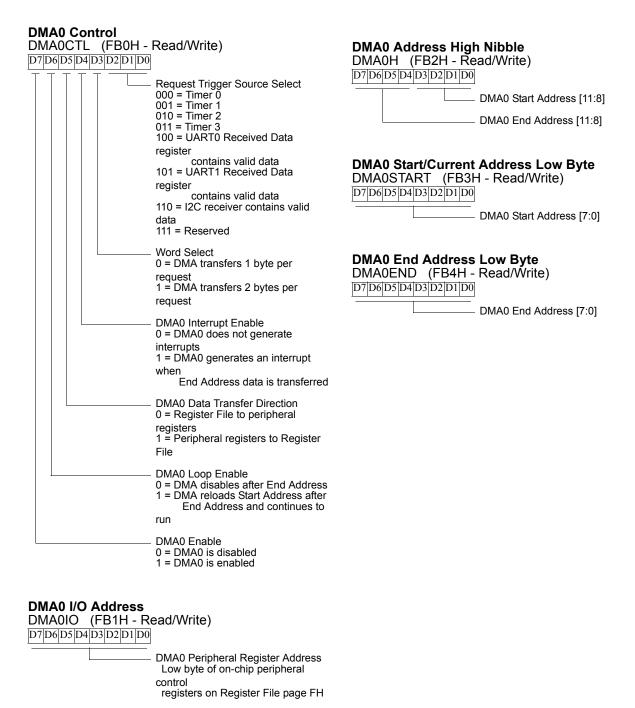

#### Configuring DMA0 and DMA1 for Data Transfer

Follow the steps below to configure and enable DMA0 or DMA1:

- 1. Write to the DMAx I/O Address register to set the Register File address identifying the on-chip peripheral control register. The upper nibble of the 12-bit address for on-chip peripheral control registers is always FH. The full address is {FH, DMAx IO[7:0]}.

- 2. Determine the 12-bit Start and End Register File addresses. The 12-bit Start Address is given by {DMAx\_H[3:0], DMA\_START[7:0]}. The 12-bit End Address is given by {DMAx\_H[7:4], DMA\_END[7:0]}.

- 3. Write the Start and End Register File address high nibbles to the DMA*x* End/Start Address High Nibble register.

- 4. Write the lower byte of the Start Address to the DMAx Start/Current Address register.

- 5. Write the lower byte of the End Address to the DMAx End Address register.

- 6. Write to the DMAx Control register to complete the following:

- Select loop or single-pass mode operation

- Select the data transfer direction (either from the Register File RAM to the onchip peripheral control register; or from the on-chip peripheral control register to the Register File RAM)

- Enable the DMAx interrupt request, if desired

- Select Word or Byte mode

- Select the DMAx request trigger

- Enable the DMAx channel

#### **DMA ADC Operation**

DMA\_ADC transfers data from the ADC to the Register File. The sequence of operations in a DMA\_ADC data transfer is:

- 1. ADC completes conversion on the current ADC input channel and signals the DMA controller that two-bytes of ADC data are ready for transfer.

- 2. DMA\_ADC requests control of the system bus (address and data) from the eZ8 CPU.

- 3. After the eZ8 CPU acknowledges the bus request, DMA\_ADC transfers the two-byte ADC output value to the Register File and then returns system bus control back to the eZ8 CPU.

- 4. If the current ADC Analog Input is the highest numbered input to be converted:

- DMA\_ADC resets the ADC Analog Input number to 0 and initiates data conversion on ADC Analog Input 0.

- If configured to generate an interrupt, DMA\_ADC sends an interrupt request to the Interrupt Controller

#### DMAA ADDR—DMA ADC Address

These bits specify the seven most-significant bits of the 12-bit Register File addresses used for storing the ADC output data. The ADC Analog Input Number defines the five least-significant bits of the Register File address. Full 12-bit address is {DMAA ADDR[7:1], 4-bit ADC Analog Input Number, 0}.

#### Reserved

This bit is reserved and must be 0.

#### DMA\_ADC Control Register

The DMA\_ADC Control register (Table 84 on page 172) enables and sets options (DMA enable and interrupt enable) for ADC operation.

Table 84. DMA\_ADC Control Register (DMAACTL)

| BITS  | 7    | 6     | 5    | 4     | 3      | 2 | 1 | 0 |  |

|-------|------|-------|------|-------|--------|---|---|---|--|

| FIELD | DAEN | IRQEN | Rese | erved | ADC_IN |   |   |   |  |

| RESET |      | 0     |      |       |        |   |   |   |  |

| R/W   |      | R/W   |      |       |        |   |   |   |  |

| ADDR  |      | FBEH  |      |       |        |   |   |   |  |

#### DAEN—DMA ADC Enable

0 = DMA ADC is disabled and the ADC Analog Input Number (ADC IN) is reset to 0.

1 = DMA ADC is enabled.

#### IRQEN—Interrupt Enable

0 = DMA ADC does not generate any interrupts.

1 = DMA\_ADC generates an interrupt after transferring data from the last ADC Analog Input specified by the ADC IN field.

#### Reserved

These bits are reserved and must be 0.

#### ADC IN—ADC Analog Input Number

These bits set the number of ADC Analog Inputs to be used in the continuous update (data conversion followed by DMA data transfer). The conversion always begins with ADC Analog Input 0 and then progresses sequentially through the other selected ADC Analog Inputs.

0000 = ADC Analog Input 0 updated.

0001 = ADC Analog Inputs 0-1 updated.

0010 = ADC Analog Inputs 0-2 updated.

0011 = ADC Analog Inputs 0-3 updated.

0100 = ADC Analog Inputs 0-4 updated.

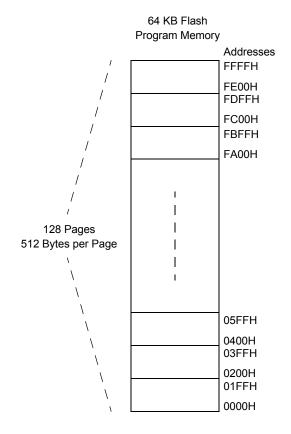

**Table 90. Flash Memory Sector Addresses**

|               | Flash Sector Address Ranges |             |             |             |             |  |  |  |  |

|---------------|-----------------------------|-------------|-------------|-------------|-------------|--|--|--|--|

| Sector Number | Z8F162x                     | Z8F242x     | Z8F322x     | Z8F482x     | Z8F642x     |  |  |  |  |

| 0             | 0000H-07FFH                 | 0000H-0FFFH | 0000H-0FFFH | 0000H-1FFFH | 0000H-1FFFH |  |  |  |  |

| 1             | 0800H-0FFFH                 | 1000H-1FFFH | 1000H-1FFFH | 2000H-3FFFH | 2000H-3FFFH |  |  |  |  |

| 2             | 1000H-17FFH                 | 2000H-2FFFH | 2000H-2FFFH | 4000H-5FFFH | 4000H-5FFFH |  |  |  |  |

| 3             | 1800H-1FFFH                 | 3000H-3FFFH | 3000H-3FFFH | 6000H-7FFFH | 6000H-7FFFH |  |  |  |  |

| 4             | 2000H-27FFH                 | 4000H-4FFFH | 4000H-4FFFH | 8000H-9FFFH | 8000H-9FFFH |  |  |  |  |

| 5             | 2800H-2FFFH                 | 5000H-5FFFH | 5000H-5FFFH | A000H-BFFFH | A000H-BFFFH |  |  |  |  |

| 6             | 3000H-37FFH                 | N/A         | 6000H-6FFFH | N/A         | C000H-DFFFH |  |  |  |  |

| 7             | 3800H-3FFFH                 | N/A         | 7000H-7FFFH | N/A         | E000H-FFFFH |  |  |  |  |

Figure 35. Flash Memory Arrangement

PS019919-1207 Flash Memory

# Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

zilog

194

PS019919-1207 Flash Memory

#### Flash Memory Address 0000H

Table 98. Flash Option Bits At Flash Memory Address 0000H

| BITS        | 7                                               | 6      | 5            | 4 | 3      | 2  | 1        | 0   |  |

|-------------|-------------------------------------------------|--------|--------------|---|--------|----|----------|-----|--|

| FIELD       | WDT_RE<br>S                                     | WDT_AO | OSC_SEL[1:0] |   | VBO_AO | RP | Reserved | FWP |  |

| RESET       | Ü                                               |        |              |   |        |    |          |     |  |

| R/W         | R/W                                             |        |              |   |        |    |          |     |  |

| ADDR        | Program Memory 0000H                            |        |              |   |        |    |          |     |  |

| Note: U = □ | Note: U = Unchanged by Reset. R/W = Read/Write. |        |              |   |        |    |          |     |  |

#### WDT RES—Watchdog Timer Reset

- 0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

- 1 = Watchdog Timer time-out causes a Short Reset. This setting is the default for unprogrammed (erased) Flash.

#### WDT AO—Watchdog Timer Always On

- 0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled except during STOP Mode (if configured to power down during STOP Mode).

- 1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

#### OSC SEL[1:0]—Oscillator Mode Selection

- 00 = On-chip oscillator configured for use with external RC networks (<4 MHz).

- 01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0 MHz).

- 10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 10.0 MHz).

- 11 = Maximum power for use with high frequency crystals (8.0 MHz to 20.0 MHz). This setting is the default for unprogrammed (erased) Flash.

#### VBO AO—Voltage Brownout Protection Always On

- 0 = Voltage Brownout Protection is disabled in STOP mode to reduce total power consumption.

- 1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

#### RP—Read Protect

0 = User program code is inaccessible. Limited control features are available through

PS019919-1207 Option Bits

## Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Product Specification

zilog

260

PS019919-1207 eZ8<sup>™</sup> CPU Instruction Set

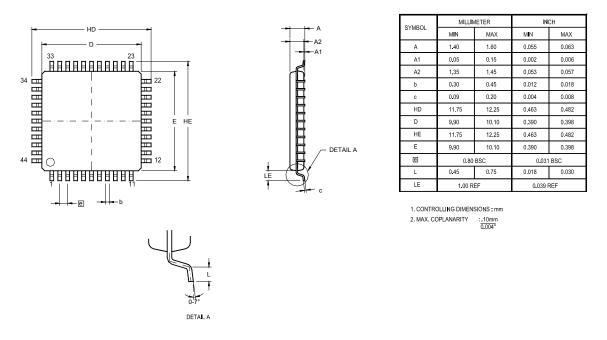

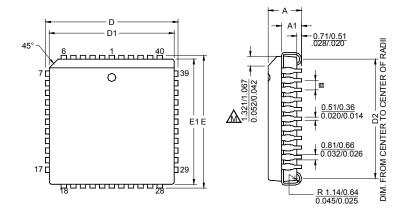

Figure 63 displays the 44-pin Low Profile Quad Flat Package (LQFP) available for the Z8X1621, Z8X2421, Z8X3221, Z8X4821, and Z8X6421 devices.

Figure 63. 44-Lead Low-Profile Quad Flat Package (LQFP)

PS019919-1207 Packaging

Figure 64 displays the 44-pin Plastic Lead Chip Carrier (PLCC) package available for the Z8X1621, Z8X2421, Z8X3221, Z8X4821, and Z8X6421 devices.

| SYMBOL  | MILLIN | METER | INCH  |       |  |

|---------|--------|-------|-------|-------|--|

| STWIBOL | MIN    | MAX   | MIN   | MAX   |  |

| А       | 4.27   | 4.57  | 0.168 | 0.180 |  |

| A1      | 2.41   | 2.92  | 0.095 | 0.115 |  |

| D/E     | 17.40  | 17.65 | 0.685 | 0.695 |  |

| D1/E1   | 16.51  | 16.66 | 0.650 | 0.656 |  |

| D2      | 15.24  | 16.00 | 0.600 | 0.630 |  |

| е       | 1.27   | BSC   | 0.050 | BSC   |  |

NOTES:

1. CONTROLLING DIMENSION: INCH 2. LEADS ARE COPLANAR WITHIN 0.004". 3. DIMENSION: MM INCH

Figure 64. 44-Lead Plastic Lead Chip Carrier Package (PLCC)

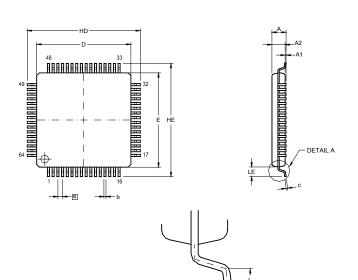

Figure 64 displays the 64-pin Low-Profile Quad Flat Package (LQFP) available for the Z8X1622, Z8X2422, Z8X3222, Z8X4822, and Z8X6422 devices.

DETAIL A

| SYMBOL | MILLIN   | METER | INC       | СН    |  |

|--------|----------|-------|-----------|-------|--|

| SYMBUL | MIN      | MAX   | MIN       | MAX   |  |

| Α      | 1.40     | 1.60  | 0.055     | 0.063 |  |

| A1     | 0.05     | 0.15  | 0.002     | 0.006 |  |

| A2     | 1.35     | 1.45  | 0.053     | 0.057 |  |

| b      | 0.17     | 0.27  | 0.007     | 0.011 |  |

| С      | 0.09     | 0,20  | 0.004     | 0.008 |  |

| HD     | 11.75    | 12.25 | 0.463     | 0.482 |  |

| D      | 9.90     | 10.10 | 0.390     | 0.398 |  |

| HE     | 11.75    | 12.25 | 0.463     | 0.482 |  |

| Е      | 9.90     | 10.10 | 0.390     | 0.398 |  |

| е      | 0.50 BSC |       | 0.0197    | BSC   |  |

| L      | 0.45     | 0.75  | 0.018     | 0.030 |  |

| LE     | 1.00 R   | EF    | 0.039 REF |       |  |

2. MAX. COPLANARITY : 0.10mm 0.004"

Figure 65. 64-Lead Low-Profile Quad Flat Package (LQFP)

PS019919-1207 Packaging

## Index

## **Symbols**

# 244

% 244

@ 244

#### **Numerics**

10-bit ADC 4

40-lead plastic dual-inline package 265

44-lead low-profile quad flat package 266

44-lead plastic lead chip carrier package 267

64-lead low-profile quad flat package 267

68-lead plastic lead chip carrier package 268

80-lead quad flat package 269

## Α

absolute maximum ratings 215

AC characteristics 231

ADC 246

architecture 175

automatic power-down 176

block diagram 176

continuous conversion 177

control register 179

control register definitions 179

data high byte register 180

data low bits register 180

DMA control 178

electrical characteristics and timing 229

operation 176

single-shot conversion 177

ADCCTL register 179

ADCDH register 180

ADCDL register 180

ADCX 246

**ADD 246**

add - extended addressing 246

add with carry 246

add with carry - extended addressing 246

additional symbols 244

address space 19

**ADDX 246**

analog signals 15

analog-to-digital converter (ADC) 175

AND 248

ANDX 248

arithmetic instructions 246

assembly language programming 241

assembly language syntax 242

#### В

B 244

b 243

baud rate generator, UART 113

**BCLR 246**

binary number suffix 244

BIT 246

bit 243

clear 246

manipulation instructions 246

set 246

set or clear 246

swap 247

test and jump 249

test and jump if non-zero 249

test and jump if zero 249

bit jump and test if non-zero 249

bit swap 249

block diagram 3

block transfer instructions 247

**BRK 249**

**BSET 246**

BSWAP 247, 249

BTJ 249

BTJNZ 249

**BTJZ 249**

#### C

CALL procedure 249 capture mode 95

capture/compare mode 95

PS019919-1207 Index