# E·XFL

#### Zilog - Z8F6422AR020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 46                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 64-LQFP                                                       |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6422ar020sc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Manual Objectives**

This Product Specification provides detailed operating information for the Flash devices within Zilog's Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers Microcontroller (MCU) products. Within this document, the Z8F642x, Z8F482x, Z8F322x, Z8F242x, and Z8F162x devices are referred to collectively as the Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers unless specifically stated otherwise.

#### **About This Manual**

Zilog<sup>®</sup> recommends that you read and understand everything in this manual before setting up and using the product. However, we recognize that there are different styles of learning. Therefore, we have designed this Product Specification to be used either as a *how to* procedural manual or a reference guide to important data.

#### Intended Audience

This document is written for Zilog customers who are experienced at working with microcontrollers, integrated circuits, or printed circuit assemblies.

#### **Manual Conventions**

The following assumptions and conventions are adopted to provide clarity and ease of use:

#### **Courier Typeface**

Commands, code lines and fragments, bits, equations, hexadecimal addresses, and various executable items are distinguished from general text by the use of the Courier typeface. Where the use of the font is not indicated, as in the Index, the name of the entity is presented in upper case.

• Example: FLAGS[1] is smrf.

#### **Hexadecimal Values**

Hexadecimal values are designated by uppercase *H* suffix and appear in the Courier typeface.

• Example: R1 is set to F8H.

#### **Brackets**

The square brackets, [], indicate a register or bus.

• Example: For the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant bit, and R1[0] is the least significant bit.

# **Program Memory**

The eZ8<sup>™</sup> CPU supports 64 KB of Program Memory address space. The Z8 Encore! XP 64K Series Flash Microcontrollers contains 16 KB to 64 KB of on-chip Flash in the Program Memory address space, depending upon the device. Reading from Program Memory addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory maps for the 64K Series products.

| Program Memory Address | (Hex) Function           |

|------------------------|--------------------------|

| Z8F162x Products       |                          |

| 0000-0001              | Option Bits              |

| 0002-0003              | Reset Vector             |

| 0004-0005              | WDT Interrupt Vector     |

| 0006-0007              | Illegal Instruction Trap |

| 0008-0037              | Interrupt Vectors*       |

| 0038-3FFF              | Program Memory           |

| Z8F242x Products       |                          |

| 0000-0001              | Option Bits              |

| 0002-0003              | Reset Vector             |

| 0004-0005              | WDT Interrupt Vector     |

| 0006-0007              | Illegal Instruction Trap |

| 0008-0037              | Interrupt Vectors*       |

| 0038-5FFF              | Program Memory           |

| Z8F322x Products       |                          |

| 0000-0001              | Option Bits              |

| 0002-0003              | Reset Vector             |

| 0004-0005              | WDT Interrupt Vector     |

| 0006-0007              | Illegal Instruction Trap |

| 0008-0037              | Interrupt Vectors*       |

| 0038-7FFF              | Program Memory           |

| Z8F482x Products       |                          |

### Table 5. Z8 Encore! XP 64K Series Flash Microcontrollers Program Memory Maps

Reserved

#### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the WDT Control register is set.

#### **Stop Mode Recovery**

STOP mode is entered by the eZ8 executing a STOP instruction. For detailed STOP mode information, see Low-Power Modes on page 47. During Stop Mode Recovery, the devices are held in reset for 66 cycles of the Watchdog Timer oscillator followed by 16 cycles of the system clock. Stop Mode Recovery only affects the contents of the Watchdog Timer Control register. Stop Mode Recovery does not affect any other values in the Register File, including the Stack Pointer, Register Pointer, Flags, peripheral control registers, and general-purpose RAM.

The eZ8<sup>™</sup> CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the STOP bit in the Watchdog Timer Control Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions.

| Operating Mode | Stop Mode Recovery Source                                                         | Action                                                               |  |  |

|----------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| STOP mode      | Watchdog Timer time-out when configured for Reset                                 | Stop Mode Recovery                                                   |  |  |

|                | Watchdog Timer time-out when configured for interrupt                             | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |  |  |

|                | Data transition on any GPIO Port pin<br>enabled as a Stop Mode Recovery<br>source | Stop Mode Recovery                                                   |  |  |

#### Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Watchdog Timer Control register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the 64K Series devices are configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

## Table 42. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7                      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|------------------------|---|---|---|---|---|---|---|--|--|--|

| FIELD | TRL                    |   |   |   |   |   |   |   |  |  |  |

| RESET | 1                      |   |   |   |   |   |   |   |  |  |  |

| R/W   | R/W                    |   |   |   |   |   |   |   |  |  |  |

| ADDR  | F03H, F0BH, F13H, F1BH |   |   |   |   |   |   |   |  |  |  |

TRH and TRL-Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two byte form the 16-bit Compare value.

# Timer 0-3 PWM High and Low Byte Registers

The Timer 0-3 PWM High and Low Byte (TxPWMH and TxPWML) registers (see Table 43 and Table 44 on page 92) are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the Capture and Capture/COM-PARE modes.

## Table 43. Timer 0-3 PWM High Byte Register (TxPWMH)

| BITS  | 7                      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|------------------------|---|---|---|---|---|---|---|--|--|--|

| FIELD | PWMH                   |   |   |   |   |   |   |   |  |  |  |

| RESET | 0                      |   |   |   |   |   |   |   |  |  |  |

| R/W   | R/W                    |   |   |   |   |   |   |   |  |  |  |

| ADDR  | F04H, F0CH, F14H, F1CH |   |   |   |   |   |   |   |  |  |  |

## Table 44. Timer 0-3 PWM Low Byte Register (TxPWML)

| BITS  | 7    | 6                      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|------|------------------------|---|---|---|---|---|---|--|--|--|

| FIELD | PWML |                        |   |   |   |   |   |   |  |  |  |

| RESET | 0    |                        |   |   |   |   |   |   |  |  |  |

| R/W   | R/W  |                        |   |   |   |   |   |   |  |  |  |

| ADDR  |      | F05H, F0DH, F15H, F1DH |   |   |   |   |   |   |  |  |  |

92

### 108

### **Receiving Data using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the desired priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) mode functions, if desired.

- Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- Set the MULTIPROCESSOR Mode Bits, MPMD[1:0], to select the desired address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! devices without a DMA block).

- 7. Write the device address to the Address Compare Register (automatic multiprocessor modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception.

- Enable parity, if desired and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine performs the following:

- 1. Check the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. If the interrupt was caused by data available, read the data from the UART Receive Data register. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

configuration bits. In general, the address compare feature reduces the load on the CPU, since it does not need to access the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes.

- Interrupt on matched address bytes and correctly framed data bytes.

- Interrupt only on correctly framed data bytes.

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all MULTIPROCESSOR modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. At this point, each new incoming byte interrupts the CPU. The software is then responsible for determining the end of the frame. It checks for end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, then set MPMD[0] to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme is enabled by setting MPMD[1:0] to 10b and writing the UART's address into the UART Address Compare Register. This mode introduces more hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. The first data byte in the frame contains the NEWFRM=1 in the UART Status 1 Register. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continue sand the NEWFRM bit is set for the first byte of the new frame. If there is no match, then the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame is still accompanied by a NEWFRM assertion.

#### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 17. The Driver Enable signal asserts

- 120

- 1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

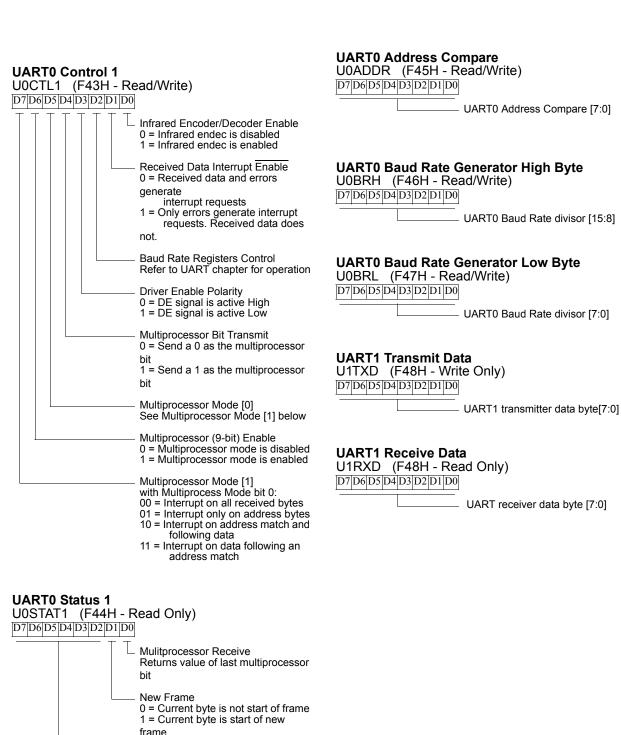

## **UART Address Compare Register**

The UART Address Compare register (Table 58) stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

#### Table 58. UART Address Compare Register (UxADDR)

| BITS  | 7         | 6 | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |

|-------|-----------|---|---|---------|---------|---|---|---|--|--|--|

| FIELD | COMP_ADDR |   |   |         |         |   |   |   |  |  |  |

| RESET | 0         |   |   |         |         |   |   |   |  |  |  |

| R/W   | R/W       |   |   |         |         |   |   |   |  |  |  |

| ADDR  |           |   |   | F45H ar | nd F4DH |   |   |   |  |  |  |

COMP\_ADDR—Compare Address

This 8-bit value is compared to the incoming address bytes.

## UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (see Table 59 and Table 60 on page 121) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the desired 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the UART BRG interrupt interval is calculated using the following equation:

UART BRG Interrupt Interval(s) = System Clock Period (s) × BRG[15:0]

## Table 59. UART Baud Rate High Byte Register (UxBRH)

| BITS  | 7   | 6 | 5 | 4       | 3       | 2 | 1 | 0             |  |  |  |  |  |  |  |  |

|-------|-----|---|---|---------|---------|---|---|---------------|--|--|--|--|--|--|--|--|

| FIELD | BRH |   |   |         |         |   |   |               |  |  |  |  |  |  |  |  |

| RESET | 1   |   |   |         |         |   |   |               |  |  |  |  |  |  |  |  |

| R/W   | R/W |   |   |         |         |   |   |               |  |  |  |  |  |  |  |  |

| ADDR  |     |   |   | F46H ar | nd F4EH |   |   | F46H and F4EH |  |  |  |  |  |  |  |  |

## Table 60. UART Baud Rate Low Byte Register (UxBRL)

| BITS  | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------------|---|---|---|---|---|---|---|--|--|--|

| FIELD | BRL           |   |   |   |   |   |   |   |  |  |  |

| RESET | 1             |   |   |   |   |   |   |   |  |  |  |

| R/W   | R/W           |   |   |   |   |   |   |   |  |  |  |

| ADDR  | F47H and F4FH |   |   |   |   |   |   |   |  |  |  |

For a given UART data rate, the integer baud rate divisor value is calculated using the following equation:

UART Baud Rate Divisor Value (BRG) =  $Round\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the desired baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 61 provides information on data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

The Master and Slave are each capable of exchanging a character of data during a sequence of NUMBITS clock cycles (see NUMBITS field in the SPI Mode Register on page 140). In both Master and Slave SPI devices, data is shifted on one edge of the SCK and is sampled on the opposite edge where data is stable. Edge polarity is determined by the SPI phase and polarity control.

#### **Slave Select**

The active Low Slave Select ( $\overline{SS}$ ) input signal selects a Slave SPI device.  $\overline{SS}$  must be Low prior to all data communication to and from the Slave device.  $\overline{SS}$  must stay Low for the full duration of each character transferred. The  $\overline{SS}$  signal may stay Low during the transfer of multiple characters or may deassert between each character.

When the SPI is configured as the only Master in an SPI system, the  $\overline{SS}$  pin can be set as either an input or an output. For communication between the Z8F642x family Z8R642x family device's SPI Master and external Slave devices, the  $\overline{SS}$  signal, as an output, can assert the  $\overline{SS}$  input pin on one of the Slave devices. Other GPIO output pins can also be employed to select external SPI Slave devices.

When the SPI is configured as one Master in a multi-master SPI system, the  $\overline{SS}$  pin must be set as an input. The  $\overline{SS}$  input signal on the Master must be High. If the  $\overline{SS}$  signal goes Low (indicating another Master is driving the SPI bus), a Collision error Flag is set in the SPI Status register.

#### SPI Clock Phase and Polarity Control

The SPI supports four combinations of serial clock phase and polarity using two bits in the SPI Control register. The clock polarity bit, CLKPOL, selects an active high or active Low clock and has no effect on the transfer format. Table 62 lists the SPI Clock Phase and Polarity Operation parameters. The clock phase bit, PHASE, selects one of two fundamentally different transfer formats. For proper data transmission, the clock phase and polarity must be identical for the SPI Master and the SPI Slave. The Master always places data on the MOSI line a half-cycle before the receive clock edge (SCK signal), in order for the Slave to latch the data.

| PHASE | CLKPOL | SCK Transmit<br>Edge | SCK Receive<br>Edge | SCK Idle<br>State |

|-------|--------|----------------------|---------------------|-------------------|

| 0     | 0      | Falling              | Rising              | Low               |

| 0     | 1      | Rising               | Falling             | High              |

| 1     | 0      | Rising               | Falling             | Low               |

| 1     | 1      | Falling              | Rising              | High              |

|       |        |                      |                     |                   |

#### Table 62. SPI Clock Phase (PHASE) and Clock Polarity (CLKPOL) Operation

0100 = ANA4 0101 = ANA5 0110 = ANA6 0111 = ANA7 1000 = ANA8 1001 = ANA9 1010 = ANA10 1011 = ANA1111XX = Reserved.

### ADC Data High Byte Register

The ADC Data High Byte register (Table 87) contains the upper eight bits of the 10-bit ADC output. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

| Table 87. | ADC Data | High I | Byte | Register | (ADCD | _H) |

|-----------|----------|--------|------|----------|-------|-----|

|-----------|----------|--------|------|----------|-------|-----|

| BITS  | 7      | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |  |  |

|-------|--------|---|---|----|----|---|---|---|--|--|--|--|--|--|

| FIELD | ADCD_H |   |   |    |    |   |   |   |  |  |  |  |  |  |

| RESET |        | X |   |    |    |   |   |   |  |  |  |  |  |  |

| R/W   |        |   |   | F  | २  |   |   |   |  |  |  |  |  |  |

| ADDR  |        |   |   | F7 | 2H |   |   |   |  |  |  |  |  |  |

#### ADCD\_H—ADC Data High Byte

This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the last conversion output is held in this register. These bits are undefined after a Reset.

#### ADC Data Low Bits Register

The ADC Data Low Bits register (Table 88) contains the lower two bits of the conversion value. The data in the ADC Data Low Bits register is latched each time the ADC Data High Byte register is read. Reading this register always returns the lower two bits of the conversion last read into the ADC High Byte register. Access to the ADC Data Low Bits register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

#### 190

## **Flash Control Register Definitions**

### **Flash Control Register**

The Flash Control register (Table 92) unlocks the Flash Controller for programming and erase operations, or to select the Flash Sector Protect register.

The Write-only Flash Control Register shares its Register File address with the Read-only Flash Status Register.

Table 92. Flash Control Register (FCTL)

| BITS  | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |  |  |

|-------|------|---|---|----|----|---|---|---|--|--|--|--|--|--|

| FIELD | FCMD |   |   |    |    |   |   |   |  |  |  |  |  |  |

| RESET |      | 0 |   |    |    |   |   |   |  |  |  |  |  |  |

| R/W   |      |   |   | V  | V  |   |   |   |  |  |  |  |  |  |

| ADDR  |      |   |   | FF | 8H |   |   |   |  |  |  |  |  |  |

FCMD—Flash Command

73H = First unlock command.

8CH = Second unlock command.

95H = Page erase command.

63H = Mass erase command

5EH = Flash Sector Protect register select.

\* All other commands, or any command out of sequence, lock the Flash Controller.

#### Flash Status Register

The Flash Status register (Table 93) indicates the current state of the Flash Controller. This register can be read at any time. The Read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

| BITS  | 7              | 6 | 5 4 3 2 1 0 |   |   |  |  |  |  |  |  |  |  |

|-------|----------------|---|-------------|---|---|--|--|--|--|--|--|--|--|

| FIELD | Reserved FSTAT |   |             |   |   |  |  |  |  |  |  |  |  |

| RESET |                |   |             | ( | 0 |  |  |  |  |  |  |  |  |

| R/W   |                | R |             |   |   |  |  |  |  |  |  |  |  |

| ADDR  | FF8H           |   |             |   |   |  |  |  |  |  |  |  |  |

Table 93. Flash Status Register (FSTAT)

## Table 96. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7 6    |   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |  |  |

|-------|--------|---|---|----|----|---|---|---|--|--|--|--|--|--|

| FIELD | FFREQH |   |   |    |    |   |   |   |  |  |  |  |  |  |

| RESET |        | 0 |   |    |    |   |   |   |  |  |  |  |  |  |

| R/W   |        |   |   | R/ | W  |   |   |   |  |  |  |  |  |  |

| ADDR  |        |   |   | FF | AH |   |   |   |  |  |  |  |  |  |

## Table 97. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7      | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |  |  |

|-------|--------|-----|---|----|----|---|---|---|--|--|--|--|--|--|

| FIELD | FFREQL |     |   |    |    |   |   |   |  |  |  |  |  |  |

| RESET |        |     |   | (  | D  |   |   |   |  |  |  |  |  |  |

| R/W   |        | R/W |   |    |    |   |   |   |  |  |  |  |  |  |

| ADDR  |        |     |   | FF | BH |   |   |   |  |  |  |  |  |  |

FFREQH and FFREQL—Flash Frequency High and Low Bytes

These 2 bytes, {FFREQH[7:0], FFREQL[7:0]}, contain the 16-bit Flash Frequency value.

| Accombly             |                                                                                           |     | ress<br>ode | Openda/c)            |   |   | Fla | ıgs | - Fetch | Instr. |        |   |

|----------------------|-------------------------------------------------------------------------------------------|-----|-------------|----------------------|---|---|-----|-----|---------|--------|--------|---|

| Assembly<br>Mnemonic | Symbolic Operation                                                                        | dst | src         | – Opcode(s)<br>(Hex) | С | Ζ | S   | V   | D       | Н      | Cycles |   |

| AND dst, src         | $dst \leftarrow dst \ AND \ src$                                                          | r   | r           | 52                   | - | * | *   | 0   | -       | -      | 2      | 3 |

|                      | -                                                                                         | r   | lr          | 53                   |   |   |     |     |         |        | 2      | 4 |

|                      | -                                                                                         | R   | R           | 54                   |   |   |     |     |         |        | 3      | 3 |

|                      | -                                                                                         | R   | IR          | 55                   |   |   |     |     |         |        | 3      | 4 |

|                      | -                                                                                         | R   | IM          | 56                   |   |   |     |     |         |        | 3      | 3 |

|                      | -                                                                                         | IR  | IM          | 57                   |   |   |     |     |         |        | 3      | 4 |

| ANDX dst, src        | $dst \gets dst \ AND \ src$                                                               | ER  | ER          | 58                   | - | * | *   | 0   | -       | -      | 4      | 3 |

|                      | -                                                                                         | ER  | IM          | 59                   |   |   |     |     |         |        | 4      | 3 |

| ATM                  | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |     |             | 2F                   | - | - | -   | -   | -       | -      | 1      | 2 |

| BCLR bit, dst        | dst[bit] ← 0                                                                              | r   |             | E2                   | - | * | *   | 0   | -       | -      | 2      | 2 |

| BIT p, bit, dst      | dst[bit] ← p                                                                              | r   |             | E2                   | - | * | *   | 0   | -       | -      | 2      | 2 |

| BRK                  | Debugger Break                                                                            |     |             | 00                   | - | - | -   | -   | -       | -      | 1      | 1 |

| BSET bit, dst        | dst[bit] ← 1                                                                              | r   |             | E2                   | - | * | *   | 0   | -       | -      | 2      | 2 |

| BSWAP dst            | dst[7:0] ← dst[0:7]                                                                       | R   |             | D5                   | Х | * | *   | 0   | -       | -      | 2      | 2 |

| BTJ p, bit, src,     |                                                                                           |     | r           | F6                   | - | - | -   | -   | -       | -      | 3      | 3 |

| dst                  | $PC \leftarrow PC + X$                                                                    |     | lr          | F7                   |   |   |     |     |         |        | 3      | 4 |

| BTJNZ bit,           | if src[bit] = 1                                                                           |     | r           | F6                   | - | - | -   | -   | -       | -      | 3      | 3 |

| src, dst             | $PC \leftarrow PC + X$                                                                    |     | lr          | F7                   |   |   |     |     |         |        | 3      | 4 |

| BTJZ bit, src,       |                                                                                           |     | r           | F6                   | - | - | -   | -   | -       | -      | 3      | 3 |

| dst                  | $PC \leftarrow PC + X$                                                                    |     | lr          | F7                   |   |   |     |     |         |        | 3      | 4 |

| CALL dst             | $SP \leftarrow SP$ -2                                                                     | IRR |             | D4                   | - | - | -   | -   | -       | -      | 2      | 6 |

|                      |                                                                                           | DA  |             | D6                   |   |   |     |     |         |        | 3      | 3 |

| CCF                  | $C \leftarrow \sim C$                                                                     |     |             | EF                   | * | - | -   | -   | -       | -      | 1      | 2 |

| CLR dst              | dst ← 00H                                                                                 | R   |             | B0                   | - | - | -   | -   | -       | -      | 2      | 2 |

|                      | -                                                                                         | IR  |             | B1                   |   |   |     |     |         |        | 2      | 3 |

## Table 133. eZ8 CPU Instruction Summary (Continued)

263

|   |                         |                            |                              |                                |                             |                             | Le                         | ower Nil                       | bble (He                      | x)                             |                            |                          |                           |                           |                         |                          |

|---|-------------------------|----------------------------|------------------------------|--------------------------------|-----------------------------|-----------------------------|----------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|--------------------------|

|   | 0                       | 1                          | 2                            | 3                              | 4                           | 5                           | 6                          | 7                              | 8                             | 9                              | А                          | В                        | С                         | D                         | Е                       | F                        |

| 0 | 1.2<br>BRK              | 2.2<br>SRP<br>IM           | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br><b>ADD</b><br>r1,lr2    | 3.3<br><b>ADD</b><br>R2,R1  | 3.4<br><b>ADD</b><br>IR2,R1 | 3.3<br><b>ADD</b><br>R1,IM | 3.4<br><b>ADD</b><br>IR1,IM    | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1 | 2.3<br><b>RLC</b><br>IR1   | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br><b>ADC</b><br>R2,R1  | 3.4<br>ADC<br>IR2,R1        | 3.3<br><b>ADC</b><br>R1,IM | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                           |                           |                         | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1          | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1  | 3.4<br><b>SUB</b><br>IR2,R1 | 3.3<br><b>SUB</b><br>R1,IM | 3.4<br>SUB<br>IR1,IM           | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                           |                           |                         | 1,2<br><b>ATM</b>        |

| 3 | 2.2<br><b>DEC</b><br>R1 | 2.3<br><b>DEC</b><br>IR1   | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br><b>SBC</b><br>R2,R1  | 3.4<br>SBC<br>IR2,R1        | 3.3<br><b>SBC</b><br>R1,IM | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                           |                           |                         |                          |

| 4 | 2.2<br><b>DA</b><br>R1  | 2.3<br><b>DA</b><br>IR1    | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br>OR<br>r1,lr2            | 3.3<br><b>OR</b><br>R2,R1   | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM  | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br>ORX<br>ER2,ER1         | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                           |                           |                         |                          |

| 5 | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1   | 2.3<br><b>AND</b><br>r1,r2   | 2.4<br><b>AND</b><br>r1,lr2    | 3.3<br><b>AND</b><br>R2,R1  | 3.4<br><b>AND</b><br>IR2,R1 | 3.3<br><b>AND</b><br>R1,IM | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                           |                           |                         | <b>WDT</b>               |

| 6 | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1          | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1  | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                           |                           |                         | <b>STOP</b>              |

| 7 | 2.2<br>PUSH<br>R2       | 2.3<br><b>PUSH</b><br>IR2  | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1   | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM  | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.2<br>HALT              |

| 8 | 2.5<br>DECW<br>RR1      | 2.6<br><b>DECW</b><br>IRR1 | 2.5<br><b>LDE</b><br>r1,Irr2 | 2.9<br><b>LDEI</b><br>Ir1,Irr2 | 3.2<br><b>LDX</b><br>r1,ER2 | 3.3<br>LDX<br>Ir1,ER2       | 3.4<br>LDX<br>IRR2,R1      | 3.5<br><b>LDX</b><br>IRR2,IR1  | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br><b>LDX</b><br>rr1,r2,X  |                            |                          |                           |                           |                         | 1.2<br>DI                |

| 9 | 2.2                     | 2.3<br>RL<br>IR1           | 2.5<br>LDE<br>r2,Irr1        | 2.9<br><b>LDEI</b><br>Ir2,Irr1 | 3.2<br>LDX<br>r2,ER1        | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br>LDX<br>R2,IRR1      | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                           |                           |                         | 1.2<br>El                |

| A | 2.5                     | 2.6<br>INCW                | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1   | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM  | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.4<br>RET               |

| В | 2.2                     | 2.3<br>CLR<br>IR1          | 2.3<br>XOR<br>r1,r2          | 2.4<br>XOR<br>r1,lr2           | 3.3<br><b>XOR</b><br>R2,R1  | 3.4<br>XOR<br>IR2,R1        | 3.3<br>XOR<br>R1,IM        | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br>XORX<br>IM,ER1          |                            |                          |                           |                           |                         | 1.5<br>IRET              |

| С | 2.2                     | 2.3<br>RRC<br>IR1          | 2.5<br>LDC<br>r1,lrr2        | 2.9<br>LDCI<br>Ir1,Irr2        | 2.3<br>JP<br>IRR1           | 2.9<br>LDC<br>lr1,lrr2      | ,                          | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           | ,                              |                            |                          |                           |                           |                         | 1.2<br>RCF               |

| D | 2.2                     | 2.3<br>SRA<br>IR1          | 2.5<br>LDC<br>r2,Irr1        | 2.9<br>LDCI<br>Ir2,Irr1        | 2.6<br>CALL<br>IRR1         | 2.2<br>BSWAP<br>R1          | 3.3<br>CALL<br>DA          | 3.4<br>LD<br>r2,r1,X           | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                           |                           |                         | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1  | 2.3<br><b>RR</b><br>IR1    | 2.2<br>BIT<br>p,b,r1         | 2.3<br>LD<br>r1,lr2            | 3.2<br><b>LD</b><br>R2,R1   | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM  | 3.3<br>LD<br>IR1,IM            | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br>LDX<br>IM,ER1           |                            |                          |                           |                           |                         | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1       | 2.3<br><b>SWAP</b><br>IR1  | 2.6<br>TRAP<br>Vector        | 2.3<br><b>LD</b><br>lr1,r2     | 2.8<br><b>MULT</b><br>RR1   | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b>          | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | V                          | V                        | V                         | V                         | V                       |                          |

Figure 60. First Opcode Map

# zilog

279

eZ8 CPU instruction classes 245 eZ8 CPU instruction notation 242 eZ8 CPU instruction set 241 eZ8 CPU instruction summary 250

# F

FCTL register 190 features, Z8 Encore! 1 first opcode map 263 FLAGS 244 flags register 244 flash controller 4 option bit address space 195 option bit configuration - reset 195 program memory address 0001H 197 flash memory arrangement 184 byte programming 187 code protection 186 configurations 183 control register definitions 190 controller bypass 189 electrical characteristics and timing 228 flash control register 190 flash status register 190 frequency high and low byte registers 192 mass erase 189 operation 185 operation timing 186 page erase 188 page select register 191 FPS register 191 FSTAT register 190

# G

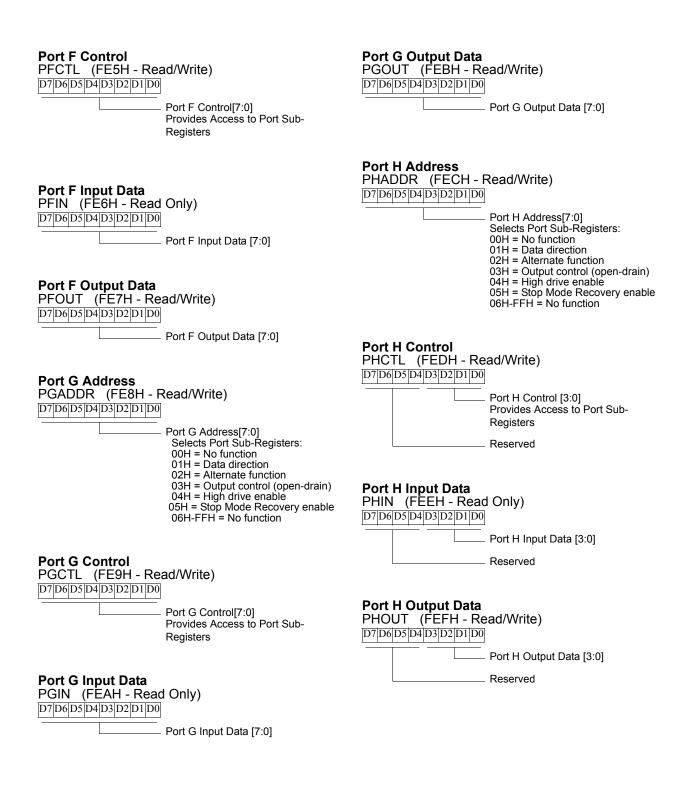

gated mode 95 general-purpose I/O 57 GPIO 4, 57 alternate functions 59 architecture 58 control register definitions 61 input data sample timing 232 interrupts 60 port A-H address registers 61 port A-H alternate function sub-registers 63 port A-H control registers 62 port A-H data direction sub-registers 63 port A-H high drive enable sub-registers 64 port A-H input data registers 66 port A-H output control sub-registers 64 port A-H output data registers 66 port A-H output data registers 66 port A-H Stop Mode Recovery sub-registers 65 port availability by device 57 port input timing 232 port output timing 233

# Η

H 244 HALT 247 halt mode 56, 247 hexadecimal number prefix/suffix 244

#

I2C 4 10-bit address read transaction 154 10-bit address transaction 151 10-bit addressed slave data transfer format 151 10-bit receive data format 154 7-bit address transaction 149 7-bit address, reading a transaction 153 7-bit addressed slave data transfer format 148, 149, 150 7-bit receive data transfer format 153 baud high and low byte registers 160, 161, 163 C status register 157 control register definitions 156 controller 143 controller signals 14 interrupts 145 operation 144 SDA and SCL signals 145 stop and start conditions 147 I2CBRH register 160, 161, 163

280

I2CBRL register 161 I2CCTL register 158 I2CDATA register 157 I2CSTAT register 157 IM 243 immediate data 243 immediate operand prefix 244 **INC 246** increment 246 increment word 246 **INCW 246** indexed 243 indirect address prefix 244 indirect register 243 indirect register pair 243 indirect working register 243 indirect working register pair 243 infrared encoder/decoder (IrDA) 125 instruction set, ez8 CPU 241 instructions ADC 246 ADCX 246 ADD 246 ADDX 246 AND 248 ANDX 248 arithmetic 246 **BCLR 246** BIT 246 bit manipulation 246 block transfer 247 **BRK 249** BSET 246 BSWAP 247, 249 BTJ 249 **BT.INZ 249** BTJZ 249 **CALL 249** CCF 247 **CLR 248** COM 248 CP 246 CPC 246 **CPCX 246**

CPU control 247 CPX 246 DA 246 **DEC 246 DECW 246** DI 247 **DJNZ 249** EI 247 **HALT 247 INC 246** INCW 246 **IRET 249** JP 249 LD 248 LDC 248 LDCI 247, 248 LDE 248 **LDEI 247** LDX 248 LEA 248 load 248 logical 248 **MULT 246** NOP 247 OR 248 **ORX 248** POP 248 **POPX 248** program control 249 **PUSH 248** PUSHX 248 **RCF 247 RET 249** RL 249 RLC 249 rotate and shift 249 RR 249 **RRC 249** SBC 246 SCF 247 SRA 249 SRL 250 SRP 247 **STOP 248**

286

architecture 103 asynchronous data format without/with parity 105 baud rate generator 113 baud rates table 122 control register definitions 114 controller signals 15 data format 104 interrupts 111 multiprocessor mode 109 receiving data using interrupt-driven method 108 receiving data using the polled method 107 transmitting data using the interrupt-driven method 106 transmitting data using the polled method 105 x baud rate high and low registers 120 x control 0 and control 1 registers 117 x status 0 and status 1 registers 115, 116 UxBRH register 121 UxBRL register 121 UxCTL0 register 117, 120 UxCTL1 register 118 UxRXD register 115 UxSTAT0 register 115 UxSTAT1 register 117 UxTXD register 114

# V

vector 243 voltage brown-out reset (VBR) 50

# W

watch-dog timer approximate time-out delay 98 approximate time-out delays 97 CNTL 50 control register 100 electrical characteristics and timing 228 interrupt in normal operation 98 interrupt in STOP mode 98 operation 97 refresh 98, 248 reload unlock sequence 99 reload upper, high and low registers 101 reset 51 reset in normal operation 99 reset in STOP mode 99 time-out response 98 WDTCTL register 100 WDTH register 102 WDTL register 102 working register 243 working register pair 243 WTDU register 102

# Χ

X 243 XOR 249 XORX 249

# Ζ

Z8 Encore! block diagram 3 features 1 introduction 1 part selection guide 2