Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 60                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 80-BQFP                                                       |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6423ft020ec00tr |

## Z8 Encore! XP® 64K Series Flash Microcontrollers | **Product Specification**

| Master Interrupt Enable                                  |    |

|----------------------------------------------------------|----|

| Interrupt Vectors and Priority                           |    |

| Interrupt Assertion                                      |    |

| Software Interrupt Assertion                             |    |

| Interrupt Control Register Definitions                   |    |

| Interrupt Request 0 Register                             |    |

| Interrupt Request 1 Register                             |    |

| Interrupt Request 2 Register                             |    |

| IRQ0 Enable High and Low Bit Registers                   |    |

| IRQ1 Enable High and Low Bit Registers                   |    |

| IRQ2 Enable High and Low Bit Registers                   |    |

| Interrupt Edge Select Register                           |    |

| Interrupt Port Select Register                           |    |

| Interrupt Control Register 7                             | 79 |

| Timers                                                   | 81 |

| Overview                                                 | 31 |

| Architecture                                             | 31 |

| Operation                                                | 32 |

| Timer Operating Modes                                    | 32 |

| Reading the Timer Count Values 9                         | 90 |

| Timer Output Signal Operation 9                          | 90 |

| Timer Control Register Definitions 9                     | 90 |

| Timer 0-3 High and Low Byte Registers 9                  | 90 |

| Timer Reload High and Low Byte Registers 9               | 91 |

| Timer 0-3 PWM High and Low Byte Registers 9              | 92 |

| Timer 0-3 Control 0 Registers 9                          | 93 |

| Timer 0-3 Control 1 Registers 9                          | 94 |

| Watchdog Timer9                                          | 97 |

| Overview                                                 | 97 |

|                                                          | 97 |

| Watchdog Timer Refresh 9                                 | 98 |

| Watchdog Timer Time-Out Response                         |    |

| Watchdog Timer Reload Unlock Sequence                    |    |

| Watchdog Timer Control Register Definitions              |    |

| Watchdog Timer Control Register                          |    |

| Watchdog Timer Reload Upper, High and Low Byte Registers |    |

PS019919-1207 **Table of Contents**

# Introduction

Zilog's Z8 Encore! XP MCU family of products are a line of Zilog<sup>®</sup> microcontroller products based upon the 8-bit eZ8 CPU. The Z8 Encore! XP<sup>®</sup> 64K Series Flash Microcontrollers, hereafter referred to collectively as the Z8 Encore! XP or the 64K Series adds Flash memory to Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8<sup>TM</sup> CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich-peripheral set of the Z8 Encore! XP makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

### **Features**

The features of Z8 Encore! XP 64K Series Flash Microcontrollers include:

- 20 MHz eZ8 CPU

- Up to 64 KB Flash with in-circuit programming capability

- Up to 4 KB register RAM

- 12-channel, 10-bit Analog-to-Digital Converter (ADC)

- Two full-duplex 9-bit UARTs with bus transceiver Driver Enable control

- Inter-integrated circuit (I<sup>2</sup>C)

- Serial Peripheral Interface (SPI)

- Two Infrared Data Association (IrDA)-compliant infrared encoder/decoders

- Up to four 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with internal RC oscillator

- Three-channel DMA

- Up to 60 input/output (I/O) pins

- 24 interrupts with configurable priority

- On-Chip Debugger

- Voltage Brownout (VBO) Protection

- Power-On Reset (POR)

- Operating voltage of 3.0 V to 3.6 V with 5 V-tolerant inputs

- 0 °C to +70 °C, –40 °C to +105 °C, and –40 °C to +125 °C operating temperature ranges

PS019919-1207 Introduction

**Table 3. Signal Descriptions (Continued)**

| Signal<br>Mnemon | ic       | I/O      | Description                                                                                                                                                                                                                                                                                                                     |

|------------------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN              |          | I        | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. This signal is usable with external RC networks and an external clock driver.                                                                                    |

| XOUT             |          | O        | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the XIN pin to form the oscillator. When the system clock is referred to in this manual, it refers to the frequency of the signal at this pin. This pin must be left unconnected when not using a crystal. |

| RCOUT            |          | О        | RC Oscillator Output. This signal is the output of the RC oscillator. It is multiplexed with a general-purpose I/O pin. This signal must be left unconnected when not using a crystal.                                                                                                                                          |

| On-Chip          | Debug    | ger      |                                                                                                                                                                                                                                                                                                                                 |

| DBG              |          | I/O      | Debug. This pin is the control and data input and output to and from the On-Chip Debugger. This pin is open-drain.                                                                                                                                                                                                              |

|                  | <u>^</u> | Caution: | For operation of the On-Chip Debugger, all power pins ( $V_{DD}$ and $AV_{DD}$ ) must be supplied with power and all ground pins ( $V_{SS}$ and $AV_{SS}$ ) must be properly grounded.                                                                                                                                          |

|                  |          |          | The DBG pin is open-drain and must have an external pull-up resistor to ensure proper operation.                                                                                                                                                                                                                                |

| Reset            |          |          |                                                                                                                                                                                                                                                                                                                                 |

| RESET            |          | I        | RESET. Generates a Reset when asserted (driven Low).                                                                                                                                                                                                                                                                            |

| Power St         | upply    |          |                                                                                                                                                                                                                                                                                                                                 |

| VDD              |          | I        | Power Supply.                                                                                                                                                                                                                                                                                                                   |

| AVDD             |          | Ι        | Analog Power Supply.                                                                                                                                                                                                                                                                                                            |

| VSS              |          | I        | Ground.                                                                                                                                                                                                                                                                                                                         |

| AVSS             |          | I        | Analog Ground.                                                                                                                                                                                                                                                                                                                  |

## **Pin Characteristics**

Table 4 on page 17 provides detailed information on the characteristics for each pin available on the 64K Series products and the data is sorted alphabetically by the pin symbol mnemonic.

## Port A-H Input Data Registers

Reading from the Port A–H Input Data registers (Table 21) returns the sampled values from the corresponding port pins. The Port A–H Input Data registers are Read-only.

Table 21. Port A-H Input Data Registers (PxIN)

| BITS  | 7    | 6                                       | 5           | 4         | 3         | 2          | 1   | 0 |  |  |  |  |

|-------|------|-----------------------------------------|-------------|-----------|-----------|------------|-----|---|--|--|--|--|

| FIELD | PIN7 | PIN7 PIN6 PIN5 PIN4 PIN3 PIN2 PIN1 PIN0 |             |           |           |            |     |   |  |  |  |  |

| RESET | X    |                                         |             |           |           |            |     |   |  |  |  |  |

| R/W   |      | R                                       |             |           |           |            |     |   |  |  |  |  |

| ADDR  |      | FD2                                     | H, FD6H, FI | DAH, FDEH | FE2H, FE6 | H, FEAH, F | EEH |   |  |  |  |  |

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 =Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

## Port A-H Output Data Register

The Port A–H Output Data register (Table 22) writes output data to the pins.

Table 22. Port A-H Output Data Register (PxOUT)

| BITS  | 7     | 6                                               | 5           | 4         | 3         | 2          | 1   | 0 |  |  |  |  |

|-------|-------|-------------------------------------------------|-------------|-----------|-----------|------------|-----|---|--|--|--|--|

| FIELD | POUT7 | POUT7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POUT0 |             |           |           |            |     |   |  |  |  |  |

| RESET | 0     |                                                 |             |           |           |            |     |   |  |  |  |  |

| R/W   |       | R/W                                             |             |           |           |            |     |   |  |  |  |  |

| ADDR  |       | FD3                                             | H, FD7H, FI | DBH, FDFH | FE3H, FE7 | H, FEBH, F | EFH |   |  |  |  |  |

POUT[7:0]—Port Output Data

These bits contain the data to be driven out from the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 = Drive a logical 0 (Low).

1= Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

PS019919-1207 General-Purpose I/O

PADxS—PAx/PDx Selection

0 = PAx is used for the interrupt for PAx/PDx interrupt request.

1 = PDx is used for the interrupt for PAx/PDx interrupt request. where *x* indicates the specific GPIO Port pin number (0 through 7).

### **Interrupt Control Register**

The Interrupt Control (IRQCTL) register (Table 38) contains the master enable bit for all interrupts.

**Table 38. Interrupt Control Register (IRQCTL)**

| BITS  | 7    | 6             | 5 4 3 2 1 |    |    |  |  |  |  |  |  |  |

|-------|------|---------------|-----------|----|----|--|--|--|--|--|--|--|

| FIELD | IRQE | IRQE Reserved |           |    |    |  |  |  |  |  |  |  |

| RESET |      | 0             |           |    |    |  |  |  |  |  |  |  |

| R/W   | R/W  | R/W R         |           |    |    |  |  |  |  |  |  |  |

| ADDR  |      |               |           | FC | FH |  |  |  |  |  |  |  |

IRQE—Interrupt Request Enable

This bit is set to 1 by execution of an EI or IRET instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, or Reset.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—Must be 0.

PS019919-1207 Interrupt Controller

### 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All steps of the Watchdog Timer Reload Unlock sequence must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur, unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## **Watchdog Timer Control Register Definitions**

### **Watchdog Timer Control Register**

The Watchdog Timer Control (WDTCTL) register (Table 48) is a Read-Only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

Writing the 55H, AAH unlock sequence to the Watchdog Timer Control (WDTCTL) register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

Table 48. Watchdog Timer Control Register (WDTCTL)

| BITS  | 7                        | 6    | 5   | 4            | 3  | 2 | 1 | 0            |  |  |  |    |

|-------|--------------------------|------|-----|--------------|----|---|---|--------------|--|--|--|----|

| FIELD | POR                      | STOP | WDT | EXT Reserved |    |   |   | EXT Reserved |  |  |  | SM |

| RESET | See descriptions below 0 |      |     |              |    |   |   |              |  |  |  |    |

| R/W   |                          | R    |     |              |    |   |   |              |  |  |  |    |

| ADDR  |                          |      |     | FF           | 0H |   |   |              |  |  |  |    |

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCDCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

PS019919-1207 Watchdog Timer

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

When the UART is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the desired 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

## **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, see Infrared Encoder/Decoder on page 125.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data register (Table 52) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the Read-only UART Receive Data register.

Table 52. UART Transmit Data Register (UxTXD)

| BITS  | 7 6 5 4 3 2 1 |   |  |         |         |  |  |  |  |  |  |  |

|-------|---------------|---|--|---------|---------|--|--|--|--|--|--|--|

| FIELD | TXD           |   |  |         |         |  |  |  |  |  |  |  |

| RESET | X             |   |  |         |         |  |  |  |  |  |  |  |

| R/W   |               | W |  |         |         |  |  |  |  |  |  |  |

| ADDR  |               |   |  | F40H ar | nd F48H |  |  |  |  |  |  |  |

PS019919-1207 **UART**

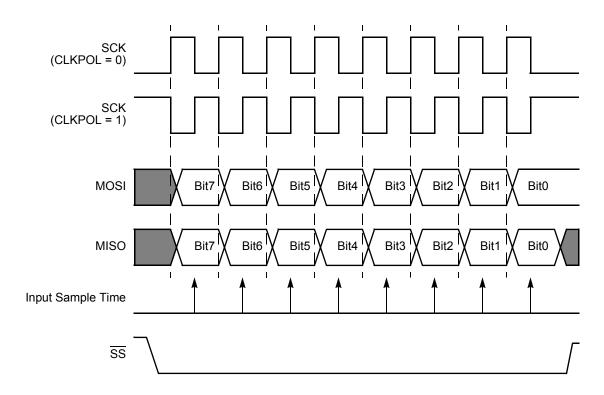

Figure 26. SPI Timing When PHASE is 1

### **Multi-Master Operation**

In a multi-master SPI system, all SCK pins are tied together, all MOSI pins are tied together and all MISO pins are tied together. All SPI pins must then be configured in OPEN-DRAIN mode to prevent bus contention. At any one time, only one SPI device is configured as the Master and all other SPI devices on the bus are configured as Slaves. The Master enables a single Slave by asserting the  $\overline{\rm SS}$  pin on that Slave only. Then, the single Master drives data out its SCK and MOSI pins to the SCK and MOSI pins on the Slaves (including those which are not enabled). The enabled Slave drives data out its MISO pin to the MISO Master pin.

For a Master device operating in a multi-master system, if the  $\overline{SS}$  pin is configured as an input and is driven Low by another Master, the COL bit is set to 1 in the SPI Status Register. The COL bit indicates the occurrence of a multi-master collision (mode fault error condition).

### **Slave Operation**

The SPI block is configured for SLAVE mode operation by setting the SPIEN bit to 1 and the MMEN bit to 0 in the SPICTL register and setting the SSIO bit to 0 in the SPIMODE

- $0 = \overline{SS}$  input pin is asserted (Low).

- $1 = \overline{SS}$  input is not asserted (High).

If SPI enabled as a Master, this bit is not applicable.

## **SPI Mode Register**

The SPI Mode register (Table 66) configures the character bit width and the direction and value of the  $\overline{SS}$  pin.

### Table 66. SPI Mode Register (SPIMODE)

| BITS  | 7    | 6                                   | 5 | 4  | 3  | 1 | 0 |  |  |  |  |  |  |

|-------|------|-------------------------------------|---|----|----|---|---|--|--|--|--|--|--|

| FIELD | Rese | Reserved DIAG NUMBITS[2:0] SSIO SSV |   |    |    |   |   |  |  |  |  |  |  |

| RESET |      | 0                                   |   |    |    |   |   |  |  |  |  |  |  |

| R/W   | F    | R R/W                               |   |    |    |   |   |  |  |  |  |  |  |

| ADDR  |      |                                     |   | F6 | 3H |   |   |  |  |  |  |  |  |

Reserved—Must be 0.

DIAG—Diagnostic Mode Control bit

This bit is for SPI diagnostics. Setting this bit allows the Baud Rate Generator value to be read using the SPIBRH and SPIBRL register locations.

- 0 = Reading SPIBRH, SPIBRL returns the value in the SPIBRH and SPIBRL registers

- 1 = Reading SPIBRH returns bits [15:8] of the SPI Baud Rate Generator; and reading SPIBRL returns bits [7:0] of the SPI Baud Rate Counter. The Baud Rate Counter High and Low byte values are not buffered.

**Caution:** *Exercise caution if reading the values while the BRG is counting.*

NUMBITS[2:0]—Number of Data Bits Per Character to Transfer

This field contains the number of bits to shift for each character transfer. For information on valid bit positions when the character length is less than 8-bits, see SPI Data Register description.

000 = 8 bits

001 = 1 bit

010 = 2 bits

011 = 3 bits

100 = 4 bits

101 = 5 bits

110 = 6 bits

111 = 7 bits

- 4. The I<sup>2</sup>C Controller sends the START condition.

- 5. The I<sup>2</sup>C Controller shifts the address and read bit out the SDA signal.

- 6. If the I<sup>2</sup>C slave acknowledges the address by pulling the SDA signal Low during the next high period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status register. Continue with step 7.

If the slave does not acknowledge, the Not Acknowledge interrupt occurs (NCKI bit is set in the Status register, ACK bit is cleared). Software responds to the Not Acknowledge interrupt by setting the STOP bit and clearing the TXI bit. The I<sup>2</sup>C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore the following steps).

- 7. The  $I^2C$  Controller shifts in the byte of data from the  $I^2C$  slave on the SDA signal. The I<sup>2</sup>C Controller sends a Not Acknowledge to the I<sup>2</sup>C slave if the NAK bit is set (last byte), else it sends an Acknowledge.

- 8. The I<sup>2</sup>C Controller asserts the Receive interrupt (RDRF bit set in the Status register).

- 9. Software responds by reading the I<sup>2</sup>C Data register which clears the RDRF bit. If there is only one more byte to receive, set the NAK bit of the I<sup>2</sup>C Control register.

- 10. If there are more bytes to transfer, return to step 7.

- 11. After the last byte is shifted in, a Not Acknowledge interrupt is generated by the I<sup>2</sup>C Controller.

- 12. Software responds by setting the STOP bit of the I<sup>2</sup>C Control register.

- 13. A STOP condition is sent to the I<sup>2</sup>C slave, the STOP and NCKI bits are cleared.

### Read Transaction with a 10-Bit Address

Figure 33 displays the read transaction format for a 10-bit addressed slave. The shaded regions indicate data transferred from the I<sup>2</sup>C Controller to slaves and unshaded regions indicate data transferred from the slaves to the I<sup>2</sup>C Controller

| s | Slave Address<br>1st 7 bits | W=0 | Α | Slave Address<br>2nd Byte | Α | s | Slave Address<br>1st 7 bits | R=1 | Α | Data | A | Data | Ā | Р |  |

|---|-----------------------------|-----|---|---------------------------|---|---|-----------------------------|-----|---|------|---|------|---|---|--|

|---|-----------------------------|-----|---|---------------------------|---|---|-----------------------------|-----|---|------|---|------|---|---|--|

Figure 33. Receive Data Format for a 10-Bit Addressed Slave

The first seven bits transmitted in the first byte are 11110xx. The two bits xx are the two most-significant bits of the 10-bit address. The lowest bit of the first byte transferred is the write control bit.

PS019919-1207 **I2C Controller**

### IEN—I<sup>2</sup>C Enable

$1 = \text{The } I^2C$  transmitter and receiver are enabled.

$0 = \text{The I}^2\text{C}$  transmitter and receiver are disabled.

### START—Send Start Condition

This bit sends the Start condition. Once asserted, it is cleared by the I<sup>2</sup>C Controller after it sends the START condition or if the IEN bit is deasserted. If this bit is 1, it cannot be cleared to 0 by writing to the register. After this bit is set, the Start condition is sent if there is data in the I<sup>2</sup>C Data or I<sup>2</sup>C Shift register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until the Data register is written. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a START condition after the byte shifts and the acknowledge phase completes. If the STOP bit is also set, it also waits until the STOP condition is sent before the sending the START condition.

### STOP—Send Stop Condition

This bit causes the I<sup>2</sup>C Controller to issue a Stop condition after the byte in the I<sup>2</sup>C Shift register has completed transmission or after a byte has been received in a receive operation. Once set, this bit is reset by the I<sup>2</sup>C Controller after a Stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by writing to the register.

### BIRQ—Baud Rate Generator Interrupt Request

This bit allows the I<sup>2</sup>C Controller to be used as an additional timer when the I<sup>2</sup>C Controller is disabled. This bit is ignored when the I<sup>2</sup>C Controller is enabled.

1 = An interrupt occurs every time the baud rate generator counts down to one.

0 = No band rate generator interrupt occurs.

### TXI—Enable TDRE interrupts

This bit enables the transmit interrupt when the  $I^2C$  Data register is empty (TDRE = 1).

- 1 = Transmit interrupt (and DMA transmit request) is enabled.

- 0 = Transmit interrupt (and DMA transmit request) is disabled.

### NAK—Send NAK

This bit sends a Not Acknowledge condition after the next byte of data has been read from the I<sup>2</sup>C slave. Once asserted, it is deasserted after a Not Acknowledge is sent or the IEN bit is deasserted. If this bit is 1, it cannot be cleared to 0 by writing to the register.

### FLUSH—Flush Data

Setting this bit to 1 clears the I<sup>2</sup>C Data register and sets the TDRE bit to 1. This bit allows flushing of the I<sup>2</sup>C Data register when a Not Acknowledge interrupt is received after the data has been sent to the I<sup>2</sup>C Data register. Reading this bit always returns 0.

## FILTEN—I<sup>2</sup>C Signal Filter Enable

This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.

- 1 = low-pass filters are enabled.

- 0 = low-pass filters are disabled.

PS019919-1207 I2C Controller

If the current ADC Analog Input is not the highest numbered input to be converted, DMA ADC initiates data conversion in the next higher numbered ADC Analog Input.

## Configuring DMA ADC for Data Transfer

Follow the steps below to configure and enable DMA ADC:

- 1. Write the DMA ADC Address register with the 7 most-significant bits of the Register File address for data transfers.

- 2. Write to the DMA ADC Control register to complete the following:

- Enable the DMA ADC interrupt request, if desired

- Select the number of ADC Analog Inputs to convert

- Enable the DMA ADC channel

**Caution:** When using the DMA ADC to perform conversions on multiple ADC inputs, the Analog-to-Digital Converter must be configured for SINGLE-SHOT mode. If the ADC IN field in the DMA ADC Control Register is greater than 000b, the ADC must be in SINGLE-SHOT mode.

> CONTINUOUS mode operation of the ADC can only be used in conjunction with DMA ADC if the ADC IN field in the DMA ADC Control Register is reset to 000b to enable conversion on ADC Analog Input 0 only.

## **DMA Control Register Definitions**

### DMAx Control Register

The DMAx Control register (see Table 77 on page 167) enables and selects the mode of operation for DMAx.

Table 77. DMAx Control Register (DMAxCTL)

| BITS  | 7   | 6   | 5    | 4     | 3    | 2   | 0 |  |  |  |  |  |

|-------|-----|-----|------|-------|------|-----|---|--|--|--|--|--|

| FIELD | DEN | DLE | DDIR | IRQEN | WSEL | RSS |   |  |  |  |  |  |

| RESET | 0   |     |      |       |      |     |   |  |  |  |  |  |

| R/W   |     | R/W |      |       |      |     |   |  |  |  |  |  |

| ADDR  |     |     |      | FB0H, | FB8H |     |   |  |  |  |  |  |

DEN—DMA*x* Enable

0 = DMAx is disabled and data transfer requests are disregarded.

1 = DMAx is enabled and initiates a data transfer upon receipt of a request from the trigger source.

### DLE—DMA*x* Loop Enable

- 0 = DMAx reloads the original Start Address and is then disabled after the End Address data is transferred.

- 1 = DMAx, after the End Address data is transferred, reloads the original Start Address and continues operating.

### DDIR—DMAx Data Transfer Direction

- $0 = \text{Register File} \rightarrow \text{on-chip peripheral control register}$ .

- $1 = \text{on-chip peripheral control register} \rightarrow \text{Register File.}$

### IRQEN—DMAx Interrupt Enable

- 0 = DMAx does not generate any interrupts.

- 1 = DMAx generates an interrupt when the End Address data is transferred.

### WSEL—Word Select

- 0 = DMAx transfers a single byte per request.

- 1 = DMAx transfers a two-byte word per request. The address for the on-chip peripheral control register must be an even address.

### RSS—Request Trigger Source Select

The Request Trigger Source Select field determines the peripheral that can initiate a DMA transfer. The corresponding interrupts do not need to be enabled within the Interrupt Controller to initiate a DMA transfer. However, if the Request Trigger Source can enable or disable the interrupt request sent to the Interrupt Controller, the interrupt request must be enabled within the Request Trigger Source block.

- 000 = Timer 0.

- 001 = Timer 1.

- 010 = Timer 2.

- 011 = Timer 3.

- 100 = DMA0 Control register: UARTO Received Data register contains valid data.

DMA1 Control register: UARTO Transmit Data register empty.

- 101 = DMA0 Control register: UART1 Received Data register contains valid data. DMA1 Control register: UART1 Transmit Data register empty.

- 110 = DMA0 Control register: I<sup>2</sup>C Receiver Interrupt. DMA1 Control register: I<sup>2</sup>C Transmitter Interrupt register empty.

- 111 = Reserved.

## DMAx I/O Address Register

The DMAx I/O Address register (Table 78) contains the low byte of the on-chip peripheral address for data transfer. The full 12-bit Register File address is given by {FH,

## **Flash Control Register Definitions**

### Flash Control Register

The Flash Control register (Table 92) unlocks the Flash Controller for programming and erase operations, or to select the Flash Sector Protect register.

The Write-only Flash Control Register shares its Register File address with the Read-only Flash Status Register.

**Table 92. Flash Control Register (FCTL)**

| BITS  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|---|---|---|---|---|---|---|

| FIELD | FCMD |   |   |   |   |   |   |   |

| RESET | 0    |   |   |   |   |   |   |   |

| R/W   | W    |   |   |   |   |   |   |   |

| ADDR  | FF8H |   |   |   |   |   |   |   |

FCMD—Flash Command

73H = First unlock command.

8CH = Second unlock command.

95H = Page erase command.

63H = Mass erase command

5EH = Flash Sector Protect register select.

## Flash Status Register

The Flash Status register (Table 93) indicates the current state of the Flash Controller. This register can be read at any time. The Read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

Table 93. Flash Status Register (FSTAT)

| BITS  | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|-------|------|-------|-------|---|---|---|---|---|

| FIELD | Rese | erved | FSTAT |   |   |   |   |   |

| RESET | 0    |       |       |   |   |   |   |   |

| R/W   | R    |       |       |   |   |   |   |   |

| ADDR  | FF8H |       |       |   |   |   |   |   |

PS019919-1207 Flash Memory

<sup>\*</sup> All other commands, or any command out of sequence, lock the Flash Controller.

### Reserved

These bits are reserved and must be 0.

FSTAT—Flash Controller Status

00 0000 = Flash Controller locked

00 0001 = First unlock command received

00 0010 = Second unlock command received

00 0011 = Flash Controller unlocked

00 0100 = Flash Sector Protect register selected

$00_1xxx = Program operation in progress$

$01 \ 0xxx = Page erase operation in progress$

10 0xxx = Mass erase operation in progress

### Page Select Register

The Page Select (FPS) register (Table 94) selects one of the 128 available Flash memory pages to be erased or programmed. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory locations with the 7 most significant bits of the address given by the PAGE field are erased to FFH.

The Page Select register shares its Register File address with the Flash Sector Protect Register. The Page Select register cannot be accessed when the Flash Sector Protect register is enabled.

### Table 94. Page Select Register (FPS)

| BITS  | 7       | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|-------------|---|---|---|---|---|---|

| FIELD | INFO_EN | NFO_EN PAGE |   |   |   |   |   |   |

| RESET | 0       |             |   |   |   |   |   |   |

| R/W   | R/W     |             |   |   |   |   |   |   |

| ADDR  | FF9H    |             |   |   |   |   |   |   |

INFO EN—Information Area Enable

0 = Information Area is not selected.

1 = Information Area is selected. The Information area is mapped into the Flash Memory address space at addresses FE00H through FFFFH.

PAGE—Page Select

This 7-bit field selects the Flash memory page for Programming and Page Erase operations. Flash Memory Address[15:9] = PAGE[6:0].

PS019919-1207 Flash Memory

193

## Table 96. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---|---|---|---|---|---|---|

| FIELD | FFREQH |   |   |   |   |   |   |   |

| RESET | 0      |   |   |   |   |   |   |   |

| R/W   | R/W    |   |   |   |   |   |   |   |

| ADDR  | FFAH   |   |   |   |   |   |   |   |

## Table 97. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---|---|---|---|---|---|---|

| FIELD | FFREQL |   |   |   |   |   |   |   |

| RESET | 0      |   |   |   |   |   |   |   |

| R/W   | R/W    |   |   |   |   |   |   |   |

| ADDR  | FFBH   |   |   |   |   |   |   |   |

FFREQH and FFREQL—Flash Frequency High and Low Bytes These 2 bytes, {FFREQH[7:0], FFREQL[7:0]}, contain the 16-bit Flash Frequency value.

PS019919-1207 Flash Memory

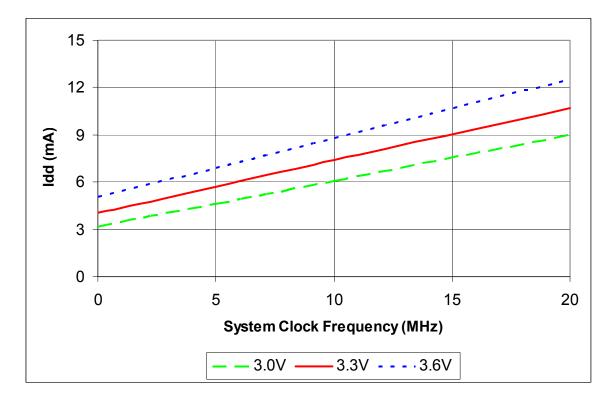

Figure 43 displays the typical active mode current consumption while operating at 25 °C versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 43. Typical Active Mode Idd Versus System Clock Frequency

PS019919-1207 Electrical Characteristics

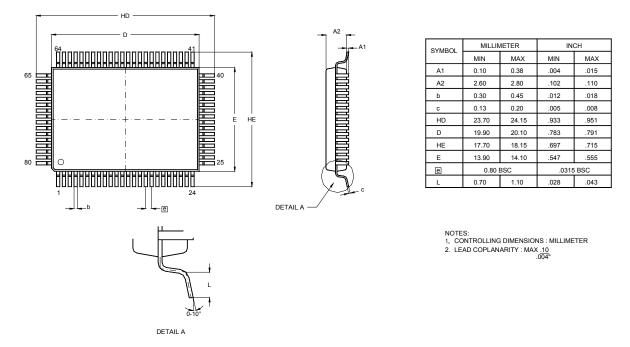

Figure 67 displays the 80-pin Quad Flat Package (QFP) available for the Z8X4823 and Z8X6423 devices.

Figure 67. 80-Lead Quad-Flat Package (QFP)

PS019919-1207 Packaging

# Index

## **Symbols**

# 244

% 244

@ 244

### **Numerics**

10-bit ADC 4

40-lead plastic dual-inline package 265

44-lead low-profile quad flat package 266

44-lead plastic lead chip carrier package 267

64-lead low-profile quad flat package 267

68-lead plastic lead chip carrier package 268

80-lead quad flat package 269

## Α

absolute maximum ratings 215

AC characteristics 231

ADC 246

architecture 175

automatic power-down 176

block diagram 176

continuous conversion 177

control register 179

control register definitions 179

data high byte register 180

data low bits register 180

DMA control 178

electrical characteristics and timing 229

operation 176

single-shot conversion 177

ADCCTL register 179

ADCDH register 180

ADCDL register 180

ADCX 246

**ADD 246**

add - extended addressing 246

add with carry 246

add with carry - extended addressing 246

additional symbols 244

address space 19

**ADDX 246**

analog signals 15

analog-to-digital converter (ADC) 175

AND 248

ANDX 248

arithmetic instructions 246

assembly language programming 241

assembly language syntax 242

### В

B 244

b 243

baud rate generator, UART 113

**BCLR 246**

binary number suffix 244

BIT 246

bit 243

clear 246

manipulation instructions 246

set 246

set or clear 246

swap 247

test and jump 249

test and jump if non-zero 249

test and jump if zero 249

bit jump and test if non-zero 249

bit swap 249

block diagram 3

block transfer instructions 247

**BRK 249**

**BSET 246**

BSWAP 247, 249

BTJ 249

BTJNZ 249

**BTJZ 249**

### C

CALL procedure 249 capture mode 95 capture/compare mode 95

PS019919-1207 Index

| flash page select (FPS) 191                    | sources 48                               |

|------------------------------------------------|------------------------------------------|

| flash status (FSTAT) 190                       | RET 249                                  |

| GPIO port A-H address (PxADDR) 61              | return 249                               |

| GPIO port A-H alternate function sub-registers | RL 249                                   |

| 63                                             | RLC 249                                  |

| GPIO port A-H control address (PxCTL) 62       | rotate and shift instructions 249        |

| GPIO port A-H data direction sub-registers 63  | rotate left 249                          |

| I2C baud rate high (I2CBRH) 160, 161, 163      | rotate left through carry 249            |

| I2C control (I2CCTL) 158                       | rotate right 249                         |

| I2C data (I2CDATA) 157                         | rotate right through carry 249           |

| I2C status 157                                 | RP 244                                   |

| I2C status (I2CSTAT) 157                       | RR 243, 249                              |

| I2Cbaud rate low (I2CBRL) 161                  | rr 243                                   |

| mode, SPI 140                                  | RRC 249                                  |

| OCD control 209                                |                                          |

| OCD status 210                                 |                                          |

| SPI baud rate high byte (SPIBRH) 142           | S                                        |

| SPI baud rate low byte (SPIBRL) 142            | SBC 246                                  |

| SPI control (SPICTL) 138                       | SCF 247                                  |

| SPI data (SPIDATA) 137                         | SDA and SCL (IrDA) signals 145           |

| SPI status (SPISTAT) 139                       | second opcode map after 1FH 264          |

| status, I2C 157                                | serial clock 131                         |

| status, SPI 139                                | serial peripheral interface (SPI) 129    |

| UARTx baud rate high byte (UxBRH) 121          | set carry flag 247                       |

| UARTx baud rate low byte (UxBRL) 121           | set register pointer 247                 |

| UARTx Control 0 (UxCTL0) 117, 120              | shift right arithmetic 249               |

| UARTx control 1 (UxCTL1) 118                   | shift right logical 250                  |

| UARTx receive data (UxRXD) 115                 | signal descriptions 14                   |

| UARTx status 0 (UxSTAT0) 115                   | single-shot conversion (ADC) 177         |

| UARTx status 1 (UxSTAT1) 117                   | SIO 5                                    |

| UARTx transmit data (UxTXD) 114                | slave data transfer formats (I2C) 151    |

| watch-dog timer control (WDTCTL) 100           | slave select 132                         |

| watch-dog timer reload high byte (WDTH) 102    | software trap 249                        |

| watch-dog timer reload low byte (WDTL) 102     | source operand 244                       |

| watch-dog timer reload upper byte (WDTU)       | SP 244                                   |

| 102                                            | SPI                                      |

| register file 19                               | architecture 129                         |

| register file address map 23                   | baud rate generator 136                  |

| register pair 243                              | baud rate high and low byte register 142 |

| register pointer 244                           | clock phase 132                          |

| reset                                          | configured as slave 130                  |

| and STOP mode characteristics 48               | control register 137                     |

| carry flag 247                                 | control register definitions 137         |

| controller 5                                   | data register 137                        |

PS019919-1207 Index