Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                       |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 72MHz                                                                     |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 104                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 58K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 144-LQFP                                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc2377fbd144-551 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- On-chip crystal oscillator with an operating range of 1 MHz to 25 MHz.

- 4 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as the system clock. When used as the CPU clock, does not allow CAN and USB to run.

- On-chip PLL allows CPU operation up to the maximum CPU rate without the need for a high frequency crystal. Can be run from the main oscillator, the internal RC oscillator, or the RTC oscillator.

- Boundary scan for simplified board testing.

- Versatile pin function selections allow more possibilities for using on-chip peripheral functions.

## 3. Applications

- Industrial control

- Medical systems

- Protocol converter

- Communications

## 4. Ordering information

#### Table 1.Ordering information

| Type number   | Package |                                                                                     |          |  |  |  |

|---------------|---------|-------------------------------------------------------------------------------------|----------|--|--|--|

|               | Name    | Description                                                                         | Version  |  |  |  |

| LPC2377FBD144 | LQFP144 | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm | SOT486-1 |  |  |  |

| LPC2378FBD144 | LQFP144 | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm | SOT486-1 |  |  |  |

## 4.1 Ordering options

| Type number   | Flash |           | SRAM (kB)       |        |     |       | External bus                                               | Ether | USB                      |                     | SD/ | GP  |              |              | Temp                |

|---------------|-------|-----------|-----------------|--------|-----|-------|------------------------------------------------------------|-------|--------------------------|---------------------|-----|-----|--------------|--------------|---------------------|

|               | (kB)  | Local bus | Ethernet buffer | GP/USB | RTC | Total |                                                            | net   | device<br>+ 4 kB<br>FIFO | <b>CAN</b> channels | MMC | DMA | ADC channels | DAC channels | range               |

| LPC2377FBD144 | 512   | 32        | 16              | 8      | 2   | 58    | MiniBus: 8 data, 16<br>address, and 2 chip<br>select lines | RMII  | no                       | -                   | yes | yes | 8            | 1            | –40 °C to<br>+85 °C |

| LPC2378FBD144 | 512   | 32        | 16              | 8      | 2   | 58    | MiniBus: 8 data, 16<br>address, and 2 chip<br>select lines | RMII  | yes                      | 2                   | yes | yes | 8            | 1            | –40 °C to<br>+85 °C |

#### Table 2.Ordering options

LPC2377\_78

#### Single-chip 16-bit/32-bit microcontrollers

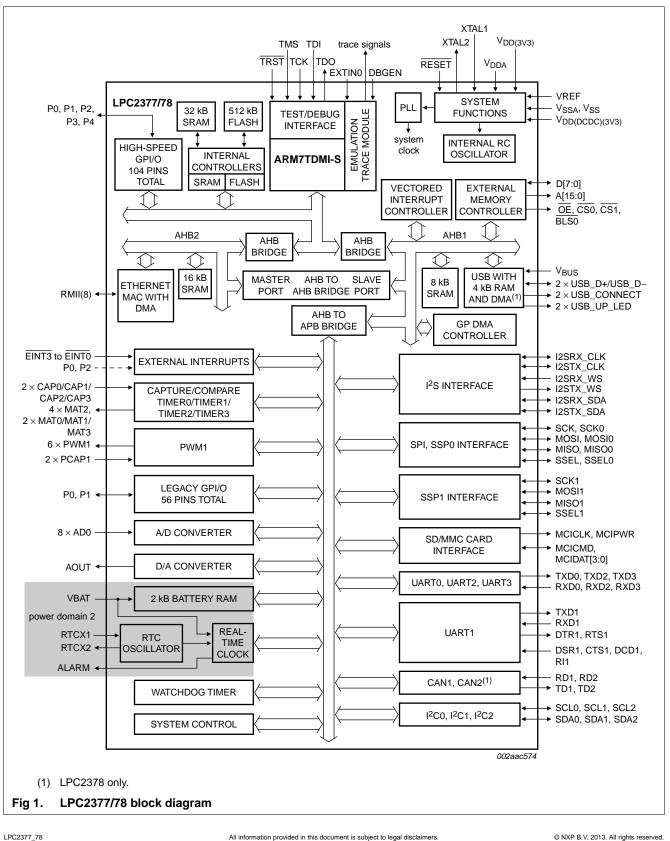

## 5. Block diagram

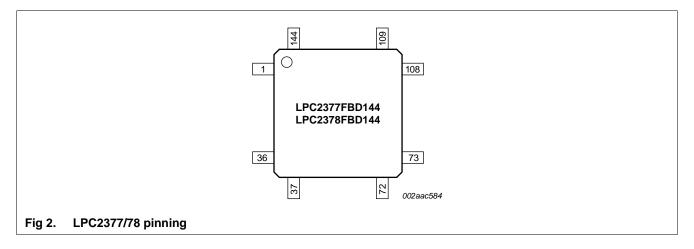

## 6. Pinning information

## 6.1 Pinning

## **NXP Semiconductors**

# LPC2377/78

### Single-chip 16-bit/32-bit microcontrollers

| Table 3. P                   | in descriptio    | ncontinue | ed                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                       | Pin              | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P0[9]/                       | 109 <u>[1]</u>   | I/O       | P0[9] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                  |

| I2STX_SDA/<br>MOSI1/MAT2     |                  | I/O       | <b>I2STX_SDA</b> — Transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification.                                                                                                                                                                                                                                                                                         |

|                              |                  | I/O       | MOSI1 — Master Out Slave In for SSP1.                                                                                                                                                                                                                                                                                                                                                                                                              |

|                              |                  | 0         | MAT2[3] — Match output for Timer 2, channel 3.                                                                                                                                                                                                                                                                                                                                                                                                     |

| P0[10]/TXD2                  |                  | I/O       | P0[10] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

| SDA2/MAT3                    | [0]              | 0         | <b>TXD2</b> — Transmitter output for UART2.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              |                  | I/O       | SDA2 — I <sup>2</sup> C2 data input/output (this pin is not open-drain).                                                                                                                                                                                                                                                                                                                                                                           |

|                              |                  | 0         | MAT3[0] — Match output for Timer 3, channel 0.                                                                                                                                                                                                                                                                                                                                                                                                     |

| P0[11]/RXD2                  |                  | I/O       | P0[11] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCL2/MAT3[                   | 1]               | Ι         | RXD2 — Receiver input for UART2.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                              |                  | I/O       | SCL2 — I <sup>2</sup> C2 clock input/output (this pin is not open-drain).                                                                                                                                                                                                                                                                                                                                                                          |

|                              |                  | 0         | MAT3[1] — Match output for Timer 3, channel 1.                                                                                                                                                                                                                                                                                                                                                                                                     |

| P0[12]/MISO                  | 1/ 29 <u>[2]</u> | I/O       | P0[12] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

| AD0[6]                       |                  | I/O       | MISO1 — Master In Slave Out for SSP1.                                                                                                                                                                                                                                                                                                                                                                                                              |

|                              |                  | Ι         | AD0[6] — A/D converter 0, input 6.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P0[13]/                      | 32 <u>[2]</u>    | I/O       | P0[13] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

| USB_UP_LED2/<br>MOSI1/AD0[7] |                  | 0         | <b>USB_UP_LED2</b> — USB2 Good Link LED indicator. It is LOW when device is configured (non-control endpoints enabled), or when host is enabled and has detected a device on the bus. It is HIGH when the device is not configured, or when host is enabled and has not detected a device on the bus, or during global suspend. It transitions between LOW and HIGH (flashes) when host is enabled and detects activity on the bus. (LPC2378 only) |

|                              |                  | I/O       | MOSI1 — Master Out Slave In for SSP1.                                                                                                                                                                                                                                                                                                                                                                                                              |

|                              |                  | Ι         | AD0[7] — A/D converter 0, input 7.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P0[14]/                      | 48 <u>[1]</u>    | I/O       | P0[14] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

| USB_CONN<br>SSEL1            | ECT2/            | 0         | <b>USB_CONNECT2</b> — USB2 Soft Connect control. Signal used to switch an external 1.5 k $\Omega$ resistor under software control. Used with the SoftConnect USB feature. (LPC2378 only)                                                                                                                                                                                                                                                           |

|                              |                  | I/O       | SSEL1 — Slave Select for SSP1.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P0[15]/TXD1                  | / 89[1]          | I/O       | P0[15] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCK0/SCK                     |                  | 0         | TXD1 — Transmitter output for UART1.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                  | I/O       | SCK0 — Serial clock for SSP0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                              |                  | I/O       | SCK — Serial clock for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P0[16]/RXD1                  |                  | I/O       | P0[16] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

| SSEL0/SSEL                   | -                | Ι         | <b>RXD1</b> — Receiver input for UART1.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                              |                  | I/O       | SSEL0 — Slave Select for SSP0.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                  | I/O       | SSEL — Slave Select for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P0[17]/CTS1                  |                  | I/O       | P0[17] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |

| MISO0/MISC                   | )                | Ι         | <b>CTS1</b> — Clear to Send input for UART1.                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              |                  | I/O       | MISO0 — Master In Slave Out for SSP0.                                                                                                                                                                                                                                                                                                                                                                                                              |

|                              |                  | I/O       | MISO — Master In Slave Out for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                |

|                              |                  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 3. Pin description ...continued

LPC2377\_78

### **NXP Semiconductors**

# LPC2377/78

### Single-chip 16-bit/32-bit microcontrollers

|                                     | cription .                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------|---------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                              | Pin                       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P0[28]/SCL0                         | 34 <u><sup>[4]</sup></u>  | I/O  | <b>P0[28]</b> — General purpose digital input/output pin. Output is open-drain.                                                                                                                                                                                                                                                                                                                                                                         |

|                                     |                           | I/O  | <b>SCL0</b> — I <sup>2</sup> C0 clock input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                                                                                                                                                                                                            |

| P0[29]/USB_D+1                      | 42 <u><sup>[5]</sup></u>  | I/O  | P0[29] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     |                           | I/O  | USB_D+1 — USB1 port bidirectional D+ line. (LPC2378 only)                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[30]/USB_D-1                      | 43 <u>[5]</u>             | I/O  | P0[30] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     |                           | I/O  | USB_D-1 — USB1 port bidirectional D- line. (LPC2378 only)                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[31]/USB_D+2                      | 36 <u>[5]</u>             | I/O  | P0[31] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     |                           | I/O  | USB_D+2 — USB2 port bidirectional D+ line. (LPC2378 only)                                                                                                                                                                                                                                                                                                                                                                                               |

| P1[0] to P1[31]                     |                           | I/O  | <b>Port 1:</b> Port 1 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 1 pins depends upon the pin function selected via the pin connect block. Pins 2, 3, 5, 6, 7, 11, 12, and 13 of this port are not available.                                                                                                                                                                                           |

| P1[0]/                              | 136 <u>[1]</u>            | I/O  | P1[0] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                       |

| ENET_TXD0                           |                           | 0    | ENET_TXD0 — Ethernet transmit data 0.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P1[1]/                              | 135 <u>[1]</u>            | I/O  | P1[1] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                       |

| ENET_TXD1                           |                           | 0    | ENET_TXD1 — Ethernet transmit data 1.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P1[4]/                              | 133 <u>[1]</u>            | I/O  | P1[4] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                       |

| ENET_TX_EN                          |                           | 0    | ENET_TX_EN — Ethernet transmit data enable.                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1[8]/                              | 132 <u>[1]</u>            | I/O  | P1[8] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                       |

| ENET_CRS                            |                           | I    | ENET_CRS — Ethernet carrier sense.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P1[9]/                              | 131 <u>[1]</u>            | I/O  | P1[9] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                       |

| ENET_RXD0                           |                           | I    | ENET_RXD0 — Ethernet receive data.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P1[10]/                             | 129 <u><sup>[1]</sup></u> | I/O  | P1[10] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENET_RXD1                           |                           | I    | ENET_RXD1 — Ethernet receive data.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P1[14]/                             | 128 <u>[1]</u>            | I/O  | P1[14] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENET_RX_ER                          |                           | Ι    | ENET_RX_ER — Ethernet receive error.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P1[15]/                             | 126 <u><sup>[1]</sup></u> | I/O  | P1[15] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENET_REF_CLK                        |                           | Ι    | ENET_REF_CLK/ENET_RX_CLK — Ethernet receiver clock.                                                                                                                                                                                                                                                                                                                                                                                                     |

| P1[16]/                             | 125 <u>[1]</u>            | I/O  | P1[16] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENET_MDC                            |                           | 0    | ENET_MDC — Ethernet MIIM clock.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P1[17]/                             | 123 <u>[1]</u>            | I/O  | P1[17] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENET_MDIO                           |                           | I/O  | ENET_MDIO — Ethernet MIIM data input and output.                                                                                                                                                                                                                                                                                                                                                                                                        |

| P1[18]/                             | 46 <u>[1]</u>             | I/O  | P1[18] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

| USB_UP_LED1/<br>PWM1[1]/<br>CAP1[0] |                           | 0    | <b>USB_UP_LED1</b> — USB1 port Good Link LED indicator. It is LOW when device is configured (non-control endpoints enabled), or when host is enabled and has detected a device on the bus. It is HIGH when the device is not configured, or when host is enabled and has not detected a device on the bus, or during global suspend. It transitions between LOW and HIGH (flashes) when host is enabled and detects activity on the bus. (LPC2378 only) |

|                                     |                           | 0    | PWM1[1] — Pulse Width Modulator 1, channel 1 output.                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                     |                           | I    | CAP1[0] — Capture input for Timer 1, channel 0.                                                                                                                                                                                                                                                                                                                                                                                                         |

| P1[19]/CAP1[1]                      | 47 <u>[1]</u>             | I/O  | P1[19] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     |                           | I    | CAP1[1] — Capture input for Timer 1, channel 1.                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Table 3 Pin description continued

LPC2377\_78

### Single-chip 16-bit/32-bit microcontrollers

|                                  | cription          |               |                                                                                                                                                                                             |                                                   |

|----------------------------------|-------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Symbol                           | Pin               | Туре          | Description                                                                                                                                                                                 |                                                   |

| P2[1]/PWM1[2]/<br>RXD1/          | 106 <u>[1]</u>    | I/O           | P2[1] — General purpose digital input/output pin.                                                                                                                                           |                                                   |

| PIPESTAT0                        |                   | 0             | <b>PWM1[2]</b> — Pulse Width Modulator 1, channel 2 output.                                                                                                                                 |                                                   |

|                                  |                   | I             | <b>RXD1</b> — Receiver input for UART1.                                                                                                                                                     |                                                   |

|                                  |                   | 0             | PIPESTAT0 — Pipeline Status, bit 0.                                                                                                                                                         |                                                   |

| P2[2]/PWM1[3]/                   | 105 <u>[1]</u>    | I/O           | P2[2] — General purpose digital input/output pin.                                                                                                                                           |                                                   |

| CTS1/<br>PIPESTAT1               |                   | 0             | <b>PWM1[3]</b> — Pulse Width Modulator 1, channel 3 output.                                                                                                                                 |                                                   |

|                                  |                   | I             | <b>CTS1</b> — Clear to Send input for UART1.                                                                                                                                                |                                                   |

|                                  |                   | 0             | PIPESTAT1 — Pipeline Status, bit 1.                                                                                                                                                         |                                                   |

| P2[3]/PWM1[4]/                   | 100 <u>[1]</u>    | I/O           | P2[3] — General purpose digital input/output pin.                                                                                                                                           |                                                   |

| DCD1/<br>PIPESTAT2               |                   | 0             | PWM1[4] — Pulse Width Modulator 1, channel 4 output.                                                                                                                                        |                                                   |

| FIFESTAIZ                        |                   | I             | DCD1 — Data Carrier Detect input for UART1.                                                                                                                                                 |                                                   |

|                                  |                   | 0             | PIPESTAT2 — Pipeline Status, bit 2.                                                                                                                                                         |                                                   |

| P2[4]/PWM1[5]/                   | 99 <u>[1]</u>     | I/O           | P2[4] — General purpose digital input/output pin.                                                                                                                                           |                                                   |

| DSR1/                            |                   | 0             | PWM1[5] — Pulse Width Modulator 1, channel 5 output.                                                                                                                                        |                                                   |

| TRACESYNC                        |                   | Ι             | DSR1 — Data Set Ready input for UART1.                                                                                                                                                      |                                                   |

|                                  |                   | 0             | TRACESYNC — Trace Synchronization.                                                                                                                                                          |                                                   |

| P2[5]/PWM1[6]/                   | 97 <u>[1]</u>     | I/O           | P2[5] — General purpose digital input/output pin.                                                                                                                                           |                                                   |

| DTR1/<br>TRACEPKT0               |                   | 0             | PWM1[6] — Pulse Width Modulator 1, channel 6 output.                                                                                                                                        |                                                   |

|                                  |                   | 0             | <b>DTR1</b> — Data Terminal Ready output for UART1.                                                                                                                                         |                                                   |

|                                  |                   | 0             | TRACEPKT0 — Trace Packet, bit 0.                                                                                                                                                            |                                                   |

| P2[6]/PCAP1[0]/                  | 96 <u>[1]</u>     | 96 <u>[1]</u> | I/O                                                                                                                                                                                         | P2[6] — General purpose digital input/output pin. |

| RI1/<br>TRACEPKT1                |                   | Ι             | PCAP1[0] — Capture input for PWM1, channel 0.                                                                                                                                               |                                                   |

| TRACEPRIT                        |                   | Ι             | RI1 — Ring Indicator input for UART1.                                                                                                                                                       |                                                   |

|                                  |                   | 0             | TRACEPKT1 — Trace Packet, bit 1.                                                                                                                                                            |                                                   |

| P2[7]/RD2/                       | 95 <u>[1]</u>     | I/O           | P2[7] — General purpose digital input/output pin.                                                                                                                                           |                                                   |

| RTS1/<br>TRACEPKT2               |                   | Ι             | RD2 — CAN2 receiver input. (LPC2378 only)                                                                                                                                                   |                                                   |

| TRACEPRIZ                        |                   | 0             | RTS1 — Request to Send output for UART1.                                                                                                                                                    |                                                   |

|                                  |                   | 0             | TRACEPKT2 — Trace Packet, bit 2.                                                                                                                                                            |                                                   |

| P2[8]/TD2/                       | 93 <u>[1]</u>     | I/O           | P2[8] — General purpose digital input/output pin.                                                                                                                                           |                                                   |

| TXD2/                            |                   | 0             | TD2 — CAN2 transmitter output. (LPC2378 only)                                                                                                                                               |                                                   |

| TRACEPKT3                        |                   | 0             | TXD2 — Transmitter output for UART2.                                                                                                                                                        |                                                   |

|                                  |                   | 0             | TRACEPKT3 — Trace Packet, bit 3.                                                                                                                                                            |                                                   |

| P2[9]/                           | 92 <sup>[1]</sup> | I/O           | P2[9] — General purpose digital input/output pin.                                                                                                                                           |                                                   |

| USB_CONNECT1/<br>RXD2/<br>EXTIN0 |                   | 0             | <b>USB_CONNECT1</b> — USB1 Soft Connect control. Signal used to switch an externa 1.5 k $\Omega$ resistor under the software control. Used with the SoftConnect USB feature. (LPC2378 only) |                                                   |

|                                  |                   | I             | <b>RXD2</b> — Receiver input for UART2.                                                                                                                                                     |                                                   |

|                                  |                   | I             | EXTINO — External Trigger Input.                                                                                                                                                            |                                                   |

| P2[10]/EINT0                     | 76 <u>[6]</u>     | I/O           | P2[10] — General purpose digital input/output pin.                                                                                                                                          |                                                   |

|                                  | -                 |               | Note: LOW on this pin while RESET is LOW forces on-chip bootloader to take over control of the part after a reset.                                                                          |                                                   |

|                                  |                   | I             | EINT0 — External interrupt 0 input.                                                                                                                                                         |                                                   |

| .PC2377_78                       |                   |               | All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserv                                                                               |                                                   |

| Product data sheet               |                   |               | Rev. 6.1 — 16 October 2013 11 of 6                                                                                                                                                          |                                                   |

The 16-bit instruction length of the Thumb set allows it to approach twice the density of standard ARM code, while retaining most of the ARM performance advantage over a traditional 16-bit processor using 16-bit registers. This increase is possible because Thumb code operates on the same 32-bit register set as ARM code.

Thumb code is able to provide up to 65 % of the code size of ARM, and 160 % of the performance of an equivalent ARM processor connected to a 16-bit memory system.

### 7.2 On-chip flash programming memory

The LPC2377/78 incorporate a 512 kB flash memory system. This memory can be used for both code and data storage. Programming of the flash memory can be accomplished in several ways. It may be programmed In System via the serial port (UART0). The application program may also erase and/or program the flash while the application is running, allowing a great degree of flexibility for data storage field and firmware upgrades.

The flash memory is 128 bits wide and includes pre-fetching and buffering techniques to allow it to operate at SRAM speeds of 72 MHz.

### 7.3 On-chip SRAM

The LPC2377/78 include a SRAM memory of 32 kB reserved for the ARM processor exclusive use. This RAM may be used for code and/or data storage and may be accessed as 8 bits, 16 bits, and 32 bits.

A 16 kB SRAM block serving as a buffer for the Ethernet controller and an 8 kB SRAM used by the GPDMA controller or the USB device can be used for data and code storage. The 2 kB RTC SRAM can be used for data storage only. The RTC SRAM is battery powered and retains the content in the absence of the main power supply.

### 7.5 Interrupt controller

The ARM processor core has two interrupt inputs called Interrupt Request (IRQ) and Fast Interrupt Request (FIQ). The VIC takes 32 interrupt request inputs which can be programmed as FIQ or vectored IRQ types. The programmable assignment scheme means that priorities of interrupts from the various peripherals can be dynamically assigned and adjusted.

FIQs have the highest priority. If more than one request is assigned to FIQ, the VIC ORs the requests to produce the FIQ signal to the ARM processor. The fastest possible FIQ latency is achieved when only one request is classified as FIQ, because then the FIQ service routine can simply start dealing with that device. But if more than one request is assigned to the FIQ class, the FIQ service routine can read a word from the VIC that identifies which FIQ source(s) is (are) requesting an interrupt.

Vectored IRQs, which include all interrupt requests that are not classified as FIQs, have a programmable interrupt priority. When more than one interrupt is assigned the same priority and occur simultaneously, the one connected to the lowest numbered VIC channel will be serviced first.

The VIC ORs the requests from all of the vectored IRQs to produce the IRQ signal to the ARM processor. The IRQ service routine can start by reading a register from the VIC and jumping to the address supplied by that register.

#### 7.5.1 Interrupt sources

Each peripheral device has one interrupt line connected to the VIC but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

Any pin on Port 0 and Port 2 (total of 46 pins) regardless of the selected function, can be programmed to generate an interrupt on a rising edge, a falling edge, or both. Such interrupt requests coming from Port 0 and/or Port 2 will be combined with the EINT3 interrupt requests.

### 7.6 Pin connect block

The pin connect block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on-chip peripherals.

Peripherals should be connected to the appropriate pins prior to being activated and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined.

### 7.7 External memory controller

The LPC2377/78 EMC is an ARM PrimeCell MultiPort Memory Controller peripheral offering support for asynchronous static memory devices such as RAM, ROM, and flash. In addition, it can be used as an interface with off-chip memory-mapped devices and peripherals. The EMC is an Advanced Microcontroller Bus Architecture (AMBA) compliant peripheral.

#### 7.10 Ethernet

The Ethernet block contain a full featured 10 Mbit/s or 100 Mbit/s Ethernet MAC designed to provide optimized performance through the use of DMA hardware acceleration. Features include a generous suite of control registers, half or full duplex operation, flow control, control frames, hardware acceleration for transmit retry, receive packet filtering and wake-up on LAN activity. Automatic frame transmission and reception with scatter-gather DMA off-loads many operations from the CPU.

The Ethernet block and the CPU share a dedicated AHB subsystem that is used to access the Ethernet SRAM for Ethernet data, control, and status information. All other AHB traffic in the LPC2377/78 takes place on a different AHB subsystem, effectively separating Ethernet activity from the rest of the system. The Ethernet DMA can also access off-chip memory via the EMC, as well as the SRAM located on another AHB, if it is not being used by the USB block. However, using memory other than the Ethernet SRAM, especially off-chip memory, will slow Ethernet access to memory and increase the loading of its AHB.

The Ethernet block interfaces between an off-chip Ethernet PHY using the Reduced MII (RMII) protocol and the on-chip Media Independent Interface Management (MIIM) serial bus.

#### 7.10.1 Features

- Ethernet standards support:

- Supports 10 Mbit/s or 100 Mbit/s PHY devices including 10 Base-T, 100 Base-TX, 100 Base-TX, and 100 Base-T4.

- Fully compliant with IEEE standard 802.3.

- Fully compliant with 802.3x full duplex flow control and half duplex back pressure.

- Flexible transmit and receive frame options.

- Virtual Local Area Network (VLAN) frame support.

- Memory management:

- Independent transmit and receive buffers memory mapped to shared SRAM.

- DMA managers with scatter/gather DMA and arrays of frame descriptors.

- Memory traffic optimized by buffering and pre-fetching.

- Enhanced Ethernet features:

- Receive filtering.

- Multicast and broadcast frame support for both transmit and receive.

- Optional automatic Frame Check Sequence (FCS) insertion with Circular Redundancy Check (CRC) for transmit.

- Selectable automatic transmit frame padding.

- Over-length frame support for both transmit and receive allows any length frames.

- Promiscuous receive mode.

- Automatic collision back-off and frame retransmission.

- Includes power management by clock switching.

- Wake-on-LAN power management support allows system wake-up: using the receive filters or a magic frame detection filter.

- Physical interface:

- Attachment of external PHY chip through standard RMII interface.

- PHY register access is available via the MIIM interface.

### 7.11 USB interface (LPC2378 only)

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and a number (127 maximum) of peripherals. The host controller allocates the USB bandwidth to attached devices through a token based protocol. The bus supports hot plugging, unplugging and dynamic configuration of the devices. All transactions are initiated by the host controller.

The two sets of pins needed by a USB device are named  $V_{BUS}$ , USB\_D+1, USB\_D-1, USB\_UP\_LED1, USB\_CONNECT1, and USB\_D+2, USB\_D-2, USB\_UP\_LED2, and USB\_CONNECT2 respectively. At any given time only one of these two sets can be active and used by the application.

#### 7.11.1 USB device controller

The device controller enables 12 Mbit/s data exchange with a USB host controller. It consists of register interface, serial interface engine, endpoint buffer memory, and the DMA controller. The serial interface engine decodes the USB data stream and writes data to the appropriate end point buffer memory. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled. The DMA controller when enabled transfers data between the endpoint buffer and the USB RAM.

#### 7.11.1.1 Features

- Fully compliant with USB 2.0 specification (full speed).

- Supports 32 physical (16 logical) endpoints with a 4 kB endpoint buffer RAM.

- Supports Control, Bulk, Interrupt and Isochronous endpoints.

- Scalable realization of endpoints at run time.

- Endpoint Maximum packet size selection (up to USB maximum specification) by software at run time.

- Supports SoftConnect and GoodLink features.

- While USB is in the Suspend mode, the LPC2377/78 can enter one of the reduced power modes and wake up on a USB activity.

- Supports DMA transfers with the DMA RAM of 8 kB on all non-control endpoints.

- Allows dynamic switching between CPU-controlled and DMA modes.

- Double buffer implementation for Bulk and Isochronous endpoints.

### 7.14 10-bit DAC

The DAC allows the LPC2377/78 to generate a variable analog output. The maximum output value of the DAC is  $V_{i(\text{VREF})}.$

#### 7.14.1 Features

- 10-bit DAC

- Resistor string architecture

- Buffered output

- Power-down mode

- Selectable output drive

#### 7.15 UARTs

The LPC2377/78 contain four UARTs. In addition to standard transmit and receive data lines, UART1 also provides a full modem control handshake interface.

The UARTs include a fractional baud rate generator. Standard baud rates such as 115200 can be achieved with any crystal frequency above 2 MHz.

#### 7.15.1 Features

- 16 B Receive and Transmit FIFOs.

- Register locations conform to 16C550 industry standard.

- Receiver FIFO trigger points at 1 B, 4 B, 8 B, and 14 B.

- Built-in fractional baud rate generator covering wide range of baud rates without a need for external crystals of particular values.

- Fractional divider for baud rate control, auto baud capabilities and FIFO control mechanism that enables software flow control implementation.

- UART1 equipped with standard modem interface signals. This module also provides full support for hardware flow control (auto-CTS/RTS).

- UART3 includes an IrDA mode to support infrared communication.

### 7.16 SPI serial I/O controller

The LPC2377/78 contain one SPI controller. SPI is a full duplex serial interface designed to handle multiple masters and slaves connected to a given bus. Only a single master and a single slave can communicate on the interface during a given data transfer. During a data transfer the master always sends 8 bits to 16 bits of data to the slave, and the slave always sends 8 bits to 16 bits of data to the master.

#### 7.16.1 Features

- Compliant with SPI specification

- Synchronous, Serial, Full Duplex Communication

- Combined SPI master and slave

- Maximum data bit rate of one eighth of the input clock rate

- 8 bits to 16 bits per transfer

LPC2377 78

25 of 69

#### Single-chip 16-bit/32-bit microcontrollers

### 7.24 RTC and battery RAM

The RTC is a set of counters for measuring time when system power is on, and optionally when it is off. It uses little power in Power-down and Deep power-down modes. On the LPC2377/78, the RTC can be clocked by a separate 32.768 kHz oscillator or by a programmable prescale divider based on the APB clock. Also, the RTC is powered by its own power supply pin, VBAT, which can be connected to a battery or to the same 3.3 V supply used by the rest of the device.

The VBAT pin supplies power only to the RTC and the battery RAM. These two functions require a minimum of power to operate, which can be supplied by an external battery. When the CPU and the rest of chip functions are stopped and power removed, the RTC can supply an alarm output that can be used by external hardware to restore chip power and resume operation.

#### 7.24.1 Features

- Measures the passage of time to maintain a calendar and clock.

- Ultra low power design to support battery powered systems.

- Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year.

- Dedicated 32 kHz oscillator or programmable prescaler from APB clock.

- Dedicated power supply pin can be connected to a battery or to the main 3.3 V.

- An alarm output pin is included to assist in waking up from Power-down mode, or when the chip has had power removed to all functions except the RTC and battery RAM.

- Periodic interrupts can be generated from increments of any field of the time registers, and selected fractional second values.

- 2 kB data SRAM powered by VBAT.

- RTC and battery RAM power supply is isolated from the rest of the chip.

### 7.25 Clocking and power control

#### 7.25.1 Crystal oscillators

The LPC2377/78 include three independent oscillators. These are the Main Oscillator, the Internal RC oscillator, and the RTC oscillator. Each oscillator can be used for more than one purpose as required in a particular application. Any of the three clock sources can be chosen by software to drive the PLL and ultimately the CPU.

Following reset, the LPC2377/78 will operate from the Internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the bootloader code to operate at a known frequency.

#### 7.25.1.1 Internal RC oscillator

The IRC may be used as the clock source for the WDT, and/or as the clock that drives the PLL and subsequently the CPU. The nominal IRC frequency is 4 MHz. The IRC is trimmed to  $\pm$  1 % accuracy.

Upon power-up or any chip reset, the LPC2377/78 use the IRC as the clock source. Software may later switch to one of the other available clock sources.

Running an application with level CRP3 selected fully disables any access to chip via the JTAG pins and the ISP. This mode effectively disables ISP override using P2[10] pin, too. It is up to the user's application to provide (if needed) flash update mechanism using IAP calls or call reinvoke ISP command to enable flash update via UART0.

#### CAUTION

If level three Code Read Protection (CRP3) is selected, no future factory testing can be performed on the device.

#### 7.26.4 AHB

The LPC2377/78 implement two AHBs in order to allow the Ethernet block to operate without interference caused by other system activity. The primary AHB, referred to as AHB1, includes the Vectored Interrupt Controller, GPDMA controller, USB interface, and 8 kB SRAM primarily intended for use by the USB.

The second AHB, referred to as AHB2, includes only the Ethernet block and an associated 16 kB SRAM. In addition, a bus bridge is provided that allows the secondary AHB to be a bus master on AHB1, allowing expansion of Ethernet buffer space into off-chip memory or unused space in memory residing on AHB1.

In summary, bus masters with access to AHB1 are the ARM7 itself, the USB block, the GPDMA function, and the Ethernet block (via the bus bridge from AHB2). Bus masters with access to AHB2 are the ARM7 and the Ethernet block.

#### 7.26.5 External interrupt inputs

The LPC2377/78 include up to 50 edge sensitive interrupt inputs combined with up to four level sensitive external interrupt inputs as selectable pin functions. The external interrupt inputs can optionally be used to wake up the processor from Power-down mode.

#### 7.26.6 Memory mapping control

The memory mapping control alters the mapping of the interrupt vectors that appear at the beginning at address 0x0000 0000. Vectors may be mapped to the bottom of the Boot ROM, the SRAM, or external memory. This allows code running in different memory spaces to have control of the interrupts.

#### 7.27 Emulation and debugging

The LPC2377/78 support emulation and debugging via a JTAG serial port. A trace port allows tracing program execution. Debugging and trace functions are multiplexed only with GPIOs on P2[0] to P2[9]. This means that all communication, timer, and interface peripherals residing on other pins are available during the development and debugging phase as they are when the application is run in the embedded system itself.

#### Single-chip 16-bit/32-bit microcontrollers

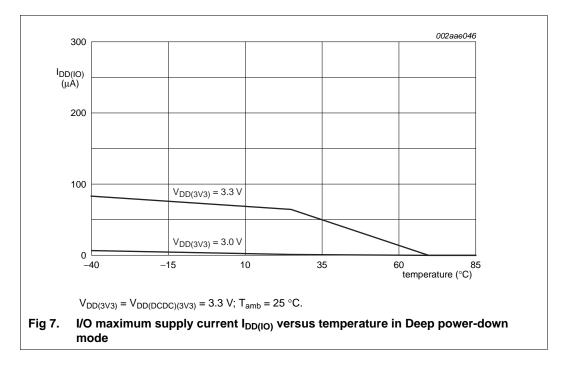

## 10.2 Deep power-down mode

#### Single-chip 16-bit/32-bit microcontrollers

## 11. Dynamic characteristics

#### Table 8. Dynamic characteristics

$T_{amb} = -40 \text{ °C to } +85 \text{ °C for commercial applications; } V_{DD(3V3)}$  over specified ranges.[1]

|                                        |                                                                                                                | (                                                                                 | -                               |                |      |      |  |  |  |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------|----------------|------|------|--|--|--|--|

| Symbol                                 | Parameter                                                                                                      | Conditions                                                                        | Min                             | Typ <u>[2]</u> | Max  | Unit |  |  |  |  |

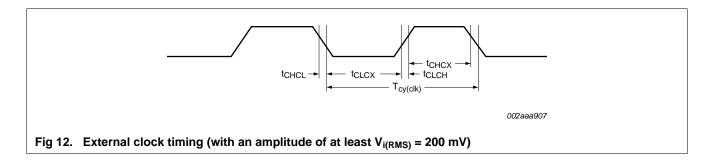

| External clock (see <u>Figure 12</u> ) |                                                                                                                |                                                                                   |                                 |                |      |      |  |  |  |  |

| f <sub>osc</sub>                       | oscillator frequency                                                                                           |                                                                                   | 1                               | -              | 25   | MHz  |  |  |  |  |

| T <sub>cy(clk)</sub>                   | clock cycle time                                                                                               |                                                                                   | 40                              | -              | 1000 | ns   |  |  |  |  |

| t <sub>CHCX</sub>                      | clock HIGH time                                                                                                |                                                                                   | $T_{\text{cy(clk)}} \times 0.4$ | -              | -    | ns   |  |  |  |  |

| t <sub>CLCX</sub>                      | clock LOW time                                                                                                 |                                                                                   | $T_{\text{cy(clk)}} \times 0.4$ | -              | -    | ns   |  |  |  |  |

| t <sub>CLCH</sub>                      | clock rise time                                                                                                |                                                                                   | -                               | -              | 5    | ns   |  |  |  |  |