Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.75K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6525-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nama             | Pin N                                     | umber       | Pin        | Buffer      | Description                                            |  |  |

|----------------------|-------------------------------------------|-------------|------------|-------------|--------------------------------------------------------|--|--|

| Pin Name             | PIC18F6X2X                                | PIC18F8X2X  | Туре       | Туре        | Description                                            |  |  |

|                      |                                           |             |            |             | PORTA is a bidirectional I/O port.                     |  |  |

| RA0/AN0              | 24                                        | 30          |            |             |                                                        |  |  |

| RA0                  |                                           |             | I/O        | TTL         | Digital I/O.                                           |  |  |

| AN0                  |                                           |             | I          | Analog      | Analog input 0.                                        |  |  |

| RA1/AN1              | 23                                        | 29          |            |             |                                                        |  |  |

| RA1                  |                                           |             | I/O        | TTL         | Digital I/O.                                           |  |  |

| AN1                  |                                           |             | I          | Analog      | Analog input 1.                                        |  |  |

| RA2/AN2/VREF-        | 22                                        | 28          |            |             |                                                        |  |  |

| RA2                  |                                           |             | I/O        | TTL         | Digital I/O.                                           |  |  |

| AN2                  |                                           |             | I          | Analog      | Analog input 2.                                        |  |  |

| VREF-                |                                           |             | I          | Analog      | A/D reference voltage (low) input.                     |  |  |

| RA3/AN3/VREF+        | 21                                        | 27          |            |             |                                                        |  |  |

| RA3                  |                                           |             | I/O        | TTL         | Digital I/O.                                           |  |  |

| AN3                  |                                           |             | I          | Analog      | Analog input 3.                                        |  |  |

| VREF+                |                                           |             | I          | Analog      | A/D reference voltage (high) input.                    |  |  |

| RA4/T0CKI            | 28                                        | 34          |            |             |                                                        |  |  |

| RA4                  |                                           |             | I/O        | ST/OD       | Digital I/O – Open-drain when configured<br>as output. |  |  |

| TOCKI                |                                           |             | I          | ST          | Timer0 external clock input.                           |  |  |

| RA5/AN4/LVDIN        | 27                                        | 33          |            |             |                                                        |  |  |

| RA5                  |                                           |             | I/O        | TTL         | Digital I/O.                                           |  |  |

| AN4                  |                                           |             | I          | Analog      | Analog input 4.                                        |  |  |

| LVDIN                |                                           |             | I          | Analog      | Low-Voltage Detect input.                              |  |  |

| RA6                  |                                           |             |            |             | See the OSC2/CLKO/RA6 pin.                             |  |  |

| Legend: TTL = TTL co | mpatible input                            | •           | CMOS       | S = CMOS    | compatible input or output                             |  |  |

| ST = Schmit          | tt Trigger input with C                   | CMOS levels | Analo      | g = Analog  | •                                                      |  |  |

| I = Input            |                                           |             | 0          | = Output    |                                                        |  |  |

| P = Power            |                                           |             | OD         | •           | Drain (no P diode to VDD)                              |  |  |

|                      | gnment for ECCP2/F<br>nory modes except N |             | 5/8621 d   | evices wher | n CCP2MX (CONFIG3H<0>) is not set (all                 |  |  |

| 0                    | nment for ECCP2/P2                        | ,           | is sat (al | devices)    |                                                        |  |  |

| -                    | lory interface function                   |             |            |             | 621 devices                                            |  |  |

|                      | -                                         |             |            |             | s when ECCPMX (CONFIG3H<1>) is set and for             |  |  |

#### TABLE 1-2: PIC18F6525/6621/8525/8621 PINOUT I/O DESCRIPTIONS (CONTINUED)

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8525/8621 devices when ECCPMX (CONFIG3H<1>) is set and for all PIC18F6525/6621 devices.

5: Alternate assignment for ECCP2/P2A in PIC18F8525/8621 devices when CCP2MX is not set (Microcontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8525/8621 devices.

7: Alternate assignment for P1B/P1C/P3B/P3C for PIC18F8525/8621 devices when ECCPMX (CONFIG3H<1>) is not set.

8: AVDD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of the part in user or ICSP<sup>™</sup> modes. See parameter D001 for details.

9: RG5 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

#### 2.6.1 SYSTEM CLOCK SWITCH BIT

The system clock source switching is performed under software control. The system clock switch bits, SCS1:SCS0 (OSCCON<1:0>), control the clock switching. When the SCS0 bit is '0', the system clock source comes from the main oscillator that is selected by the FOSC configuration bits in the CONFIG1H Configuration register. When the SCS0 bit is set, the system clock source will come from the Timer1 oscillator. The SCS0 bit is cleared on all forms of Reset.

When the FOSC bits are programmed for Software PLL mode, the SCS1 bit can be used to select between primary oscillator/clock and PLL output. The SCS1 bit will only have an effect on the system clock if the PLL is enabled (PLLEN = 1) and locked (LOCK = 1), else it will be forced cleared. When programmed with Configuration Controlled PLL, the SCS1 bit will be forced clear.

Note: The Timer1 oscillator must be enabled and operating to switch the system clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON). If the Timer1 oscillator is not enabled, then any write to the SCS0 bit will be ignored (SCS0 bit forced cleared) and the main oscillator will continue to be the system clock source.

#### REGISTER 2-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0                     | R/W-0 | R/W-0               |

|-------|-----|-----|-----|-------|---------------------------|-------|---------------------|

| _     | —   | —   | —   | LOCK  | LOCK PLLEN <sup>(1)</sup> |       | SCS0 <sup>(2)</sup> |

| bit 7 |     |     |     |       |                           |       | bit 0               |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                     |  |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 3   | LOCK: Phase Lock Loop Lock Status bit                                                                                                                                                          |  |  |  |  |  |  |  |

|         | <ul> <li>1 = Phase Lock Loop output is stable as system clock</li> <li>0 = Phase Lock Loop output is not stable and output cannot be used as system clock</li> </ul>                           |  |  |  |  |  |  |  |

| bit 2   | PLLEN: Phase Lock Loop Enable bit <sup>(1)</sup>                                                                                                                                               |  |  |  |  |  |  |  |

|         | <ul> <li>1 = Enable Phase Lock Loop output as system clock</li> <li>0 = Disable Phase Lock Loop</li> </ul>                                                                                     |  |  |  |  |  |  |  |

| bit 1   | SCS1: System Clock Switch bit 1                                                                                                                                                                |  |  |  |  |  |  |  |

|         | When PLLEN and LOCK bits are set:<br>1 = Use PLL output<br>0 = Use primary oscillator/clock input pin<br>When PLLEN or LOCK bit is cleared:                                                    |  |  |  |  |  |  |  |

|         | Bit is forced clear.                                                                                                                                                                           |  |  |  |  |  |  |  |

| bit 0   | SCS0: System Clock Switch bit 0 <sup>(2)</sup>                                                                                                                                                 |  |  |  |  |  |  |  |

|         | When OSCSEN configuration bit = 0 and T1OSCEN bit = 1:                                                                                                                                         |  |  |  |  |  |  |  |

|         | Switch to Timer1 oscillator/clock pin Use primary oscillator/clock input pin                                                                                                                   |  |  |  |  |  |  |  |

|         | When OSCSEN and T1OSCEN are in other states:<br>Bit is forced clear.                                                                                                                           |  |  |  |  |  |  |  |

|         | Note 1: PLLEN bit is forced set when configured for ECIO+PLL and HS+PLL modes. This<br>bit is writable for ECIO+SPLL and HS+SPLL modes only; forced cleared for all other<br>oscillator modes. |  |  |  |  |  |  |  |

|         | <b>2:</b> The setting of SCS0 = 1 supersedes SCS1 = 1.                                                                                                                                         |  |  |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 4.3 Fast Register Stack

A "fast interrupt return" option is available for interrupts. A fast register stack is provided for the STATUS, WREG and BSR registers and is only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers if the FAST RETURN instruction is used to return from the interrupt.

A low or high priority interrupt source will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably for low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten.

If high priority interrupts are not disabled during low priority interrupts, users must save the key registers in software during a low priority interrupt.

If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a FAST CALL instruction must be executed.

Example 4-1 shows a source code example that uses the fast register stack.

#### EXAMPLE 4-1: FAST REGISTER STACK CODE EXAMPLE

|                  | •••                                                     |

|------------------|---------------------------------------------------------|

| CALL SUB1, FAST  | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

| •                |                                                         |

| SUB1 •<br>•<br>• |                                                         |

| RETURN FAST      | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

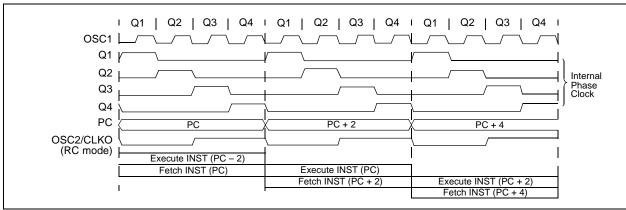

## FIGURE 4-5: CLOCK/INSTRUCTION CYCLE

### 4.4 PCL, PCLATH and PCLATU

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide. The low byte is called the PCL register; this register is readable and writable. The high byte is called the PCH register. This register contains the PC<15:8> bits and is not directly readable or writable; updates to the PCH register may be performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable; updates to the PCH register the PC<20:16> bits and is not directly readable or writable; updates to the PCU register may be performed through the PCLATH register.

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of the PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 4.8.1** "**Computed GOTO**").

### 4.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the Program Counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the Instruction Register (IR) in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 4-5.

### 7.0 DATA EEPROM MEMORY

The data EEPROM is readable and writable during normal operation over the entire VDD range. The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are five SFRs used to read and write the program and data EEPROM memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADRH

- EEADR

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write. EEADR and EEADRH hold the address of the EEPROM location being accessed. These devices have 1024 bytes of data EEPROM with an address range from 00h to 3FFh.

The EEPROM data memory is rated for high erase/ write cycles. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip-to-chip. Please refer to parameter D122 (Section 27.0 "Electrical Characteristics") for exact limits.

### 7.1 EEADR and EEADRH

The address register pair can address up to a maximum of 1024 bytes of data EEPROM. The two Most Significant bits of the address are stored in EEADRH, while the remaining eight Least Significant bits are stored in EEADR. The six Most Significant bits of EEADRH are unused and are read as '0'.

### 7.2 EECON1 and EECON2 Registers

EECON1 is the control register for EEPROM memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

Control bits RD and WR initiate read and write operations, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at the completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

| Note: | During normal operation, the WRERR bit         |  |  |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|--|--|

|       | is read as '1'. This can indicate that a write |  |  |  |  |  |  |  |  |

|       | operation was prematurely terminated by        |  |  |  |  |  |  |  |  |

|       | a Reset, or a write operation was              |  |  |  |  |  |  |  |  |

|       | attempted improperly.                          |  |  |  |  |  |  |  |  |

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR) due to the Reset condition forcing the contents of the registers to zero.

**Note:** Interrupt flag bit, EEIF in the PIR2 register, is set when write is complete. It must be cleared in software.

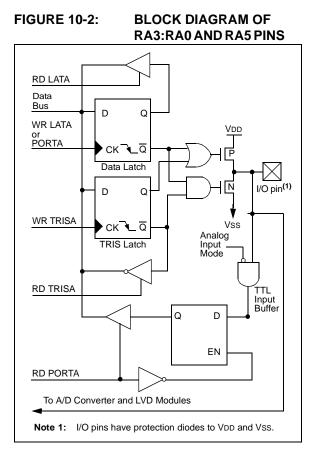

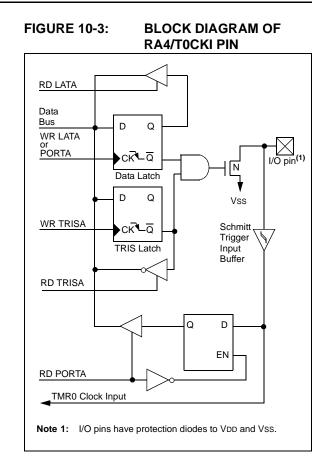

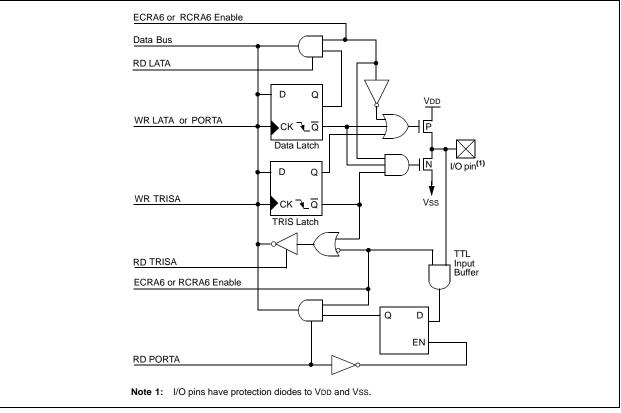

### FIGURE 10-4: BLOCK DIAGRAM OF RA6 PIN (WHEN ENABLED AS I/O)

| Name          | Bit#  | Buffer | Function                                                                       |

|---------------|-------|--------|--------------------------------------------------------------------------------|

| RA0/AN0       | bit 0 | TTL    | Input/output or analog input.                                                  |

| RA1/AN1       | bit 1 | TTL    | Input/output or analog input.                                                  |

| RA2/AN2/VREF- | bit 2 | TTL    | Input/output, analog input or VREF                                             |

| RA3/AN3/VREF+ | bit 3 | TTL    | Input/output, analog input or VREF+.                                           |

| RA4/T0CKI     | bit 4 | ST     | Input/output or external clock input for Timer0.<br>Output is open-drain type. |

| RA5/AN4/LVDIN | bit 5 | TTL    | Input/output, analog input or Low-Voltage Detect input.                        |

| OSC2/CLKO/RA6 | bit 6 | TTL    | OSC2, clock output or I/O pin                                                  |

#### TABLE 10-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6                 | Bit 5   | Bit 4                         | Bit 3    | Bit 2     | Bit 1     | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-----------------------|---------|-------------------------------|----------|-----------|-----------|-------|----------------------|---------------------------------|

| PORTA  |       | RA6 <sup>(1)</sup>    | RA5     | RA4                           | RA3      | RA2       | RA1       | RA0   | -x0x 0000            | -u0u 0000                       |

| LATA   | —     | LATA6 <sup>(1)</sup>  | LATA Da | ta Output                     | Register | -xxx xxxx | -uuu uuuu |       |                      |                                 |

| TRISA  | _     | TRISA6 <sup>(1)</sup> | PORTA [ | PORTA Data Direction Register |          |           |           |       |                      | -111 1111                       |

| ADCON1 | _     | —                     | VCFG1   | VCFG0                         | PCFG3    | PCFG2     | PCFG1     | PCFG0 | 00 0000              | 00 0000                         |

**Legend:** x = unknown, u = unchanged, — = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator modes only and read '0' in all other oscillator modes.

| Name    | Bit#  | Buffer Type | Function                                                                             |

|---------|-------|-------------|--------------------------------------------------------------------------------------|

| RJ0/ALE | bit 0 | ST          | Input/output port pin or address latch enable control for external memory interface. |

| RJ1/OE  | bit 1 | ST          | Input/output port pin or output enable control for external memory interface.        |

| RJ2/WRL | bit 2 | ST          | Input/output port pin or write low byte control for external memory interface.       |

| RJ3/WRH | bit 3 | ST          | Input/output port pin or write high byte control for external memory interface.      |

| RJ4/BA0 | bit 4 | ST          | Input/output port pin or byte address 0 control for external memory interface.       |

| RJ5/CE  | bit 5 | ST          | Input/output port pin or chip enable control for external memory interface.          |

| RJ6/LB  | bit 6 | ST          | Input/output port pin or lower byte select control for external memory interface.    |

| RJ7/UB  | bit 7 | ST          | Input/output port pin or upper byte select control for external memory interface.    |

#### TABLE 10-17: PORTJ FUNCTIONS

**Legend:** ST = Schmitt Trigger input

#### TABLE 10-18: SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ

| Name  | Bit 7     | Bit 6                                     | Bit 5 | Bit 4     | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|-------|-----------|-------------------------------------------|-------|-----------|-----------|-------|-------|-------|----------------------|---------------------------------|--|

| PORTJ | Read PC   | )RTJ pin/                                 |       | xxxx xxxx | uuuu uuuu |       |       |       |                      |                                 |  |

| LATJ  | LATJ Da   | LATJ Data Output Register                 |       |           |           |       |       |       |                      | uuuu uuuu                       |  |

| TRISJ | Data Dire | Data Direction Control Register for PORTJ |       |           |           |       |       |       |                      | 1111 1111                       |  |

**Legend:** x = unknown, u = unchanged

| REGISTER 10-1: | PSPCON: PARALLEL SLAVE PORT CONTROL REGISTER <sup>(1)</sup>                                                                                                                                                                                                 |                      |       |       |     |     |     |       |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-------|-----|-----|-----|-------|--|--|--|

|                | R-0                                                                                                                                                                                                                                                         | R-0                  | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |  |  |  |

|                | IBF                                                                                                                                                                                                                                                         | IBF OBF IBOV PSPMODE |       |       |     |     |     |       |  |  |  |

|                | bit 7                                                                                                                                                                                                                                                       |                      |       |       |     |     |     | bit 0 |  |  |  |

| bit 7          | <b>IBF:</b> Input Buffer Full Status bit<br>1 = A word has been received and is waiting to be read by the CPU<br>0 = No word has been received                                                                                                              |                      |       |       |     |     |     |       |  |  |  |

| bit 6          | <ul> <li>O = No word has been received</li> <li>OBF: Output Buffer Full Status bit</li> <li>1 = The output buffer still holds a previously written word</li> </ul>                                                                                          |                      |       |       |     |     |     |       |  |  |  |

| bit 5          | <ul> <li>0 = The output buffer has been read</li> <li><b>IBOV:</b> Input Buffer Overflow Detect bit</li> <li>1 = A write occurred when a previously input word has not been read (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |                      |       |       |     |     |     |       |  |  |  |

| bit 4          | <b>PSPMODE:</b> Parallel Slave Port Mode Select bit 1 = Parallel Slave Port mode 0 = General Purpose I/O mode                                                                                                                                               |                      |       |       |     |     |     |       |  |  |  |

| bit 3-0        | Unimplemented: Read as '0'<br>Note 1: Enabled only in Microcontroller mode for PIC18F8525/8621 devices.                                                                                                                                                     |                      |       |       |     |     |     |       |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

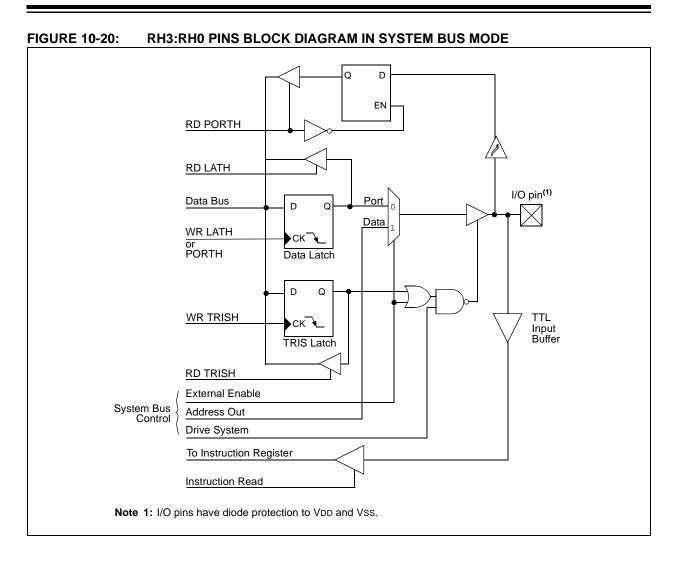

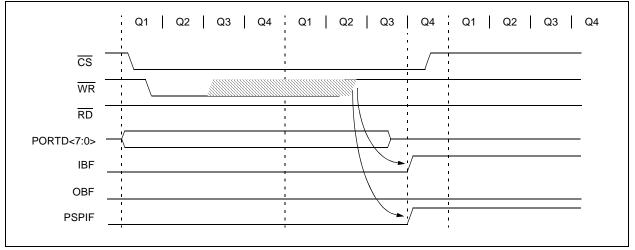

#### FIGURE 10-25: PARALLEL SLAVE PORT WRITE WAVEFORMS

NOTES:

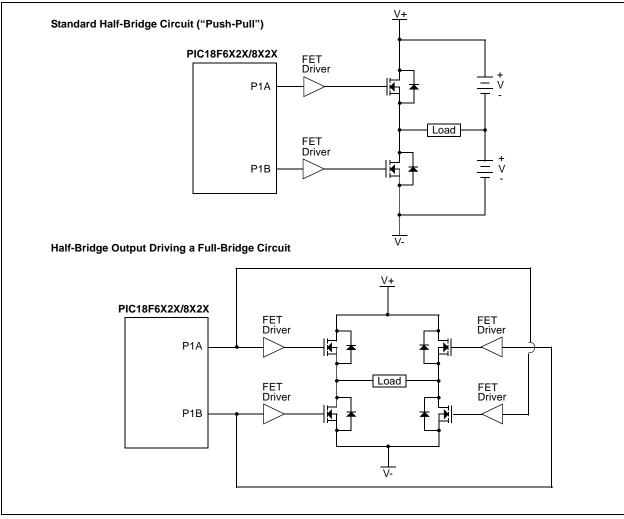

#### FIGURE 17-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

#### 18.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 18.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 18.3.10 BUS MODE COMPATIBILITY

Table 18-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

#### TABLE 18-1: SPI™ BUS MODES

| Standard SPI Mode | Control E | Bits State |

|-------------------|-----------|------------|

| Terminology       | СКР       | CKE        |

| 0, 0              | 0         | 1          |

| 0, 1              | 0         | 0          |

| 1, 0              | 1         | 1          |

| 1, 1              | 1         | 0          |

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                | Bit 6           | Bit 5      | Bit 4         | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Value on POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------|-----------------|------------|---------------|--------|--------|---------------|--------|-------------------|---------------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL       | TMR0IE     | <b>INTOIE</b> | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 0000 000x         | 0000 000u                       |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF            | RC1IF      | TX1IF         | SSPIF  | CCP1IF | TMR2IF        | TMR1IF | 0000 0000         | 0000 0000                       |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE            | RC1IE      | TX1IE         | SSPIE  | CCP1IE | TMR2IE        | TMR1IE | 0000 0000         | 0000 0000                       |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP            | RC1IP      | TX1IP         | SSPIP  | CCP1IP | TMR2IP        | TMR1IP | 1111 1111         | 1111 1111                       |

| TRISC   | PORTC Dat            | a Direction R   | egister    |               |        |        |               |        | 1111 1111         | 1111 1111                       |

| TRISF   | TRISF7               | TRISF6          | TRISF5     | TRISF4        | TRISF3 | TRISF2 | TRISF1        | TRISF0 | 1111 1111         | 1111 1111                       |

| SSPBUF  | MSSP Rece            | eive Buffer/Tra | ansmit Reg | ister         |        |        |               |        | xxxx xxxx         | uuuu uuuu                       |

| SSPCON1 | WCOL                 | SSPOV           | SSPEN      | CKP           | SSPM3  | SSPM2  | SSPM1         | SSPM0  | 0000 0000         | 0000 0000                       |

| SSPSTAT | SMP                  | CKE             | D/A        | Р             | S      | R/W    | UA            | BF     | 0000 0000         | 0000 0000                       |

#### TABLE 18-2: REGISTERS ASSOCIATED WITH SPI™ OPERATION

**Legend:** x = unknown, u = unchanged, ---= unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI<sup>TM</sup> mode.**Note 1:**Enabled only in Microcontroller mode for PIC18F8525/8621 devices.

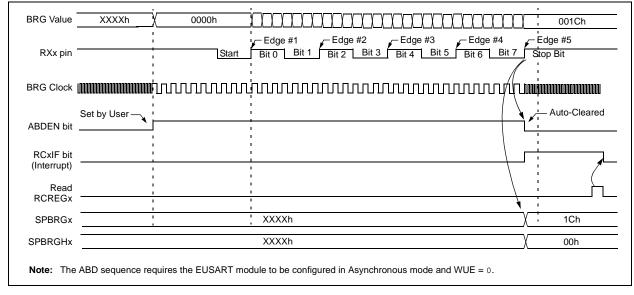

#### 19.1.2 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 19-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RXx signal, the RXx signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value 55h (ASCII "U", which is also the LIN bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRGx begins counting up using the preselected clock source on the first rising edge of RXx. After eight bits on the RXx pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGHx:SPBRGx register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRGx and SPBRGHx will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGHx register. Refer to Table 19-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCxIF interrupt is set once the fifth rising edge on RXx is detected. The value in the RCREGx needs to be read to clear the RC1IF interrupt. RCREGx content should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

#### TABLE 19-4: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/128          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

**Note:** During the ABD sequence, SPBRGx and SPBRGHx are both used as a 16-bit counter, independent of BRG16 setting.

#### FIGURE 19-1: AUTOMATIC BAUD RATE CALCULATION

#### 21.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 21.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the comparator Reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators will be powered down during the Reset interval.

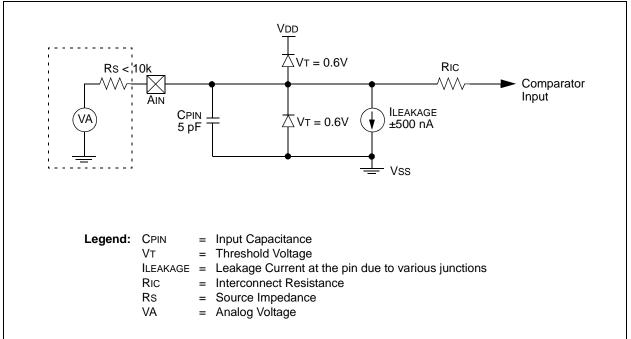

#### 21.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 21-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 21-4: COMPARATOR ANALOG INPUT MODEL

| DEC         | FSZ                                             | Decreme                                                                                                                           | nt f, Skip if (                                                                                                                                                                                                                           | )                                                                                                                                                    |

|-------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synta       | ax:                                             | [label] D                                                                                                                         | ECFSZ f[,d[                                                                                                                                                                                                                               | ,a]]                                                                                                                                                 |

| Oper        | ands:                                           | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                               |                                                                                                                                                                                                                                           |                                                                                                                                                      |

| Oper        | ation:                                          | (f) – 1 $\rightarrow$ d<br>skip if resu                                                                                           |                                                                                                                                                                                                                                           |                                                                                                                                                      |

| Statu       | s Affected:                                     | None                                                                                                                              |                                                                                                                                                                                                                                           |                                                                                                                                                      |

| Enco        | ding:                                           | 0010                                                                                                                              | 11da fff                                                                                                                                                                                                                                  | f ffff                                                                                                                                               |

| Desc        | ription:                                        | decrement<br>placed in V<br>placed bac<br>If the result<br>which is all<br>and a NOP<br>it a two-cyc<br>Access Ba<br>riding the E | hts of register 'f<br>ed. If 'd' is '0',<br>V. If 'd' is '1', th<br>k in register 'f'<br>t is '0', the nex<br>ready fetched i<br>is executed ins<br>cle instruction.<br>nk will be seler<br>BSR value. If 'a<br>e selected as p<br>nult). | the result is<br>ne result is<br>(default).<br>t instruction<br>s discarded<br>stead, making<br>If 'a' is '0', the<br>cted, over-<br>' = 1, then the |

| Word        | ls:                                             | 1                                                                                                                                 |                                                                                                                                                                                                                                           |                                                                                                                                                      |

| Cycle       | es:                                             | 1(2)                                                                                                                              |                                                                                                                                                                                                                                           |                                                                                                                                                      |

| QC          | ycle Activity:                                  |                                                                                                                                   | ycles if skip ar<br>a 2-word instru                                                                                                                                                                                                       |                                                                                                                                                      |

|             | Q1                                              | Q2                                                                                                                                | Q3                                                                                                                                                                                                                                        | Q4                                                                                                                                                   |

|             | Decode                                          | Read<br>register 'f'                                                                                                              | Process<br>Data                                                                                                                                                                                                                           | Write to destination                                                                                                                                 |

| lf sk       | •                                               |                                                                                                                                   |                                                                                                                                                                                                                                           |                                                                                                                                                      |

| 1           | Q1                                              | Q2                                                                                                                                | Q3                                                                                                                                                                                                                                        | Q4                                                                                                                                                   |

|             | No<br>operation                                 | No<br>operation                                                                                                                   | No<br>operation                                                                                                                                                                                                                           | No<br>operation                                                                                                                                      |

| lf sk       |                                                 | d by 2-word in                                                                                                                    |                                                                                                                                                                                                                                           | operation                                                                                                                                            |

|             | Q1                                              | Q2                                                                                                                                | Q3                                                                                                                                                                                                                                        | Q4                                                                                                                                                   |

|             | No                                              | No                                                                                                                                | No                                                                                                                                                                                                                                        | No                                                                                                                                                   |

|             | operation                                       | operation                                                                                                                         | operation                                                                                                                                                                                                                                 | operation                                                                                                                                            |

|             | No                                              | No                                                                                                                                | No                                                                                                                                                                                                                                        | No                                                                                                                                                   |

|             | operation                                       | operation                                                                                                                         | operation                                                                                                                                                                                                                                 | operation                                                                                                                                            |

| <u>Exan</u> | nple:                                           | HERE<br>CONTINUE                                                                                                                  | DECFSZ<br>GOTO                                                                                                                                                                                                                            | CNT, 1, 1<br>LOOP                                                                                                                                    |

|             | Before Instruc<br>PC<br>After Instructio<br>CNT | = Addres<br>on<br>= CNT –                                                                                                         | s (here)<br>1                                                                                                                                                                                                                             |                                                                                                                                                      |

|             | If CNT<br>PC                                    | = 0;<br>= Addres                                                                                                                  | s (CONTINUE                                                                                                                                                                                                                               | :)                                                                                                                                                   |

|             | If CNT<br>PC                                    | ≠ 0;<br>= Addres                                                                                                                  |                                                                                                                                                                                                                                           |                                                                                                                                                      |

| DCF         | SNZ                                 | Decremer                                                                                                                                 | nt f, Skip if N                                                                                                                                                                                                                      | Not 0                                                                                                                                |

|-------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Synta       | ax:                                 | [label] D                                                                                                                                | CFSNZ f[,d                                                                                                                                                                                                                           | [,a]                                                                                                                                 |

| Oper        | ands:                               | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                       |                                                                                                                                                                                                                                      |                                                                                                                                      |

| Oper        | ation:                              | (f) – 1 $\rightarrow$ de skip if resul                                                                                                   | -                                                                                                                                                                                                                                    |                                                                                                                                      |

| Statu       | is Affected:                        | None                                                                                                                                     |                                                                                                                                                                                                                                      |                                                                                                                                      |

| Enco        | oding:                              | 0100                                                                                                                                     | 11da fff                                                                                                                                                                                                                             | f ffff                                                                                                                               |

| Word        | ription:<br>ds:                     | decremented<br>placed in W<br>placed back<br>If the result<br>which is alru<br>and a NOP i<br>it a two-cyc<br>Access Bar<br>riding the B | ts of register 'f<br>ed. If 'd' is '0', '<br>/. If 'd' is '1', th<br>< in register 'f'<br>is '0', the nex:<br>eady fetched i<br>s executed ins<br>le instruction.<br>k will be select<br>SR value. If 'a<br>e selected as p<br>ult). | the result is<br>(default).<br>t instruction<br>s discarded<br>stead, making<br>If 'a' is '0', the<br>cted, over-<br>' = 1, then the |

| Cycle       | 26.                                 | 1(2)                                                                                                                                     |                                                                                                                                                                                                                                      |                                                                                                                                      |

| QC          | ycle Activity:                      | Note: 3 c                                                                                                                                | ycles if skip ar<br>a 2-word instru                                                                                                                                                                                                  |                                                                                                                                      |

|             | Q1                                  | Q2                                                                                                                                       | Q3                                                                                                                                                                                                                                   | Q4                                                                                                                                   |

|             | Decode                              | Read<br>register 'f'                                                                                                                     | Process<br>Data                                                                                                                                                                                                                      | Write to<br>destination                                                                                                              |

| lf sk       | ip:                                 |                                                                                                                                          |                                                                                                                                                                                                                                      |                                                                                                                                      |

|             | Q1                                  | Q2                                                                                                                                       | Q3                                                                                                                                                                                                                                   | Q4                                                                                                                                   |

|             | No<br>operation                     | No<br>operation                                                                                                                          | No<br>operation                                                                                                                                                                                                                      | No<br>operation                                                                                                                      |

| lf sk       | ip and followe                      |                                                                                                                                          |                                                                                                                                                                                                                                      |                                                                                                                                      |

|             | Q1                                  | Q2                                                                                                                                       | Q3                                                                                                                                                                                                                                   | Q4                                                                                                                                   |

|             | No                                  | No                                                                                                                                       | No                                                                                                                                                                                                                                   | No                                                                                                                                   |

|             | operation                           | operation                                                                                                                                | operation                                                                                                                                                                                                                            | operation                                                                                                                            |

|             | No<br>operation                     | No<br>operation                                                                                                                          | No<br>operation                                                                                                                                                                                                                      | No<br>operation                                                                                                                      |

| <u>Exan</u> | nple:                               | ZERO                                                                                                                                     | DCFSNZ TEM<br>:                                                                                                                                                                                                                      | IP, 1, 0                                                                                                                             |

|             | Before Instruc                      | tion                                                                                                                                     |                                                                                                                                                                                                                                      |                                                                                                                                      |

|             | TEMP                                | = ?                                                                                                                                      |                                                                                                                                                                                                                                      |                                                                                                                                      |

|             | After Instructio<br>TEMP<br>If TEMP |                                                                                                                                          | MP – 1,                                                                                                                                                                                                                              |                                                                                                                                      |

|             |                                     |                                                                                                                                          | dress (ZERO                                                                                                                                                                                                                          | )                                                                                                                                    |

|             | If TEMP<br>PC                       | ≠ 0;<br>= Ad                                                                                                                             | dress (NZER                                                                                                                                                                                                                          | 0)                                                                                                                                   |

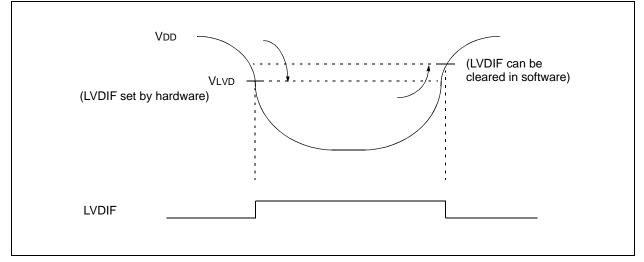

### FIGURE 27-3: LOW-VOLTAGE DETECT CHARACTERISTICS

| TABLE 27-3: | LOW-VOLTAGE DETECT CHARACTERISTICS |

|-------------|------------------------------------|

|             |                                    |

| LOW-V        | OLTAGE I | DETECT CHARACTER       | RISTICS       |      |      | erature | -40°C ≤ T | (unless otherwise stated)<br>A $\leq$ +85°C for industrial<br>TA $\leq$ +125°C for extended |

|--------------|----------|------------------------|---------------|------|------|---------|-----------|---------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol   | Characteris            | stic          | Min  | Тур† | Max     | Units     | Conditions                                                                                  |

| D420         | Vlvd     | LVD Voltage on VDD     | LVV = 0000    | —    | —    | —       | V         |                                                                                             |

|              |          | transition high-to-low | LVV = 0001    | 1.96 | 2.06 | 2.16    | V         |                                                                                             |

|              |          |                        | LVV = 0010    | 2.16 | 2.27 | 2.38    | V         |                                                                                             |

|              |          |                        | LVV = 0011    | 2.35 | 2.47 | 2.59    | V         |                                                                                             |

|              |          |                        | LVV = 0100    | 2.46 | 2.58 | 2.71    | V         |                                                                                             |

|              |          |                        | LVV = 0101    | 2.64 | 2.78 | 2.92    | V         |                                                                                             |

|              |          |                        | LVV = 0110    | 2.75 | 2.89 | 3.03    | V         |                                                                                             |

|              |          |                        | LVV = 0111    | 2.95 | 3.10 | 3.26    | V         |                                                                                             |

|              |          |                        | LVV = 1000    | 3.24 | 3.41 | 3.58    | V         |                                                                                             |

|              |          |                        | LVV = 1001    | 3.43 | 3.61 | 3.79    | V         |                                                                                             |

|              |          |                        | LVV = 1010    | 3.53 | 3.72 | 3.91    | V         |                                                                                             |

|              |          |                        | LVV = 1011    | 3.72 | 3.92 | 4.12    | V         |                                                                                             |

|              |          |                        | LVV = 1100    | 3.92 | 4.13 | 4.33    | V         |                                                                                             |

|              |          |                        | LVV = 1101    | 4.11 | 4.33 | 4.55    | V         |                                                                                             |

|              |          |                        | LVV = 1110    | 4.41 | 4.64 | 4.87    | V         |                                                                                             |

| D423         | Vbg      | Band Gap Reference     | /oltage Value |      | 1.22 | _       | V         |                                                                                             |

† Production tested at TAMB = 25°C. Specifications over temp. limits ensured by characterization.

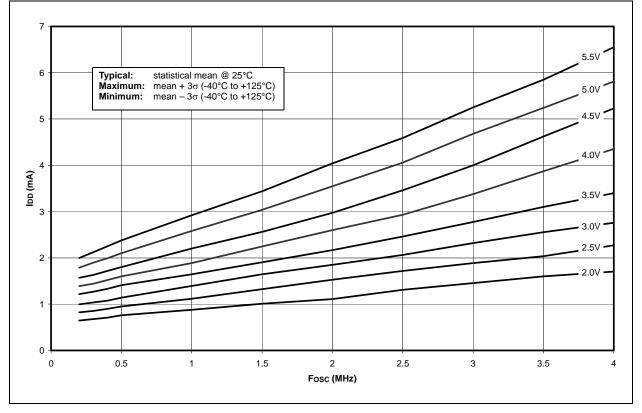

FIGURE 28-27: MINIMUM AND MAXIMUM VIN vs. VDD (I<sup>2</sup>C INPUT, -40°C TO +125°C)

### APPENDIX C: CONVERSION CONSIDERATIONS

This appendix discusses the considerations for converting from previous versions of a device to the ones listed in this data sheet. Typically, these changes are due to the differences in the process technology used. An example of this type of conversion is from a PIC17C756 to a PIC18F8720.

Not Applicable

### APPENDIX D: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in *AN716, "Migrating Designs from PIC16C74A/74B to PIC18C442.*" The changes discussed, while device specific, are generally applicable to all mid-range to enhanced device migrations.

This Application Note is available as Literature Number DS00716.

| L |

|---|

|   |

| - |

| 1                                             |   |

|-----------------------------------------------|---|

| I/O Ports                                     | 3 |

| I <sup>2</sup> C Mode                         |   |

| Associated Registers                          | 2 |

| General Call Address Support                  |   |

|                                               | 0 |

| Master Mode                                   | _ |

| Operation198                                  |   |

| Master Mode Transmit Sequence                 |   |

| Read/Write Bit Information (R/W Bit) 186, 187 | 7 |

| Serial Clock (RC3/SCK/SCL)187                 | 7 |

| ID Locations                                  |   |

| INCF                                          |   |

| INCFSZ                                        | - |

|                                               |   |

| In-Circuit Debugger                           |   |

| Resources (table)274                          | 4 |

| In-Circuit Serial Programming (ICSP)          | 4 |

| Indirect Addressing                           |   |

| INDF and FSR Registers56                      |   |

| Operation                                     |   |

| Indirect Addressing Operation                 |   |

|                                               |   |

| Indirect File Operand47                       |   |

| INFSNZ                                        |   |

| Initialization Conditions for All Registers   | 6 |

| Instruction Flow/Pipelining48                 | 5 |

| Instruction Set                               |   |

| ADDLW                                         | 1 |

| ADDUW                                         |   |

|                                               |   |

| ADDWFC                                        |   |

| ANDLW                                         |   |

| ANDWF                                         | 3 |

| BC                                            | 3 |

| BCF                                           |   |

| BN                                            |   |

| -                                             |   |

| BNC                                           |   |

| BNN285                                        | - |

| BNOV                                          | 6 |

| BNZ                                           | 6 |

| BOV                                           | 9 |

| BRA                                           |   |

| BSF                                           |   |

|                                               |   |

| BTFSC                                         |   |

| BTFSS                                         | - |

| BTG289                                        | 9 |

| BZ                                            | 0 |

| CALL                                          | 0 |

| CLRF                                          |   |

| CLRWDT                                        |   |

|                                               |   |

| COMF                                          |   |

| CPFSEQ                                        |   |

| CPFSGT                                        | 3 |

| CPFSLT                                        | 3 |

| DAW                                           | 4 |

| DCFSNZ                                        |   |

| DECF                                          |   |

| -                                             |   |

| DECFSZ                                        |   |

| Firmware Instructions275                      |   |

| General Format277                             | 7 |