Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.75K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6525t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

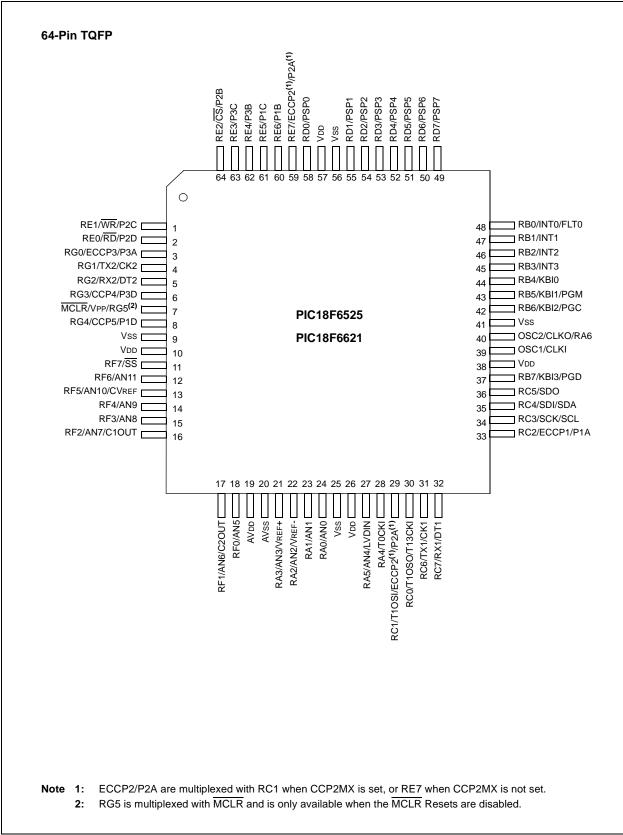

## **Pin Diagrams**

## 4.7.1 TWO-WORD INSTRUCTIONS

The PIC18F6525/6621/8525/8621 devices have four two-word instructions: MOVFF, CALL, GOTO and LFSR. The second word of these instructions has the 4 MSBs set to '1's and is a special kind of NOP instruction. The lower 12 bits of the second word contain data to be used by the instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the second word of the instruction is executed by itself (first word was skipped), it will execute as a NOP. This action is necessary when the two-word instruction is preceded by a conditional instruction that changes the PC. A program example that demonstrates this concept is shown in Example 4-3. Refer to **Section 25.0 "Instruction Set Summary"** for further details of the instruction set.

| EXAMPLE 4-3: | TWO-WORD INSTRUCTIONS |

|--------------|-----------------------|

|              |                       |

| CASE 1:             |                                                   |  |  |  |  |  |  |

|---------------------|---------------------------------------------------|--|--|--|--|--|--|

| Object Code         | Source Code                                       |  |  |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1 ; is RAM location 0?                  |  |  |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 ; No, execute 2-word instruction |  |  |  |  |  |  |

| 1111 0100 0101 0110 | ; 2nd operand holds address of REG2               |  |  |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3 ; continue code                        |  |  |  |  |  |  |

|                     |                                                   |  |  |  |  |  |  |

## CASE 2:

| ••= =.              |                 |                           |

|---------------------|-----------------|---------------------------|

| Object Code         | Source Code     |                           |

| 0110 0110 0000 0000 | TSTFSZ REG1     | ; is RAM location 0?      |

| 1100 0001 0010 0011 | MOVFF REG1, REG | 2 ; Yes                   |

| 1111 0100 0101 0110 |                 | ; 2nd operand becomes NOP |

| 0010 0100 0000 0000 | ADDWF REG3      | ; continue code           |

## 4.8 Look-up Tables

Look-up tables are implemented two ways. These are:

- Computed GOTO

- Table Reads

## 4.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL).

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called

routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions that returns the value 0xnn to the calling function.

The offset value (value in WREG) specifies the number of bytes that the program counter should advance.

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

Note: The ADDWF PCL instruction does not update PCLATH and PCLATU. A read operation on PCL must be performed to update PCLATH and PCLATU.

## EXAMPLE 4-4: COMPUTED GOTO USING AN OFFSET VALUE

| MAIN: | ORG<br>MOVLW<br>CALL                                                              | 0x0000<br>0x00<br>TABLE |                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE | ORG<br>MOVF<br>RLNCF<br>ADDWF<br>RETLW<br>RETLW<br>RETLW<br>RETLW<br>RETLW<br>END | W, W                    | ; A simple read of PCL will update PCLATH, PCLATU<br>; Multiply by 2 to get correct offset in table<br>; Add the modified offset to force jump into table |

| File Name | Bit 7                                                                                                  | Bit 6                                                                                                                                             | Bit 5                     | Bit 4           | Bit 3         | Bit 2         | Bit 1                      | Bit 0       | Value on<br>POR, BOR | Details on page: |

|-----------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------|---------------|---------------|----------------------------|-------------|----------------------|------------------|

| PREINC2   | Uses contents of FSR2 to address data memory – value of FSR2 pre-incremented (not a physical register) |                                                                                                                                                   |                           |                 |               |               |                            |             | N/A                  | 56               |

| PLUSW2    |                                                                                                        | Uses contents of FSR2 to address data memory – value of FSR2 pre-incremented<br>(not a physical register) – value of FSR2 offset by value in WREG |                           |                 |               |               |                            |             | N/A                  | 56               |

| FSR2H     | _                                                                                                      | _                                                                                                                                                 | _                         | _               | Indirect Data | Memory Add    | dress Pointer              | 2 High Byte | 0000                 | 33, 56           |

| FSR2L     | Indirect Data                                                                                          | Memory Add                                                                                                                                        | ress Pointer 2            | Low Byte        | •             |               |                            |             | xxxx xxxx            | 33, 56           |

| STATUS    | —                                                                                                      | —                                                                                                                                                 | —                         | Ν               | OV            | Z             | DC                         | С           | x xxxx               | 33, 58           |

| TMR0H     | Timer0 Regis                                                                                           | ster High Byte                                                                                                                                    |                           | •               |               |               | •                          |             | 0000 0000            | 33, 133          |

| TMR0L     | Timer0 Regis                                                                                           | ster Low Byte                                                                                                                                     |                           |                 |               |               |                            |             | xxxx xxxx            | 33, 133          |

| T0CON     | TMR0ON                                                                                                 | T08BIT                                                                                                                                            | TOCS                      | T0SE            | PSA           | T0PS2         | T0PS1                      | T0PS0       | 1111 1111            | 33, 131          |

| OSCCON    | _                                                                                                      |                                                                                                                                                   | _                         | _               | LOCK          | PLLEN         | SCS1                       | SCS0        | 0000                 | 25, 33           |

| LVDCON    | _                                                                                                      |                                                                                                                                                   | IRVST                     | LVDEN           | LVDL3         | LVDL2         | LVDL1                      | LVDL0       | 00 0101              | 33, 255          |

| WDTCON    | _                                                                                                      |                                                                                                                                                   | _                         | _               | _             | _             | _                          | SWDTEN      | 0                    | 33, 267          |

| RCON      | IPEN                                                                                                   | _                                                                                                                                                 | _                         | RI              | TO            | PD            | POR                        | BOR         | 01 11qq              | 33, 59,<br>101   |

| TMR1H     | Timer1 Regis                                                                                           | ster High Byte                                                                                                                                    | 1                         | •               |               |               | •                          |             | xxxx xxxx            | 33, 139          |

| TMR1L     | Timer1 Regis                                                                                           | ster Low Byte                                                                                                                                     |                           |                 |               |               |                            |             | xxxx xxxx            | 33, 139          |

| T1CON     | RD16                                                                                                   |                                                                                                                                                   | T1CKPS1                   | T1CKPS0         | T1OSCEN       | T1SYNC        | TMR1CS                     | TMR10N      | 0-00 0000            | 33, 139          |

| TMR2      | Timer2 Regis                                                                                           | ster                                                                                                                                              |                           |                 |               |               |                            |             | 0000 0000            | 33, 142          |

| PR2       | Timer2 Perio                                                                                           | d Register                                                                                                                                        |                           |                 |               |               |                            |             | 1111 1111            | 33, 142          |

| T2CON     |                                                                                                        | T2OUTPS3                                                                                                                                          | T2OUTPS2                  | T2OUTPS1        | T2OUTPS0      | TMR2ON        | T2CKPS1                    | T2CKPS0     | -000 0000            | 33, 142          |

| SSPBUF    | MSSP Recei                                                                                             | ve Buffer/Trar                                                                                                                                    | nsmit Register            |                 |               |               |                            |             | xxxx xxxx            | 33, 181          |

| SSPADD    | MSSP Addre                                                                                             | ess Register ir                                                                                                                                   | I <sup>2</sup> C Slave mo | ode. MSSP Ba    | aud Rate Relo | ad Register i | in I <sup>2</sup> C Master | mode.       | 0000 0000            | 33, 181          |

| SSPSTAT   | SMP                                                                                                    | CKE                                                                                                                                               | D/A                       | Р               | S             | R/W           | UA                         | BF          | 0000 0000            | 33, 174          |

| SSPCON1   | WCOL                                                                                                   | SSPOV                                                                                                                                             | SSPEN                     | CKP             | SSPM3         | SSPM2         | SSPM1                      | SSPM0       | 0000 0000            | 33, 175          |

| SSPCON2   | GCEN                                                                                                   | ACKSTAT                                                                                                                                           | ACKDT                     | ACKEN           | RCEN          | PEN           | RSEN                       | SEN         | 0000 0000            | 33, 185          |

| ADRESH    | A/D Result R                                                                                           | egister High E                                                                                                                                    | Byte                      |                 |               |               |                            |             | XXXX XXXX            | 33, 241          |

| ADRESL    | A/D Result R                                                                                           | legister Low E                                                                                                                                    | Byte                      |                 |               |               |                            |             | xxxx xxxx            | 33, 241          |

| ADCON0    | _                                                                                                      | _                                                                                                                                                 | CHS3                      | CHS2            | CHS1          | CHS0          | GO/DONE                    | ADON        | 00 0000              | 34, 233          |

| ADCON1    | _                                                                                                      |                                                                                                                                                   | VCFG1                     | VCFG0           | PCFG3         | PCFG2         | PCFG1                      | PCFG0       | 00 0000              | 34, 234          |

| ADCON2    | ADFM                                                                                                   |                                                                                                                                                   | ACQT2                     | ACQT1           | ACQT0         | ADCS2         | ADCS1                      | ADCS0       | 0-00 0000            | 34, 235          |

| CCPR1H    | Enhanced C                                                                                             | apture/Compa                                                                                                                                      | are/PWM Regi              | ister 1 High By |               |               |                            |             | XXXX XXXX            | 34, 172          |

| CCPR1L    | Enhanced C                                                                                             | apture/Compa                                                                                                                                      | are/PWM Regi              | ister 1 Low By  | te            |               |                            |             | XXXX XXXX            | 34, 172          |

| CCP1CON   | P1M1                                                                                                   | . P1M0                                                                                                                                            | DC1B1                     | DC1B0           | CCP1M3        | CCP1M2        | CCP1M1                     | CCP1M0      | 0000 0000            | 34, 157          |

| CCPR2H    |                                                                                                        |                                                                                                                                                   |                           | ister 2 High By |               |               |                            |             | XXXX XXXX            | 34, 172          |

| CCPR2L    | Enhanced C                                                                                             | apture/Compa                                                                                                                                      | are/PWM Regi              | ister 2 Low By  | te            |               |                            |             | xxxx xxxx            | 34, 172          |

| CCP2CON   | P2M1                                                                                                   | P2M0                                                                                                                                              | DC2B1                     | DC2B0           | CCP2M3        | CCP2M2        | CCP2M1                     | CCP2M0      | 0000 0000            | 34, 157          |

| CCPR3H    |                                                                                                        |                                                                                                                                                   |                           | ister 3 High By |               |               | L                          | 1           | xxxx xxxx            | 34, 172          |

| CCPR3L    |                                                                                                        |                                                                                                                                                   | 0                         | ister 3 Low By  |               |               |                            |             | xxxx xxxx            | 34, 172          |

| CCP3CON   | P3M1                                                                                                   | P3M0                                                                                                                                              | DC3B1                     | DC2B0           | CCP3M3        | CCP3M2        | CCP3M1                     | CCP3M0      | 0000 0000            | 34, 157          |

| 001 3001  |                                                                                                        |                                                                                                                                                   |                           | l               |               |               |                            |             |                      |                  |

| ECCP1AS   | ECCP1ASE                                                                                               | ECCP1AS2                                                                                                                                          | ECCP1AS1                  | ECCP1AS0        | PSS1AC1       | PSS1AC0       | PSS1BD1                    | PSS1BD0     | 0000 0000            | 34, 169          |

## TABLE 4-3: REGISTER FILE SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: RA6 and associated bits are configured as a port pin in RCIO and ECIO Oscillator modes only and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: These registers are unused on PIC18F6525/6621 devices and read as '0'.

4: RG5 is available only if MCLR function is disabled in configuration.

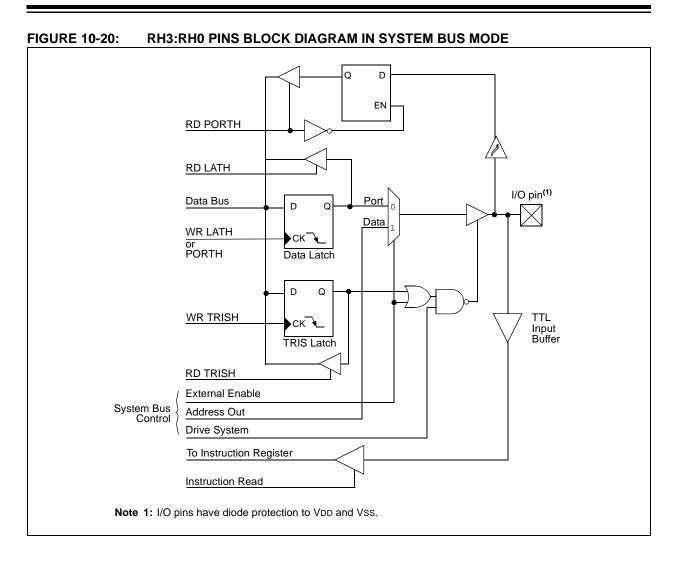

5: Enabled only in Microcontroller mode for PIC18F8525/8621 devices.

## 7.0 DATA EEPROM MEMORY

The data EEPROM is readable and writable during normal operation over the entire VDD range. The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are five SFRs used to read and write the program and data EEPROM memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADRH

- EEADR

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write. EEADR and EEADRH hold the address of the EEPROM location being accessed. These devices have 1024 bytes of data EEPROM with an address range from 00h to 3FFh.

The EEPROM data memory is rated for high erase/ write cycles. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip-to-chip. Please refer to parameter D122 (Section 27.0 "Electrical Characteristics") for exact limits.

## 7.1 EEADR and EEADRH

The address register pair can address up to a maximum of 1024 bytes of data EEPROM. The two Most Significant bits of the address are stored in EEADRH, while the remaining eight Least Significant bits are stored in EEADR. The six Most Significant bits of EEADRH are unused and are read as '0'.

## 7.2 EECON1 and EECON2 Registers

EECON1 is the control register for EEPROM memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

Control bits RD and WR initiate read and write operations, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at the completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

| Note: | During normal operation, the WRERR bit         |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|

|       | is read as '1'. This can indicate that a write |  |  |  |  |  |  |

|       | operation was prematurely terminated by        |  |  |  |  |  |  |

|       | a Reset, or a write operation was              |  |  |  |  |  |  |

|       | attempted improperly.                          |  |  |  |  |  |  |

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR) due to the Reset condition forcing the contents of the registers to zero.

**Note:** Interrupt flag bit, EEIF in the PIR2 register, is set when write is complete. It must be cleared in software.

## 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2 and PIE3). When the IPEN bit (RCON<7>) is '0', the PEIE bit must be set to enable any of these peripheral interrupts.

| <b>REGISTER 9-7:</b>                                                                                                  | PIE1: PER                                                                                   | IPHERAL                        | INTERRU                       | PT ENABL       | E REGIST      | ER 1       |             |        |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|----------------|---------------|------------|-------------|--------|

|                                                                                                                       | R/W-0                                                                                       | R/W-0                          | R/W-0                         | R/W-0          | R/W-0         | R/W-0      | R/W-0       | R/W-0  |

|                                                                                                                       | PSPIE <sup>(1)</sup>                                                                        | ADIE                           | RC1IE                         | TX1IE          | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE |

|                                                                                                                       | bit 7                                                                                       |                                |                               |                |               |            |             | bit 0  |

| bit 7                                                                                                                 | <b>PSPIE:</b> Par                                                                           | allel Slave I                  | Port Read/W                   | /rite Interrup | ot Enable bit | (1)        |             |        |

|                                                                                                                       |                                                                                             |                                | ead/write in<br>read/write ir |                |               |            |             |        |

|                                                                                                                       | Note:                                                                                       | Enabled or                     | ly in Microc                  | ontroller mo   | de for PIC18  | 3F8525/862 | 1 devices.  |        |

| bit 6                                                                                                                 | ADIE: A/D                                                                                   | Converter Ir                   | nterrupt Ena                  | ble bit        |               |            |             |        |

|                                                                                                                       |                                                                                             | es the A/D in<br>es the A/D in |                               |                |               |            |             |        |

| bit 5                                                                                                                 | RC1IE: US                                                                                   | ART1 Rece                      | ive Interrupt                 | Enable bit     |               |            |             |        |

|                                                                                                                       |                                                                                             |                                | RT1 receive<br>RT1 receive    |                |               |            |             |        |

| bit 4                                                                                                                 | TX1IE: USA                                                                                  | ART1 Trans                     | mit Interrupt                 | Enable bit     |               |            |             |        |

|                                                                                                                       |                                                                                             |                                | RT1 transmit<br>RT1 transmi   |                |               |            |             |        |

| bit 3                                                                                                                 | SSPIE: Ma                                                                                   | ster Synchro                   | onous Seria                   | l Port Interru | ipt Enable b  | it         |             |        |

|                                                                                                                       | <ul> <li>1 = Enables the MSSP interrupt</li> <li>0 = Disables the MSSP interrupt</li> </ul> |                                |                               |                |               |            |             |        |

| bit 2                                                                                                                 | CCP1IE: E                                                                                   | CCP1 Interr                    | upt Enable I                  | oit            |               |            |             |        |

| <ul><li>1 = Enables the ECCP1 interrupt</li><li>0 = Disables the ECCP1 interrupt</li></ul>                            |                                                                                             |                                |                               |                |               |            |             |        |

| bit 1                                                                                                                 | bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit                                        |                                |                               |                |               |            |             |        |

| <ul> <li>1 = Enables the TMR2 to PR2 match interrupt</li> <li>0 = Disables the TMR2 to PR2 match interrupt</li> </ul> |                                                                                             |                                |                               |                |               |            |             |        |

| bit 0                                                                                                                 | TMR1IE: T                                                                                   | MR1 Overflo                    | ow Interrupt                  | Enable bit     |               |            |             |        |

|                                                                                                                       |                                                                                             |                                | overflow in<br>1 overflow ir  | •              |               |            |             |        |

|                                                                                                                       | Legend:                                                                                     |                                |                               |                |               |            |             | ]      |

|                                                                                                                       | R – Readal                                                                                  | hla hit                        | $\lambda / - \lambda $        | ritable hit    | II – I Inim   | nlemented  | hit read as | 'O'    |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 15.0 TIMER4 MODULE

The Timer4 module timer has the following features:

- 8-bit timer (TMR4 register)

- 8-bit period register (PR4)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR4 match of PR4

Timer4 has a control register shown in Register 15-1. Timer4 can be shut off by clearing control bit, TMR4ON (T4CON<2>), to minimize power consumption. The prescaler and postscaler selection of Timer4 are also controlled by this register. Figure 15-1 is a simplified block diagram of the Timer4 module.

#### 15.1 **Timer4 Operation**

Timer4 can be used as the PWM time base for the PWM mode of the CCP module. The TMR4 register is readable and writable and is cleared on any device Reset. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T4CKPS1:T4CKPS0 (T4CON<1:0>). The match output of TMR4 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR4 interrupt, latched in flag bit TMR4IF (PIR3<3>).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR4 register

- a write to the T4CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR4 is not cleared when T4CON is written.

## REGISTER 15-1: T4CON: TIMER4 CONTROL REGISTER

|   | U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|---|-------|----------|----------|----------|----------|--------|---------|---------|

| ſ | —     | T4OUTPS3 | T4OUTPS2 | T4OUTPS1 | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 |

| _ | bit 7 |          |          |          |          |        |         | bit 0   |

#### bit 7 Unimplemented: Read as '0'

|       | 0000 = 1:1 Postscale  |  |

|-------|-----------------------|--|

|       | 0001 = 1:2 Postscale  |  |

|       | •                     |  |

|       | •                     |  |

|       | •                     |  |

|       | 1111 = 1:16 Postscale |  |

| bit 2 | TMR4ON: Timer4 On bit |  |

|       | 1 = Timer4 is on      |  |

|       | 0 – Timer/Lis off     |  |

0 = Timer4 is off

### bit 1-0 T4CKPS1:T4CKPS0: Timer4 Clock Prescale Select bits

- 00 = Prescaler is 1

- 01 = Prescaler is 4

- 1x = Prescaler is 16

### Leaend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

|                                   |                  |                                    |                    |  |  |

|         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                  | R/W-0                 | R/W-0           | R/W-0        | R/W-0        | R/W-0        | R/W-0      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------|-----------------|--------------|--------------|--------------|------------|

|         | WCOL                                                                                                                                                                                                                                                                                                                                                                                            | SSPOV                                  | SSPEN                 | CKP             | SSPM3        | SSPM2        | SSPM1        | SSPM0      |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                           |                                        |                       |                 |              |              |              | bit 0      |

| bit 7   | <ul> <li>WCOL: Write Collision Detect bit (Transmit mode only)</li> <li>1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)</li> </ul>                                                                                                                                                                                            |                                        |                       |                 |              |              |              |            |

|         | 0 = No col                                                                                                                                                                                                                                                                                                                                                                                      |                                        | ,                     |                 |              |              |              |            |

| bit 6   | SSPOV: R                                                                                                                                                                                                                                                                                                                                                                                        | eceive Overf                           | low Indicato          | r bit           |              |              |              |            |

|         | SPI Slave                                                                                                                                                                                                                                                                                                                                                                                       |                                        |                       |                 |              |              |              |            |

|         | <ul> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).</li> <li>0 = No overflow</li> </ul>                                            |                                        |                       |                 |              |              |              |            |

|         | <b>Note:</b> In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.                                                                                                                                                                                                                                            |                                        |                       |                 |              |              | eption (and  |            |

| bit 5   | SSPEN: M                                                                                                                                                                                                                                                                                                                                                                                        | aster Synchi                           | ronous Seria          | l Port Enab     | le bit       |              |              |            |

|         |                                                                                                                                                                                                                                                                                                                                                                                                 | s serial port                          | •                     |                 |              |              | l port pins  |            |

|         | <ul> <li>Disables serial port and configures these pins as I/O port pins</li> <li>Note: When enabled, these pins must be properly configured as input or output.</li> </ul>                                                                                                                                                                                                                     |                                        |                       |                 |              |              | Nut          |            |

| bit 4   |                                                                                                                                                                                                                                                                                                                                                                                                 | k Polarity Se                          | •                     |                 | property cer | inguiou do i | iput of outp |            |

| DIL 4   |                                                                                                                                                                                                                                                                                                                                                                                                 | te for clock i                         |                       | 2               |              |              |              |            |

|         |                                                                                                                                                                                                                                                                                                                                                                                                 | te for clock i                         | 0                     |                 |              |              |              |            |

| bit 3-0 | SSPM3:SS                                                                                                                                                                                                                                                                                                                                                                                        | SPM0: Maste                            | r Synchrond           | ous Serial Po   | ort Mode Se  | lect bits    |              |            |

|         | <ul> <li>0101 = SPI Slave mode, clock = SCK pin, SS pin control disabled, SS can be used as I/O pin</li> <li>0100 = SPI Slave mode, clock = SCK pin, SS pin control enabled</li> <li>0011 = SPI Master mode, clock = TMR2 output/2</li> <li>0010 = SPI Master mode, clock = Fosc/64</li> <li>0001 = SPI Master mode, clock = Fosc/16</li> <li>0000 = SPI Master mode, clock = Fosc/4</li> </ul> |                                        |                       |                 |              |              |              |            |

|         | Note:                                                                                                                                                                                                                                                                                                                                                                                           | Bit combina<br>I <sup>2</sup> C mode o | itions not sp<br>nly. | ecifically list | ed here are  | either resei | ved or impl  | emented in |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                         |                                        |                       |                 |              |              |              |            |

|         | R = Reada                                                                                                                                                                                                                                                                                                                                                                                       | hle hit                                | W = Writab            | le hit          | LI = Unimp   | lemented bit | read as '0   | ,          |

### SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE) **REGISTER 18-2:**

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

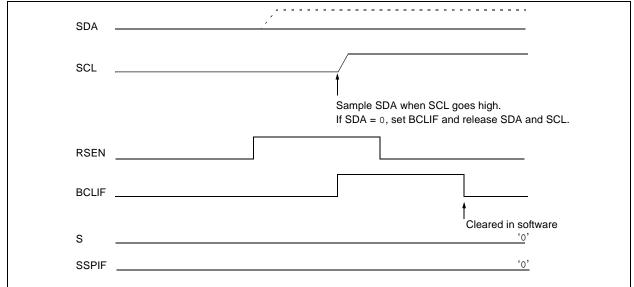

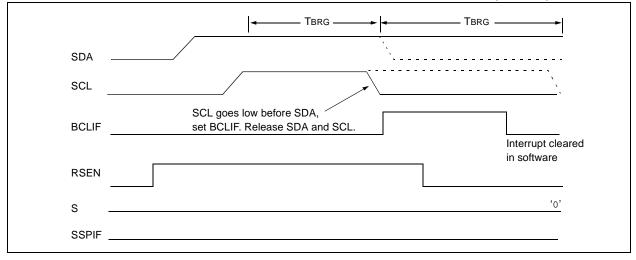

## 18.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to '0'. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 18-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 18-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 18-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### FIGURE 18-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

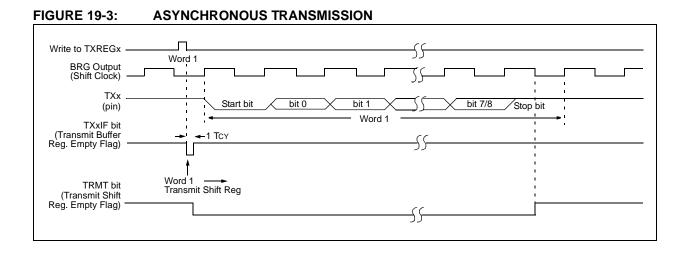

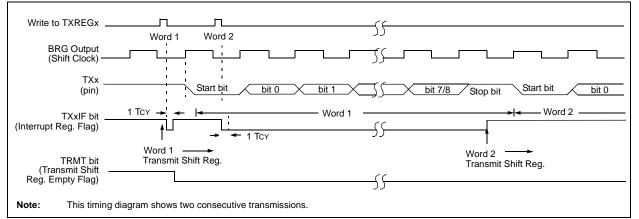

## FIGURE 19-4: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

### TABLE 19-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name      | Bit 7                | Bit 6        | Bit 5      | Bit 4     | Bit 3       | Bit 2      | Bit 1         | Bit 0       | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------|----------------------|--------------|------------|-----------|-------------|------------|---------------|-------------|----------------------|---------------------------------|

| INTCON    | GIE/GIEH             | PEIE/GIEL    | TMR0IE     | INTOIE    | RBIE        | TMR0IF     | <b>INT0IF</b> | RBIF        | 0000 000x            | 0000 000u                       |

| PIR1      | PSPIF <sup>(1)</sup> | ADIF         | RC1IF      | TX1IF     | SSPIF       | CCP1IF     | TMR2IF        | TMR1IF      | 0000 0000            | 0000 0000                       |

| PIE1      | PSPIE <sup>(1)</sup> | ADIE         | RC1IE      | TX1IE     | SSPIE       | CCP1IE     | TMR2IE        | TMR1IE      | 0000 0000            | 0000 0000                       |

| IPR1      | PSPIP <sup>(1)</sup> | ADIP         | RC1IP      | TX1IP     | SSPIP       | CCP1IP     | TMR2IP        | TMR1IP      | 1111 1111            | 1111 1111                       |

| PIR3      | _                    | _            | RC2IF      | TX2IF     | TMR4IF      | CCP5IF     | CCP4IF        | CCP3IF      | 00 0000              | 00 0000                         |

| PIE3      | —                    | _            | RC2IE      | TX2IE     | TMR4IE      | CCP5IE     | CCP4IE        | CCP3IE      | 00 0000              | 00 0000                         |

| IPR3      | —                    | _            | RC2IP      | TX2IP     | TMR4IP      | CCP5IP     | CCP4IP        | CCP3IP      | 11 1111              | 11 1111                         |

| RCSTAx    | SPEN                 | RX9          | SREN       | CREN      | ADDEN       | FERR       | OERR          | RX9D        | 0000 000x            | 0000 000x                       |

| TXREGx    | Enhanced U           | SARTx Trans  | mit Regist | er        |             |            |               |             | 0000 0000            | 0000 0000                       |

| TXSTAx    | CSRC                 | TX9          | TXEN       | SYNC      | SENDB       | BRGH       | TRMT          | TX9D        | 0000 0010            | 0000 0010                       |

| BAUDCONx  | _                    | RCIDL        |            | SCKP      | BRG16       | _          | WUE           | ABDEN       | -1-0 0-00            | -1-0 0-00                       |

| SPBRGHx   | Enhanced U           | SARTx Baud   | Rate Gene  | erator Re | gister High | Byte       |               |             | 0000 0000            | 0000 0000                       |

| SPBRGx    | Enhanced U           | SARTx Baud   | Rate Gen   | erator Re | gister Low  | Byte       |               |             | 0000 0000            | 0000 0000                       |

| legend: v | - unknown            | – – unimplem | ented loca | tions roa | d as 'o' Sh | aded cells | are not us    | ad for asyn | hronous transi       | mission                         |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

**Note 1:** Enabled only in Microcontroller mode for PIC18F8525/8621 devices.

## 20.4 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as a digital input will convert as an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- Analog levels on any pin defined as a digital input may cause the input buffer to consume current out of the device's specification limits.

## 20.5 A/D Conversions

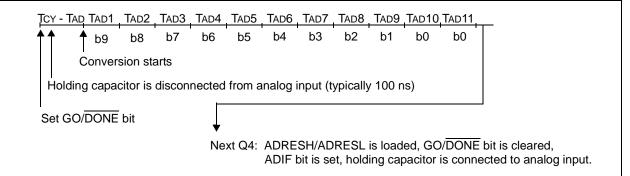

Figure 20-3 shows the operation of the A/D converter after the GODONE bit has been set. Clearing the GO/ DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

## FIGURE 20-3: A/D CONVERSION TAD CYCLES

| BNC                                                         | ov              | Branch if                                                                                 | Branch if Not Overflow                                                                                                                                                                                                                                                                     |                 |  |  |  |  |

|-------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Syntax:                                                     |                 | [label] BN                                                                                | [ <i>label</i> ] BNOV n                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Oper                                                        | ands:           | -128 ≤ n ≤ 1                                                                              | 27                                                                                                                                                                                                                                                                                         |                 |  |  |  |  |

| Oper                                                        | ation:          | if Overflow<br>(PC) + 2 -                                                                 | bit is '0'<br>+ 2n → PC                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Statu                                                       | s Affected:     | None                                                                                      |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Enco                                                        | ding:           | 1110                                                                                      | 0101 nr                                                                                                                                                                                                                                                                                    | inn nnnn        |  |  |  |  |

| Description:                                                |                 | program will<br>The 2's con<br>added to the<br>incremented<br>instruction,<br>PC + 2 + 2r | If the Overflow bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                 |  |  |  |  |

| Word                                                        | ls:             | 1                                                                                         |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Cycles:                                                     |                 | 1(2)                                                                                      | 1(2)                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |

| Q Cycle Activity:<br>If Jump:                               |                 |                                                                                           |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

|                                                             | Q1              | Q2                                                                                        | Q3                                                                                                                                                                                                                                                                                         | Q4              |  |  |  |  |

|                                                             | Decode          | Read literal<br>'n'                                                                       | Process<br>Data                                                                                                                                                                                                                                                                            | Write to PC     |  |  |  |  |

|                                                             | No<br>operation | No<br>operation                                                                           | No<br>operation                                                                                                                                                                                                                                                                            | No<br>operation |  |  |  |  |

| If No                                                       | o Jump:         |                                                                                           |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| 1                                                           | Q1              | Q2                                                                                        | Q3                                                                                                                                                                                                                                                                                         | Q4              |  |  |  |  |

|                                                             | Decode          | Read literal<br>'n'                                                                       | Process<br>Data                                                                                                                                                                                                                                                                            | No<br>operation |  |  |  |  |

| Exam                                                        | <u>nple:</u>    | HERE                                                                                      | BNOV Jum                                                                                                                                                                                                                                                                                   | ò               |  |  |  |  |

| Before Instructi<br>PC                                      |                 | = ade                                                                                     | = address (HERE)                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| After Instruction<br>If Overflow<br>PC<br>If Overflow<br>PC |                 | ow = 0;<br>= ado<br>ow = 1;                                                               | dress (Jumg<br>dress (HERE                                                                                                                                                                                                                                                                 |                 |  |  |  |  |

| BNZ                   | Branch i                                                                         | Branch if Not Zero                                                                                                                                                                                                                                                                     |             |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| Syntax:               | [ <i>label</i> ] B                                                               | [ <i>label</i> ] BNZ n                                                                                                                                                                                                                                                                 |             |  |  |  |  |

| Operands:             | -128 ≤ n ≤                                                                       | 127                                                                                                                                                                                                                                                                                    |             |  |  |  |  |

| Operation:            |                                                                                  | if Zero bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                   |             |  |  |  |  |

| Status Affected       | l: None                                                                          |                                                                                                                                                                                                                                                                                        |             |  |  |  |  |

| Encoding:             | 1110                                                                             | 0001 nn:                                                                                                                                                                                                                                                                               | nn nnnn     |  |  |  |  |

| Description:          | program w<br>The 2's co<br>added to tl<br>increment<br>instruction<br>PC + 2 + 2 | If the Zero bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |             |  |  |  |  |

| Words:                | 1                                                                                | 1                                                                                                                                                                                                                                                                                      |             |  |  |  |  |

| Cycles:               | 1(2)                                                                             | 1(2)                                                                                                                                                                                                                                                                                   |             |  |  |  |  |

| Q Cycle Activ         |                                                                                  |                                                                                                                                                                                                                                                                                        |             |  |  |  |  |

| Q1                    | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                     | Q4          |  |  |  |  |

| Decod                 | e Read literal<br>'n'                                                            | Process<br>Data                                                                                                                                                                                                                                                                        | Write to PC |  |  |  |  |

| No                    | No                                                                               | No                                                                                                                                                                                                                                                                                     | No          |  |  |  |  |

| operati               | on operation                                                                     | operation                                                                                                                                                                                                                                                                              | operation   |  |  |  |  |

| If No Jump:           |                                                                                  |                                                                                                                                                                                                                                                                                        |             |  |  |  |  |

| Q1                    | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                     | Q4          |  |  |  |  |

| Decod                 | e Read literal                                                                   | Process                                                                                                                                                                                                                                                                                | No          |  |  |  |  |

|                       | 'n'                                                                              | Data                                                                                                                                                                                                                                                                                   | operation   |  |  |  |  |

| Example:<br>Before In | HERE                                                                             | BNZ Jump                                                                                                                                                                                                                                                                               |             |  |  |  |  |

Before Instruction PC = address (HERE) After Instruction If Zero = 0; PC = address (Jump) If Zero = 1; PC = address (HERE + 2)