Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.75K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6621-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.6.2 OSCILLATOR TRANSITIONS

PIC18F6525/6621/8525/8621 devices contain circuitry to prevent "glitches" when switching between oscillator sources. Essentially, the circuitry waits for eight rising edges of the clock source that the processor is switching to. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

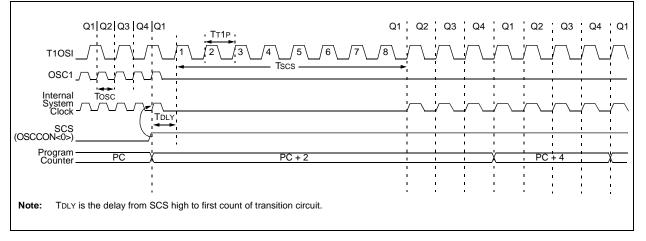

A timing diagram indicating the transition from the main oscillator to the Timer1 oscillator is shown in Figure 2-8. The Timer1 oscillator is assumed to be running all the time. After the SCS0 bit is set, the processor is frozen at the next occurring Q1 cycle. After eight synchronization cycles are counted from the Timer1 oscillator, operation resumes. No additional delays are required after the synchronization cycles.

# FIGURE 2-8: TIMING DIAGRAM FOR TRANSITION FROM OSC1 TO TIMER1 OSCILLATOR

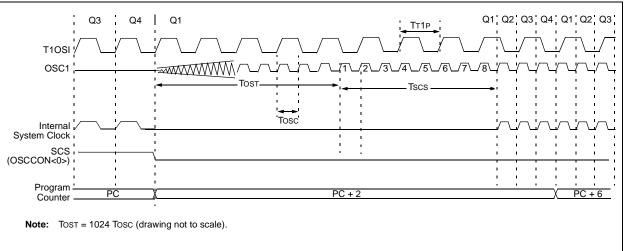

The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will depend on the mode of the main oscillator. In addition to eight clock cycles of the main oscillator, additional delays may take place. If the main oscillator is configured for an external crystal (HS, XT, LP), then the transition will take place after an oscillator start-up time (TOST) has occurred. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for HS, XT and LP modes, is shown in Figure 2-9.

### FIGURE 2-9: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS, XT, LP)

# 3.1 Power-on Reset (POR)

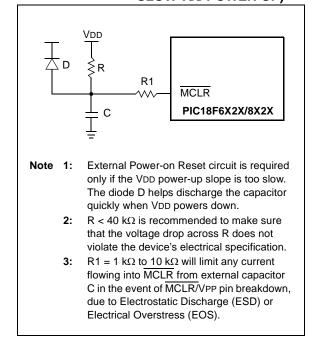

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, tie the MCLR pin through a 1 k $\Omega$  to 10 k $\Omega$  resistor to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

FIGURE 3-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

# 3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter 33) only on power-up from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameter 33 for details.

# 3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delays after the PWRT delay is over (parameter 32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from Sleep.

### 3.4 PLL Lock Time-out

With the PLL enabled, the time-out sequence following a Power-on Reset is different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

# 3.5 Brown-out Reset (BOR)

A configuration bit, BOR, can disable (if clear/ programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below parameter D005 for greater than parameter 35, the brown-out situation will reset the chip. A Reset may not occur if VDD falls below parameter D005 for less than parameter 35. The chip will remain in Brown-out Reset until VDD rises above BVDD. If the Power-up Timer is enabled, it will be invoked after VDD rises above BVDD; it then will keep the chip in Reset for an additional time delay (parameter 33). If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute the additional time delay.

### 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired. Then, OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-6 and Figure 3-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, the time-outs will expire if MCLR is kept low long enough. Bringing MCLR high will begin execution immediately (Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC18F6525/6621/8525/ 8621 device operating in parallel.

Table 3-2 shows the Reset conditions for some Special Function Registers, while Table 3-3 shows the Reset conditions for all of the registers.

### 9.1 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 9-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|----------|-----------|--------|--------|-------|--------|--------|-------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7    |           |        |        |       |        |        | bit 0 |

bit 7 **GIE/GIEH:** Global Interrupt Enable bit When IPEN (RCON<7>) = 0: 1 = Enables all unmasked interrupts 0 = Disables all interrupts When IPEN (RCON<7>) = 1: 1 = Enables all high priority interrupts 0 = Disables all interrupts bit 6 PEIE/GIEL: Peripheral Interrupt Enable bit When IPEN (RCON<7>) = 0: 1 = Enables all unmasked peripheral interrupts 0 = Disables all peripheral interrupts When IPEN (RCON<7>) = 1: 1 = Enables all low priority peripheral interrupts 0 = Disables all low priority peripheral interrupts bit 5 TMR0IE: TMR0 Overflow Interrupt Enable bit 1 = Enables the TMR0 overflow interrupt 0 = Disables the TMR0 overflow interrupt bit 4 INTOIE: INTO External Interrupt Enable bit 1 = Enables the INT0 external interrupt 0 = Disables the INT0 external interrupt bit 3 RBIE: RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt 0 = Disables the RB port change interrupt bit 2 TMR0IF: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software) 0 = TMR0 register did not overflow bit 1 **INTOIF:** INTO External Interrupt Flag bit 1 = The INT0 external interrupt occurred (must be cleared in software) 0 = The INT0 external interrupt did not occur **RBIF:** RB Port Change Interrupt Flag bit bit 0 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software) 0 = None of the RB7:RB4 pins have changed state A mismatch condition will continue to set this bit. Reading PORTB will end the Note: mismatch condition and allow the bit to be cleared.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2 and PIE3). When the IPEN bit (RCON<7>) is '0', the PEIE bit must be set to enable any of these peripheral interrupts.

| <b>REGISTER 9-7:</b>                                                                                                                                                            | PIE1: PER                                                                                     | IPHERAL                                                    | INTERRU                       | PT ENABL       | E REGIST      | ER 1       |             |        |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------|----------------|---------------|------------|-------------|--------|--|

|                                                                                                                                                                                 | R/W-0                                                                                         | R/W-0                                                      | R/W-0                         | R/W-0          | R/W-0         | R/W-0      | R/W-0       | R/W-0  |  |

|                                                                                                                                                                                 | PSPIE <sup>(1)</sup>                                                                          | ADIE                                                       | RC1IE                         | TX1IE          | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE |  |

|                                                                                                                                                                                 | bit 7                                                                                         |                                                            |                               |                |               |            |             | bit 0  |  |

| bit 7                                                                                                                                                                           | <b>PSPIE:</b> Par                                                                             | allel Slave I                                              | Port Read/W                   | /rite Interrup | ot Enable bit | (1)        |             |        |  |

|                                                                                                                                                                                 |                                                                                               |                                                            | ead/write in<br>read/write ir |                |               |            |             |        |  |

|                                                                                                                                                                                 | Note:                                                                                         | Enabled or                                                 | ly in Microc                  | ontroller mo   | de for PIC18  | 3F8525/862 | 1 devices.  |        |  |

| bit 6                                                                                                                                                                           | ADIE: A/D                                                                                     | Converter Ir                                               | nterrupt Ena                  | ble bit        |               |            |             |        |  |

|                                                                                                                                                                                 |                                                                                               | es the A/D in<br>es the A/D in                             |                               |                |               |            |             |        |  |

| bit 5                                                                                                                                                                           | RC1IE: US                                                                                     | ART1 Rece                                                  | ive Interrupt                 | Enable bit     |               |            |             |        |  |

|                                                                                                                                                                                 |                                                                                               |                                                            | RT1 receive<br>RT1 receive    |                |               |            |             |        |  |

| bit 4                                                                                                                                                                           | TX1IE: USA                                                                                    | ART1 Trans                                                 | mit Interrupt                 | Enable bit     |               |            |             |        |  |

|                                                                                                                                                                                 |                                                                                               |                                                            | RT1 transmit<br>RT1 transmi   |                |               |            |             |        |  |

| bit 3                                                                                                                                                                           | SSPIE: Ma                                                                                     | SSPIE: Master Synchronous Serial Port Interrupt Enable bit |                               |                |               |            |             |        |  |

|                                                                                                                                                                                 | <ul> <li>1 = Enables the MSSP interrupt</li> <li>0 = Disables the MSSP interrupt</li> </ul>   |                                                            |                               |                |               |            |             |        |  |

| bit 2                                                                                                                                                                           | CCP1IE: ECCP1 Interrupt Enable bit                                                            |                                                            |                               |                |               |            |             |        |  |

|                                                                                                                                                                                 | <ul> <li>1 = Enables the ECCP1 interrupt</li> <li>0 = Disables the ECCP1 interrupt</li> </ul> |                                                            |                               |                |               |            |             |        |  |

| bit 1                                                                                                                                                                           | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit                                                |                                                            |                               |                |               |            |             |        |  |

| <ul> <li>1 = Enables the TMR2 to PR2 match interrupt</li> <li>0 = Disables the TMR2 to PR2 match interrupt</li> <li>bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit</li> </ul> |                                                                                               |                                                            |                               |                |               |            |             |        |  |

|                                                                                                                                                                                 |                                                                                               |                                                            |                               |                |               |            |             |        |  |

|                                                                                                                                                                                 |                                                                                               |                                                            | overflow in<br>1 overflow ir  | •              |               |            |             |        |  |

|                                                                                                                                                                                 | Legend:                                                                                       |                                                            |                               |                |               |            |             | ]      |  |

|                                                                                                                                                                                 | R – Readal                                                                                    | hla hit                                                    | $\lambda / - \lambda $        | ritable hit    | II – I Inim   | nlemented  | hit read as | 'O'    |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

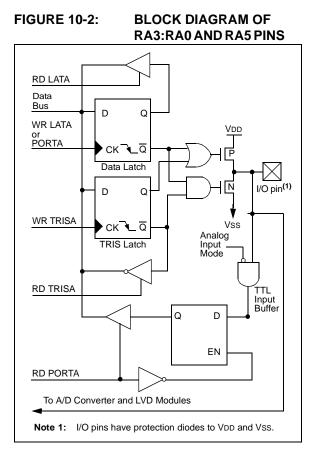

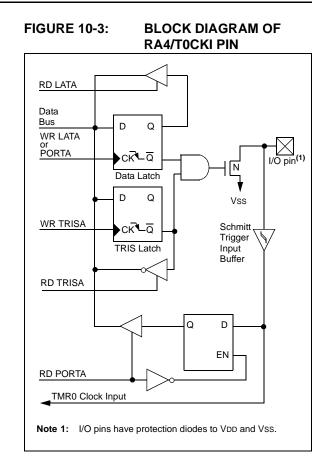

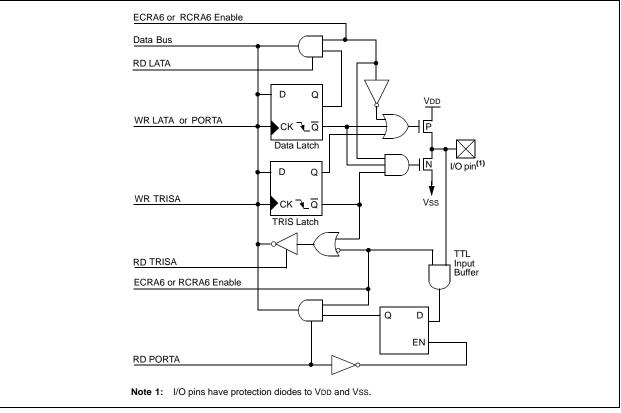

# FIGURE 10-4: BLOCK DIAGRAM OF RA6 PIN (WHEN ENABLED AS I/O)

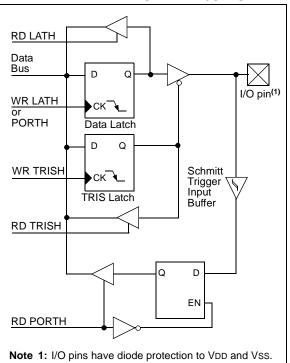

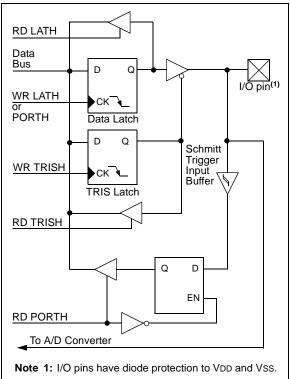

# 10.8 PORTH, LATH and TRISH Registers

| Note: | PORTH is available only on PIC18F8525/ |

|-------|----------------------------------------|

|       | 8621 devices.                          |

PORTH is an 8-bit wide, bidirectional I/O port. The corresponding data direction register is TRISH. Setting a TRISH bit (= 1) will make the corresponding PORTH pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISH bit (= 0) will make the corresponding PORTH pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATH register, read and write the latched output value for PORTH.

Pins RH7:RH4 are multiplexed with analog inputs AN15:AN12. Pins RH3:RH0 are multiplexed with the system bus as the external memory interface; they are the high-order address bits A19:A16. By default, pins RH7:RH4 are enabled as A/D inputs and pins RH3:RH0 are enabled as the system address bus. Register ADCON1 configures RH7:RH4 as I/O or A/D inputs. Register MEMCON configures RH3:RH0 as I/O or system bus pins.

- Note 1: On Power-on Reset, PORTH pins RH7:RH4 default to A/D inputs and read as '0'.

- 2: On Power-on Reset, PORTH pins RH3:RH0 default to system bus signals.

#### EXAMPLE 10-8: INITIALIZING PORTH

| CLRF  | PORTH  | ; Initialize PORTH by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        | ; data latches                             |

| CLRF  | LATH   | : Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 0Fh    | ;                                          |

| MOVWF | ADCON1 | ;                                          |

| MOVLW | 0CFh   | ,<br>; Value used to                       |

| -     |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISH  | ; Set RH3:RH0 as inputs                    |

| -     |        | ; RH5:RH4 as outputs                       |

|       |        | ; RH7:RH6 as inputs                        |

| 1     |        | , <u>r</u>                                 |

#### FIGURE 10-18: RH3:RH0 PINS BLOCK DIAGRAM IN I/O MODE

# FIGURE 10-19: RHZ

#### RH7:RH4 PINS BLOCK DIAGRAM IN I/O MODE

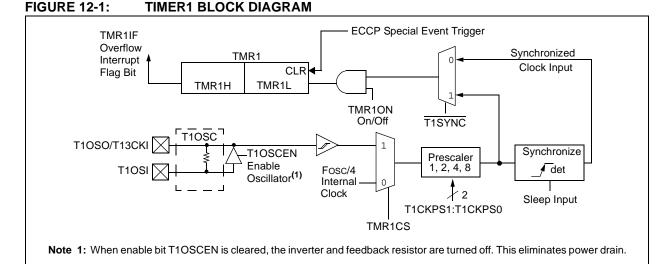

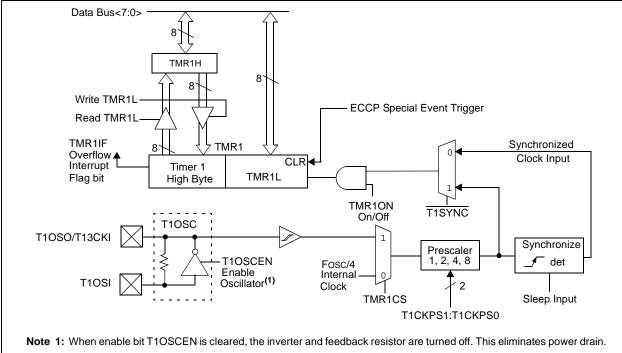

# 12.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

When TMR1CS = 0, Timer1 increments every instruction cycle. When TMR1CS = 1, Timer1 increments on every rising edge of the external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T13CKI pins become inputs. That is, the TRISC<1:0> value is ignored and the pins are read as '0'.

Timer1 also has an internal "Reset input". This Reset can be generated by the ECCP1 or ECCP2 special event trigger. This is discussed in detail in Section 12.4 "Resetting Timer1 Using an ECCP Special Trigger Output".

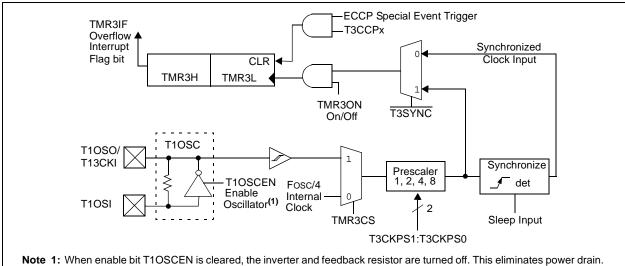

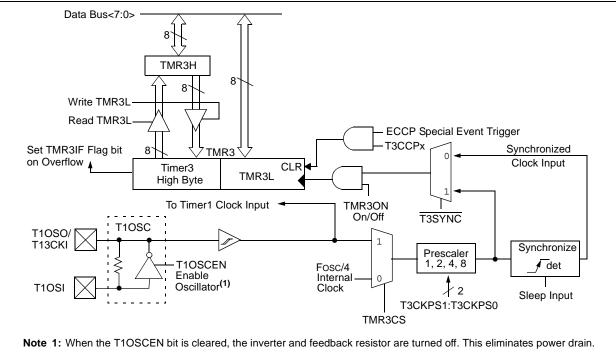

# 14.1 Timer3 Operation

Timer3 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>).

When TMR3CS = 0, Timer3 increments every instruction cycle. When TMR3CS = 1, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T13CKI pins become inputs. That is, the TRISC<1:0> value is ignored and the pins are read as '0'.

Timer3 also has an internal "Reset input". This Reset can be generated by the ECCP module (**Section 14.0** "**Timer3 Module**").

### FIGURE 14-2: TIMER3 BLOCK DIAGRAM CONFIGURED IN 16-BIT READ/WRITE MODE

# FIGURE 14-1: TIMER3 BLOCK DIAGRAM

#### 18.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 18-2) is to broadcast data by the software protocol.

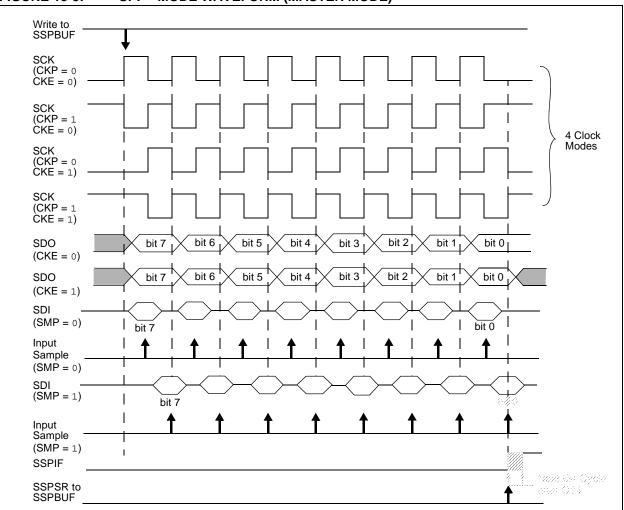

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode. The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in Figure 18-3, Figure 18-5 and Figure 18-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 18-3 shows the waveforms for Master mode.

### 18.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 18.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 18.3.10 BUS MODE COMPATIBILITY

Table 18-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

#### TABLE 18-1: SPI™ BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

There is also a SMP bit which controls when the data is sampled.

| Name    | Bit 7                                 | Bit 6          | Bit 5    | Bit 4         | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|---------------------------------------|----------------|----------|---------------|--------|--------|---------------|--------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH                              | PEIE/GIEL      | TMR0IE   | <b>INTOIE</b> | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1    | PSPIF <sup>(1)</sup>                  | ADIF           | RC1IF    | TX1IF         | SSPIF  | CCP1IF | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1    | PSPIE <sup>(1)</sup>                  | ADIE           | RC1IE    | TX1IE         | SSPIE  | CCP1IE | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1    | PSPIP <sup>(1)</sup>                  | ADIP           | RC1IP    | TX1IP         | SSPIP  | CCP1IP | TMR2IP        | TMR1IP | 1111 1111            | 1111 1111                       |

| TRISC   | PORTC Dat                             | ta Direction R | legister |               |        |        |               |        | 1111 1111            | 1111 1111                       |

| TRISF   | TRISF7                                | TRISF6         | TRISF5   | TRISF4        | TRISF3 | TRISF2 | TRISF1        | TRISF0 | 1111 1111            | 1111 1111                       |

| SSPBUF  | MSSP Receive Buffer/Transmit Register |                |          |               |        |        |               |        | xxxx xxxx            | uuuu uuuu                       |

| SSPCON1 | WCOL                                  | SSPOV          | SSPEN    | CKP           | SSPM3  | SSPM2  | SSPM1         | SSPM0  | 0000 0000            | 0000 0000                       |

| SSPSTAT | SMP                                   | CKE            | D/A      | Р             | S      | R/W    | UA            | BF     | 0000 0000            | 0000 0000                       |

#### TABLE 18-2: REGISTERS ASSOCIATED WITH SPI™ OPERATION

**Legend:** x = unknown, u = unchanged, ---= unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI<sup>TM</sup> mode.**Note 1:**Enabled only in Microcontroller mode for PIC18F8525/8621 devices.

### 23.1 Control Register

bit 5

The Low-Voltage Detect Control register (Register 23-1) controls the operation of the Low-Voltage Detect circuitry.

#### REGISTER 23-1: LVDCON: LOW-VOLTAGE DETECT CONTROL REGISTER

| U-0   | U-0 | R-0   | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IRVST | LVDEN | LVDL3 | LVDL2 | LVDL1 | LVDL0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

IRVST: Internal Reference Voltage Stable Flag bit

- 1 = Indicates that the Low-Voltage Detect logic will generate the interrupt flag at the specified voltage range

- 0 = Indicates that the Low-Voltage Detect logic will not generate the interrupt flag at the specified voltage range and the LVD interrupt should not be enabled

- bit 4 LVDEN: Low-Voltage Detect Power Enable bit

1 = Enables LVD, powers up LVD circuit

- 0 = Disables LVD, powers down LVD circuit

- bit 3-0 LVDL3:LVDL0: Low-Voltage Detection Limit bits

- 1111 = External analog input is used (input comes from the LVDIN pin)

- 1111 = External ana 1110 = 4.45V-4.83V 1101 = 4.16V-4.5V 1100 = 3.96V-4.3V 1011 = 3.76V-3.92V 1010 = 3.57V-3.87V 1001 = 3.47V-3.75V 1000 = 3.27V-3.55V 0111 = 2.98V-3.22V 0110 = 2.77V-3.01V 0101 = 2.67V-2.89V 0100 = 2.48V-2.68V 0011 = 2.37V-2.57V 0010 = 2.18V-2.36V 0001 = 1.98V-2.14V 0000 = Reserved

- **Note:** LVDL3:LVDL0 modes, which result in a trip point below the valid operating voltage of the device, are not tested.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 25.1 Instruction Set

| ADD         | DLW            | Add Lite              | Add Literal to W                                                                          |      |          |  |  |  |

|-------------|----------------|-----------------------|-------------------------------------------------------------------------------------------|------|----------|--|--|--|

| Synta       | ax:            | [label] Al            | [ <i>label</i> ] ADDLW k                                                                  |      |          |  |  |  |

| Oper        | ands:          | $0 \le k \le 255$     | 5                                                                                         |      |          |  |  |  |

| Oper        | ation:         | (W) + k $\rightarrow$ | W                                                                                         |      |          |  |  |  |

| Statu       | is Affected:   | N, OV, C, I           | DC, Z                                                                                     |      |          |  |  |  |

| Enco        | oding:         | 0000                  | 1111                                                                                      | kkkk | kkkk     |  |  |  |

| Desc        | cription:      |                       | The contents of W are added to the<br>8-bit literal 'k' and the result is placed in<br>W. |      |          |  |  |  |

| Word        | ls:            | 1                     | 1                                                                                         |      |          |  |  |  |

| Cycle       | es:            | 1                     | 1                                                                                         |      |          |  |  |  |

| QC          | ycle Activity: |                       |                                                                                           |      |          |  |  |  |

|             | Q1             | Q2                    | Q3                                                                                        | 3    | Q4       |  |  |  |

|             | Decode         | Read<br>literal 'k'   | Proce<br>Data                                                                             |      | ite to W |  |  |  |

| <u>Exan</u> | nple:          | ADDLW                 | 0x15                                                                                      |      |          |  |  |  |

| ADDWFAdd W to fSyntax:[ label ] ADDWFf [,d [,a] f [,d [,a]Operands: $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ Operation:(W) + (f) $\rightarrow$ destStatus Affected:N, OV, C, DC, ZEncoding: $0010$ $01da$ Description:Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default). If 'a' is '0', the Access Bank<br>will be selected. If 'a' is '1', the BSR is<br>used.Words:1Cycles:1Q Cycle Activity: $Q2$ Q1Q2Q3Q4DecodeRead<br>register 'f'DatadestinationExample:ADDWFREG0, 0Before Instruction<br>W=W=0x17<br>REGCta Laturation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |                                                                 |                                       |                              |                        |                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------|---------------------------------------|------------------------------|------------------------|---------------------------|

| Operands: $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ Operation:(W) + (f) $\rightarrow$ destStatus Affected:N, OV, C, DC, ZEncoding: $0010$ $01da$ Description:Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default). If 'a' is '0', the Access Bank<br>will be selected. If 'a' is '1', the BSR is<br>used.Words:1Cycles:1Q Cycle Activity:Q1Q2Q3Q4DecodeRead<br>register 'f'DecodeRead<br>register 'f'Process<br>DataWrite to<br>destinationExample:ADDWFREG, 0, 0Before Instruction<br>W=W=0x17<br>REGREG=0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADDWF             | Add W to                                                        | f                                     |                              |                        |                           |

| $\begin{array}{rcl} d \in [0,1] \\ a \in [0,1] \\ a \in [0,1] \\ \end{array}$ Operation: (W) + (f) $ ightarrow$ dest Status Affected: N, OV, C, DC, Z Encoding: $0010  01da  \mathrm{ffff}  \mathrm{ffff} \\ \hline 0010  01da  \mathrm{ffff}  \mathrm{ffff} \\ \hline \mathrm{Description:} & \mathrm{Add} \ W \ \mathrm{to} \ \mathrm{register} \ \mathrm{'f'}. \ \mathrm{If} \ \mathrm{'d'} \ \mathrm{is} \ \mathrm{'o'}, \ \mathrm{the} \\ \mathrm{result} \ \mathrm{is} \ \mathrm{stored} \ \mathrm{in} \ W. \ \mathrm{If} \ \mathrm{'d'} \ \mathrm{is} \ \mathrm{'o'}, \ \mathrm{the} \\ \mathrm{result} \ \mathrm{is} \ \mathrm{stored} \ \mathrm{back} \ \mathrm{in} \ \mathrm{register} \ \mathrm{'f'}. \ \mathrm{If} \ \mathrm{'d'} \ \mathrm{is} \ \mathrm{'1'}, \ \mathrm{the} \\ \mathrm{result} \ \mathrm{is} \ \mathrm{stored} \ \mathrm{back} \ \mathrm{in} \ \mathrm{register} \ \mathrm{'f'} \\ (\mathrm{default}). \ \mathrm{If} \ \mathrm{'a'} \ \mathrm{is} \ \mathrm{'0'}, \ \mathrm{the} \ \mathrm{Access} \ \mathrm{Bank} \\ \mathrm{will} \ \mathrm{be} \ \mathrm{selected}. \ \mathrm{If} \ \mathrm{'a'} \ \mathrm{is} \ \mathrm{'1'}, \ \mathrm{the} \ \mathrm{BSR} \ \mathrm{is} \\ \mathrm{used}. \\ \\ \end{words:} \ 1 \\ \ \mathrm{Cycles:} \ 1 \\ \ \mathrm{QCycle} \ \mathrm{Activity:} \\ \hline \ \mathrm{Q1} \ \ \mathrm{Q2} \ \ \mathrm{Q3} \ \ \mathrm{Q4} \\ \hline \ \ \mathrm{Decode} \ \ \ \ \mathrm{Read} \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ | Syntax:           | [ label ] AD                                                    | DWF                                   | f [,d [,a                    | a] f [                 | ,d [,a]                   |

| Status Affected:N, OV, C, DC, ZEncoding: $0010$ $01da$ ffffDescription:Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default). If 'a' is '0', the Access Bank<br>will be selected. If 'a' is '1', the BSR is<br>used.Words:1Cycles:1Q Cycle Activity:Q2Q1Q2Q3Q4DecodeRead<br>register 'f'<br>DataExample:ADDWFREG=0x17<br>REG=0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Operands:         | d ∈ [0,1]                                                       |                                       |                              |                        |                           |

| Encoding: $0010$ $01da$ ffffffffDescription:Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default). If 'a' is '0', the Access Bank<br>will be selected. If 'a' is '1', the BSR is<br>used.Words:1Cycles:1Q Cycle Activity:Q2Q1Q2Q3Q4DecodeRead<br>register 'f'DecodeRead<br>register 'f'DecodeRead<br>register 'f'Example:ADDWFREG, 0, 0Before Instruction<br>W=W=0x17<br>REGREG=0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Operation:        | $(W) + (f) \rightarrow$                                         | dest                                  |                              |                        |                           |

| Description:Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default). If 'a' is '0', the Access Bank<br>will be selected. If 'a' is '1', the BSR is<br>used.Words:1Cycles:1Q Cycle Activity:Q1Q1Q2Q3Q4DecodeRead<br>register 'f'DecodeRead<br>register 'f'Process<br>DataWrite to<br>destinationExample:ADDWFREG0, 0Before Instruction<br>W=W=0x17<br>REG=0x2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Status Affected:  | N, OV, C, D                                                     | 0C, Z                                 |                              |                        |                           |

| $\begin{array}{rcl} \mbox{result is stored in W. If 'd' is '1', the} \\ \mbox{result is stored back in register 'f'} \\ (default). If 'a' is '0', the Access Bank \\ \mbox{will be selected. If 'a' is '1', the BSR is} \\ \mbox{used.} \end{array}$ $\begin{array}{rcl} \mbox{Words:} & 1 \\ \mbox{Cycles:} & 1 \\ \mbox{Q cycle Activity:} \\ \hline \end{tabular} \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Encoding:         | 0010                                                            | 01da                                  | fff                          | f                      | ffff                      |

| Cycles:1Q Cycle Activity:Q1Q2Q3Q4DecodeRead<br>register 'f'Process<br>DataWrite to<br>destinationExample:ADDWFREG, 0, 0Before Instruction<br>W=0x17<br>REG=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Description:      | result is sto<br>result is sto<br>(default). If<br>will be sele | ored in W<br>ored back<br>'a' is '0', | . If 'd'<br>in reg<br>the Ac | is '1<br>giste<br>cces | ', the<br>r 'f'<br>s Bank |

| Q Cycle Activity:Q1Q2Q3Q4DecodeRead<br>register 'f'Process<br>DataWrite to<br>destinationExample:ADDWFREG, 0, 0Before Instruction<br>W=0x17<br>REG=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Words:            | 1                                                               |                                       |                              |                        |                           |

| Q1     Q2     Q3     Q4       Decode     Read<br>register 'f'     Process     Write to<br>destination       Example:     ADDWF     REG, 0, 0       Before Instruction<br>W = 0x17<br>REG = 0xC2     0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Cycles:           | 1                                                               |                                       |                              |                        |                           |

| Decode     Read<br>register 'f'     Process<br>Data     Write to<br>destination       Example:     ADDWF     REG, 0, 0       Before Instruction     W = 0x17<br>REG = 0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q Cycle Activity: |                                                                 |                                       |                              |                        |                           |

| Example:     ADDWF     REG, 0, 0       Before Instruction     W = 0x17       REG = 0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q1                | Q2                                                              | Q3                                    |                              |                        | Q4                        |

| Before Instruction<br>W = 0x17<br>REG = 0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Decode            |                                                                 |                                       |                              |                        |                           |

| W = 0x17<br>REG = 0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Example:          | ADDWF                                                           | REG,                                  | 0, 0                         |                        |                           |

| REG = 0xC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Before Instruc    | tion                                                            |                                       |                              |                        |                           |

| After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ••                |                                                                 |                                       |                              |                        |                           |

| W = 0xD9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | After Instructio  |                                                                 |                                       |                              |                        |                           |

| W   | = | 0xD9 |

|-----|---|------|

| REG | = | 0xC2 |

Before Instruction W = 0x10

After Instruction W = 0x25

#### TBLRD **Table Read** Syntax: [label] TBLRD (\*; \*+; \*-; +\*) Operands: None Operation: if TBLRD\* (Prog Mem (TBLPTR)) $\rightarrow$ TABLAT; TBLPTR – No Change if TBLRD\*+ (Prog Mem (TBLPTR)) $\rightarrow$ TABLAT; (TBLPTR) + 1 $\rightarrow$ TBLPTR if TBLRD\*-(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT; (TBLPTR) – 1 $\rightarrow$ TBLPTR if TBLRD+\* (TBLPTR) + 1 $\rightarrow$ TBLPTR; (Prog Mem (TBLPTR)) $\rightarrow$ TABLAT Status Affected: None Encoding: 0000 0000 0000 10nn nn=0 \* =1 =2 \* =3 +\* Description: This instruction is used to read the contents of Program Memory (P.M.). To address the program memory, a pointer called Table Pointer (TBLPTR) is used. The TBLPTR (a 21-bit pointer) points to each byte in the program memory. TBLPTR has a 2-Mbyte address range. TBLPTR[0] = 0: Least Significant Byte of Program Memory Word TBLPTR[0] = 1: Most Significant Byte of Program Memory Word The TBLRD instruction can modify the value of TBLPTR as follows: • no change post-increment • post-decrement pre-increment Words: 1 Cycles: 2 Q Cycle Activity: Q1 Q2 Q3 Q4

| Decode          | No                                       | No              | No                                |

|-----------------|------------------------------------------|-----------------|-----------------------------------|

|                 | operation                                | operation       | operation                         |

| No<br>operation | No operation<br>(Read Program<br>Memory) | No<br>operation | No operation<br>(Write<br>TABLAT) |

#### TBLRD Table Read (Continued)

| Example 1:                             | TBLRD    | *+ | ;           |                                  |

|----------------------------------------|----------|----|-------------|----------------------------------|

| Before Instruction                     | on       |    |             |                                  |

| TABLAT<br>TBLPTR<br>MEMORY(            | 0x00A356 | 6) | =<br>=<br>= | 0x55<br>0x00A356<br>0x34         |

| After Instruction<br>TABLAT<br>TBLPTR  |          |    | =<br>=      | 0x34<br>0x00A357                 |

| Example 2:                             | TBLRD    | +* | ;           |                                  |

| Before Instructio                      | on       |    |             |                                  |

| TABLAT<br>TBLPTR<br>MEMORY(<br>MEMORY( |          |    | =<br>=<br>= | 0xAA<br>0x01A357<br>0x12<br>0x34 |

| Param.<br>No. | Symbol |                   | Character         | istic                         | Min                           | Max | Units                             | Conditions |  |

|---------------|--------|-------------------|-------------------|-------------------------------|-------------------------------|-----|-----------------------------------|------------|--|

| 50            | TccL   | CCPx Input        | No prescale       | er                            | 0.5 TCY + 20                  |     | ns                                |            |  |

|               |        | Low Time          | With<br>prescaler | PIC18F6525/6621/<br>8525/8621 | 10                            | _   | ns                                |            |  |

|               |        |                   |                   | PIC18LF6X2X/8X2X              | 20                            |     | ns                                |            |  |

| 51            | TccH   |                   |                   | er                            | 0.5 TCY + 20                  |     | ns                                |            |  |

|               |        | High Time         | High Time         | With<br>prescaler             | PIC18F6525/6621/<br>8525/8621 | 10  |                                   | ns         |  |

|               |        |                   |                   | PIC18LF6X2X/8X2X              | 20                            | _   | ns                                |            |  |

| 52            | TccP   | CCPx Input Period |                   | <u>3 Tcy + 40</u><br>N        | _                             | ns  | N = prescale<br>value (1,4 or 16) |            |  |

| 53            | TccR   | CCPx Output Ri    | se Time           | PIC18F6525/6621/<br>8525/8621 | —                             | 25  | ns                                |            |  |

|               |        | F                 | PIC18LF6X2X/8X2X  | —                             | 45                            | ns  |                                   |            |  |

| 54            | TccF   | CCPx Output Fa    | all Time          | PIC18F6525/6621/<br>8525/8621 | —                             | 25  | ns                                |            |  |

|               |        |                   |                   | PIC18LF6X2X/8X2X              | —                             | 45  | ns                                |            |  |

# TABLE 27-13: CAPTURE/COMPARE/PWM REQUIREMENTS (ALL ECCP/CCP MODULES)

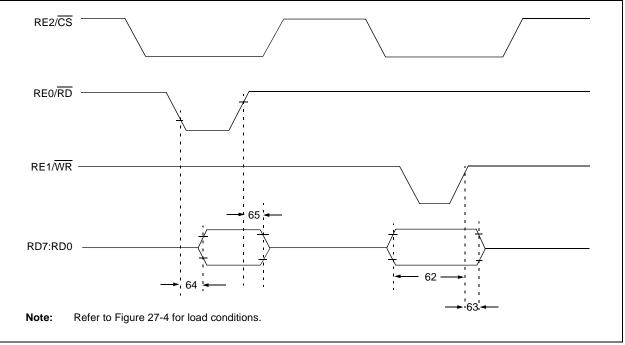

### FIGURE 27-13: PARALLEL SLAVE PORT TIMING (PIC18F8525/8621)

| Param.<br>No. | Symbol  | Charact                | eristic      | Min         | Max  | Units | Conditions                                                              |

|---------------|---------|------------------------|--------------|-------------|------|-------|-------------------------------------------------------------------------|

| 100           | Тнідн   | Clock High Time        | 100 kHz mode | 4.0         |      | μs    | PIC18F6525/6621/8525/<br>8621 must operate at a<br>minimum of 1.5 MHz   |

|               |         |                        | 400 kHz mode | 0.6         | _    | μS    | PIC18F6525/6621/8525/<br>8621 must operate at a<br>minimum of<br>10 MHz |

|               |         |                        | MSSP module  | 1.5 TCY     | _    |       |                                                                         |

| 101 TLOW      |         | Clock Low Time         | 100 kHz mode | 4.7         | —    | μs    | PIC18F6525/6621/8525/<br>8621 must operate at a<br>minimum of 1.5 MHz   |

|               |         |                        | 400 kHz mode | 1.3         | _    | μS    | PIC18F6525/6621/8525/<br>8621 must operate at a<br>minimum of<br>10 MHz |

|               |         |                        | MSSP module  | 1.5 TCY     | _    |       |                                                                         |

| 102           | TR      | SDA and SCL Rise       | 100 kHz mode | —           | 1000 | ns    |                                                                         |

|               |         | Time                   | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from<br>10 to 400 pF                              |

| 103           | TF      | SDA and SCL Fall       | 100 kHz mode | —           | 300  | ns    |                                                                         |

|               |         | Time                   | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from<br>10 to 400 pF                              |

| 90            | TSU:STA | Start Condition        | 100 kHz mode | 4.7         | —    | μs    | Only relevant for Repeated                                              |

|               |         | Setup Time             | 400 kHz mode | 0.6         | —    | μs    | Start condition                                                         |

| 91            | THD:STA | Start Condition        | 100 kHz mode | 4.0         | —    | μs    | After this period, the first                                            |

|               |         | Hold Time              | 400 kHz mode | 0.6         |      | μS    | clock pulse is generated                                                |

| 106           | THD:DAT | Data Input Hold        | 100 kHz mode | 0           | —    | ns    |                                                                         |

|               |         | Time                   | 400 kHz mode | 0           | 0.9  | μs    |                                                                         |

| 107           | TSU:DAT | Data Input Setup       | 100 kHz mode | 250         |      | ns    | (Note 2)                                                                |

|               |         | Time                   | 400 kHz mode | 100         | —    | ns    |                                                                         |

| 92            | Tsu:sto | Stop Condition         | 100 kHz mode | 4.7         | —    | μs    |                                                                         |

|               |         | Setup Time             | 400 kHz mode | 0.6         | —    | μs    |                                                                         |

| 109           | ΤΑΑ     | Output Valid from      | 100 kHz mode | —           | 3500 | ns    | (Note 1)                                                                |

|               |         | Clock                  | 400 kHz mode | —           | —    | ns    |                                                                         |

| 110           | TBUF    | BUF Bus Free Time      | 100 kHz mode | 4.7         | —    | μS    | Time the bus must be free                                               |

|               |         |                        | 400 kHz mode | 1.3         |      | μS    | before a new transmission<br>can start                                  |

| D102          | Св      | Bus Capacitive Loading |              | —           | 400  | pF    |                                                                         |

# TABLE 27-20: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS (SLAVE MODE)

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode I<sup>2</sup>C bus system but the requirement TSU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line.

TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

NOTES:

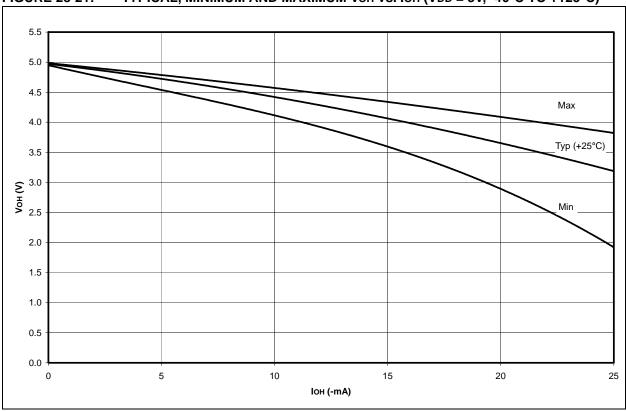

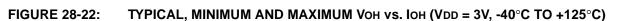

FIGURE 28-21: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO +125°C)

| Reading                         |

|---------------------------------|

| Using                           |

| Write Verify82                  |

| Writing To                      |

| Data Memory47                   |

| General Purpose Registers47     |

| Map for PIC18F6X2X/8X2X Devices |

| Special Function Registers47    |

| DAW                             |

| DC and AC Characteristics       |

| Graphs and Tables357            |

| DC Characteristics              |

| Power-Down and Supply Current   |

| Supply Voltage                  |

| DCFSNZ                          |

| DECF                            |

| DECFSZ                          |

| Demonstration Boards            |

| PICDEM 1 320                    |

| PICDEM 17 321                   |

| PICDEM 18R                      |

| PICDEM 2 Plus 320               |

| PICDEM 3 320                    |

| PICDEM 4                        |

| PICDEM LIN                      |

| PICDEM USB321                   |

| PICDEM.net Internet/Ethernet    |

| Development Support             |

| Device Differences              |

| Direct Addressing57             |

| Direct Addressing55             |

# Е

| ECCP                                        |     |

|---------------------------------------------|-----|

| Capture and Compare Modes                   |     |

| Standard PWM Mode                           | 160 |

| Electrical Characteristics                  |     |

| Enhanced Capture/Compare/PWM (ECCP)         | 157 |

| and Program Memory modes                    | 158 |

| Capture Mode. See Capture (ECCP Module).    |     |

| Outputs and Configuration                   |     |

| Pin Configurations for ECCP1                | 158 |

| Pin Configurations for ECCP2                | 159 |

| Pin Configurations for ECCP3                | 159 |