Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 69                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.75K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8525-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nomo                   | Pin N      | umber      | Pin  | Buffer | Description                                        |

|----------------------------|------------|------------|------|--------|----------------------------------------------------|

| Pin Name                   | PIC18F6X2X | PIC18F8X2X | Туре | Туре   | Description                                        |

|                            |            |            |      |        | PORTH is a bidirectional I/O port <sup>(6)</sup> . |

| RH0/A16                    | _          | 79         |      |        |                                                    |

| RH0                        |            |            | I/O  | ST     | Digital I/O.                                       |

| A16                        |            |            | 0    | TTL    | External memory address 16.                        |

| RH1/A17                    | _          | 80         |      |        |                                                    |

| RH1                        |            |            | I/O  | ST     | Digital I/O.                                       |

| A17                        |            |            | 0    | TTL    | External memory address 17.                        |

| RH2/A18                    | _          | 1          |      |        |                                                    |

| RH2                        |            |            | I/O  | ST     | Digital I/O.                                       |

| A18                        |            |            | 0    | TTL    | External memory address 18.                        |

| RH3/A19                    | —          | 2          |      |        |                                                    |

| RH3                        |            |            | I/O  | ST     | Digital I/O.                                       |

| A19                        |            |            | 0    | TTL    | External memory address 19.                        |

| RH4/AN12/P3C               | —          | 22         |      |        |                                                    |

| RH4                        |            |            | I/O  | ST     | Digital I/O.                                       |

| AN12<br>P3C <sup>(7)</sup> |            |            |      | Analog | Analog input 12.                                   |

|                            |            |            | 0    | _      | ECCP3 output P3C.                                  |

| RH5/AN13/P3B               | —          | 21         |      |        |                                                    |

| RH5<br>AN13                |            |            | I/O  | ST     | Digital I/O.                                       |

| P3B <sup>(7)</sup>         |            |            |      | Analog | Analog input 13.<br>ECCP3 output P3B.              |

| -                          |            | 20         |      | _      |                                                    |

| RH6/AN14/P1C<br>RH6        | _          | 20         | I/O  | ST     | Digital I/O.                                       |

| AN14                       |            |            |      | Analog | Analog input 14.                                   |

| P1C <sup>(7)</sup>         |            |            | Ö    |        | ECCP1 output P1C.                                  |

| RH7/AN15/P1B               | _          | 19         | -    |        |                                                    |

| RH7                        |            | 10         | I/O  | ST     | Digital I/O.                                       |

| AN15                       |            |            | 1    | Analog | Analog input 15.                                   |

| P1B <sup>(7)</sup>         |            |            | 0    | _ Ŭ    | ECCP1 output P1B.                                  |

#### TABLE 1-2: PIC18F6525/6621/8525/8621 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input

I.

Р

ST = Schmitt Trigger input with CMOS levels

CMOS = CMOS compatible input or output

Analog = Analog input

= Input = Power O = Output

OD = Open-Drain (no P diode to VDD)

Note 1: Alternate assignment for ECCP2/P2A in PIC18F8525/8621 devices when CCP2MX (CONFIG3H<0>) is not set (all Program Memory modes except Microcontroller).

2: Default assignment for ECCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8525/8621 devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8525/8621 devices when ECCPMX (CONFIG3H<1>) is set and for all PIC18F6525/6621 devices.

5: Alternate assignment for ECCP2/P2A in PIC18F8525/8621 devices when CCP2MX is not set (Microcontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8525/8621 devices.

7: Alternate assignment for P1B/P1C/P3B/P3C for PIC18F8525/8621 devices when ECCPMX (CONFIG3H<1>) is not set.

8: AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP<sup>™</sup> modes. See parameter D001 for details.

**9:** RG5 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

# 2.6 Oscillator Switching Feature

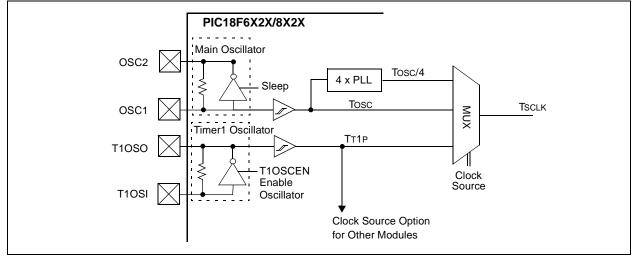

The PIC18F6525/6621/8525/8621 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For the PIC18F6525/6621/8525/8621 devices, this alternate clock source is the Timer1 oscillator. If a low-frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a low-power execution mode.

Figure 2-7 shows a block diagram of the system clock sources. The clock switching feature is enabled by programming the Oscillator Switching Enable (OSCSEN) bit in the CONFIG1H Configuration register to a '0'. Clock switching is disabled in an erased device. See Section 12.0 "Timer1 Module" for further details of the Timer1 oscillator. See Section 24.0 "Special Features of the CPU" for Configuration register details.

### FIGURE 2-7: DEVICE CLOCK SOURCES

# 5.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable, during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

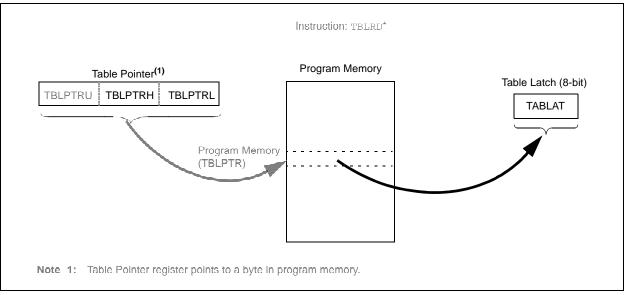

#### 5.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 5-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 5.5 "Writing to Flash Program Memory"**. Figure 5-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

#### FIGURE 5-1: TABLE READ OPERATION

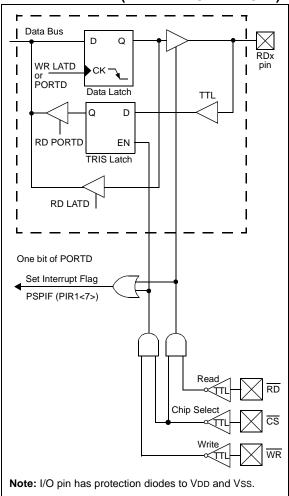

### 10.10 Parallel Slave Port

PORTD also operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (PSPCON<4>) is set. It is asynchronously readable and writable by the external world through RD control input pin, RE0/RD and WR control input pin, RE1/WR.

| Note: | For PIC | 18F852    | 25/86                 | 21 devices, | the Para | allel |  |  |  |  |

|-------|---------|-----------|-----------------------|-------------|----------|-------|--|--|--|--|

|       | Slave   | Port      | is                    | available   | only     | in    |  |  |  |  |

|       | Microco | ontroller | Microcontroller mode. |             |          |       |  |  |  |  |

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG2:PCFG0 (ADCON1<2:0>), must be set, which will configure pins RE2:RE0 as digital I/O.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (PSPCON<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs) and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

# FIGURE 10-24: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

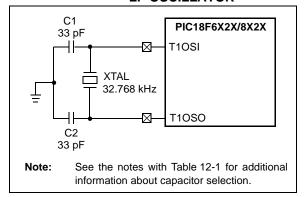

# 12.2 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 12-3. Table 12-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

#### FIGURE 12-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

# TABLE 12-1: CAPACITOR SELECTION FOR THE ALTERNATE OSCILLATOR<sup>(2-4)</sup>

| Osc Type       | Freq   | C1                      | C2                      |  |  |  |  |  |

|----------------|--------|-------------------------|-------------------------|--|--|--|--|--|

| LP             | 32 kHz | 15-22 pF <sup>(1)</sup> | 15-22 pF <sup>(1)</sup> |  |  |  |  |  |

| Crystal Tested |        |                         |                         |  |  |  |  |  |

| 32.768 kHz     |        |                         |                         |  |  |  |  |  |

- **Note 1:** Microchip suggests 33 pF as a starting point in validating the oscillator circuit.

- **2:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

# 12.3 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the TMR1 Interrupt Enable bit, TMR1IE (PIE1<0>).

### 12.4 Resetting Timer1 Using an ECCP Special Trigger Output

If either the ECCP1 or ECCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1. The trigger for ECCP2 will also start an A/D conversion if the A/D module is enabled.

| Note: | The special event triggers from the      |

|-------|------------------------------------------|

|       | ECCP1 module will not set interrupt flag |

|       | bit TMR1IF (PIR1<0>).                    |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from ECCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

# 12.5 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

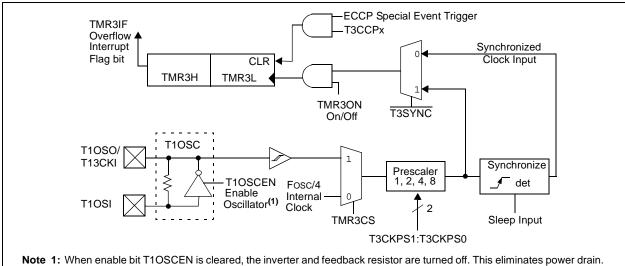

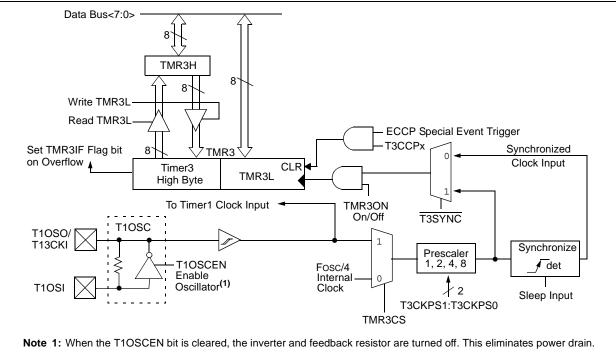

# 14.1 Timer3 Operation

Timer3 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>).

When TMR3CS = 0, Timer3 increments every instruction cycle. When TMR3CS = 1, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T13CKI pins become inputs. That is, the TRISC<1:0> value is ignored and the pins are read as '0'.

Timer3 also has an internal "Reset input". This Reset can be generated by the ECCP module (**Section 14.0** "**Timer3 Module**").

#### FIGURE 14-2: TIMER3 BLOCK DIAGRAM CONFIGURED IN 16-BIT READ/WRITE MODE

# FIGURE 14-1: TIMER3 BLOCK DIAGRAM

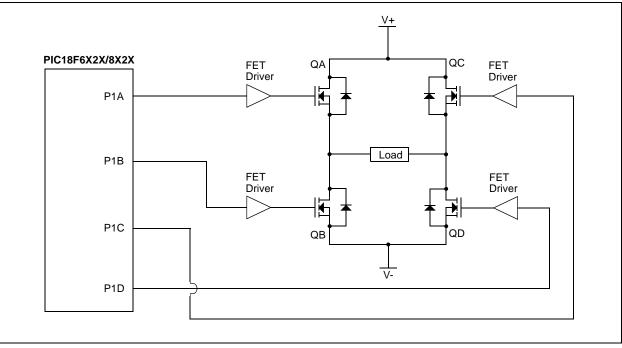

### FIGURE 17-7: EXAMPLE OF FULL-BRIDGE APPLICATION

### 17.4.5.1 Direction Change in Full-Bridge Mode

In the Full-Bridge Output mode, the P1M1 bit in the CCP1CON register allows users to control the forward/ reverse direction. When the application firmware changes this direction control bit, the module will assume the new direction on the next PWM cycle.

Just before the end of the current PWM period, the modulated outputs (P1B and P1D) are placed in their inactive state, while the unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction. This occurs in a time interval of (4 Tosc \* (Timer2 Prescale Value) before the next PWM period begins. The Timer2 prescaler will be either 1, 4 or 16, depending on the value of the T2CKPS bit (T2CON<1:0>). During the interval from the switch of the unmodulated outputs to the beginning of the next period, the modulated outputs (P1B and P1D) remain inactive. This relationship is shown in Figure 17-8.

Note that in the Full-Bridge Output mode, the ECCP1 module does not provide any dead-band delay. In general, since only one output is modulated at all times, dead-band delay is not required. However, there is a situation where a dead-band delay might be required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 17-9 shows an example where the PWM direction changes from forward to reverse at a near 100% duty cycle. At time t1, the output P1A and P1D become inactive, while output P1C becomes active. In this example, since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current may flow through power devices QC and QD (see Figure 17-7) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, one of the following requirements must be met:

- 1. Reduce PWM for a PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### 18.3.5 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 18-2) is to broadcast data by the software protocol.

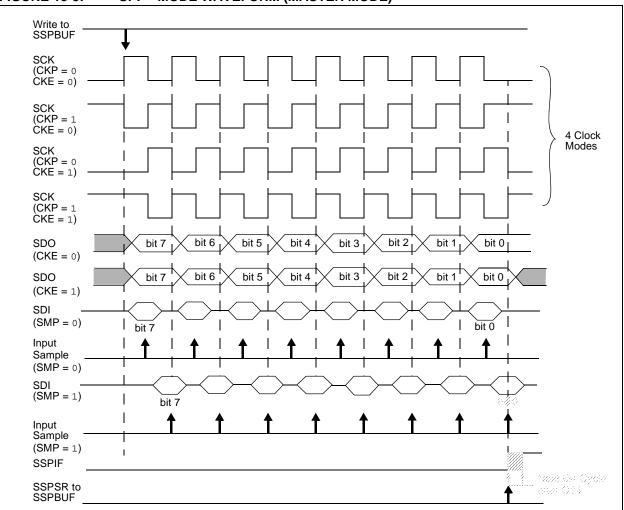

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode. The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in Figure 18-3, Figure 18-5 and Figure 18-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 18-3 shows the waveforms for Master mode.

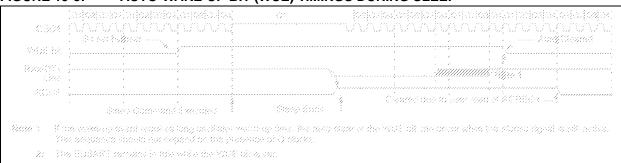

#### 19.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RXx/DTx line, while the EUSART is operating in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit (BAUDCONx<1>). Once set, the typical receive sequence on RXx/DTx is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RXx/DTx line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN protocol.)

Following a wake-up event, the module generates an RC1IF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 19-7) and asynchronously, if the device is in Sleep mode (Figure 19-8). The interrupt condition is cleared by reading the RCREGx register.

The WUE bit is automatically cleared once a low-to-high transition is observed on the RXx line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

#### 19.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RXx/DTx, information with any state changes before the Stop bit may signal a false end-of-

character and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bytes) for standard RS-232 devices, or 000h (12 bits) for LIN bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., XT or HS mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

# 19.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCxIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared after this when a rising edge is seen on RXx/DTx. The interrupt condition is then cleared by reading the RCREGx register. Ordinarily, the data in RCREGx will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCxIF flag is set should not be used as an indicator of the integrity of the data in RCREGx. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

## FIGURE 19-7: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

| 0.906    | yanana.       | punun          | punna. | <i>m.</i> n  | JAN J            | NA AM | ijunin.                                                   | nyniain                               | INAN       | UNUNUNU                                | NAVAVA | 10A.  |

|----------|---------------|----------------|--------|--------------|------------------|-------|-----------------------------------------------------------|---------------------------------------|------------|----------------------------------------|--------|-------|

|          | 4 – BB set by | Wester and the | 2<br>3 |              |                  | 2     |                                                           | *                                     |            |                                        |        | 99-90 |

| 8036.03  |               |                |        | ·····        | ······<br>,      | 2     | · · · · · · · · · · · · · · · · · · ·                     | · · · · · · · · · · · · · · · · · · · | ······     | ·····                                  |        |       |

| areco ex | -             | ?              |        |              | unconce          | ar?   | 4                                                         | ,                                     | i (<br>    | seconde contractor                     |        |       |

| 1948     |               |                | 2<br>2 | * 100<br>* 5 | 0000000000<br>', |       |                                                           | ·····;······                          | .:9009000  |                                        |        |       |

| 20.00    | s             |                | ×      | ×            | ¢                |       | <sup>9</sup> . улт. т. т |                                       |            | ······································ | N      |       |

|          |               | *<br>*         | 4<br>4 | 1            | 3                |       | ·<br>·                                                    | - Classed de                          | 60 20 USAN | 1086 oc 8803                           | aax (j |       |

|          | 1             |                | 2      | ÷            | 4                |       |                                                           |                                       |            |                                        | ,      |       |

#### FIGURE 19-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

#### REGISTER 20-2: ADCON1: A/D CONTROL REGISTER 1

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | —   | VCFG1 | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 VCFG1:VCFG0: Voltage Reference Configuration bits:

| VCFG1<br>VCFG0 | A/D VREF+      | A/D VREF-      |  |  |  |  |

|----------------|----------------|----------------|--|--|--|--|

| 00             | AVdd           | AVss           |  |  |  |  |

| 01             | External VREF+ | AVss           |  |  |  |  |

| 10             | AVdd           | External VREF- |  |  |  |  |

| 11             | External VREF+ | External VREF- |  |  |  |  |

bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits:

| PCFG3<br>PCFG0 | AN15 | AN14 | AN13 | AN12 | AN11 | AN10 | AN9 | AN8 | AN7 | AN6 | AN5 | AN4 | AN3 | AN2 | AN1 | ANO |

|----------------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000           | Α    | Α    | А    | Α    | А    | А    | А   | А   | А   | А   | Α   | А   | Α   | А   | Α   | Α   |

| 0001           | D    | D    | А    | Α    | А    | А    | А   | А   | Α   | А   | А   | А   | Α   | А   | А   | А   |

| 0010           | D    | D    | D    | Α    | А    | А    | А   | А   | А   | А   | А   | А   | Α   | А   | Α   | Α   |

| 0011           | D    | D    | D    | D    | А    | А    | А   | А   | А   | А   | А   | А   | Α   | А   | Α   | Α   |

| 0100           | D    | D    | D    | D    | D    | А    | А   | А   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0101           | D    | D    | D    | D    | D    | D    | А   | А   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0110           | D    | D    | D    | D    | D    | D    | D   | А   | А   | А   | А   | А   | А   | А   | А   | А   |

| 0111           | D    | D    | D    | D    | D    | D    | D   | D   | А   | А   | А   | А   | А   | А   | Α   | А   |

| 1000           | D    | D    | D    | D    | D    | D    | D   | D   | D   | А   | А   | А   | А   | А   | А   | А   |

| 1001           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | А   | А   | А   | А   | А   | А   |

| 1010           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | А   | А   | А   | А   | А   |

| 1011           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | А   | А   | А   | А   |

| 1100           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | А   | А   | Α   |

| 1101           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | А   | А   |

| 1110           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | А   |

| 1111           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

A = Analog input D = Digital I/O

Note: Shaded cells indicate A/D channels available only on PIC18F8525/8621 devices.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 20.4 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as a digital input will convert as an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- Analog levels on any pin defined as a digital input may cause the input buffer to consume current out of the device's specification limits.

#### 20.5 A/D Conversions

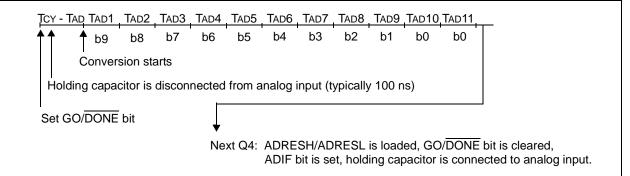

Figure 20-3 shows the operation of the A/D converter after the GODONE bit has been set. Clearing the GO/ DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

#### FIGURE 20-3: A/D CONVERSION TAD CYCLES

### 23.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- Write the value to the LVDL3:LVDL0 bits (LVDCON register) which selects the desired LVD trip point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- Clear the LVD interrupt flag, which may have falsely become set, until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

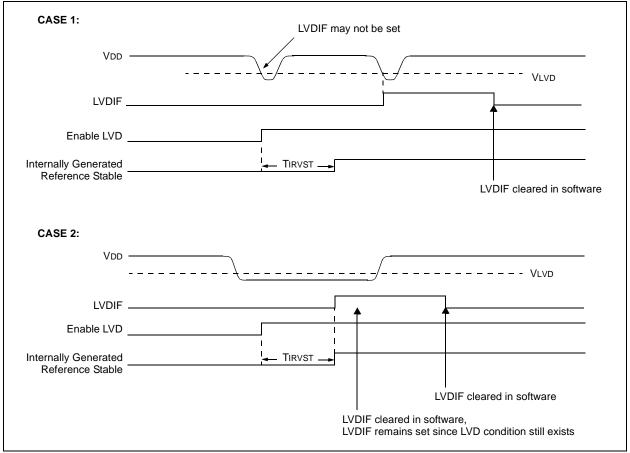

Figure 23-4 shows typical waveforms that the LVD module may be used to detect.

# FIGURE 23-4: LOW-VOLTAGE DETECT WAVEFORMS

| REGISTER 24-12: | CONFIG7                                                      | H: CONFIG              |                 | I REGISTE     | R 7 HIGH     | (BYTE AD                            | DRESS 30       | 000Dh) |  |  |

|-----------------|--------------------------------------------------------------|------------------------|-----------------|---------------|--------------|-------------------------------------|----------------|--------|--|--|

|                 | U-0                                                          | R/C-1                  | U-0             | U-0           | U-0          | U-0                                 | U-0            | U-0    |  |  |

|                 |                                                              | EBTRB                  | _               | _             | _            | _                                   | —              | —      |  |  |

|                 | bit 7                                                        |                        |                 |               |              |                                     |                | bit 0  |  |  |

| bit 7           | Unimplem                                                     | ented: Read            | <b>d as</b> '0' |               |              |                                     |                |        |  |  |

| bit 6           | EBTRB: B                                                     | oot Block Ta           | ble Read Pr     | otection bit  |              |                                     |                |        |  |  |

|                 |                                                              |                        |                 |               | d from table |                                     |                |        |  |  |

|                 | 0 = Boot b                                                   | ock (000000            | )-0007FFh)      | protected fro | om table rea | ds executed                         | l in other blo | ocks   |  |  |

| bit 5-0         | Unimplem                                                     | ented: Read            | <b>d as</b> '0' |               |              |                                     |                |        |  |  |

|                 | <u> </u>                                                     |                        |                 |               |              |                                     |                |        |  |  |

|                 | Legend:                                                      |                        |                 |               |              |                                     |                |        |  |  |

|                 | R = Reada                                                    | ble bit                | C = Clear       | able bit      | U = Unir     | nplemented                          | bit, read as   | '0'    |  |  |

|                 | -n = Value                                                   | when device            | e is unprogra   | ammed         | u = Uncł     | u = Unchanged from programmed state |                |        |  |  |

| REGISTER 24-13: | (ADDRES                                                      | DEVICE ID<br>S 3FFFFEI |                 | R 1 FOR P     | IC18F6525    | 5/6621/852                          | 5/8621 DE      |        |  |  |

|                 | R                                                            | R                      | R               | R             | R            | R                                   | R              | R      |  |  |

|                 | DEV2                                                         | DEV1                   | DEV0            | REV4          | REV3         | REV2                                | REV1           | REV0   |  |  |

|                 | bit 7                                                        |                        |                 |               |              |                                     |                | bit 0  |  |  |

|                 |                                                              |                        |                 |               |              |                                     |                |        |  |  |

| bit 7-5         | DEV2:DEV<br>100 = PIC<br>101 = PIC<br>110 = PIC<br>111 = PIC | 18F6621<br>18F8525     | ) bits          |               |              |                                     |                |        |  |  |

bit 4-0 **REV4:REV0:** Revision ID bits

These bits are used to indicate the device revision.

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

# REGISTER 24-14: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F6525/6621/8525/8621 DEVICES (ADDRESS 3FFFFh)

| R-0   | R-0  | R-0  | R-0  | R-1  | R-0  | R-1  | R-0   |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 DEV10:DEV3: Device ID bits

These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number.

0000 1010 = PIC18F6525/6621/8525/8621

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Readable bit       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device | is unprogrammed      | u = Unchanged from programmed state |

# 27.2 DC Characteristics: Power-Down and Supply Current PIC18F6525/6621/8525/8621 (Industrial, Extended) PIC18LF6X2X/8X2X (Industrial) (Continued)

| PIC18LF6X2X/8X2X<br>(Industrial)<br>PIC18F6525/6621/8525/8621<br>(Industrial, Extended) |                                   |                                                       | rd Oper  |          | onditions (unless -40°C $\leq$ TA | s otherwise stated<br>≤ +85°C for indust |                        |  |  |  |

|-----------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------|----------|----------|-----------------------------------|------------------------------------------|------------------------|--|--|--|

|                                                                                         |                                   | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |          |          |                                   |                                          |                        |  |  |  |

| Param<br>No.                                                                            | Device                            | Тур                                                   | Max      | Units    | Conditions                        |                                          |                        |  |  |  |

|                                                                                         | Module Differential Currer        | nts (∆lw                                              | от, ∆Іво | R, ∆ILVD | , $\Delta$ IOSCB, $\Delta$ IAD)   |                                          |                        |  |  |  |

| D022                                                                                    | Watchdog Timer                    | <1                                                    | 2.0      | μA       | -40°C                             |                                          |                        |  |  |  |

| (∆IWDT)                                                                                 |                                   | <1                                                    | 2        | μA       | +25°C                             | VDD = 2.0V                               |                        |  |  |  |

|                                                                                         |                                   | 5                                                     | 20       | μΑ       | +85°C                             |                                          |                        |  |  |  |

|                                                                                         |                                   | 3                                                     | 10       | μA       | -40°C                             |                                          |                        |  |  |  |

|                                                                                         |                                   | 3                                                     | 20       | μΑ       | +25°C                             |                                          | VDD = 3.0V             |  |  |  |

|                                                                                         |                                   | 10                                                    | 35       | μΑ       | +85°C                             |                                          |                        |  |  |  |

|                                                                                         |                                   | 12                                                    | 25       | μΑ       | -40°C                             |                                          |                        |  |  |  |

|                                                                                         |                                   | 15                                                    | 35       | μΑ       | +25°C                             |                                          | VDD = 5.0V             |  |  |  |

|                                                                                         |                                   | 20                                                    | 50       | μΑ       | +85°C                             |                                          |                        |  |  |  |

| D022A                                                                                   | Brown-out Reset <sup>(4)</sup>    | 55                                                    | 115      | μA       | -40°C to +85°C                    | VDD = 3.0V<br>VDD = 5.0V                 |                        |  |  |  |

| ( $\Delta$ IBOR)                                                                        |                                   | 105                                                   | 175      | μA       | -40°C to +85°C                    |                                          |                        |  |  |  |

| D022B                                                                                   | Low-Voltage Detect <sup>(4)</sup> | 45                                                    | 125      | μΑ       | -40°C to +85°C                    |                                          | VDD = 2.0V             |  |  |  |

| (∆ILVD)                                                                                 |                                   | 45                                                    | 150      | μΑ       | -40°C to +85°C                    | VDD = 3.0V                               |                        |  |  |  |

|                                                                                         |                                   | 45                                                    | 225      | μΑ       | -40°C to +85°C                    | VDD = 5.0V                               |                        |  |  |  |

| D025                                                                                    | Timer1 Oscillator                 | 20                                                    | 27       | μΑ       | -10°C                             |                                          |                        |  |  |  |

| (∆IOSCB)                                                                                |                                   | 20                                                    | 30       | μΑ       | +25°C                             | VDD = 2.0V                               | 32 kHz on Timer1       |  |  |  |

|                                                                                         |                                   | 25                                                    | 35       | μA       | +70°C                             |                                          |                        |  |  |  |

|                                                                                         |                                   | 22                                                    | 60       | μA       | -10°C                             |                                          |                        |  |  |  |

|                                                                                         |                                   | 22                                                    | 65       | μA       | +25°C                             | VDD = 3.0V                               | 32 kHz on Timer1       |  |  |  |

|                                                                                         |                                   | 25                                                    | 75       | μA       | +70°C                             |                                          |                        |  |  |  |

|                                                                                         |                                   | 30                                                    | 75       | μA       | -10°C                             |                                          |                        |  |  |  |

|                                                                                         |                                   | 30                                                    | 85       | μA       | +25°C                             | VDD = 5.0V                               | 32 kHz on Timer1       |  |  |  |

|                                                                                         |                                   | 35                                                    | 100      | μΑ       | +70°C                             |                                          |                        |  |  |  |

| D026                                                                                    | A/D Converter                     | <1                                                    | 2        | μA       | +25°C                             | VDD = 2.0V                               |                        |  |  |  |

| ( $\Delta$ IAD)                                                                         |                                   | <1                                                    | 2        | μΑ       | +25°C                             | VDD = 3.0V                               | A/D on, not converting |  |  |  |

|                                                                                         |                                   | <1                                                    | 2        | μA       | +25°C                             | VDD = 5.0V                               |                        |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

4: The band gap reference is a shared resource used by both BOR and LVD modules. Enabling both modules will consume less than the specified sum current of the modules.

| Param<br>No. | Symbol | Characteristic                      | Min | Тур | Мах | Units | Conditions |

|--------------|--------|-------------------------------------|-----|-----|-----|-------|------------|

| 22†          | TINP   | INT pin High or Low Time            | Тсү |     |     | ns    |            |

| 23†          | Trbp   | RB7:RB4 Change INT High or Low Time | Тсү | —   | _   | ns    |            |

| 24†          | TRCP   | RC7:RC4 Change INT High or Low Time | 20  |     |     | ns    |            |

† These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC mode, where CLKO output is 4 x Tosc.

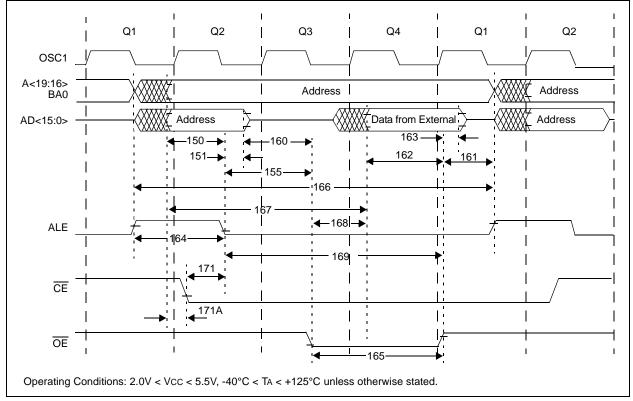

# FIGURE 27-7: PROGRAM MEMORY READ TIMING DIAGRAM

#### TABLE 27-9: PROGRAM MEMORY READ TIMING REQUIREMENTS

| Param.<br>No | Symbol   | Characteristics                                                           | Min           | Тур       | Max | Units |

|--------------|----------|---------------------------------------------------------------------------|---------------|-----------|-----|-------|

| 150          | TadV2alL | Address Out Valid to ALE $\downarrow$ (address setup time)                | 0.25 Tcy – 10 | —         |     | ns    |

| 151          | TalL2adl | ALE $\downarrow$ to Address Out Invalid (address hold time)               | 5             | _         | _   | ns    |

| 155          | TalL2oeL | ALE $\downarrow$ to $\overline{OE} \downarrow$                            | 10            | 0.125 Tcy | —   | ns    |

| 160          | TadZ2oeL | AD high-Z to $\overline{OE} \downarrow$ (bus release to $\overline{OE}$ ) | 0             | —         | —   | ns    |

| 161          | ToeH2adD | OE ↑ to AD Driven                                                         | 0.125 Tcy – 5 | _         | _   | ns    |

| 162          | TadV2oeH | LS Data Valid before $\overline{OE} \uparrow$ (data setup time)           | 20            | _         |     | ns    |

| 163          | ToeH2adl | $\overline{OE}$ $\uparrow$ to Data In Invalid (data hold time)            | 0             | _         | _   | ns    |

| 164          | TalH2alL | ALE Pulse Width                                                           | —             | 0.25 TCY  | _   | ns    |

| 165          | ToeL2oeH | OE Pulse Width                                                            | 0.5 Tcy – 5   | 0.5 TCY   | _   | ns    |

| 166          | TalH2alH | ALE $\uparrow$ to ALE $\uparrow$ (cycle time)                             | 40 ns         | Тсү       |     | ns    |

# APPENDIX A: REVISION HISTORY

# Revision A (July 2003)

Original data sheet for PIC18F6525/6621/8525/8621 family.

# Revision B (August 2004)

This revision includes updates to the Electrical Specifications in **Section 27.0**, the DC and AC Characteristics Graphs and Tables in **Section 28.0** have been added and includes minor corrections to the data sheet text.

# Revision C (January 2013)

Added a note to each package outline drawing.

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1.

# TABLE B-1: DEVICE DIFFERENCES

PIC18F6525 PIC18F6621 PIC18F8525 PIC18F8621 Feature On-chip Program Memory (Kbytes) 48K 64K 48K 64K I/O Ports Ports A, B, C, D, E, F, G E, F, G E, F, G, H, J E, F, G, H, J A/D Channels 12 12 16 16 Yes External Memory Interface No No Yes Package Types 64-pin TQFP 64-pin TQFP 80-pin TQFP 80-pin TQFP

NOTES:

| Analog Port Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

| Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 116                              |

| LATE Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| PORTE Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| PSP Mode Select (PSPMODE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

| RE0/AD8/RD/P2D Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| RE1/AD9/WR/P2C Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| RE2/AD10/CS/P2B Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |

| TRISE Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 114                              |

| PORTF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 119                              |

| Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| LATF Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| PORTF Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| TRISF Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| PORTG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 404                              |

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

| Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| LATG Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| PORTG Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| TRISG Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120                              |

| PORTH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

| Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| LATH Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| PORTH Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |