Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 69                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.75K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

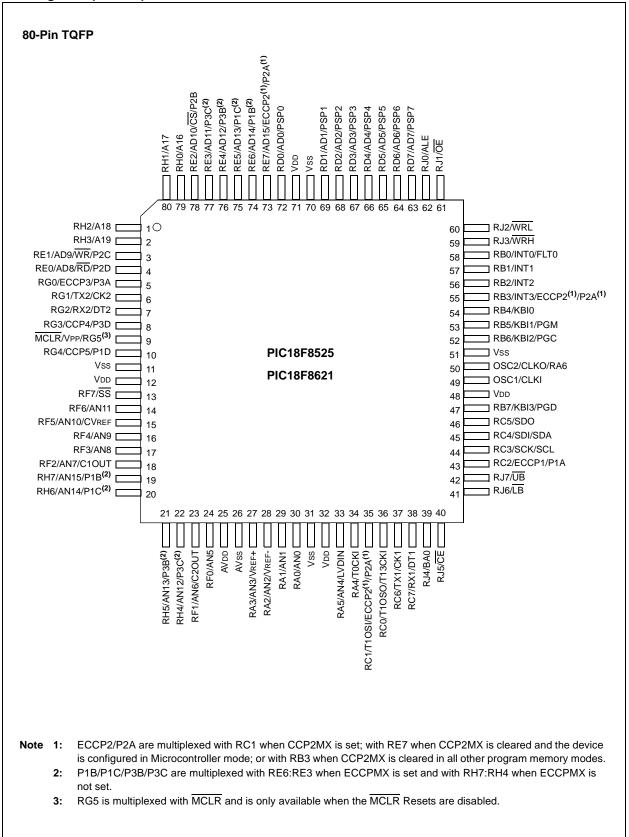

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8525t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Pin Diagrams (Cont.'d)

| Din Nome            | Pin N                           | Pin Number  |             |            | Description                         |

|---------------------|---------------------------------|-------------|-------------|------------|-------------------------------------|

| Pin Name            | PIC18F6X2X PIC18F8X2X Type Type |             | Description |            |                                     |

|                     |                                 |             |             |            | PORTG is a bidirectional I/O port.  |

| RG0/ECCP3/P3A       | 3                               | 5           |             |            |                                     |

| RG0                 | Ū,                              | Ũ           | I/O         | ST         | Digital I/O.                        |

| ECCP3               |                                 |             | 1/O         | ST         | Enhanced Capture 3 input, Compare 3 |

| 200.0               |                                 |             | ., C        | •          | output, PWM 3 output.               |

| P3A                 |                                 |             | 0           | _          | ECCP3 output P3A.                   |

| RG1/TX2/CK2         | 4                               | 6           | _           |            |                                     |

| RG1                 | 4                               | 0           | I/O         | ST         | Digital I/O.                        |

| TX2                 |                                 |             | 0           | 01         | USART2 asynchronous transmit.       |

| CK2                 |                                 |             | 1/0         | ST         | USART2 asynchronous clock           |

| UNZ                 |                                 |             | 1/0         | 51         | (see RX2/DT2).                      |

|                     | _                               | -           |             |            |                                     |

| RG2/RX2/DT2         | 5                               | 7           | 1/0         | от         |                                     |

| RG2                 |                                 |             | I/O         | ST         | Digital I/O.                        |

| RX2                 |                                 |             |             | ST         | USART2 asynchronous receive.        |

| DT2                 |                                 |             | I/O         | ST         | USART2 synchronous data             |

|                     |                                 |             |             |            | (see TX2/CK2).                      |

| RG3/CCP4/P3D        | 6                               | 8           |             |            |                                     |

| RG3                 |                                 |             | I/O         | ST         | Digital I/O.                        |

| CCP4                |                                 |             | I/O         | ST         | Capture 4 input, Compare 4 output,  |

|                     |                                 |             |             |            | PWM 4 output.                       |

| P3D                 |                                 |             | 0           | —          | ECCP3 output P3D.                   |

| RG4/CCP5/P1D        | 8                               | 10          |             |            |                                     |

| RG4                 |                                 |             | I/O         | ST         | Digital I/O.                        |

| CCP5                |                                 |             | I/O         | ST         | Capture 5 input, Compare 5 output,  |

|                     |                                 |             |             |            | PWM 5 output.                       |

| P1D                 |                                 |             | 0           | —          | ECCP1 output P1D.                   |

| RG5                 | 7                               | 9           | —           | —          | See MCLR/VPP/RG5 pin.               |

| Legend: TTL = TTL c | ompatible input                 |             | CMOS        | S = CMOS   | compatible input or output          |

|                     | itt Trigger input with C        | CMOS levels |             | g = Analog |                                     |

| I = Input           |                                 |             | 0           | = Output   |                                     |

| P = Power           | r                               |             | OD          | = Open-I   | Drain (no P diode to VDD)           |

#### TABLE 1-2: PIC18F6525/6621/8525/8621 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Alternate assignment for ECCP2/P2A in PIC18F8525/8621 devices when CCP2MX (CONFIG3H<0>) is not set (all Program Memory modes except Microcontroller).

**2:** Default assignment for ECCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8525/8621 devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8525/8621 devices when ECCPMX (CONFIG3H<1>) is set and for all PIC18F6525/6621 devices.

5: Alternate assignment for ECCP2/P2A in PIC18F8525/8621 devices when CCP2MX is not set (Microcontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8525/8621 devices.

7: Alternate assignment for P1B/P1C/P3B/P3C for PIC18F8525/8621 devices when ECCPMX (CONFIG3H<1>) is not set.

8: AVDD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of the part in user or ICSP<sup>™</sup> modes. See parameter D001 for details.

9: RG5 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

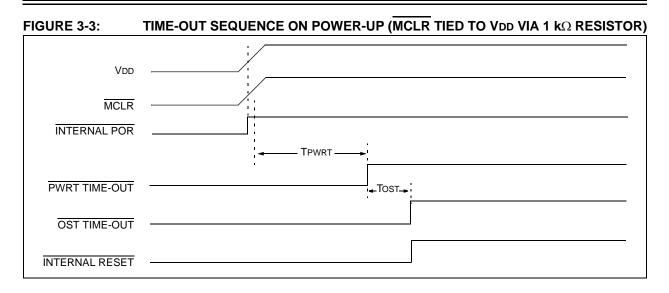

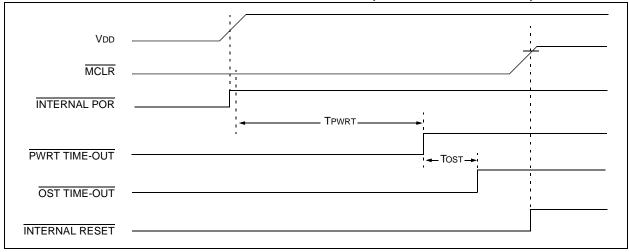

FIGURE 3-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

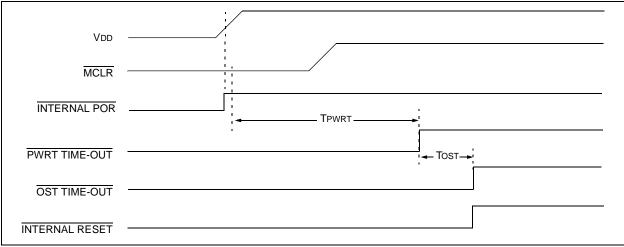

FIGURE 3-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

NOTES:

## 9.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Priority registers (IPR1, IPR2 and IPR3). The operation of the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

|       | R/W-1                      | R/W-1        | R/W-1          | R/W-1          | R/W-1           | R/W-1      | R/W-1        | R/W-1  |

|-------|----------------------------|--------------|----------------|----------------|-----------------|------------|--------------|--------|

|       | PSPIP <sup>(1)</sup>       | ADIP         | RC1IP          | TX1IP          | SSPIP           | CCP1IP     | TMR2IP       | TMR1IP |

|       | bit 7                      |              |                |                |                 |            |              | bit 0  |

| it 7  | PSPIP: Par                 | allel Slave  | Port Read/W    | /rite Interrup | ot Priority bit | (1)        |              |        |

|       | 1 = High pr<br>0 = Low pri | •            |                |                |                 |            |              |        |

|       | Note:                      | Enabled or   | nly in Microc  | ontroller mo   | de for PIC1     | 8F8525/862 | 1 devices.   |        |

| oit 6 | ADIP: A/D (                | Converter li | nterrupt Prio  | rity bit       |                 |            |              |        |

|       | 1 = High pr<br>0 = Low pri | •            |                |                |                 |            |              |        |

| bit 5 | RC1IP: US/                 | ART1 Rece    | ive Interrupt  | Priority bit   |                 |            |              |        |

|       | 1 = High pr<br>0 = Low pri |              |                |                |                 |            |              |        |

| oit 4 | TX1IP: USA                 | RT1 Trans    | mit Interrupt  | Priority bit   |                 |            |              |        |

|       | 1 = High pr<br>0 = Low pri | ,            |                |                |                 |            |              |        |

| bit 3 | SSPIP: Mas                 | ster Synchr  | onous Seria    | l Port Interru | upt Priority b  | it         |              |        |

|       | 1 = High pr<br>0 = Low pri | •            |                |                |                 |            |              |        |

| bit 2 | CCP1IP: EC                 | CCP1 Interr  | upt Priority I | bit            |                 |            |              |        |

|       | 1 = High pr<br>0 = Low pri |              |                |                |                 |            |              |        |

| oit 1 | TMR2IP: TN                 | /IR2 to PR2  | 2 Match Inte   | rrupt Priority | / bit           |            |              |        |

|       | 1 = High pr<br>0 = Low pri | •            |                |                |                 |            |              |        |

| oit 0 |                            |              | ow Interrupt   | Priority bit   |                 |            |              |        |

|       | 1 = High pr                |              |                |                |                 |            |              |        |

|       | 0 = Low pri                | ority        |                |                |                 |            |              |        |

|       | Legend:                    |              |                |                |                 |            |              |        |

|       | R = Readat                 | ole bit      | W = W          | /ritable bit   | U = Unir        | nplemented | bit, read as | '0'    |

| R = Readable bit  | vv = vvritable bit | U = Unimplemented    | bit, read as 0     |

|-------------------|--------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

# 9.5 RCON Register

The RCON register contains the IPEN bit which is used to enable prioritized interrupts. The functions of the other bits in this register are discussed in more detail in **Section 4.14 "RCON Register"**.

| REGISTER 9-13: | RCON: RE    | RCON: RESET CONTROL REGISTER                                                                                                                                   |              |             |     |     |       |       |  |  |  |  |

|----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-----|-----|-------|-------|--|--|--|--|

|                | R/W-0       | U-0                                                                                                                                                            | U-0          | R/W-1       | R-1 | R-1 | R/W-0 | R/W-0 |  |  |  |  |

|                | IPEN        | _                                                                                                                                                              | _            | RI          | TO  | PD  | POR   | BOR   |  |  |  |  |

|                | bit 7       |                                                                                                                                                                |              |             |     |     |       | bit 0 |  |  |  |  |

| bit 7          | 1 = Enable  | <b>IPEN:</b> Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (PIC16 Compatibility mode) |              |             |     |     |       |       |  |  |  |  |

| bit 6-5        | Unimplem    | Unimplemented: Read as '0'                                                                                                                                     |              |             |     |     |       |       |  |  |  |  |

| bit 4          | RI: RESET   | RI: RESET Instruction Flag bit                                                                                                                                 |              |             |     |     |       |       |  |  |  |  |

|                | For details | of bit opera                                                                                                                                                   | tion, see Re | gister 4-4. |     |     |       |       |  |  |  |  |

| bit 3          | TO: Watch   | TO: Watchdog Time-out Flag bit                                                                                                                                 |              |             |     |     |       |       |  |  |  |  |

|                | For details | of bit opera                                                                                                                                                   | tion, see Re | gister 4-4. |     |     |       |       |  |  |  |  |

| bit 2          | PD: Power   | -down Dete                                                                                                                                                     | ction Flag b | it          |     |     |       |       |  |  |  |  |

|                | For details | of bit opera                                                                                                                                                   | tion, see Re | gister 4-4. |     |     |       |       |  |  |  |  |

| bit 1          | POR: Pow    | er-on Reset                                                                                                                                                    | Status bit   |             |     |     |       |       |  |  |  |  |

|                | For details | of bit opera                                                                                                                                                   | tion, see Re | gister 4-4. |     |     |       |       |  |  |  |  |

| bit 0          | BOR: Brov   | BOR: Brown-out Reset Status bit                                                                                                                                |              |             |     |     |       |       |  |  |  |  |

|                | For details | For details of bit operation, see Register 4-4.                                                                                                                |              |             |     |     |       |       |  |  |  |  |

|                |             |                                                                                                                                                                |              |             |     |     |       |       |  |  |  |  |

|                | Legend:     |                                                                                                                                                                |              |             |     |     |       |       |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| REGISTER 10-1: | PSPCON:                                                                                                                                                                                                                                                     | PARALLE | EL SLAVE |         | ITROL RE | GISTER <sup>(1)</sup> |     |       |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|---------|----------|-----------------------|-----|-------|--|--|

|                | R-0                                                                                                                                                                                                                                                         | R-0     | R/W-0    | R/W-0   | U-0      | U-0                   | U-0 | U-0   |  |  |

|                | IBF                                                                                                                                                                                                                                                         | OBF     | IBOV     | PSPMODE | _        | _                     |     | —     |  |  |

|                | bit 7                                                                                                                                                                                                                                                       |         |          |         |          |                       |     | bit 0 |  |  |

| bit 7          | <b>IBF:</b> Input Buffer Full Status bit<br>1 = A word has been received and is waiting to be read by the CPU<br>0 = No word has been received                                                                                                              |         |          |         |          |                       |     |       |  |  |

| bit 6          | <ul> <li>OBF: Output Buffer Full Status bit</li> <li>1 = The output buffer still holds a previously written word</li> </ul>                                                                                                                                 |         |          |         |          |                       |     |       |  |  |

| bit 5          | <ul> <li>0 = The output buffer has been read</li> <li><b>IBOV:</b> Input Buffer Overflow Detect bit</li> <li>1 = A write occurred when a previously input word has not been read (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |         |          |         |          |                       |     |       |  |  |

| bit 4          | <ul> <li>PSPMODE: Parallel Slave Port Mode Select bit</li> <li>1 = Parallel Slave Port mode</li> <li>0 = General Purpose I/O mode</li> </ul>                                                                                                                |         |          |         |          |                       |     |       |  |  |

| bit 3-0        | ·                                                                                                                                                                                                                                                           |         |          |         |          |                       |     |       |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

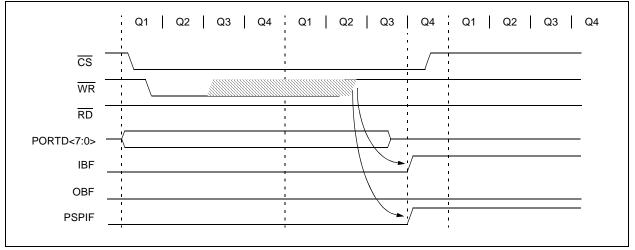

#### FIGURE 10-25: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### 18.3.5 MASTER MODE

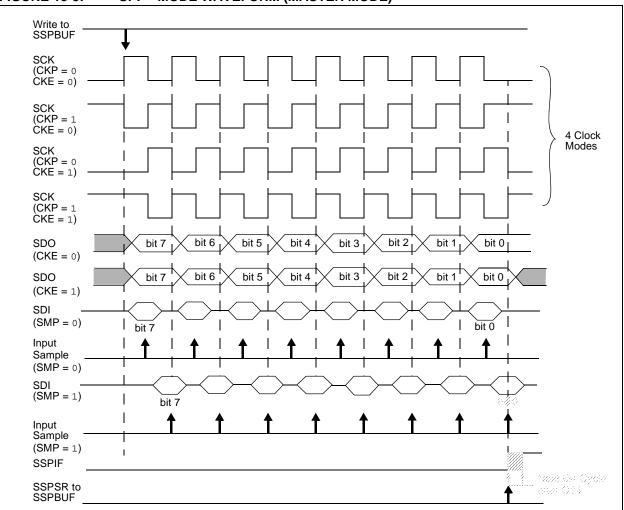

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 18-2) is to broadcast data by the software protocol.

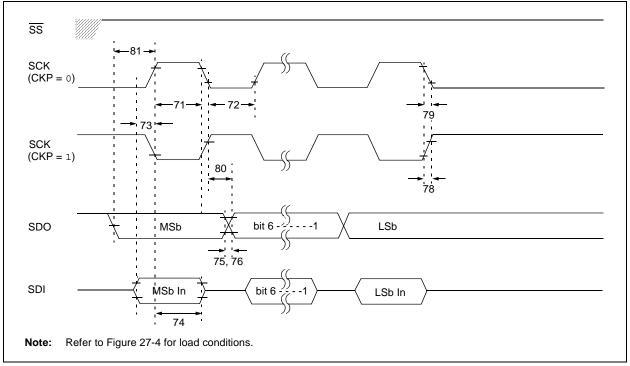

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode. The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This then, would give waveforms for SPI communication as shown in Figure 18-3, Figure 18-5 and Figure 18-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 18-3 shows the waveforms for Master mode.

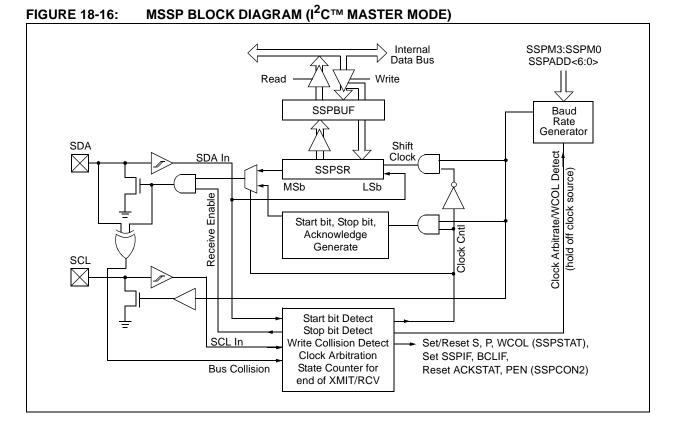

#### 18.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  ${\rm I}^2{\rm C}$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

# Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

#### © 2003-2013 Microchip Technology Inc.

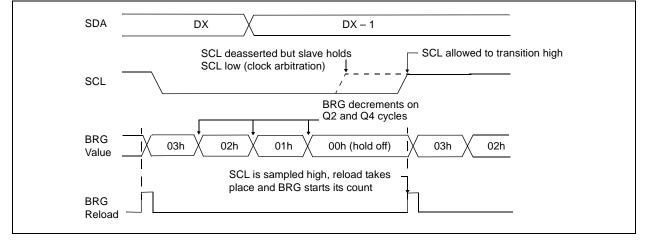

#### 18.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 18-18).

| R/W-0                                                                         | R/W-0                                         | R/W-0         | R/W-0        | R/W-0        | R/W-0      | R-1           | R/W-0 |

|-------------------------------------------------------------------------------|-----------------------------------------------|---------------|--------------|--------------|------------|---------------|-------|

| CSRC                                                                          | TX9                                           | TXEN          | SYNC         | SENDB        | BRGH       | TRMT          | TX9D  |

| bit 7                                                                         |                                               |               |              |              |            |               | bit   |

| CSRC: Clo                                                                     | ock Source S                                  | elect bit     |              |              |            |               |       |

| Asynchron<br>Don't care.                                                      |                                               |               |              |              |            |               |       |

|                                                                               | <u>us mode:</u><br>mode (clock<br>mode (clock |               |              | om BRG)      |            |               |       |

| <b>TX9:</b> 9-bit                                                             | Transmit Ena                                  | able bit      |              |              |            |               |       |

|                                                                               | s 9-bit transı<br>s 8-bit transı              |               |              |              |            |               |       |

| TXEN: Tra                                                                     | nsmit Enable                                  | e bit         |              |              |            |               |       |

|                                                                               | mit enabled<br>mit disabled                   |               |              |              |            |               |       |

| Note:                                                                         | SREN/CRE                                      | N overrides   | STXEN in S   | ync mode.    |            |               |       |

| SYNC: EU                                                                      | SART Mode                                     | Select bit    |              |              |            |               |       |

| -                                                                             | ronous mode<br>hronous mod                    |               |              |              |            |               |       |

| •                                                                             | end Break C                                   |               |              |              |            |               |       |

| Asynchron<br>1 = Send s                                                       |                                               | n next trans  | mission (cle | ared by hard | lware upon | completion)   |       |

| Synchrono<br>Don't care.                                                      |                                               |               |              |              |            |               |       |

| BRGH: Hig                                                                     | gh Baud Rate                                  | e Select bit  |              |              |            |               |       |

| $\begin{array}{l} \underline{Asynchron}\\ 1 = High s\\ 0 = Low s \end{array}$ | peed                                          |               |              |              |            |               |       |

| Synchrono<br>Unused in                                                        | us mode:                                      |               |              |              |            |               |       |

| TRMT: Tra                                                                     | nsmit Shift R                                 | egister Stat  | tus bit      |              |            |               |       |

| 1 = TSR e<br>0 = TSR fr                                                       |                                               |               |              |              |            |               |       |

| <b>TX9D:</b> 9th                                                              | bit of Transn                                 | nit Data      |              |              |            |               |       |

| Can be ad                                                                     | dress/data bi                                 | t or a parity | bit.         |              |            |               |       |

| Legend:                                                                       |                                               |               |              |              |            |               |       |

| R = Reada                                                                     | ble bit                                       | W = V         | Vritable bit | U = Unim     | nplemented | hit read as ' | O'    |

'1' = Bit is set

## REGISTER 19-1: TXSTAX: TRANSMIT STATUS AND CONTROL REGISTER

-n = Value at POR

x = Bit is unknown

'0' = Bit is cleared

## 21.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

## 21.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the comparator Reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators will be powered down during the Reset interval.

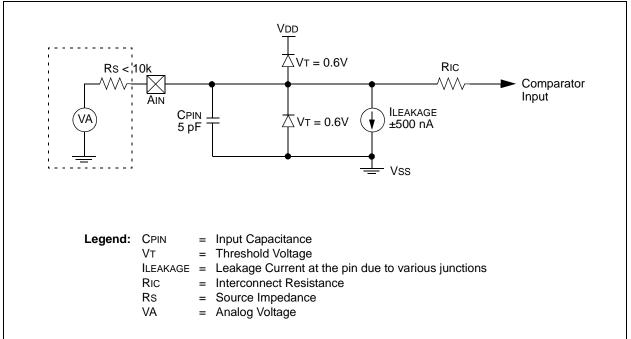

## 21.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 21-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 21-4: COMPARATOR ANALOG INPUT MODEL

| REGISTER 24-12: | CONFIG7                                                      | H: CONFIG              |                 | I REGISTE     | R 7 HIGH     | (BYTE AD                            | DRESS 30       | 000Dh) |  |

|-----------------|--------------------------------------------------------------|------------------------|-----------------|---------------|--------------|-------------------------------------|----------------|--------|--|

|                 | U-0                                                          | R/C-1                  | U-0             | U-0           | U-0          | U-0                                 | U-0            | U-0    |  |

|                 |                                                              | EBTRB                  | _               | _             | _            | _                                   | —              | —      |  |

|                 | bit 7                                                        |                        |                 |               |              |                                     |                | bit 0  |  |

| bit 7           | Unimplem                                                     | ented: Read            | <b>d as</b> '0' |               |              |                                     |                |        |  |

| bit 6           | EBTRB: B                                                     | oot Block Ta           | ble Read Pr     | otection bit  |              |                                     |                |        |  |

|                 |                                                              |                        |                 |               | d from table |                                     |                |        |  |

|                 | 0 = Boot b                                                   | ock (000000            | )-0007FFh)      | protected fro | om table rea | ds executed                         | l in other blo | ocks   |  |

| bit 5-0         | Unimplem                                                     | ented: Read            | <b>d as</b> '0' |               |              |                                     |                |        |  |

|                 | <u> </u>                                                     |                        |                 |               |              |                                     |                |        |  |

|                 | Legend:                                                      |                        |                 |               |              |                                     |                |        |  |

|                 | R = Reada                                                    | ble bit                | C = Clear       | able bit      | U = Unir     | U = Unimplemented bit, read as '0'  |                |        |  |

|                 | -n = Value                                                   | when device            | e is unprogra   | ammed         | u = Uncł     | u = Unchanged from programmed state |                |        |  |

| REGISTER 24-13: | (ADDRES                                                      | DEVICE ID<br>S 3FFFFEI |                 | R 1 FOR P     | IC18F6525    | 5/6621/852                          | 5/8621 DE      |        |  |

|                 | R                                                            | R                      | R               | R             | R            | R                                   | R              | R      |  |

|                 | DEV2                                                         | DEV1                   | DEV0            | REV4          | REV3         | REV2                                | REV1           | REV0   |  |

|                 | bit 7                                                        |                        |                 |               |              |                                     |                | bit 0  |  |

|                 |                                                              |                        |                 |               |              |                                     |                |        |  |

| bit 7-5         | DEV2:DEV<br>100 = PIC<br>101 = PIC<br>110 = PIC<br>111 = PIC | 18F6621<br>18F8525     | ) bits          |               |              |                                     |                |        |  |

bit 4-0 **REV4:REV0:** Revision ID bits

These bits are used to indicate the device revision.

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

# REGISTER 24-14: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F6525/6621/8525/8621 DEVICES (ADDRESS 3FFFFh)

| R-0   | R-0  | R-0  | R-0  | R-1  | R-0  | R-1  | R-0   |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 DEV10:DEV3: Device ID bits

These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number.

0000 1010 = PIC18F6525/6621/8525/8621

| Legend:                                |                      |                                     |

|----------------------------------------|----------------------|-------------------------------------|

| R = Readable bit                       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is unprogrammed |                      | u = Unchanged from programmed state |

## 24.2 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run even if the clock on the OSC1/CLKI and OSC2/CLKO/RA6 pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The  $\overline{TO}$  bit in the RCON register will be cleared upon a WDT time-out.

The Watchdog Timer is enabled or disabled by a device configuration bit, WDTEN (CONFIG2H<0>). If WDTEN is set, software execution may not disable this function. When WDTEN is cleared, the SWDTEN bit enables or disables the operation of the WDT.

The WDT time-out period values may be found in the Electrical Specifications section under parameter 31. Values for the WDT postscaler may be assigned using the configuration bits.

| Note 1: | The CLRWDT and SLEEP instructions        |

|---------|------------------------------------------|

|         | clear the WDT and the postscaler if      |

|         | assigned to the WDT and prevent it from  |

|         | timing out and generating a device Reset |

|         | condition.                               |

2: When a CLRWDT instruction is executed and the postscaler is assigned to the WDT, the postscaler count will be cleared but the postscaler assignment is not changed.

## 24.2.1 CONTROL REGISTER

Register 24-15 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable configuration bit only when the configuration bit has disabled the WDT.

## REGISTER 24-15: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | —   | —   | —   | —   | —   |     | SWDTEN |

| bit 7 |     |     |     |     |     |     | bit 0  |

bit 7-1 Unimplemented: Read as '0'

bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit

- 1 = Watchdog Timer is on

- 0 = Watchdog Timer is turned off (if CONFIG2H<0> = 0)

| Legend:           |                                                             |                      |                    |  |

|-------------------|-------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | ble bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared | x = Bit is unknown |  |

| BCF                                                    | Bit Clear                                                                          | f                                     |                           |                     |

|--------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------|---------------------------|---------------------|

| Syntax:                                                | [label] BC                                                                         | ;F f,b[,a                             | a]                        |                     |

| Operands:                                              | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$ |                                       |                           |                     |

| Operation:                                             | $0 \rightarrow f < b >$                                                            |                                       |                           |                     |

| Status Affected:                                       | None                                                                               |                                       |                           |                     |

| Encoding:                                              | 1001                                                                               | bbba                                  | ffff                      | ffff                |

| Description:                                           | Bit 'b' in reg<br>the Access<br>overriding the<br>the bank wi<br>BSR value         | Bank will<br>he BSR va<br>II be seled | be select<br>alue. If 'a' | ted,<br>= 1, then   |

| Words:                                                 | 1                                                                                  |                                       |                           |                     |

| Cycles:                                                | 1                                                                                  |                                       |                           |                     |

| Q Cycle Activity:                                      |                                                                                    |                                       |                           |                     |

| Q1                                                     | Q2                                                                                 | Q3                                    |                           | Q4                  |

| Decode                                                 | Read<br>register 'f'                                                               | Proces<br>Data                        |                           | Write<br>gister 'f' |

| Example:                                               | BCF F                                                                              | LAG_REG                               | B, 7, 0                   | )                   |

| Before Instruc<br>FLAG_R<br>After Instructic<br>FLAG_R | EG = 0x                                                                            | (C7<br>(47                            |                           |                     |

| BN           |                       | Branch if                                                                                                           | Branch if Negative                                                          |                                               |                                            |  |  |  |

|--------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------|--|--|--|

| Synta        | ax:                   | [label] BN                                                                                                          | [ <i>label</i> ] BN n                                                       |                                               |                                            |  |  |  |

| Oper         | ands:                 | -128 ≤ n ≤                                                                                                          | 127                                                                         |                                               |                                            |  |  |  |

| Oper         | ation:                | 0                                                                                                                   | if Negative bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                    |                                               |                                            |  |  |  |

| Statu        | s Affected:           | None                                                                                                                |                                                                             |                                               |                                            |  |  |  |

| Enco         | ding:                 | 1110                                                                                                                | 0110                                                                        | nnnn                                          | nnnn                                       |  |  |  |

| Desc         | ription:              | If the Nega<br>program wi<br>The 2's cor<br>added to th<br>incremente<br>instruction,<br>PC + 2 + 2<br>two-cycle in | ill branch<br>mplemen<br>le PC. Sir<br>ed to fetch<br>the new<br>n. This in | t number<br>nce the F<br>n the nex<br>address | r '2n' is<br>PC will have<br>tt<br>will be |  |  |  |

| Word         | ls:                   | 1                                                                                                                   |                                                                             |                                               |                                            |  |  |  |

| Cycle        | es:                   | 1(2)                                                                                                                |                                                                             |                                               |                                            |  |  |  |

| Q C<br>If Ju | ycle Activity:<br>mp: |                                                                                                                     |                                                                             |                                               |                                            |  |  |  |

|              | Q1                    | Q2                                                                                                                  | Q3                                                                          | 3                                             | Q4                                         |  |  |  |

|              | Decode                | Read literal<br>'n'                                                                                                 | Proce<br>Data                                                               |                                               | /rite to PC                                |  |  |  |

|              | No<br>operation       | No<br>operation                                                                                                     | No<br>operat                                                                |                                               | No<br>operation                            |  |  |  |

| lf No        | o Jump:               |                                                                                                                     |                                                                             | •                                             |                                            |  |  |  |

|              | Q1                    | Q2                                                                                                                  | Q3                                                                          | 3                                             | Q4                                         |  |  |  |

|              | Decode                | Read literal<br>'n'                                                                                                 | Proce<br>Data                                                               |                                               | No<br>operation                            |  |  |  |

| Example:     |                       | HERE                                                                                                                | BN                                                                          | Jump                                          |                                            |  |  |  |

| Before Instruction<br>PC | = | address (HERE)     |

|--------------------------|---|--------------------|

| After Instruction        |   |                    |

| If Negative              | = | 1;                 |

| PC                       | = | address (Jump)     |

| If Negative              | = | 0;                 |

| PC                       | = | address (HERE + 2) |

| Syntax:       |                                                              | [label] N                                                                                                                                          | /ULLW                                                                                                         | k                                                                                           |                                                                   |

|---------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Operan        |                                                              | 0 ≤ k ≤ 255                                                                                                                                        |                                                                                                               |                                                                                             |                                                                   |

| Operati       |                                                              | (W) x k $\rightarrow$                                                                                                                              | PRODH:P                                                                                                       | RODL                                                                                        |                                                                   |

| Status /      | Affected:                                                    | None                                                                                                                                               |                                                                                                               |                                                                                             |                                                                   |

| Encodir       | ng:                                                          | 0000                                                                                                                                               | 1101                                                                                                          | kkkk                                                                                        | kkkk                                                              |

| Description:  |                                                              | An unsigne<br>out betwee<br>the 8-bit lite<br>placed in F<br>pair. PROD<br>W is uncha<br>None of the<br>Note that n<br>is possible<br>result is po | n the cont<br>eral 'k'. The<br>'RODH:PR<br>DH contain<br>anged.<br>e Status fla<br>weither ove<br>in this ope | ents of W<br>e 16-bit re<br>RODL reg<br>s the high<br>ags are af<br>rflow nor<br>eration. A | Y and<br>esult is<br>ister<br>h byte.<br>fected.<br>carry<br>zero |

| Words:        |                                                              | 1                                                                                                                                                  |                                                                                                               |                                                                                             |                                                                   |

| Cycles:       |                                                              | 1                                                                                                                                                  |                                                                                                               |                                                                                             |                                                                   |

| Q Cycl        | le Activity:                                                 |                                                                                                                                                    |                                                                                                               |                                                                                             |                                                                   |

| -             | Q1                                                           | Q2                                                                                                                                                 | Q3                                                                                                            |                                                                                             | Q4                                                                |

|               | Decode                                                       | Read<br>literal 'k'                                                                                                                                | Proces<br>Data                                                                                                | re                                                                                          | Write<br>gisters<br>RODH:<br>RODL                                 |

| <u>Exampl</u> | <u>e:</u>                                                    | MULLW                                                                                                                                              | 0xC4                                                                                                          |                                                                                             |                                                                   |

|               | efore Instruct<br>W<br>PRODH<br>PRODL<br>ter Instructio<br>W | = 0x<br>= ?<br>= ?<br>n                                                                                                                            | E2                                                                                                            |                                                                                             |                                                                   |

| Syntax:                                      | [label] N                                                                                                                                                      | IULWF                                                                        | f [,a]                                                                                                     |                                                                     |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Operands:                                    | <br>0 ≤ f ≤ 255                                                                                                                                                |                                                                              |                                                                                                            |                                                                     |

|                                              | a ∈ [0,1]                                                                                                                                                      |                                                                              |                                                                                                            |                                                                     |

| Operation:                                   | (W) x (f) $\rightarrow$                                                                                                                                        | PRODH                                                                        | I:PRODL                                                                                                    |                                                                     |

| Status Affected:                             | None                                                                                                                                                           |                                                                              |                                                                                                            |                                                                     |

| Encoding:                                    | 0000                                                                                                                                                           | 001a                                                                         | ffff                                                                                                       | ffff                                                                |

|                                              | is stored in<br>register pai<br>byte.<br>Both W and<br>None of the<br>Note that n<br>possible in<br>is possible<br>the Access<br>overriding t<br>'a' = 1, ther | r. PROD<br>Status<br>either ov<br>this ope<br>but not o<br>Bank wi<br>he BSR | H contain<br>inchange<br>flags are a<br>rerflow no<br>ration. A z<br>detected.<br>ill be sele<br>value. If | d.<br>affected.<br>r carry is<br>zero resu<br>If 'a' is '0<br>cted, |

|                                              | as per the l                                                                                                                                                   | 3SR valu                                                                     | ue (defaul                                                                                                 |                                                                     |

| Words:                                       | as per the I<br>1                                                                                                                                              | BSR valı                                                                     | ue (defaul                                                                                                 |                                                                     |

| Words:<br>Cycles:                            | •                                                                                                                                                              | 3SR valı                                                                     | ue (defaul                                                                                                 |                                                                     |

| Cycles:                                      | 1                                                                                                                                                              | 3SR valı                                                                     | ue (defaul                                                                                                 |                                                                     |

|                                              | 1                                                                                                                                                              | 3SR valı<br>Q3                                                               | ,                                                                                                          |                                                                     |

| Cycles:<br>Q Cycle Activity:                 | 1<br>1                                                                                                                                                         |                                                                              | 3<br>ess<br>a r<br>F                                                                                       | lt).                                                                |

| Cycles:<br>Q Cycle Activity:<br>Q1           | 1<br>1<br>Q2<br>Read<br>register 'f'                                                                                                                           | Q                                                                            | 3<br>ess<br>a r<br>F                                                                                       | Q4<br>Write<br>egisters<br>PRODH:                                   |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode | 1<br>1<br>Q2<br>Read<br>register 'f'                                                                                                                           | Q3<br>Proce<br>Dat                                                           | 3<br>ess<br>a r<br>F                                                                                       | Q4<br>Write<br>egisters<br>PRODH:                                   |

0xC4

0xB5

0x8A

0x94

? ? =

=

=

= = =

PRODH

PRODL

After Instruction W

REG

PRODH

PRODL

| Param.<br>No. | Symbol                | Characteris                              | Min                           | Max | Units | Conditions |   |

|---------------|-----------------------|------------------------------------------|-------------------------------|-----|-------|------------|---|

| 73            | TdiV2scH,<br>TdiV2scL | Setup Time of SDI Data Input             | 100                           |     | ns    |            |   |

| 73A           | Тв2в                  | Last Clock Edge of Byte 1 to t<br>Byte 2 | 1.5 Tcy + 40                  | _   | ns    | (Note 2)   |   |

| 74            | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edge  |                               | 100 | _     | ns         |   |

| 75            | TdoR                  | SDO Data Output Rise Time                | PIC18F6525/6621/<br>8525/8621 | —   | 25    | ns         |   |

|               |                       |                                          | PIC18LF6X2X/8X2X              | _   | 45    | ns         |   |

| 76            | TdoF                  | SDO Data Output Fall Time                |                               | _   | 25    | ns         |   |

| 78            | TscR                  | SCK Output Rise Time<br>(Master mode)    | PIC18F6525/6621/<br>8525/8621 | —   | 25    | ns         |   |

|               |                       |                                          | PIC18LF6X2X/8X2X              | _   | 45    | ns         |   |

| 79            | TscF                  | SCK Output Fall Time (Master             | mode)                         | —   | 25    | ns         |   |

| 80            | TscH2doV,<br>TscL2doV | SDO Data Output Valid after<br>SCK Edge  | PIC18F6525/6621/<br>8525/8621 | —   | 50    | ns         |   |

|               |                       |                                          | PIC18LF6X2X/8X2X              |     | 100   | ns         | ] |

**Note 1:** Requires the use of Parameter #73A.

2: Only if Parameter #71A and #72A are used.

## FIGURE 27-15: EXAMPLE SPI™ MASTER MODE TIMING (CKE = 1)

| Param<br>No. | Symbol                | Characteris                                           | Min                           | Max          | Units | Conditions |  |

|--------------|-----------------------|-------------------------------------------------------|-------------------------------|--------------|-------|------------|--|

| 82           | TssL2doV              | $\frac{\text{SDO}}{\text{SS}} \downarrow \text{Edge}$ | PIC18F6525/6621/<br>8525/8621 |              | 50    | ns         |  |

|              |                       |                                                       | PIC18LF6X2X/8X2X              | _            | 100   | ns         |  |

| 83           | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                                   |                               | 1.5 Tcy + 40 | —     | ns         |  |

Note 1: Requires the use of Parameter #73A.2: Only if Parameter #71A and #72A are used.

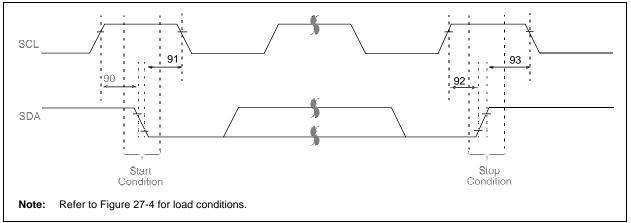

# FIGURE 27-18: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING

| TABLE 27-19: | I <sup>2</sup> C <sup>™</sup> BUS START/STOP | BITS REQUIREMENTS | (SLAVE MODE) |

|--------------|----------------------------------------------|-------------------|--------------|

|--------------|----------------------------------------------|-------------------|--------------|

| Param.<br>No. | Symbol  | Characte        | ristic       | Min  | Max | Units | Conditions                   |  |

|---------------|---------|-----------------|--------------|------|-----|-------|------------------------------|--|

| 90            | TSU:STA | Start Condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated   |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       | Start condition              |  |

| 91            | THD:STA | Start Condition | 100 kHz mode | 4000 |     | ns    | After this period, the first |  |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       | clock pulse is generated     |  |

| 92            | TSU:STO | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                              |  |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                              |  |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                              |  |

|               |         | Hold Time       | 400 kHz mode | 600  |     |       |                              |  |

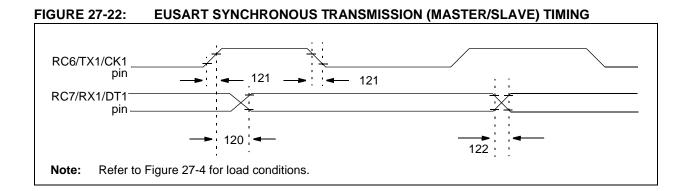

#### TABLE 27-23: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                      |                               | Min | Max | Units | Conditions |

|---------------|----------|---------------------------------------------------------------------|-------------------------------|-----|-----|-------|------------|

| 120           | TckH2dtV | <u>SYNC XMIT (Master and Slave)</u><br>Clock High to Data Out Valid | PIC18F6525/6621/<br>8525/8621 | _   | 40  | ns    |            |

|               |          |                                                                     | PIC18LF6X2X/8X2X              | Ι   | 100 | ns    |            |

| 121           | Tckrf    | Clock Out Rise Time and Fall Time (Master mode)                     | PIC18F6525/6621/<br>8525/8621 | _   | 20  | ns    |            |

|               |          |                                                                     | PIC18LF6X2X/8X2X              | _   | 50  | ns    |            |

| 122           | Tdtrf    | Data Out Rise Time and Fall Time                                    | PIC18F6525/6621/<br>8525/8621 | —   | 20  | ns    |            |

|               |          |                                                                     | PIC18LF6X2X/8X2X              | _   | 50  | ns    |            |

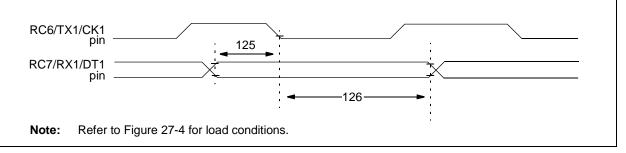

#### FIGURE 27-23: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 27-24: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                                   | Min | Max | Units | Conditions |

|---------------|----------|----------------------------------------------------------------------------------|-----|-----|-------|------------|

| 125           | TdtV2ckl | SYNC RCV (Master and Slave)<br>Data Hold before $CKx \downarrow (DTx hold time)$ | 10  | _   | ns    |            |

| 126           | TckL2dtl | Data Hold after CKx $\downarrow$ (DTx hold time)                                 | 15  |     | ns    |            |

| Timer3                                        | 144       |

|-----------------------------------------------|-----------|

| Timer3 (16-Bit Read/Write Mode)               | 144       |

| Timer4                                        | 148       |

| Watchdog Timer                                | 268       |

| BN                                            | 284       |

| BNC                                           | 285       |

| BNN                                           | 285       |

| BNOV                                          |           |

| BNZ                                           |           |

| BOR. See Brown-out Reset.                     |           |

| BOV                                           | 289       |

| BRA                                           | 287       |

| Break Character (12-Bit) Transmit and Receive | 226       |

| BRG. See Baud Rate Generator.                 |           |

| Brown-out Reset (BOR)                         | . 30, 259 |

| BSF                                           |           |

| BTFSC                                         |           |

| BTFSS                                         |           |

| BTG                                           | 289       |

| BZ                                            | 290       |

|                                               |           |

## С

| C Compilers                                                                                                                                           |                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| MPLAB C17                                                                                                                                             | 8                                |

| MPLAB C18                                                                                                                                             | 8                                |

| MPLAB C30                                                                                                                                             | 8                                |

| CALL                                                                                                                                                  | 90                               |

| Capture (CCP Module)15                                                                                                                                | 51                               |

| Associated Registers                                                                                                                                  |                                  |

| CCP Pin Configuration15                                                                                                                               | 51                               |

| CCPR4H:CCPR4L Registers15                                                                                                                             |                                  |

| Software Interrupt15                                                                                                                                  |                                  |