Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6621-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our Web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

| Din Nama                                                              | Pin N                                  | umber           | Pin  | Buffer   | Description                                 |  |  |

|-----------------------------------------------------------------------|----------------------------------------|-----------------|------|----------|---------------------------------------------|--|--|

| Pin Name                                                              | PIC18F6X2X                             | PIC18F8X2X      | Туре | Туре     | Description                                 |  |  |

|                                                                       |                                        |                 |      |          | PORTE is a bidirectional I/O port.          |  |  |

| RE0/AD8/RD/P2D                                                        | 2                                      | 4               |      |          |                                             |  |  |

| RE0                                                                   |                                        |                 | I/O  | ST       | Digital I/O.                                |  |  |

| AD8 <sup>(3)</sup>                                                    |                                        |                 | I/O  | TTL      | External memory address/data 8.             |  |  |

| RD                                                                    |                                        |                 | I    | TTL      | Read control for Parallel Slave Port.       |  |  |

| P2D                                                                   |                                        |                 | 0    | —        | ECCP2 output P2D.                           |  |  |

| RE1/AD9/WR/P2C                                                        | 1                                      | 3               |      |          |                                             |  |  |

| RE1                                                                   |                                        |                 | I/O  | ST       | Digital I/O.                                |  |  |

| AD9 <sup>(3)</sup>                                                    |                                        |                 | I/O  | TTL      | External memory address/data 9.             |  |  |

| WR                                                                    |                                        |                 | I    | TTL      | Write control for Parallel Slave Port.      |  |  |

| P2C                                                                   |                                        |                 | 0    | ST       | ECCP2 output P2C.                           |  |  |

| RE2/AD10/CS/P2B                                                       | 64                                     | 78              |      |          |                                             |  |  |

| RE2                                                                   |                                        |                 | I/O  | ST       | Digital I/O.                                |  |  |

| <u>AD</u> 10 <sup>(3)</sup>                                           |                                        |                 | I/O  | TTL      | External memory address/data 10.            |  |  |

| CS                                                                    |                                        |                 | I    | TTL      | Chip select control for Parallel Slave Port |  |  |

| P2B                                                                   |                                        |                 | 0    | —        | ECCP2 output P2B.                           |  |  |

| RE3/AD11/P3C                                                          | 63                                     | 77              |      |          |                                             |  |  |

| RE3                                                                   |                                        |                 | I/O  | ST       | Digital I/O.                                |  |  |

| AD11 <sup>(3)</sup>                                                   |                                        |                 | I/O  | TTL      | External memory address/data 11.            |  |  |

| P3C <sup>(4)</sup>                                                    |                                        |                 | 0    | —        | ECCP3 output P3C.                           |  |  |

| RE4/AD12/P3B                                                          | 62                                     | 76              |      |          |                                             |  |  |

| RE4                                                                   |                                        |                 | I/O  | ST       | Digital I/O.                                |  |  |

| AD12 <sup>(3)</sup>                                                   |                                        |                 | I/O  | TTL      | External memory address/data 12.            |  |  |

| P3B <sup>(4)</sup>                                                    |                                        |                 | 0    | _        | ECCP3 output P3B.                           |  |  |

| RE5/AD13/P1C                                                          | 61                                     | 75              |      |          |                                             |  |  |

| RE5                                                                   |                                        |                 | I/O  | ST       | Digital I/O.                                |  |  |

| AD13 <sup>(3)</sup><br>P1C <sup>(4)</sup>                             |                                        |                 | I/O  | TTL      | External memory address/data 13.            |  |  |

|                                                                       |                                        |                 | 0    |          | ECCP1 output P1C.                           |  |  |

| RE6/AD14/P1B                                                          | 60                                     | 74              |      |          |                                             |  |  |

| RE6                                                                   |                                        |                 | I/O  | ST       | Digital I/O.                                |  |  |

| AD14 <sup>(3)</sup><br>P1B <sup>(4)</sup>                             |                                        |                 | I/O  | TTL      | External memory address/data 14.            |  |  |

|                                                                       |                                        |                 | 0    |          | ECCP1 output P1B.                           |  |  |

| RE7/AD15/ECCP2/P2A                                                    | 59                                     | 73              |      |          |                                             |  |  |

| RE7                                                                   |                                        |                 | I/O  | ST       | Digital I/O.                                |  |  |

| AD15 <sup>(3)</sup><br>ECCP2 <sup>(5)</sup>                           |                                        |                 | I/O  | TTL      | External memory address/data 15.            |  |  |

| ECCP2                                                                 |                                        |                 | I/O  | ST       | Enhanced Capture 2 input, Compare 2         |  |  |

| P2A <sup>(5)</sup>                                                    |                                        |                 | 0    |          | output, PWM 2 output.<br>ECCP2 output P2A.  |  |  |

|                                                                       | notible insut                          |                 |      |          |                                             |  |  |

| Legend: TTL = TTL com<br>ST = Schmitt                                 | ipatible input<br>Trigger input with C | MOS levels      |      | g = CMOS | compatible input or output                  |  |  |

| I = Input                                                             |                                        |                 | O    | = Output | input                                       |  |  |

| P = Power                                                             |                                        |                 | OD   | •        | Drain (no P diode to VDD)                   |  |  |

|                                                                       | ment for ECCP2/F                       | 2A in PIC18F852 |      | •        | CCP2MX (CONFIG3H<0>) is not set (all        |  |  |

| •                                                                     | ry modes except N                      | ,               |      |          |                                             |  |  |

| 2: Default assignment for ECCP2/P2A when CCP2MX is set (all devices). |                                        |                 |      |          |                                             |  |  |

#### **TABLE 1-2**. PIC18E6525/6621/8525/8621 PINOUT I/O DESCRIPTIONS (CONTINUED)

3: External memory interface functions are only available on PIC18F8525/8621 devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8525/8621 devices when ECCPMX (CONFIG3H<1>) is set and for all PIC18F6525/6621 devices.

5: Alternate assignment for ECCP2/P2A in PIC18F8525/8621 devices when CCP2MX is not set (Microcontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8525/8621 devices.

7: Alternate assignment for P1B/P1C/P3B/P3C for PIC18F8525/8621 devices when ECCPMX (CONFIG3H<1>) is not set.

8: AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP™ modes. See parameter D001 for details.

9: RG5 is multiplexed with MCLR and is only available when the MCLR Resets are disabled.

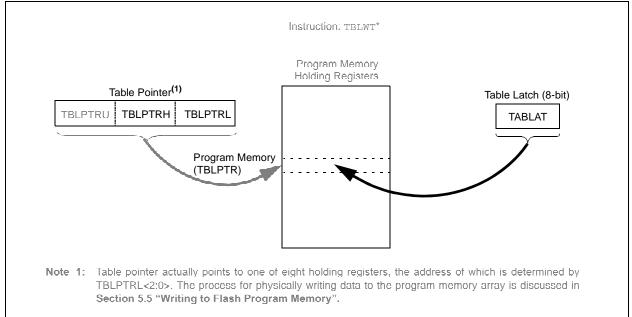

# FIGURE 5-2: TABLE WRITE OPERATION

# 5.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

#### 5.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit, EEPGD, determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

Control bit, CFGS, determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on Configuration registers regardless of EEPGD (see **Section 24.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, will allow a program memory erase operation. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$ Reset or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR) due to Reset values of zero.

| Note: | During normal operation, the WRERR bit is read as '1'. This can indicate that a write |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | operation was prematurely terminated by                                               |  |  |  |  |  |  |  |

|       | a Reset, or a write operation was                                                     |  |  |  |  |  |  |  |

|       | attempted improperly.                                                                 |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

Note: Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

| Name   | Bit 7                         | Bit 6        | Bit 5      | Bit 4      | Bit 3         | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |  |

|--------|-------------------------------|--------------|------------|------------|---------------|--------|--------|--------|-----------------------|---------------------------------|--|

| INTCON | GIE/GIEH                      | PEIE/GIEL    | TMR0IE     | INT0IE     | RBIE          | TMR0IF | INT0IF | RBIF   | 0000 000x             | 0000 000u                       |  |

| EEADRH | — — — — EE Addr Register High |              |            |            |               |        |        | 00     | 00                    |                                 |  |

| EEADR  | Data EEPR                     | OM Address   |            | 0000 0000  | 0000 0000     |        |        |        |                       |                                 |  |

| EEDATA | Data EEPR                     | OM Data Reg  | gister     |            |               |        |        |        | 0000 0000             | 0000 0000                       |  |

| EECON2 | Data EEPR                     | OM Control F | Register 2 | (not a phy | sical registe | er)    |        |        | —                     | —                               |  |

| EECON1 | EEPGD                         | CFGS         | _          | FREE       | WRERR         | WREN   | WR     | RD     | xx-0 x000             | uu-0 u000                       |  |

| IPR2   | _                             | CMIP         | _          | EEIP       | BCLIP         | LVDIP  | TMR3IP | CCP2IP | -1-1 1111             | -1-1 1111                       |  |

| PIR2   |                               | CMIF         | -          | EEIF       | BCLIF         | LVDIF  | TMR3IF | CCP2IF | -0-0 0000             | 0 0000                          |  |

| PIE2   | _                             | CMIE         | _          | EEIE       | BCLIE         | LVDIE  | TMR3IE | CCP2IE | -0-0 0000             | 0 0000                          |  |

#### TABLE 7-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

Legend: x = unknown, u = unchanged, — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

### 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Request Flag registers (PIR1, PIR2 and PIR3).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

#### REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0   | R-0   | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RC1IF | TX1IF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |       |       |       |        |        | bit 0  |

| PSPIF: Parallel Slave Port Read/Write Interrupt Flag bit <sup>(1)</sup>                                                                               |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| <ul> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> </ul>          |   |

| Note 1: Enabled only in Microcontroller mode for PIC18F8525/8621 devices.                                                                             |   |

| ADIF: A/D Converter Interrupt Flag bit                                                                                                                |   |

| <ul> <li>1 = An A/D conversion completed (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                     |   |

| RC1IF: USART1 Receive Interrupt Flag bit                                                                                                              |   |

| <ul> <li>1 = The USART1 receive buffer, RCREGx, is full (cleared when RCREGx is read)</li> <li>0 = The USART1 receive buffer is empty</li> </ul>      |   |

| TX1IF: USART1 Transmit Interrupt Flag bit                                                                                                             |   |

| <ul> <li>1 = The USART1 transmit buffer, TXREGx, is empty (cleared when TXREGx is written)</li> <li>0 = The USART1 transmit buffer is full</li> </ul> | ) |

| SSPIF: Master Synchronous Serial Port Interrupt Flag bit                                                                                              |   |

| <ul><li>1 = The transmission/reception is complete (must be cleared in software)</li><li>0 = Waiting to transmit/receive</li></ul>                    |   |

| CCP1IF: ECCP1 Interrupt Flag bit                                                                                                                      |   |

| <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred                   |   |

| Compare mode:                                                                                                                                         |   |

| <ul><li>1 = A TMR1 register compare match occurred (must be cleared in software)</li><li>0 = No TMR1 register compare match occurred</li></ul>        |   |

| <u>PWM mode:</u><br>Unused in this mode.                                                                                                              |   |

| TMR2IF: TMR2 to PR2 Match Interrupt Flag bit                                                                                                          |   |

| <ul><li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li><li>0 = No TMR2 to PR2 match occurred</li></ul>                              |   |

| TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                              |   |

| <ul> <li>1 = TMR1 register overflowed (must be cleared in software)</li> <li>0 = TMR1 register did not overflow</li> </ul>                            |   |

| Legena.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

# 11.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing the T0CS bit. In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit. In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit (T0SE). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 11.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not readable or writable.

The PSA and T0PS2:T0PS0 bits determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, x and so on) will clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count, but will not change the prescaler    |

|       | assignment.                                 |

#### 11.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

# 11.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or FFFFh to 000h in 16-bit mode. This overflow sets the TMR0IF bit. The interrupt can be masked by clearing the TMR0IE bit. The TMR0IE bit must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep since the timer is shut off during Sleep.

#### 11.4 16-Bit Mode Timer Reads and Writes

TMR0H is not the high byte of the timer/counter in 16-bit mode, but is actually a buffered version of the high byte of Timer0 (refer to Figure 11-2). The high byte of the Timer0 counter/timer is not directly readable nor writable. TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

A write to the high byte of Timer0 must also take place through the TMR0H Buffer register. Timer0 high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

| Name   | Bit 7       | Bit 6                                         | Bit 5   | Bit 4                         | Bit 3 | Bit 2  | Bit 1         | Bit 0 | Value on<br>POR, BOR |      | Value on a<br>other<br>Resets |      |

|--------|-------------|-----------------------------------------------|---------|-------------------------------|-------|--------|---------------|-------|----------------------|------|-------------------------------|------|

| TMR0L  | Timer0 Low  | Fimer0 Low Byte Register                      |         |                               |       |        |               |       |                      | xxxx | uuuu                          | uuuu |

| TMR0H  | Timer0 High | n Byte Regis                                  | ter     |                               |       |        |               |       | 0000                 | 0000 | uuuu                          | uuuu |

| INTCON | GIE/GIEH    | PEIE/GIEL                                     | TMR0IE  | INT0IE                        | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF  | 0000                 | 000x | 0000                          | 000u |

| T0CON  | TMR0ON      | TMROON TO8BIT TOCS TOSE PSA TOPS2 TOPS1 TOPS0 |         |                               |       |        |               |       | 1111                 | 1111 | 1111                          | 1111 |

| TRISA  | —           | TRISA6 <sup>(1)</sup>                         | PORTA D | PORTA Data Direction Register |       |        |               |       |                      |      | -111                          | 1111 |

TABLE 11-1: REGISTERS ASSOCIATED WITH TIMER0

**Note 1:** RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator modes only and read '0' in all other oscillator modes.

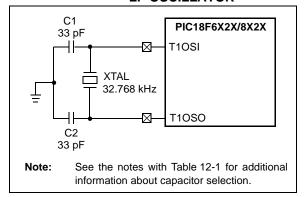

# 12.2 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 12-3. Table 12-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

#### FIGURE 12-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

# TABLE 12-1: CAPACITOR SELECTION FOR THE ALTERNATE OSCILLATOR<sup>(2-4)</sup>

| Osc Type       | Freq      | C1 | C2                      |  |  |  |  |  |

|----------------|-----------|----|-------------------------|--|--|--|--|--|

| LP             | LP 32 kHz |    | 15-22 pF <sup>(1)</sup> |  |  |  |  |  |

| Crystal Tested |           |    |                         |  |  |  |  |  |

| 32.768 kHz     |           |    |                         |  |  |  |  |  |

- **Note 1:** Microchip suggests 33 pF as a starting point in validating the oscillator circuit.

- **2:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

# 12.3 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the TMR1 Interrupt Enable bit, TMR1IE (PIE1<0>).

# 12.4 Resetting Timer1 Using an ECCP Special Trigger Output

If either the ECCP1 or ECCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1. The trigger for ECCP2 will also start an A/D conversion if the A/D module is enabled.

| Note: | The special event triggers from the      |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | ECCP1 module will not set interrupt flag |  |  |  |  |  |  |  |  |

|       | bit TMR1IF (PIR1<0>).                    |  |  |  |  |  |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from ECCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

# 12.5 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

#### 17.4.6 PROGRAMMABLE DEAD-BAND DELAY

In half-bridge applications where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 17-4 for illustration. The lower seven bits of the ECCPxDEL register (Register 17-2) set the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### 17.4.7 ENHANCED PWM AUTO-SHUTDOWN

When an ECCP module is programmed for any PWM mode, the active output pin(s) may be configured for auto-shutdown. Auto-shutdown immediately places the PWM output pin(s) into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by either of the two comparator modules or the INT0/FLT0 pin (or any combination of these three sources). The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a digital signal on the INT0/FLT0 pin can also trigger a shutdown. The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCP1AS2:ECCP1AS0 bits (bits<6:4> of the ECCP1AS register).

When a shutdown occurs, the output pin(s) are asynchronously placed in their shutdown states, specified by the PSS1AC1:PSS1AC0 and PSS1BD1:PSS1BD0 bits (ECCP1AS3:ECCP1AS0). Each pin pair (P1A/P1C and P1B/P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCP1ASE bit (ECCP1AS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCP1ASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the Auto-Shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

# **REGISTER 17-2: ECCPxDEL: PWM CONFIGURATION REGISTER**

|   | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---|--------|-------|-------|-------|-------|-------|-------|-------|

| ſ | PxRSEN | PxDC6 | PxDC5 | PxDC4 | PxDC3 | PxDC2 | PxDC1 | PxDC0 |

| - | bit 7  |       |       |       |       |       |       | bit 0 |

bit 7 PxRSEN: PWM Restart Enable bit

- 1 = Upon Auto-Shutdown, the ECCPxASE bit clears automatically once the shutdown event goes away; the PWM restarts automatically

- 0 = Upon Auto-Shutdown, ECCPxASE must be cleared in software to restart the PWM

bit 6-0 **PxDC6:PxDC0:** PWM Delay Count bits Delay time, in number of Fosc/4 (4 \* Tosc) cycles, between the scheduled and actual time for a PWM signal to transition to active.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 17.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP1 module for PWM operation using Timer2:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- 3. If auto-shutdown is required do the following:

- Disable auto-shutdown (ECCP1AS = 0)

- Configure source (FLT0, Comparator 1 or Comparator 2)

- Wait for non-shutdown condition

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M1:P1M0 bits.

- Select the polarities of the PWM output signals with the CCP1M3:CCP1M0 bits.

- 5. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 6. For Half-Bridge Output mode, set the dead-band delay by loading ECCP1DEL<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCP1AS2:ECCP1AS0 bits.

- Select the shutdown states of the PWM output pins using the PSS1AC1:PSS1AC0 and PSS1BD1:PSS1BD0 bits.

- Set the ECCP1ASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 8. If auto-restart operation is required, set the P1RSEN bit (ECCP1DEL<7>).

- 9. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 10. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRn overflows (TMRnIF bit is set).

- Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCP1ASE bit (ECCP1AS<7>).

#### 17.4.10 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

| Name   | Bit 7        | Bit 6         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|--------|--------------|---------------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| CMCON  | C2OUT        | C1OUT         | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| CVRCON | CVREN        | CVROE         | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 0000 0000       | 0000 0000                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE | INTOIE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 000x       | 0000 000u                       |

| PIR2   | _            | CMIF          | —      | EEIF   | BCLIF  | LVDIF  | TMR3IF | CCP2IF | -0-0 0000       | -0-0 0000                       |

| PIE2   | _            | CMIE          | _      | EEIE   | BCLIE  | LVDIE  | TMR3IE | CCP2IE | -0-0 0000       | -0-0 0000                       |

| IPR2   |              | CMIP          | _      | EEIP   | BCLIP  | LVDIP  | TMR3IP | CCP2IP | -1-1 1111       | -1-1 1111                       |

| PORTF  | RF7          | RF6           | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | x000 0000       | u000 0000                       |

| LATF   | LATF7        | LATF6         | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx xxxx       | uuuu uuuu                       |

| TRISF  | TRISF7       | TRISF6        | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 1111 1111       | 1111 1111                       |

#### TABLE 21-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'.

Shaded cells are unused by the comparator module.

# 22.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The CVRCON register controls the operation of the reference as shown in Register 22-1. The block diagram is given in Figure 22-1.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA3 and RA2. The comparator reference supply voltage is controlled by the CVRSS bit.

# 22.1 Configuring the Comparator Voltage Reference

The comparator voltage reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the comparator voltage reference are as follows:

<u>If CVRR = 1:</u> CVREF = (CVR<3:0>/24) x CVRSRC <u>If CVRR = 0:</u> CVREF=(CVRSRC x 1/4)+(CVR<3:0>/32)xCVRSRC

The settling time of the comparator voltage reference must be considered when changing the CVREF output (Section 27.0 "Electrical Characteristics").

### REGISTER 22-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

|         | R/W-0                         | R/W-0                         | R/W-0        | R/W-0         | R/W-0              | R/W-0           | R/W-0          | R/W-0    |

|---------|-------------------------------|-------------------------------|--------------|---------------|--------------------|-----------------|----------------|----------|

|         | CVREN                         | CVROE <sup>(1)</sup>          | CVRR         | CVRSS         | CVR3               | CVR2            | CVR1           | CVR0     |

|         | bit 7                         |                               |              |               |                    |                 |                | bit 0    |

|         |                               |                               |              |               |                    |                 |                |          |

| bit 7   | CVREN: C                      | omparator Vo                  | oltage Refer | ence Enable   | e bit              |                 |                |          |

|         |                               | circuit powe                  |              |               |                    |                 |                |          |

|         |                               | circuit powe                  |              | (1)           |                    |                 |                |          |

| bit 6   |                               | omparator VF                  |              |               |                    |                 |                |          |

|         |                               | voltage leve<br>voltage is di |              |               |                    | •               |                |          |

|         |                               | 0                             |              |               |                    | •               |                |          |

|         | Note 1:                       | If enabled fo<br>to '1'.      | r output, RI | -5 must also  | be configur        | ed as an inp    | but by setting | IRISE<5> |

| bit 5   | CVRR: Co                      | mparator VRE                  | F Range Se   | election bit  |                    |                 |                |          |

|         |                               | VRSRC to 0.6                  |              |               |                    |                 | • •            |          |

|         | 0 = 0.25 C                    | VRSRC to 0.7                  | 5 CVRSRC,    | with CVRSR    | c/32 step siz      | ze (high rang   | ge)            |          |

| bit 4   | CVRSS: C                      | omparator VF                  | REF Source   | Selection bit | t                  |                 |                |          |

|         |                               | arator referer                |              |               |                    |                 |                |          |

|         |                               | arator referer                |              |               |                    |                 | -,             |          |

| bit 3-0 |                               | R0: Comparat                  | or vref va   | lue Selection | n bits ( $0 \le V$ | $R3:VR0 \le 13$ | 5)             |          |

|         | <u>When CVR</u><br>CVREF = (C | <u>R = 1:</u><br>CVR<3:0>/ 24 | l) • (CVrsr  | C)            |                    |                 |                |          |

|         | When CVR                      |                               |              |               |                    |                 |                |          |

|         | CVREF = 1/                    | 4 • (CVRSRC)                  | ) + (CVR3:0  | CVR0/32) • (  | CVRSRC)            |                 |                |          |

|         |                               |                               |              |               |                    |                 |                |          |

|         | Legend:                       |                               |              |               |                    |                 |                |          |

|         | R = Reada                     | able bit                      | W = W        | ritable bit   | U = Unim           | plemented       | bit, read as   | 0'       |

|         | -n = Value                    | at POR                        | '1' = B      | it is set     | '0' = Bit is       | s cleared       | x = Bit is u   | nknown   |

| BNC          | ov                                         | Not Overfle                                                               | ow                                                                                                                                                                                                                                                                                        |                 |  |  |  |  |

|--------------|--------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Synta        | ax:                                        | [label] BN                                                                | [ <i>label</i> ] BNOV n                                                                                                                                                                                                                                                                   |                 |  |  |  |  |

| Oper         | ands:                                      | -128 ≤ n ≤ 1                                                              | 27                                                                                                                                                                                                                                                                                        |                 |  |  |  |  |

| Oper         | ation:                                     | if Overflow<br>(PC) + 2 -                                                 | bit is '0'<br>+ 2n → PC                                                                                                                                                                                                                                                                   |                 |  |  |  |  |

| Statu        | s Affected:                                | None                                                                      |                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| Enco         | ding:                                      | 1110                                                                      | 0101 nr                                                                                                                                                                                                                                                                                   | inn nnnn        |  |  |  |  |

| Desc         | ription:                                   | program wil<br>The 2's con<br>added to the<br>incremented<br>instruction, | If the Overflow bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two evide instruction |                 |  |  |  |  |

| Word         | ls:                                        | 1                                                                         |                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| Cycle        | es:                                        | 1(2)                                                                      | 1(2)                                                                                                                                                                                                                                                                                      |                 |  |  |  |  |

| Q C<br>If Ju | ycle Activity:<br>mp:                      |                                                                           |                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

|              | Q1                                         | Q2                                                                        | Q3                                                                                                                                                                                                                                                                                        | Q4              |  |  |  |  |

|              | Decode                                     | Read literal<br>'n'                                                       | Process<br>Data                                                                                                                                                                                                                                                                           | Write to PC     |  |  |  |  |

|              | No<br>operation                            | No<br>operation                                                           | No<br>operation                                                                                                                                                                                                                                                                           | No<br>operation |  |  |  |  |

| If No        | o Jump:                                    |                                                                           |                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| 1            | Q1                                         | Q2                                                                        | Q3                                                                                                                                                                                                                                                                                        | Q4              |  |  |  |  |

|              | Decode                                     | Read literal<br>'n'                                                       | Process<br>Data                                                                                                                                                                                                                                                                           | No<br>operation |  |  |  |  |

| Exam         | <u>nple:</u>                               | HERE                                                                      | BNOV Jum                                                                                                                                                                                                                                                                                  | ò               |  |  |  |  |

|              | Before Instruc<br>PC<br>After Instructio   | = ade                                                                     | dress (HERE                                                                                                                                                                                                                                                                               | E)              |  |  |  |  |

|              | If Overflo<br>PC<br>If Overflo<br>PC<br>PC | ow = 0;<br>= ado<br>ow = 1;                                               | dress (Jumg<br>dress (HERE                                                                                                                                                                                                                                                                |                 |  |  |  |  |

| BNZ                   | Branch i                                                                         | Branch if Not Zero                                                                                                                                                                                                                                                                     |             |  |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|

| Syntax:               | [ <i>label</i> ] B                                                               | [ <i>label</i> ] BNZ n                                                                                                                                                                                                                                                                 |             |  |  |  |  |  |

| Operands:             | -128 ≤ n ≤                                                                       | -128 ≤ n ≤ 127                                                                                                                                                                                                                                                                         |             |  |  |  |  |  |

| Operation:            |                                                                                  | if Zero bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                   |             |  |  |  |  |  |

| Status Affected       | l: None                                                                          |                                                                                                                                                                                                                                                                                        |             |  |  |  |  |  |

| Encoding:             | 1110                                                                             | 0001 nn:                                                                                                                                                                                                                                                                               | nn nnnn     |  |  |  |  |  |

| Description:          | program w<br>The 2's co<br>added to tl<br>increment<br>instruction<br>PC + 2 + 2 | If the Zero bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |             |  |  |  |  |  |

| Words:                | 1                                                                                | 1                                                                                                                                                                                                                                                                                      |             |  |  |  |  |  |

| Cycles:               | 1(2)                                                                             | 1(2)                                                                                                                                                                                                                                                                                   |             |  |  |  |  |  |

| Q Cycle Activ         |                                                                                  |                                                                                                                                                                                                                                                                                        |             |  |  |  |  |  |

| Q1                    | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                     | Q4          |  |  |  |  |  |

| Decod                 | e Read literal<br>'n'                                                            | Process<br>Data                                                                                                                                                                                                                                                                        | Write to PC |  |  |  |  |  |

| No                    | No                                                                               | No                                                                                                                                                                                                                                                                                     | No          |  |  |  |  |  |

| operati               | on operation                                                                     | operation                                                                                                                                                                                                                                                                              | operation   |  |  |  |  |  |

| If No Jump:           |                                                                                  |                                                                                                                                                                                                                                                                                        |             |  |  |  |  |  |

| Q1                    | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                     | Q4          |  |  |  |  |  |

| Decod                 | e Read literal                                                                   | Process                                                                                                                                                                                                                                                                                | No          |  |  |  |  |  |

|                       | 'n'                                                                              | Data                                                                                                                                                                                                                                                                                   | operation   |  |  |  |  |  |

| Example:<br>Before In | HERE                                                                             | BNZ Jump                                                                                                                                                                                                                                                                               |             |  |  |  |  |  |

Before Instruction PC = address (HERE) After Instruction If Zero = 0; PC = address (Jump) If Zero = 1; PC = address (HERE + 2)

# 26.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 26.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 26.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, timekeeping and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high-level source debugging with the MPLAB IDE.

# 26.6 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

### 26.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

#### 26.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high-speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

# 27.3 DC Characteristics: PIC18F6525/6621/8525/8621 (Industrial, Extended) PIC18LF6X2X/8X2X (Industrial)

|              |        | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |                    |                    |        |                                                                                                                               |  |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                                                                                                                                                                                                                              | Min                | Max                | Units  | Conditions                                                                                                                    |  |

|              | VIL    | Input Low Voltage                                                                                                                                                                                                                                           |                    |                    |        |                                                                                                                               |  |

|              |        | I/O ports:                                                                                                                                                                                                                                                  |                    |                    |        |                                                                                                                               |  |

| D030         |        | with TTL buffer                                                                                                                                                                                                                                             | Vss                | 0.15 Vdd           | V      | Vdd < 4.5V                                                                                                                    |  |

| D030A        |        |                                                                                                                                                                                                                                                             | —                  | 0.8                | V      | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                              |  |

| D031         |        | with Schmitt Trigger buffer<br>RC3 and RC4                                                                                                                                                                                                                  | Vss<br>Vss         | 0.2 Vdd<br>0.3 Vdd | V<br>V |                                                                                                                               |  |

| D032         |        | MCLR                                                                                                                                                                                                                                                        | Vss                | 0.2 Vdd            | V      |                                                                                                                               |  |

| D033         |        | OSC1                                                                                                                                                                                                                                                        | Vss                | 0.3 Vdd            | V      | HS, HS+PLL modes                                                                                                              |  |

| D033A        |        | OSC1                                                                                                                                                                                                                                                        | Vss                | 0.2 Vdd            | V      | RC, EC modes                                                                                                                  |  |

| D033B        |        | OSC1                                                                                                                                                                                                                                                        | Vss                | 0.3                | V      | XT, LP modes                                                                                                                  |  |

| D034         |        | T1OSI                                                                                                                                                                                                                                                       | Vss                | 0.3                | V      |                                                                                                                               |  |

|              | Vih    | Input High Voltage                                                                                                                                                                                                                                          |                    |                    |        |                                                                                                                               |  |

|              |        | I/O ports:                                                                                                                                                                                                                                                  |                    |                    |        |                                                                                                                               |  |

| D040         |        | with TTL buffer                                                                                                                                                                                                                                             | 0.25 VDD + 0.8V    | Vdd                | V      | Vdd < 4.5V                                                                                                                    |  |