Welcome to E-XFL.COM

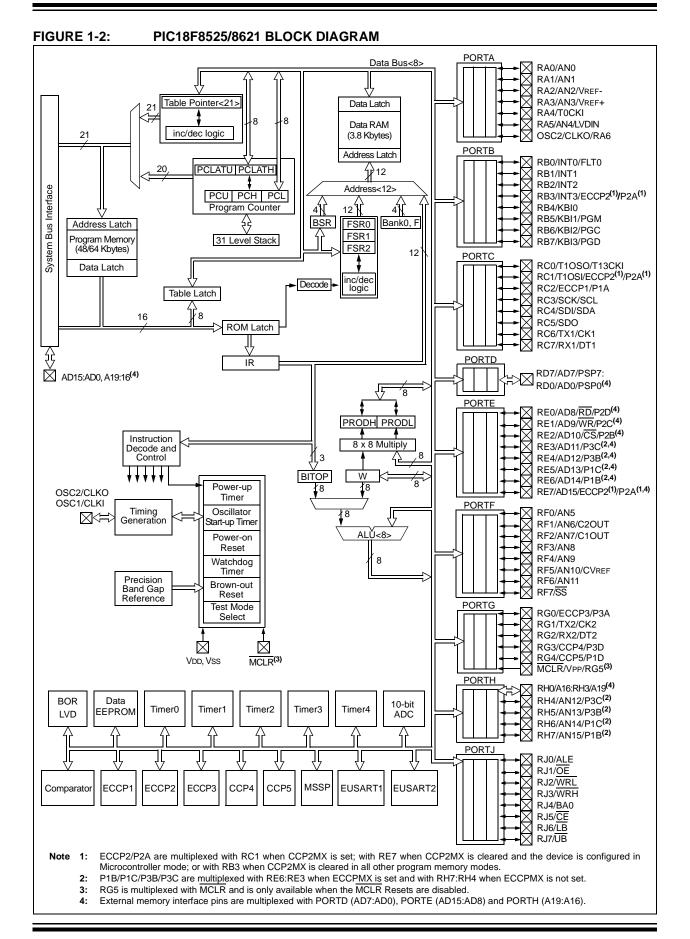

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 53                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6621t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

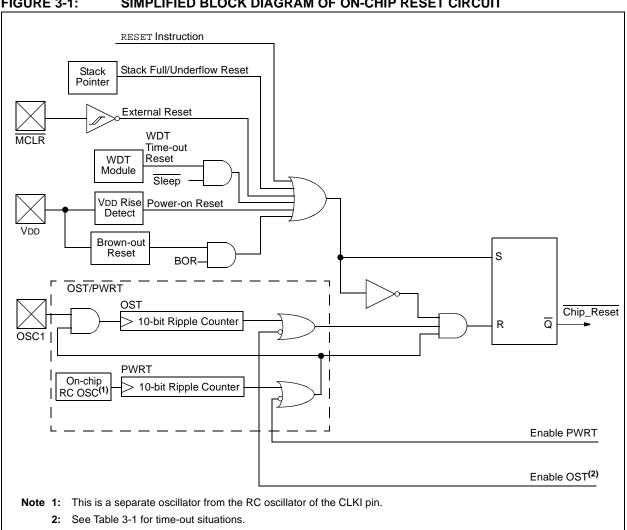

#### 3.0 RESET

The PIC18F6525/6621/8525/8621 devices differentiate between various kinds of Reset:

- Power-on Reset (POR) a)

- b) MCLR Reset during normal operation

- MCLR Reset during Sleep C)

- Watchdog Timer (WDT) Reset (during normal d) operation)

- Programmable Brown-out Reset (BOR) e)

- f) **RESET** Instruction

- Stack Full Reset g)

- h) Stack Underflow Reset

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" on Power-on Reset, MCLR, WDT Reset, Brownout Reset, MCLR Reset during Sleep and by the **RESET** instruction.

Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different Reset situations as indicated in Table 3-2. These bits are used in software to determine the nature of the Reset. See Table 3-3 for a full description of the Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The Enhanced MCU devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses. The MCLR pin is not driven low by any internal Resets, including the WDT.

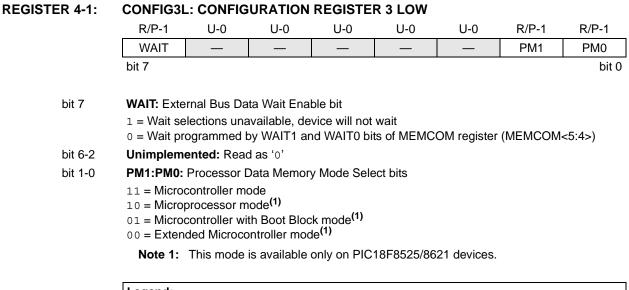

| Legend:                |                      |                      |                    |

|------------------------|----------------------|----------------------|--------------------|

| R = Readable bit       | P = Programmable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value after erase | '1' = Bit is set     | '0' = Bit is cleared | x = Bit is unknown |

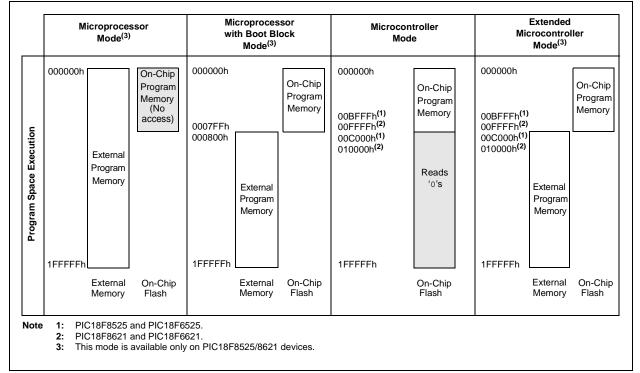

#### FIGURE 4-3: MEMORY MAPS FOR PIC18F6525/6621/8525/8621 PROGRAM MEMORY MODES

### 4.12 Indirect Addressing, INDF and FSR Registers

Indirect addressing is a mode of addressing data memory, where the data memory address in the instruction is not fixed. An FSR register is used as a pointer to the data memory location that is to be read or written. Since this pointer is in RAM, the contents can be modified by the program. This can be useful for data tables in the data memory and for software stacks. Figure 4-9 shows the operation of indirect addressing. This shows the moving of the value to the data memory address specified by the value of the FSR register.

Indirect addressing is possible by using one of the INDF registers. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = 0), will read 00h. Writing to the INDF register indirectly, results in a no operation (NOP). The FSR register contains a 12-bit address which is shown in Figure 4-10.

The INDFn register is not a physical register. Addressing INDFn actually addresses the register whose address is contained in the FSRn register (FSRn is a pointer). This is indirect addressing.

Example 4-5 shows a simple use of indirect addressing to clear the RAM in Bank 1 (locations 100h-1FFh) in a minimum number of instructions.

#### EXAMPLE 4-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|       | LFSR  | FSR0, 0x100 | ; |                |

|-------|-------|-------------|---|----------------|

| NEXT  | CLRF  | POSTINC0    | ; | Clear INDF     |

|       |       |             | ; | register and   |

|       |       |             | ; | inc pointer    |

|       | BTFSS | FSROH, 1    | ; | All done with  |

|       |       |             | ; | Bank1?         |

|       | GOTO  | NEXT        | ; | NO, clear next |

| CONTI | NUE   |             | ; | YES, continue  |

|       |       |             |   |                |

There are three indirect addressing registers. To address the entire data memory space (4096 bytes), these registers are 12 bits wide. To store the 12 bits of addressing information, two 8-bit registers are required. These indirect addressing registers are:

- 1. FSR0: composed of FSR0H:FSR0L

- 2. FSR1: composed of FSR1H:FSR1L

- 3. FSR2: composed of FSR2H:FSR2L

In addition, there are registers INDF0, INDF1 and INDF2, which are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. If an instruction writes a value to INDF0, the value will be written to the address pointed to by FSR0H:FSR0L. A read from INDF1 reads

the data from the address pointed to by FSR1H:FSR1L. INDFn can be used in code anywhere an operand can be used.

If INDF0, INDF1 or INDF2 are read indirectly via an FSR, all '0's are read (zero bit is set). Similarly, if INDF0, INDF1 or INDF2 are written to indirectly, the operation will be equivalent to a NOP instruction and the Status bits are not affected.

#### 4.12.1 INDIRECT ADDRESSING OPERATION

Each FSR register has an INDF register associated with it, plus four additional register addresses. Performing an operation on one of these five registers determines how the FSR will be modified during indirect addressing.

When data access is done to one of the five INDFn locations, the address selected will configure the FSRn register to:

- Do nothing to FSRn after an indirect access (no change) INDFn.

- Auto-decrement FSRn after an indirect access (post-decrement) POSTDECn.

- Auto-increment FSRn after an indirect access (post-increment) POSTINCn.

- Auto-increment FSRn before an indirect access (pre-increment) PREINCn.

- Use the value in the WREG register as an offset to FSRn. Do not modify the value of the WREG or the FSRn register after an indirect access (no change) – PLUSWn.

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the STATUS register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

Incrementing or decrementing an FSR affects all 12 bits. That is, when FSRnL overflows from an increment, FSRnH will be incremented automatically.

Adding these features allows the FSRn to be used as a Stack Pointer in addition to its uses for table operations in data memory.

Each FSR has an address associated with it that performs an indexed indirect access. When a data access to this INDFn location (PLUSWn) occurs, the FSRn is configured to add the signed value in the WREG register and the value in FSR to form the address before an indirect access. The FSR value is not changed.

If an FSR register contains a value that points to one of the INDFn, an indirect read will read 00h (zero bit is set), while an indirect write will be equivalent to a NOP (Status bits are not affected).

If an indirect addressing operation is done where the target address is an FSRnH or FSRnL register, the write operation will dominate over the pre- or post-increment/decrement functions.

## 5.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable, during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

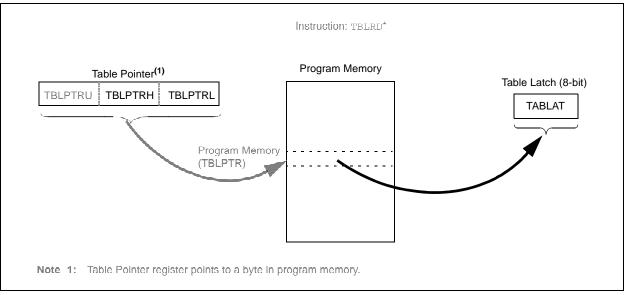

### 5.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 5-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 5.5 "Writing to Flash Program Memory"**. Figure 5-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

#### FIGURE 5-1: TABLE READ OPERATION

| REGISTER 7-1: | EECON1 F                                                                                                                                                                                                                                                                                                                   | REGISTER                                                                                                                                                                                         | (ADDRES                      | S FA6h)                    |                          |              |                |              |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------|--------------------------|--------------|----------------|--------------|--|

|               | R/W-x                                                                                                                                                                                                                                                                                                                      | R/W-x                                                                                                                                                                                            | U-0                          | R/W-0                      | R/W-x                    | R/W-0        | R/S-0          | R/S-0        |  |

|               | EEPGD                                                                                                                                                                                                                                                                                                                      | CFGS                                                                                                                                                                                             | _                            | FREE                       | WRERR                    | WREN         | WR             | RD           |  |

|               | bit 7                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                  |                              |                            |                          |              |                | bit 0        |  |

|               |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                  |                              |                            |                          |              |                |              |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                |                              |                            | ry Select bit            |              |                |              |  |

|               |                                                                                                                                                                                                                                                                                                                            | s Flash prog<br>s data EEPF                                                                                                                                                                      |                              | •                          |                          |              |                |              |  |

| bit 6         |                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                |                              |                            | iguration Sel            | lect bit     |                |              |  |

|               |                                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                |                              | ration registe<br>EEPROM r |                          |              |                |              |  |

| bit 5         | Unimplem                                                                                                                                                                                                                                                                                                                   | ented: Read                                                                                                                                                                                      | <b>d as</b> '0'              |                            |                          |              |                |              |  |

| bit 4         | FREE: Flas                                                                                                                                                                                                                                                                                                                 | sh Row Eras                                                                                                                                                                                      | e Enable bi                  | t                          |                          |              |                |              |  |

|               | (cleare                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                  |                              | w addresse<br>e operation) | d by TBLPTI              | R on the ne  | kt WR comm     | hand         |  |

| bit 3         | WRERR: F                                                                                                                                                                                                                                                                                                                   | lash Progra                                                                                                                                                                                      | m/Data EEF                   | PROM Error                 | Flag bit                 |              |                |              |  |

|               | (any M                                                                                                                                                                                                                                                                                                                     | <ul> <li>1 = A write operation is prematurely terminated<br/>(any MCLR or any WDT Reset during self-timed programming in normal operation)</li> <li>0 = The write operation completed</li> </ul> |                              |                            |                          |              |                |              |  |

|               | Note:                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                  | RERR occu<br>ne error con    |                            | GD or FRE                | E bits are n | ot cleared.    | This allows  |  |

| bit 2         | WREN: Fla                                                                                                                                                                                                                                                                                                                  | ish Program                                                                                                                                                                                      | /Data EEPF                   | ROM Write E                | nable bit                |              |                |              |  |

|               |                                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                | •                            | ogram/data<br>rogram/data  |                          |              |                |              |  |

| bit 1         | WR: Write                                                                                                                                                                                                                                                                                                                  | Control bit                                                                                                                                                                                      |                              |                            |                          |              |                |              |  |

|               | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete. The<br/>WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                                                                                                                                                                                                  |                              |                            |                          |              |                |              |  |

| bit 0         | RD: Read (                                                                                                                                                                                                                                                                                                                 | Control bit                                                                                                                                                                                      |                              |                            |                          |              |                |              |  |

|               | (Read<br>in softw                                                                                                                                                                                                                                                                                                          | ware. RD bit                                                                                                                                                                                     | /cle. RD is c<br>cannot be s | set when EE                | rdware. The<br>PGD = 1.) | RD bit can o | only be set (r | not cleared) |  |

|               | 0 = Does r                                                                                                                                                                                                                                                                                                                 | not initiate a                                                                                                                                                                                   | n EEPRÓM                     | read                       |                          |              |                |              |  |

|               | Legend:                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                  |                              |                            |                          |              |                |              |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| ER 9-11:     | IPRZ: PER               | IPHERAL        | INTERRU         |                 | I Y REGIS    | IER Z     |              |        |

|--------------|-------------------------|----------------|-----------------|-----------------|--------------|-----------|--------------|--------|

|              | U-0                     | R/W-1          | U-0             | R/W-1           | R/W-1        | R/W-1     | R/W-1        | R/W-1  |

|              |                         | CMIP           | _               | EEIP            | BCLIP        | LVDIP     | TMR3IP       | CCP2IP |

|              | bit 7                   |                |                 |                 |              |           |              | bit 0  |

|              |                         |                |                 |                 |              |           |              |        |

| bit 7        | Unimplem                | ented: Read    | <b>d as</b> '0' |                 |              |           |              |        |

| bit 6        | CMIP: Con               | nparator Inte  | errupt Priority | y bit           |              |           |              |        |

|              | 1 = High p              |                |                 |                 |              |           |              |        |

|              | 0 = Low pr              | •              |                 |                 |              |           |              |        |

| bit 5        | •                       | ented: Read    |                 |                 |              |           |              |        |

| bit 4        |                         |                | -lash Write (   | Operation Inf   | errupt Prior | ity bit   |              |        |

|              | 1 = High p              | ,              |                 |                 |              |           |              |        |

| <b>L</b> 1 0 | 0 = Low p               | •              |                 |                 |              |           |              |        |

| bit 3        |                         | s Collision Ir | nterrupt Prio   | rity dit        |              |           |              |        |

|              | 1 = High p<br>0 = Low p | ,              |                 |                 |              |           |              |        |

| bit 2        | •                       | •              | etect Interru   | pt Priority bit |              |           |              |        |

|              | 1 = High p              | •              |                 |                 |              |           |              |        |

|              | 0 = Low pi              | riority        |                 |                 |              |           |              |        |

| bit 1        | TMR3IP: T               | MR3 Overflo    | ow Interrupt    | Priority bit    |              |           |              |        |

|              | 1 = High p              | ,              |                 |                 |              |           |              |        |

|              | 0 = Low pr              | riority        |                 |                 |              |           |              |        |

| bit 0        | CCP2IP: E               | CCP2 Interr    | upt Priority I  | oit             |              |           |              |        |

|              | 1 = High p              | •              |                 |                 |              |           |              |        |

|              | 0 = Low pi              | riority        |                 |                 |              |           |              |        |

|              |                         |                |                 |                 |              |           |              | 1      |

|              | Legend:                 |                |                 |                 |              |           |              |        |

|              | R = Reada               |                |                 | ritable bit     |              | •         | bit, read as |        |

|              | -n = Value              | at POR         | '1' = Βi        | it is set       | '0' = Bit i  | s cleared | x = Bit is u | nknown |

### REGISTER 9-11: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

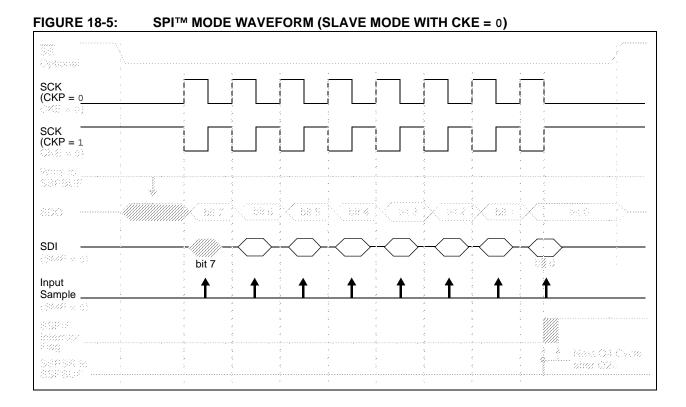

### FIGURE 18-6: SPI™ MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### REGISTER 20-2: ADCON1: A/D CONTROL REGISTER 1

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

|       | —   | VCFG1 | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 **VCFG1:VCFG0:** Voltage Reference Configuration bits:

| VCFG1<br>VCFG0 | A/D Vref+      | A/D VREF-      |  |  |  |  |

|----------------|----------------|----------------|--|--|--|--|

| 00             | AVdd           | AVss           |  |  |  |  |

| 01             | External VREF+ | AVss           |  |  |  |  |

| 10             | AVdd           | External VREF- |  |  |  |  |

| 11             | External VREF+ | External VREF- |  |  |  |  |

bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits:

| PCFG3<br>PCFG0 | AN15 | AN14 | AN13 | AN12 | AN11 | AN10 | AN9 | AN8 | AN7 | AN6 | AN5 | AN4 | AN3 | AN2 | AN1 | ANO |

|----------------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000           | Α    | Α    | А    | Α    | А    | А    | А   | А   | А   | А   | Α   | А   | Α   | А   | Α   | Α   |

| 0001           | D    | D    | А    | Α    | А    | А    | А   | А   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0010           | D    | D    | D    | Α    | А    | А    | А   | А   | А   | А   | А   | А   | Α   | А   | А   | Α   |

| 0011           | D    | D    | D    | D    | А    | А    | А   | А   | А   | А   | А   | А   | Α   | А   | А   | Α   |

| 0100           | D    | D    | D    | D    | D    | А    | А   | А   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0101           | D    | D    | D    | D    | D    | D    | А   | А   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0110           | D    | D    | D    | D    | D    | D    | D   | А   | А   | А   | А   | А   | А   | А   | А   | А   |

| 0111           | D    | D    | D    | D    | D    | D    | D   | D   | А   | А   | А   | А   | А   | А   | А   | А   |

| 1000           | D    | D    | D    | D    | D    | D    | D   | D   | D   | А   | А   | А   | А   | А   | А   | А   |

| 1001           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | А   | А   | А   | А   | А   | А   |

| 1010           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | А   | А   | А   | А   | А   |

| 1011           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | А   | А   | А   | А   |

| 1100           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | А   | А   | А   |

| 1101           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | А   | А   |

| 1110           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | А   |

| 1111           | D    | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

A = Analog input D = Digital I/O

Note: Shaded cells indicate A/D channels available only on PIC18F8525/8621 devices.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|         |                                                              |               |                 |               |               | •       |     | ,     |  |  |

|---------|--------------------------------------------------------------|---------------|-----------------|---------------|---------------|---------|-----|-------|--|--|

|         | R/C-1                                                        | R/C-1         | R/C-1           | U-0           | U-0           | U-0     | U-0 | U-0   |  |  |

|         | WRTD                                                         | WRTB          | WRTC            | —             | —             | —       | —   | —     |  |  |

|         | bit 7                                                        |               |                 |               |               |         |     | bit 0 |  |  |

|         |                                                              |               |                 |               |               |         |     |       |  |  |

| bit 7   | WRTD: Da                                                     | ta EEPRON     | Write Prote     | ection bit    |               |         |     |       |  |  |

|         | 1 = Data E                                                   | EPROM not     | write-protect   | cted          |               |         |     |       |  |  |

|         | 0 = Data EEPROM write-protected                              |               |                 |               |               |         |     |       |  |  |

| bit 6   | WRTB: Bo                                                     | ot Block Wri  | te Protection   | n bit         |               |         |     |       |  |  |

|         | 1 = Boot bl                                                  | ock (000000   | -0007FFh)       | not write-pro | otected       |         |     |       |  |  |

|         | 0 = Boot bl                                                  | ock (000000   | -0007FFh)       | write-protec  | ted           |         |     |       |  |  |

| bit 5   | WRTC: Co                                                     | nfiguration F | Register Wri    | te Protection | n bit         |         |     |       |  |  |

|         | 1 = Configu                                                  | uration regis | ters (30000     | 0-3000FFh)    | not write-pro | otected |     |       |  |  |

|         | 0 = Configuration registers (300000-3000FFh) write-protected |               |                 |               |               |         |     |       |  |  |

| bit 4-0 | Unimplem                                                     | ented: Read   | <b>l as</b> '0' |               |               |         |     |       |  |  |

|         |                                                              |               |                 |               |               |         |     |       |  |  |

|         |                                                              |               |                 |               |               |         |     |       |  |  |

REGISTER 24-10: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| Legend:            |                       |                                     |

|--------------------|-----------------------|-------------------------------------|

| R = Readable bit   | C = Clearable bit     | U = Unimplemented bit, read as '0'  |

| -n = Value when de | evice is unprogrammed | u = Unchanged from programmed state |

REGISTER 24-11: CONFIG7L: CONFIGURATION REGISTER 7 LOW (BYTE ADDRESS 30000Ch)

|   | U-0   | U-0 | U-0 | U-0 | R/C-1                | R/C-1 | R/C-1 | R/C-1 |

|---|-------|-----|-----|-----|----------------------|-------|-------|-------|

|   | —     | —   | —   | —   | EBTR3 <sup>(1)</sup> | EBTR2 | EBTR1 | EBTR0 |

| - | bit 7 |     |     |     |                      |       |       | bit 0 |

- bit 7-4 Unimplemented: Read as '0'

- bit 3 EBTR3: Table Read Protection bit<sup>(1)</sup>

- 1 =Block 3 (00C000-00FFFFh) not protected from table reads executed in other blocks 0 =Block 3 (00C000-00FFFFh) protected from table reads executed in other blocks

Note 1: Unimplemented in PIC18FX525 devices; maintain this bit set.

- bit 2 EBTR2: Table Read Protection bit

- 1 = Block 2 (008000-00BFFFh) not protected from table reads executed in other blocks

- 0 = Block 2 (008000-00BFFFh) protected from table reads executed in other blocks

#### bit 1 **EBTR1:** Table Read Protection bit

1 = Block 1 (004000-007FFFh) not protected from table reads executed in other blocks

0 = Block 1 (004000-007FFFh) protected from table reads executed in other blocks

bit 0 EBTR0: Table Read Protection bit

1 = Block 0 (000800-003FFFh) not protected from table reads executed in other blocks

0 = Block 0 (000800-003FFFh) protected from table reads executed in other blocks

| Legend:              |                    |                                     |

|----------------------|--------------------|-------------------------------------|

| R = Readable bit     | C = Clearable bit  | U = Unimplemented bit, read as '0'  |

| -n = Value when devi | ce is unprogrammed | u = Unchanged from programmed state |

### 24.3 Power-Down Mode (Sleep)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (RCON<3>) is cleared, the TO (RCON<4>) bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The T0CKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 24.3.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INTx pin, RB port change or a peripheral interrupt.

The following peripheral interrupts can wake the device from Sleep:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. TMR3 interrupt. Timer3 must be operating as an asynchronous counter.

- 4. CCP Capture mode interrupt (Capture will not occur).

- 5. MSSP (Start/Stop) bit detect interrupt.

- MSSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RXx or TXx (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation complete.

- 10. LVD interrupt.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and will cause a "wake-up". The TO and PD bits in the RCON register can be used to determine the cause of the device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 2) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address. In cases where the execution of the instruction following Sleep is not desirable, the user should have a NOP after the SLEEP instruction.

#### 24.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If an interrupt condition (interrupt flag bit and interrupt enable bits are set) occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt condition occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### TABLE 25-2: PIC18FXXXX INSTRUCTION SET

| Mnem    | onic,                           | Description                              | Cuala      | 16-E | Bit Instr | uction \ | Nord | Status          | Natas      |

|---------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

| Opera   |                                 | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| BYTE-OR | ENTED I                         | FILE REGISTER OPERATIONS                 |            |      |           |          |      |                 |            |

| ADDWF   | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N |            |

| ADDWFC  | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF   | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1,2        |

| CLRF    | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| COMF    | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ  | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| CPFSGT  | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| CPFSLT  | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| DECF    | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ  | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ  | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INCF    | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ  | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| INFSNZ  | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) |      | 10da      | ffff     | ffff | None            | 1, 2       |

| IORWF   | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |

| MOVF    | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1          |

| MOVFF   | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          |      | ffff      | ffff     |      | None            |            |

|         | 5, U                            | f <sub>d</sub> (destination) 2nd word    |            |      | ffff      | ffff     | ffff |                 |            |

| MOVWF   | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |            |

| MULWF   | f, a                            | Multiply WREG with f                     | 1          |      | 001a      | ffff     |      | None            |            |

| NEGF    | f, a                            | Negate f                                 | 1          |      | 110a      | ffff     |      | C, DC, Z, OV, N | 1.2        |

| RLCF    | f, d, a                         | Rotate Left f through Carry              | 1          |      | 01da      | ffff     |      | C, Z, N         | -, _       |

| RLNCF   | f, d, a                         | Rotate Left f (No Carry)                 | 1          |      | 01da      | ffff     | ffff | Z, N            | 1, 2       |

| RRCF    | f, d, a                         | Rotate Right f through Carry             | 1          |      | 00da      | ffff     |      | C, Z, N         | ., _       |

| RRNCF   | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 |           | ffff     | ffff | Z, N            |            |

| SETF    | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None            |            |

| SUBFWB  | f, d, a                         | Subtract f from WREG with borrow         | 1          | 0101 |           | ffff     |      | C, DC, Z, OV, N | 1, 2       |

| SUBWF   | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWFB  | f, d, a                         | Subtract WREG from f with borrow         | 1          |      | 10da      | ffff     |      | C, DC, Z, OV, N | 1, 2       |

| SWAPF   | f, d, a                         | Swap nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4          |

| TSTFSZ  | f, a                            | Test f, skip if 0                        | 1 (2 or 3) |      | 011a      | ffff     | ffff | None            | 1, 2       |

| XORWF   | f, d, a                         | Exclusive OR WREG with f                 | 1          |      | 10da      | ffff     |      | Z, N            | .,_        |

|         |                                 | E REGISTER OPERATIONS                    |            | 0001 | 2000      |          |      | _,              |            |

| BCF     | f, b, a                         | Bit Clear f                              | 1          | 1001 | bbba      | ffff     | ffff | None            | 1, 2       |

| BSF     | f, b, a                         | Bit Set f                                | 1          |      | bbba      | ffff     | ffff | None            | 1, 2       |

| BTFSC   | f, b, a                         | Bit Test f, Skip if Clear                | 1 (2 or 3) |      | bbba      | ffff     | ffff | None            | 3, 4       |

| BTFSS   | f, b, a                         | Bit Test f, Skip if Set                  | 1 (2 or 3) |      |           | ffff     | ffff | None            | 3, 4       |

| BTG     |                                 | Bit Toggle f                             | 1          |      | bbba      | ffff     | ffff |                 | 1, 2       |

|         |                                 | Port register is modified as a funct     | -          |      |           |          |      |                 |            |

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| Mnemo     | onic,  | Description                     | Cycles | 16-  | Bit Inst | ruction | Word | Status          | Notes |

|-----------|--------|---------------------------------|--------|------|----------|---------|------|-----------------|-------|

| Opera     | nds    | Description                     | Cycles | MSb  |          |         | LSb  | Affected        | Notes |

| LITERAL C | OPERAT | TIONS                           |        |      |          |         |      |                 |       |

| ADDLW     | k      | Add literal and WREG            | 1      | 0000 | 1111     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k      | AND literal with WREG           | 1      | 0000 | 1011     | kkkk    | kkkk | Z, N            |       |

| IORLW     | k      | Inclusive OR literal with WREG  | 1      | 0000 | 1001     | kkkk    | kkkk | Z, N            |       |

| LFSR      | f, k   | Move literal (12-bit) 2nd word  | 2      | 1110 | 1110     | 00ff    | kkkk | None            |       |

|           |        | to FSRx 1st word                |        | 1111 | 0000     | kkkk    | kkkk |                 |       |

| MOVLB     | k      | Move literal to BSR<3:0>        | 1      | 0000 | 0001     | 0000    | kkkk | None            |       |

| MOVLW     | k      | Move literal to WREG            | 1      | 0000 | 1110     | kkkk    | kkkk | None            |       |

| MULLW     | k      | Multiply literal with WREG      | 1      | 0000 | 1101     | kkkk    | kkkk | None            |       |

| RETLW     | k      | Return with literal in WREG     | 2      | 0000 | 1100     | kkkk    | kkkk | None            |       |

| SUBLW     | k      | Subtract WREG from literal      | 1      | 0000 | 1000     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k      | Exclusive OR literal with WREG  | 1      | 0000 | 1010     | kkkk    | kkkk | Z, N            |       |

| DATA MEN  | /ORY ← | PROGRAM MEMORY OPERATI          | ONS    |      |          |         |      |                 |       |

| TBLRD*    |        | Table Read                      | 2      | 0000 | 0000     | 0000    | 1000 | None            |       |

| TBLRD*+   |        | Table Read with post-increment  |        | 0000 | 0000     | 0000    | 1001 | None            |       |

| TBLRD*-   |        | Table Read with post-decrement  |        | 0000 | 0000     | 0000    | 1010 | None            |       |

| TBLRD+*   |        | Table Read with pre-increment   |        | 0000 | 0000     | 0000    | 1011 | None            |       |

| TBLWT*    |        | Table Write                     | 2 (5)  | 0000 | 0000     | 0000    | 1100 | None            |       |

| TBLWT*+   |        | Table Write with post-increment |        | 0000 | 0000     | 0000    | 1101 | None            |       |

| TBLWT*-   |        | Table Write with post-decrement |        | 0000 | 0000     | 0000    | 1110 | None            |       |

| TBLWT+*   |        | Table Write with pre-increment  |        | 0000 | 0000     | 0000    | 1111 | None            |       |

### TABLE 25-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| NEG                                                                                                                                                                                                                                                                                 | )F                                               | Negate f                           |                                    |              |                     |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------|------------------------------------|--------------|---------------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                               | ax:                                              | [label] N                          | [label] NEGF f[,a]                 |              |                     |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                | ands:                                            | 0 ≤ f ≤ 255<br>a ∈ [0,1]           |                                    |              |                     |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                | ation:                                           | $(\overline{f}) + 1 \rightarrow f$ | $(\overline{f}) + 1 \rightarrow f$ |              |                     |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                               | is Affected:                                     | N, OV, C, D                        | N, OV, C, DC, Z                    |              |                     |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                | oding:                                           | 0110                               | 110a                               | ffff         | ffff                |  |  |  |  |

| Description:<br>Location 'f' is negated using 2's<br>complement. The result is placed in the<br>data memory location 'f'. If 'a' is '0', the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then the<br>bank will be selected as per the BSR<br>value. |                                                  |                                    |                                    |              |                     |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                | ls:                                              | 1                                  | 1                                  |              |                     |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                               | es:                                              | 1                                  | 1                                  |              |                     |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                  | ycle Activity:                                   |                                    |                                    |              |                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                     | Q1                                               | Q2                                 | Q3                                 | 8            | Q4                  |  |  |  |  |

|                                                                                                                                                                                                                                                                                     | Decode                                           | Read<br>register 'f'               | Proce<br>Data                      |              | Write<br>gister 'f' |  |  |  |  |

| <u>Exan</u>                                                                                                                                                                                                                                                                         | nple:                                            | NEGF R                             | REG, 1                             |              |                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                     | Before Instruc<br>REG<br>After Instructio<br>REG | = 0011 1                           | 1010 <b>[0</b> )                   | «3A]<br>xC6] |                     |  |  |  |  |

| NOF   | •              | No Opera      | No Operation |     |    |         |  |  |  |

|-------|----------------|---------------|--------------|-----|----|---------|--|--|--|

| Synta | ax:            | [label] N     | [label] NOP  |     |    |         |  |  |  |

| Oper  | ands:          | None          | None         |     |    |         |  |  |  |

| Oper  | ation:         | No operati    | on           |     |    |         |  |  |  |

| Statu | s Affected:    | None          |              |     |    |         |  |  |  |

| Enco  | ding:          | 0000          | 0000         | 000 | 0  | 0000    |  |  |  |

|       |                | 1111          | xxxx         | XXX | x  | XXXX    |  |  |  |

| Desc  | ription:       | No operation. |              |     |    |         |  |  |  |

| Word  | ls:            | 1             | 1            |     |    |         |  |  |  |

| Cycle | es:            | 1             |              |     |    |         |  |  |  |

| QC    | ycle Activity: |               |              |     |    |         |  |  |  |

|       | Q1             | Q2            | Q3           | 3   |    | Q4      |  |  |  |

|       | Decode         | No            | No No        |     |    | No      |  |  |  |

|       |                | operation     | operat       | ion | ор | eration |  |  |  |

#### Example:

None.

| RET         | FIE                                         | Return fro                                                                                                                                            | om Inte                                                                                       | rrupt                                                                                                              |                                                                                       |  |  |  |

|-------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| Synta       | ax:                                         | [ <i>label</i> ] R                                                                                                                                    | ETFIE                                                                                         | [s]                                                                                                                |                                                                                       |  |  |  |

| Oper        | ands:                                       | $s \in [0,1]$                                                                                                                                         |                                                                                               |                                                                                                                    |                                                                                       |  |  |  |

| Oper        | ation:                                      | $(TOS) \rightarrow P'$<br>$1 \rightarrow GIE/Gi$<br>if $s = 1$<br>$(WS) \rightarrow W;$<br>(STATUSS)<br>$(BSRS) \rightarrow$<br>PCLATU, P             | IEH or P<br>) → STAT<br>BSR;                                                                  | rus;                                                                                                               | nged                                                                                  |  |  |  |

| Statu       | s Affected:                                 | GIE/GIEH,                                                                                                                                             | PEIE/GI                                                                                       | EL.                                                                                                                |                                                                                       |  |  |  |

| Enco        | ding:                                       | 0000                                                                                                                                                  | 0000                                                                                          | 0001                                                                                                               | 000s                                                                                  |  |  |  |

| Desc        | ription:                                    | Return from<br>and Top-of-<br>the PC. Inte<br>setting eithe<br>global intern<br>contents of<br>STATUSS a<br>their corres<br>STATUS ar<br>of these reg | Stack (T<br>errupts a<br>er the hig<br>rupt enal<br>the shac<br>and BSR<br>ponding<br>nd BSR. | OS) is loa<br>re enable<br>gh or low  <br>ble bit. If f<br>dow regist<br>S are load<br>registers,<br>If 's' = 0, r | ded into<br>d by<br>priority<br>s' = 1, the<br>ers WS,<br>ded into<br>W,<br>no update |  |  |  |

| Word        | ls:                                         | 1                                                                                                                                                     | <b>3</b> ( )                                                                                  |                                                                                                                    |                                                                                       |  |  |  |

| Cycle       | es:                                         | 2                                                                                                                                                     |                                                                                               |                                                                                                                    |                                                                                       |  |  |  |

| -           | ycle Activity:                              |                                                                                                                                                       |                                                                                               |                                                                                                                    |                                                                                       |  |  |  |

|             | Q1                                          | Q2                                                                                                                                                    | Q3                                                                                            | 5                                                                                                                  | Q4                                                                                    |  |  |  |

|             | Decode                                      | No<br>operation                                                                                                                                       | No<br>operat                                                                                  | ion fro                                                                                                            | Pop PC<br>om stack<br>t GIEH or<br>GIEL                                               |  |  |  |

|             | No<br>operation                             | No<br>operation                                                                                                                                       | No<br>operat                                                                                  | ion oj                                                                                                             | No<br>peration                                                                        |  |  |  |

| <u>Exan</u> | After Interrupt<br>PC<br>W<br>BSR<br>STATUS | RETFIE :                                                                                                                                              | = V<br>= E                                                                                    | TOS<br>VS<br>BSRS<br>STATUSS                                                                                       |                                                                                       |  |  |  |

|       | LW             | Return Li                                                              | teral to                                                                       | VV                            |             |                               |  |  |  |

|-------|----------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------|-------------|-------------------------------|--|--|--|

| Synta | ax:            | [label] R                                                              | [ <i>label</i> ] RETLW k                                                       |                               |             |                               |  |  |  |

| Oper  | ands:          | $0 \le k \le 255$                                                      | $0 \le k \le 255$                                                              |                               |             |                               |  |  |  |

| Oper  | ation:         | · · ·                                                                  | $k \rightarrow W$ ;<br>(TOS) $\rightarrow$ PC;<br>PCLATU, PCLATH are unchanged |                               |             |                               |  |  |  |

| Statu | s Affected:    | None                                                                   |                                                                                |                               |             |                               |  |  |  |

| Enco  | ding:          | 0000                                                                   | 1100                                                                           | kkk                           | k           | kkkk                          |  |  |  |

| Desc  | ription:       | W is loaded<br>The progra<br>top of the s<br>The high ad<br>remains un | m counte<br>tack (the<br>ddress la                                             | er is loa<br>return<br>tch (P | aded<br>add | l from the<br>dress).         |  |  |  |

| Word  | ls:            | 1                                                                      | 1                                                                              |                               |             |                               |  |  |  |

| Cycle | es:            | 2                                                                      |                                                                                |                               |             |                               |  |  |  |

| QC    | ycle Activity: |                                                                        |                                                                                |                               |             |                               |  |  |  |

|       | Q1             | Q2                                                                     | Q3                                                                             | 1                             |             | Q4                            |  |  |  |

|       |                | Read                                                                   | Proce                                                                          |                               | р           |                               |  |  |  |